Page 1

10 MHz to 3 GHz VGA with

www.BDTIC.com/ADI

FEATURES

Voltage-controlled amplifier/attenuator

Operating frequency 10 MHz to 3 GHz

Optimized for controlling output power

High linearity: OIP3 31 dBm @ 900 MHz

Output noise floor: −150 dBm/Hz @ 900 MHz

50 Ω input and output impedances

Single-ended or differential operation

Wide gain-control range: −34 dB to +22 dB @ 900 MHz

Linear-in-dB gain control function, 20 mV/dB

Single-supply 4.75 V to 5.25 V

APPLICATIONS

Transmit and receive power control at RF and IF

GENERAL DESCRIPTION

The ADL5330 is a high performance, voltage-controlled

variable gain amplifier/attenuator for use in applications with

frequencies up to 3 GHz. The balanced structure of the signal

path minimizes distortion while it also reduces the risk of

spurious feed-forward at low gains and high frequencies caused

by parasitic coupling. While operation between a balanced

source and load is recommended, a single-sided input is

internally converted to differential form.

The input impedance is 50 Ω from INHI to INLO. The outputs

a

re usually coupled into a 50 Ω grounded load via a 1:1 balun. A

single supply of 4.75 V to 5.25 V is required.

The 50 Ω input system converts the applied voltage to a pair of

ferential currents with high linearity and good common

dif

rejection even when driven by a single-sided source. The signal

currents are then applied to a proprietary voltage-controlled

attenuator providing precise definition of the overall gain under

the control of the linear-in-dB interface. The GAIN pin accepts

a voltage from 0 V at minimum gain to 1.4 V at full gain with a

20 mV/dB scaling factor.

60 dB Gain Control Range

ADL5330

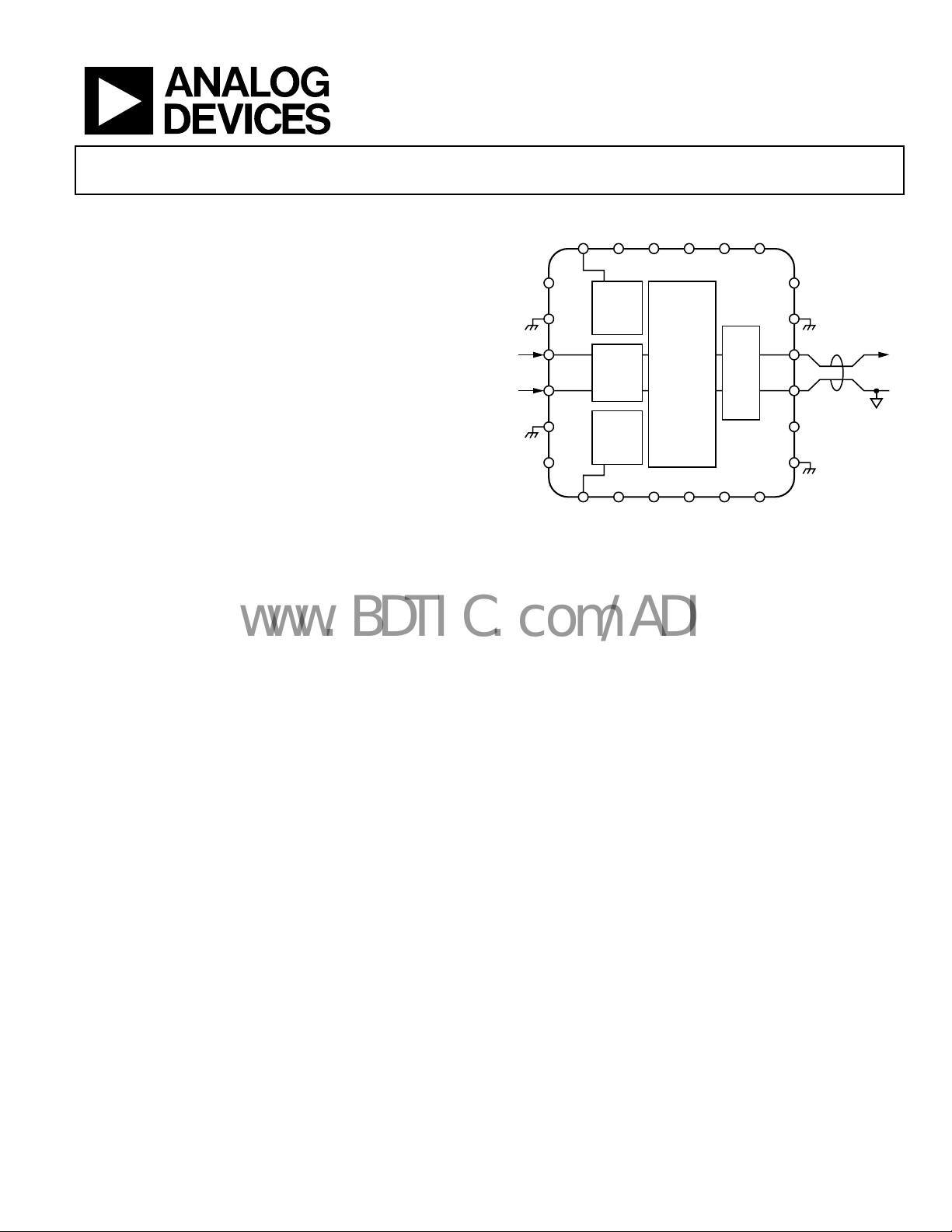

FUNCTIONAL BLOCK DIAGRAM

VPS2

VARIABLE

ATTENUATOR

CONTINUOUSLY

Figure 1.

VPS2VPS2

STAGE

COM2

O/P

(TZ)

COM2COM1OPBS

VPS2

COM2

OPHI

OPLO

COM2

VPS2

RFOUT

BALUN

GAIN

VPS1

COM1

INHI

RFIN

INLO

COM1

VPS1

VREF

ENBL VPS2

GAIN

CONTROL

INPUT

GM

STAGE

BIAS

AND

VREF

IPBS

The output of the high accuracy wideband attenuator is applied

to

a differential transimpedance output stage. The output stage

sets the 50 Ω differential output impedances and drives

Pin OPHI and Pin OPLO. The ADL5330 has a power-down

function. It can be powered down by a Logic LO input on the

ENBL pin. The current consumption in power-down mode is

250 μA.

The ADL5330 is fabricated on an ADI proprietary high

erformance, complementary bipolar IC process. The ADL5330

p

is available in a 24-lead (4 mm × 4 mm), Pb-free LFCSP_VQ

package and is specified for operation from ambient

temperatures of −40°C to +85°C. An evaluation board is also

available.

05134-001

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

Page 2

ADL5330

www.BDTIC.com/ADI

TABLE OF CONTENTS

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 5

ESD Caution.................................................................................. 5

Pin Configuration and Function Descriptions............................. 6

Typical Performance Characteristics............................................. 7

Theory of Operation ...................................................................... 12

Applications..................................................................................... 13

Basic Connections...................................................................... 13

RF Input/Output Interface ........................................................ 14

REVISION HISTORY

6/05—Rev. 0 to Rev. A

Changes to Figure 1.......................................................................... 1

Changes to Table 1............................................................................ 3

Changes to Table 2............................................................................ 5

Changes to Table 3............................................................................ 6

Changes to Figure 27...................................................................... 11

Changes to Figure 35...................................................................... 14

Changes to the Gain Control Input Section................................ 15

Changes to Figure 42...................................................................... 17

Gain Control Input .................................................................... 15

Automatic Gain Control............................................................ 15

Interfacing to an IQ Modulator................................................ 17

WCDMA Transmit Application ............................................... 18

CDMA2000 Transmit Application........................................... 19

Soldering Information ............................................................... 19

Evaluation Board ........................................................................ 20

Outline Dimensions ....................................................................... 24

Ordering Guide .......................................................................... 24

4/05—Revision 0: Initial Version

Rev. A | Page 2 of 24

Page 3

ADL5330

www.BDTIC.com/ADI

SPECIFICATIONS

VS = 5 V; TA = 25°C; M/A-COM ETC1-1-13 1:1 balun at input and output for single-ended 50 Ω match.

Table 1.

Parameter Conditions Min Typ Max Unit

GENERAL

Usable Frequency Range 0.01 3 GHz

Nominal Input Impedance Via 1:1 single-sided-to-differential balun 50 Ω

Nominal Output Impedance Via 1:1 differential-to-single-sided balun 50 Ω

100 MHz

Gain Control Span ±3 dB gain law conformance 58 dB

Maximum Gain V

Minimum Gain V

Gain Flatness vs. Frequency

Gain Control Slope 20.7 mV/dB

Gain Control Intercept Gain = 0 dB, gain = slope (V

Input Compression Point V

Input Compression Point V

Output Third-Order Intercept (OIP3) V

Output Noise Floor

1

Noise Figure V

Input Return Loss

Output Return Loss

2

2

450 MHz

Gain Control Span ±3 dB gain law conformance 57 dB

Maximum Gain V

Minimum Gain V

Gain Flatness vs. Frequency

Gain Control Slope 20.4 mV/dB

Gain Control Intercept Gain = 0 dB, gain = slope (V

Input Compression Point V

Input Compression Point V

Output Third-Order Intercept (OIP3) V

Output Noise Floor

1

Noise Figure V

Input Return Loss

Output Return Loss

2

2

900 MHz

Gain Control Span ±3 dB gain law conformance 53 dB

Maximum Gain V

Minimum Gain V

Gain Flatness vs. Frequency

Gain Control Slope 19.7 mV/dB

Gain Control Intercept Gain = 0 dB, gain = slope (V

Input Compression Point V

Input Compression Point V

Output Third-Order Intercept (OIP3) V

Output Noise Floor

1

Noise Figure V

Input Return Loss

Output Return Loss

2

2

= 1.4 V 23 dB

GAIN

= 0.1 V −35 dB

GAIN

±30 MHz around center frequency,

= 1.0 V (differential output)

V

GAIN

− intercept) 0.88 V

GAIN

= 1.2 V 1.8 dBm

GAIN

= 1.4 V −0.3 dBm

GAIN

= 1.4 V 38 dBm

GAIN

20 MHz carrier offset, V

= 1.4 V 7.8 dB

GAIN

1 V < V

< 1.4 V −12.8 dB

GAIN

= 1.4 V −140 dBm/Hz

GAIN

0.09 dB

−15.5 dB

= 1.4 V 22 dB

GAIN

= 0.1 V −35 dB

GAIN

±30 MHz around center frequency,

V

= 1.0 V, (differential output)

GAIN

− intercept) 0.89 V

GAIN

= 1.2 V 3.3 dBm

GAIN

= 1.4 V 1.2 dBm

GAIN

= 1.4 V 36 dBm

GAIN

20 MHz carrier offset, V

= 1.4 V 8.0 dB

GAIN

1 V < V

< 1.4 V −19 dB

GAIN

= 1.4 V −146 dBm/Hz

GAIN

0.08 dB

−13.4 dB

= 1.4 V 21 dB

GAIN

= 0.2 V −32 dB

GAIN

±30 MHz around center frequency,

V

= 1.0 V (differential output)

GAIN

− intercept) 0.92 V

GAIN

= 1.2 V 2.7 dBm

GAIN

= 1.4 V 1.3 dBm

GAIN

= 1.4 V 31.5 dBm

GAIN

20 MHz carrier offset, V

= 1.4 V 9.0 dB

GAIN

1 V < V

< 1.4 V −18 dB

GAIN

= 1.4 V −144 dBm/Hz

GAIN

0.14 dB

−18 dB

Rev. A | Page 3 of 24

Page 4

ADL5330

www.BDTIC.com/ADI

Parameter Conditions Min Typ Max Unit

2200 MHz

Gain Control Span ±3 dB gain law conformance 46 dB

Maximum Gain V

Minimum Gain V

Gain Flatness vs. Frequency

Gain Control Slope 16.7 mV/dB

Gain Control Intercept Gain = 0 dB, gain = slope (V

Input Compression Point V

Input Compression Point V

Output Third-Order Intercept (OIP3) V

Output Noise Floor

1

Noise Figure V

Input Return Loss

Output Return Loss

2

2

2700 MHz

Gain Control Span ±3 dB gain law conformance 42 dB

Maximum Gain V

Minimum Gain V

Gain Flatness vs. Frequency

Gain Control Slope 16 mV/dB

Gain Control Intercept Gain = 0 dB, gain = slope (V

Input Compression Point V

Input Compression Point V

Output Third-Order Intercept (OIP3) V

Output Noise Floor

1

Noise Figure V

Input Return Loss

Output Return Loss

2

2

GAIN CONTROL INPUT GAIN pin

Gain Control Voltage Range

3

Incremental Input Resistance GAIN pin to COM1 pin 1 MΩ

Response Time Full scale: to within 1 dB of final gain 380 ns

3 dB gain step, P

POWER SUPPLIES Pin VPS1, Pin VPS2, Pin COM1, Pin COM2, Pin ENBL

Voltage 4.75 5 5.25 V

Current, Nominal Active VGN = 0 V 100 mA

V

Current, Disabled ENBL = LO 250 μA

1

Noise floor varies slightly with output power level. See Figure 9 through Figure 13.

2

See Figure 27 and Figure 29 for differential input and output impedances.

3

Minimum gain voltage varies with frequency. See Figure 3 through Figure 7.

= 1.4 V 16 dB

GAIN

= 0.6 V −30 dB

GAIN

±30 MHz around center frequency,

= 1.0 V (differential output)

V

GAIN

− intercept) 1.06 V

GAIN

= 1.2 V 0.9 dBm

GAIN

= 1.4 V −2.0 dBm

GAIN

= 1.4 V 21.2 dBm

GAIN

20 MHz carrier offset, V

= 1.4 V 12.5 dB

GAIN

1 V < V

< 1.4 V −11.7 dB

GAIN

= 1.4 V −147 dBm/Hz

GAIN

0.23 dB

−9.5 dB

= 1.4 V 10 dB

GAIN

= 0.7 V −32 dB

GAIN

±30 MHz around center frequency,

= 1.0 V (differential output)

V

GAIN

− intercept) 1.15 V

GAIN

= 1.2 V 1.2 dBm

GAIN

= 1.4 V −0.9 dBm

GAIN

= 1.4 V 17 dBm

GAIN

20 MHz carrier offset, V

= 1.4 V 14.7 dB

GAIN

1 V < V

< 1.4 V −9.7 dB

GAIN

= 1.4 V −152 dBm/Hz

GAIN

0.3 dB

−5 dB

0 1.4 V

to within 1 dB of final gain 20 ns

OUT

= 1.4 V 215 mA

GN

Rev. A | Page 4 of 24

Page 5

ADL5330

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage VPS1, VPS2 5.5 V

RF Input Power at Maximum Gain 5 dBm at 50 Ω

OPHI, OPLO 5.5 V

ENBL VPS1, VPS2

GAIN 2.5 V

Internal Power Dissipation 1.1 W

θJA (with Pad Soldered to Board) 60°C/W

Maximum Junction Temperature 150°C

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Lead Temperature Range (Soldering 60 sec) 300°C

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rev. A | Page 5 of 24

Page 6

ADL5330

C

C

www.BDTIC.com/ADI

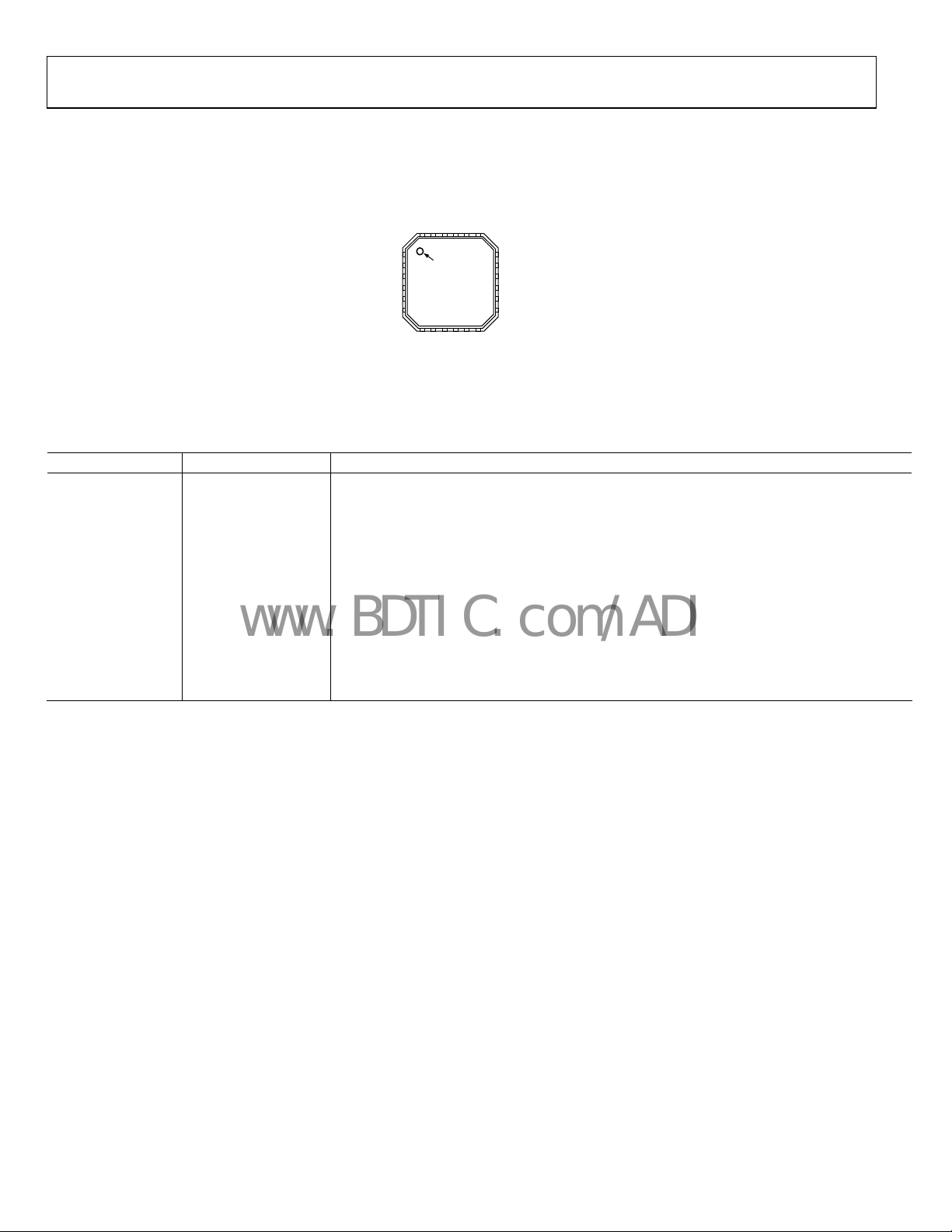

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

GAIN

ENBL

VPS2

VPS2

VPS2

2322212019

PIN 1

INDICATOR

11

10

IPBS

OPBS

GNLO

COM1

VPS2

12

COM2

18

17

16

15

14

13

VPS2

COM2

OPHI

OPLO

COM2

VPS2

05134-002

24

VPS1

1

OM1

2

INHI

3

ADL5330

4

INLO

OM1

VPS1

5

6

TOP VIEW

(Not to Scale)

789

VREF

Figure 2. Pin Configuration

Table 3. Pin Function Descriptions

Pin No. Mnemonic Descriptions

1, 6, 13, 18 to 22 VPS1, VPS2 Positive Supply. Nominally equal to 5 V.

2, 5, 10 COM1 Common for Input Stage.

3, 4 INHI, INLO Differential Inputs, AC-Coupled.

7 VREF Voltage Reference. Output at 1.5 V; normally ac-coupled to ground.

8 IPBS Input Bias. Normally ac-coupled to ground.

9 OPBS Output Bias. AC-Coupled to ground.

11 GNLO Gain Control Common. Connect to ground.

12, 14, 17 COM2 Common for Output Stage.

15 OPLO Low Side of Differential Output. Bias to VP with RF chokes.

16 OPHI High Side of Differential Output. Bias to VP with RF chokes.

23 ENBL Device Enable. Apply logic high for normal operation.

24 GAIN Gain Control Voltage Input. Nominal range 0 V to 1.4 V.

Rev. A | Page 6 of 24

Page 7

ADL5330

www.BDTIC.com/ADI

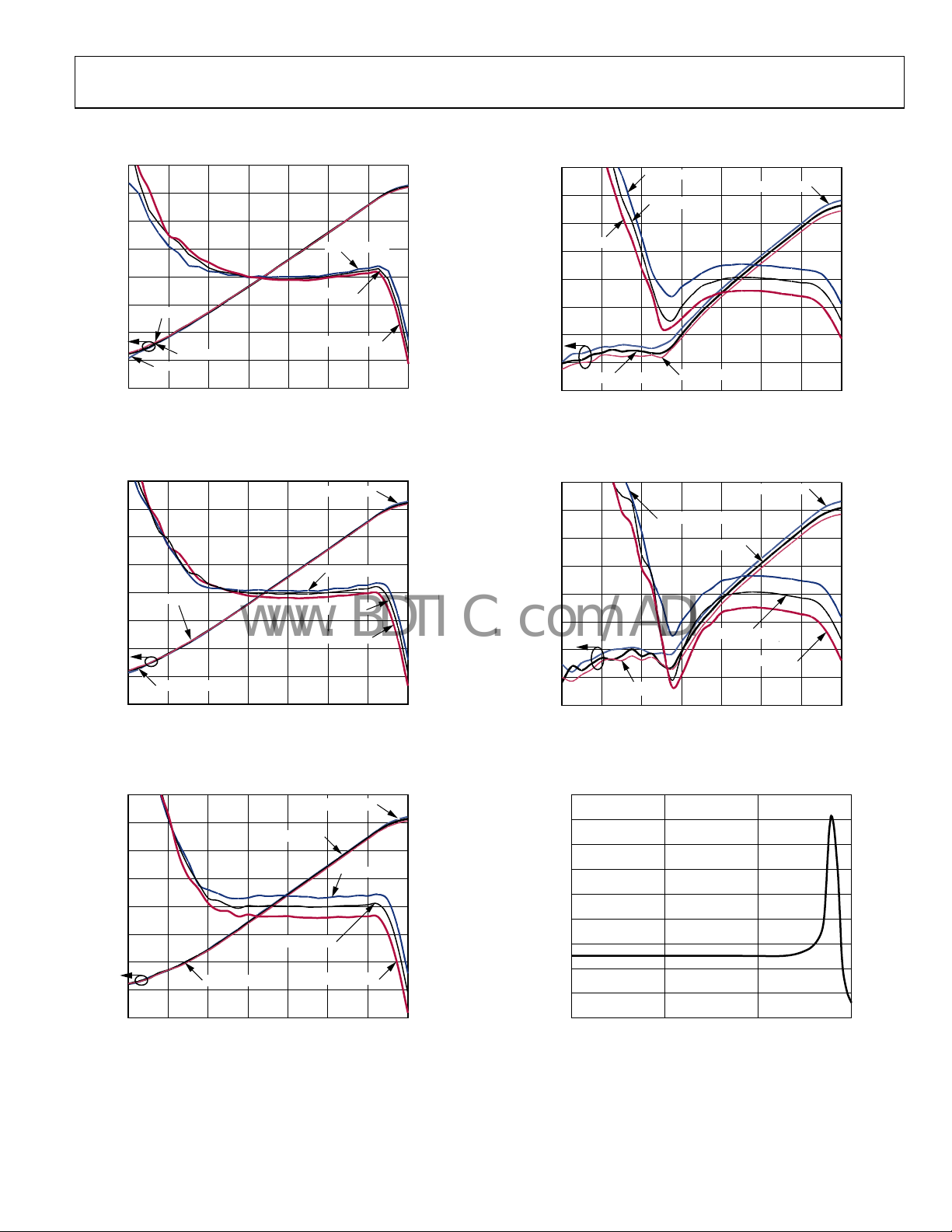

TYPICAL PERFORMANCE CHARACTERISTICS

GAIN (dB)

GAIN (dB)

GAIN (dB)

30

20

10

0

–10

–20

+85°C GAIN

–30

–40

–50

+25°C GAIN

–40°C GAIN

V

GAIN

(V)

Figure 3. Gain and Gain Law Conformance vs. V

over Temperature at 100 MHz

30

20

10

0

–10

+85°C GAIN

–20

–30

–40

–50

+25°C GAIN

V

GAIN

(V)

Figure 4. Gain and Gain Law Conformance vs. V

over Temperature at 450 MHz

30

–10

–20

–30

–40

–50

20

10

0

+85°C GAIN

+25°C GAIN

+25°C ERROR

V

(V)

GAIN

Figure 5. Gain and Gain Law Conformance vs. V

over Temperature at 900 MHz

–40°C ERROR

+25°C ERROR

+85°C ERROR

–40°C GAIN

–40°C ERROR

+25°C ERROR

+85°C ERROR

–40°C GAIN

–40°C ERROR

+85°C ERROR

GAIN

GAIN

GAIN

4

3

2

1

0

–1

–2

GAIN LAW CONFORMANCE (dB)

–3

–4

1.40 0.2 0.4 0.6 0.8 1.0 1.2

05134-003

–10

GAIN (dB)

–20

–30

–40

–50

30

20

10

+85°C ERROR

0

+25°C GAIN

–40°C ERROR

+25°C ERROR

+85°C GAIN

V

GAIN

(V)

Figure 6. Gain and Gain Law Conformance vs. V

–40°C GAIN

GAIN

12

9

6

3

0

–3

–6

GAIN LAW CONFORMANCE (dB)

–9

–12

1.40 0.2 0.4 0.6 0.8 1.0 1.2

over Temperature at 2200 MHz

4

3

2

1

0

–1

–2

GAIN LAW CONFORMANCE (dB)

–3

–4

1.40 0.2 0.4 0.6 0.8 1.0 1.2

05134-004

20

10

0

–10

–20

GAIN (dB)

–30

–40

–50

–60

+85°C GAIN

–40°C ERROR

+25°C GAIN

V

(V)

GAIN

–40°C GAIN

+25°C ERROR

+85°C ERROR

Figure 7. Gain and Gain Law Conformance vs. V

GAIN

12

9

6

3

0

–3

–6

GAIN LAW CONFORMANCE (dB)

–9

–12

1.40 0.2 0.4 0.6 0.8 1.0 1.2

over Temperature at 2700 MHz

4

3

2

1

0

–1

–2

GAIN LAW CONFORMANCE (dB)

–3

–4

1.40 0.2 0.4 0.6 0.8 1.0 1.2

05134-005

180

160

140

120

100

80

60

40

GAIN CONTROL SLOPE (dB/V)

20

0

FREQUENCY (kHz)

Figure 8. Frequency Response of Gain Control Input,

Carr

ier Frequency = 900 MHz

V

GAIN

= 1.0V

10,00010 100 1,000

05134-008

05134-006

05134-007

Rev. A | Page 7 of 24

Page 8

ADL5330

www.BDTIC.com/ADI

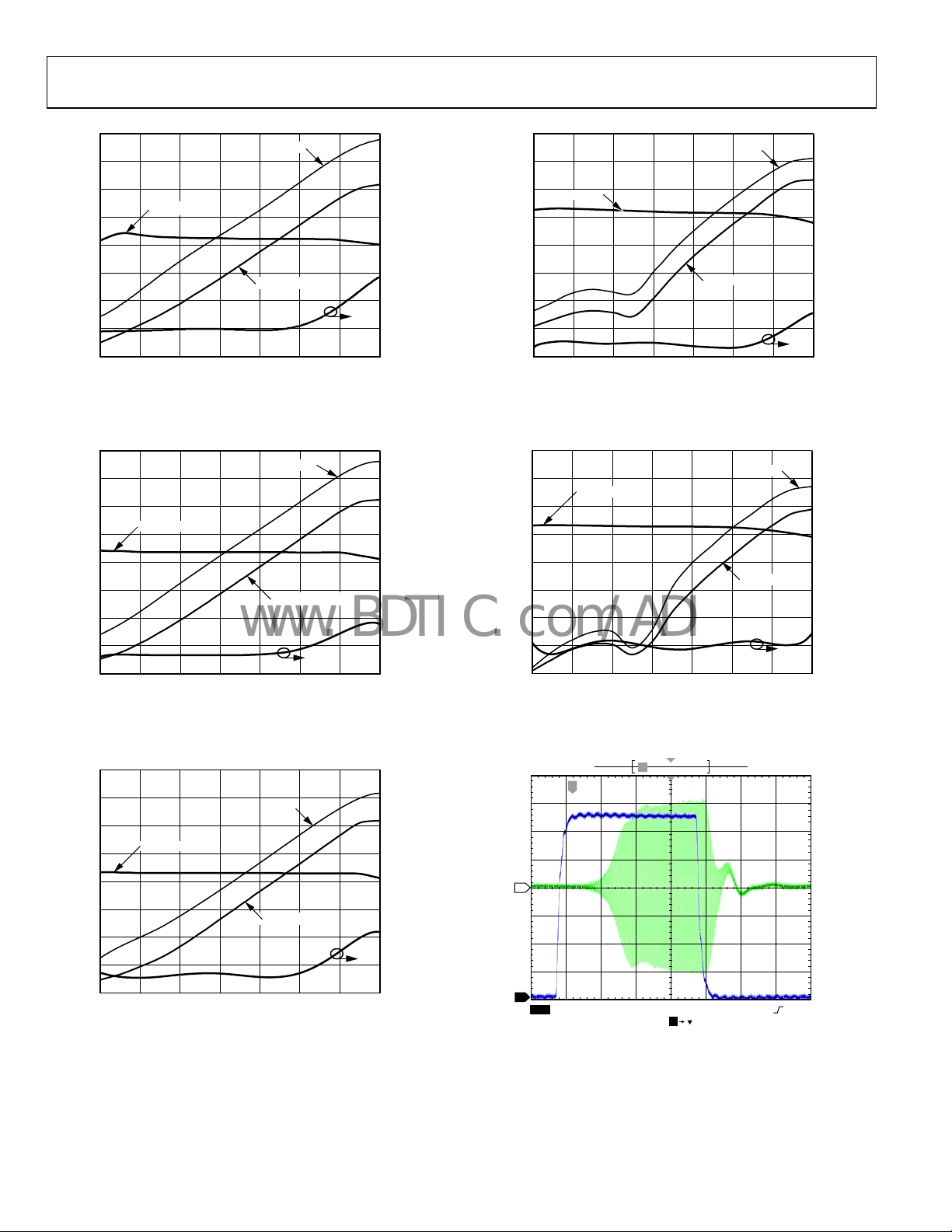

40

30

OIP3

–115

–120

30

20

OIP3

–115

–120

20

10

0

–10

POWER (dBm)

–20

–30

–40

INPUT P1dB

V

GAIN

OUTPUT P1dB

(V)

Figure 9. Input Compression Point, Output Compression Point,

OIP3,

and Noise Floor vs. V

40

30

20

10

0

–10

POWER (dBm)

–20

INPUT P1dB

at 100 MHz

GAIN

OIP3

OUTPUT P1dB

–125

–130

–135

–140

–145

–150

–155

1.40 0.2 0.4 0.6 0.8 1.0 1.2

–115

–120

–125

–130

–135

–140

–145

NOISE FLOOR (dBm/Hz)

05134-009

NOISE FLOOR (dBm/Hz)

10

INPUT P1dB

0

–10

–20

POWER (dBm)

–30

–40

–50

V

GAIN

OUTPUT P1dB

(V)

Figure 12. Input Compression Point, Output Compression Point,

OIP3,

and Noise Floor vs. V

30

20

10

0

–10

–20

POWER (dBm)

–30

INPUT P1dB

at 2200 MHz

GAIN

OIP3

OUTPUT P1dB

–125

–130

–135

–140

–145

NOISE FLOOR (dBm/Hz)

–150

–155

1.40 0.2 0.4 0.6 0.8 1.0 1.2

–120

–125

–130

–135

–140

–145

–150

05134-012

NOISE FLOOR (dBm/Hz)

–30

–40

(V)

V

GAIN

Figure 10. Input Compression Point, Output Compression Point,

GAIN

OIP3

OUTPUT P1dB

(V)

at 450 MHz

40

30

20

10

0

–10

POWER (dBm)

–20

–30

–40

OIP3,

and Noise Floor vs. V

INPUT P1dB

V

GAIN

Figure 11. Input Compression Point, Output Compression Point,

OIP3,

and Noise Floor vs. V

at 900 MHz

GAIN

–150

–155

1.40 0.40.2 0.80.6 1.0 1.2

05134-010

–40

–50

V

(V)

GAIN

–155

–160

1.40 0.2 0.4 0.6 0.8 1.0 1.2

05134-013

Figure 13. Input Compression Point, Output Compression Point,

OIP3,

and Noise Floor vs. V

–115

–120

–125

–130

–135

–140

–145

NOISE FLOOR (dBm/Hz)

–150

–155

1.40 0.40.2 0.6 0.8 1.0 1.2

05134-011

2

1

T

CH1 200mV CH2 100mV Ω M100ns A CH4 2.70V

T

T 382.000ns

at 2700 MHz

GAIN

05134-014

Figure 14. Step Response of Gain Control Input

Rev. A | Page 8 of 24

Page 9

ADL5330

www.BDTIC.com/ADI

30

20

10

OIP3 (–40°C)

0

OIP3, OP1dB (dBm)

–10

–20

–30

–40

–50

OIP3 (+85°C)

OIP3 (+25°C)

OP1dB (–40°C)

OP1dB (+25°C)

V

(V)

GAIN

OP1dB (+85°C)

Figure 18. OP1dB and OIP3 vs. Gain over Temperature at 2200 MHz

1.40 0.2 0.4 0.6 0.8 1.0 1.2

05134-018

OIP3, OP1dB (dBm)

40

30

20

10

0

–10

–20

–30

–40

–50

OIP3 (+85°C)

OIP3 (+25°C)

OP1dB (+25°C)

OIP3 (–40°C)

OP1dB (+85°C)

V

(V)

GAIN

OP1dB (–40°C)

Figure 15. OP1dB and OIP3 vs. Gain over Temperature at 100 MHz

1.40 0.2 0.4 0.6 0.8 1.0 1.2

05134-015

OIP3, OP1dB (dBm)

–10

–20

–30

–40

40

30

20

10

0

OIP3 (–40°C)

OIP3 (+25°C)

OP1dB (–40°C)

OIP3 (+85°C)

OP1dB (+25°C)

OP1dB (+85°C)

V

(V)

GAIN

Figure 16. OP1dB and OIP3 vs. Gain over Temperature at 450 MHz

OIP3, OP1dB (dBm)

–10

–20

–30

–40

40

30

20

10

0

OP1dB (–40°C)

OP1dB (+25°C)

OIP3 (+85°C)

V

(V)

GAIN

OIP3 (–40°C)

OIP3 (+25°C)

OP1dB (+85°C)

Figure 17. OP1dB and OIP3 vs. Gain over Temperature at 900 MHz

20

10

0

–10

–20

OIP3, OP1dB (dBm)

–30

–40

1.40 0.2 0.4 0.6 0.8 1.0 1.2

05134-016

–50

OIP3 (+85°C)

OIP3 (+25°C)

OIP3 (–40°C)

OP1dB (+85°C)

V

(V)

GAIN

OP1dB (+25°C)

OP1dB (–40°C)

1.40 0.2 0.4 0.6 0.8 1.0 1.2

05134-019

Figure 19. OP1dB and OIP3 vs. Gain over Temperature at 2700 MHz

250

200

150

TEMP = +25°C

(mA)

100

SUPPLY

I

50

1.40 0.2 0.4 0.6 0.8 1.0 1.2

05134-017

0

Figure 20. Supply Current vs. V

TEMP = +85°C

TEMP = –40°C

V

GAIN

(V)

and Temperature

GAIN

1.40 0.2 0.4 0.6 0.8 1.0 1.2

05134-020

Rev. A | Page 9 of 24

Page 10

ADL5330

www.BDTIC.com/ADI

70

30

60

50

40

30

PERCENTAGE (%)

20

10

0

18.5 19 19.5 20.520 21 21.5 22 22.5 24.52423.523

OP1dB (dBm)

Figure 21. OP1dB Distribution at 900 MHz at Maximum Gain, V

30

25

20

15

10

PERCENTAGE (%)

5

GAIN

= 1.4 V

05134-021

25

20

15

10

PERCENTAGE (%)

5

0

18.518 19 19.5 20 20.5 2422 2322.5 23.521.521

OIP3 (dBm)

Figure 24. OIP3 Distribution at 2200 MHz at Maximum Gain; V

30

V

= 1.4V

GAIN

20

= 1.2V

V

GAIN

10

= 1.0V

V

GAIN

0

= 0.8V

V

GAIN

–10

GAIN (dB)

–20

–30

–40

V

V

V

GAIN

GAIN

GAIN

= 0.6V

= 0.4V

= 0.2V

GAIN

= 1.4 V

05134-024

0

9.5 10 10.5 11.511 12 12.5 13 13.5 1615 15.514.514

OP1dB (dBm)

Figure 22. OP1dB Distribution at 2200 MHz at Maximum Gain, V

30

25

20

15

10

PERCENTAGE (%)

5

0

28

29 30

28.5

29.5 30.53131.5

32

OIP3 (dBm)

32.5

34 3533

Figure 23. OIP3 Distribution at 900 MHz at Maximum Gain, V

GAIN

GAIN

= 1.4 V

33.533.5 34.5

= 1.4 V

05134-022

05134-023

–50

FREQUENCY (MHz)

Figure 25. Gain vs. Frequency (Differential)

30

V

= 1.4V

GAIN

20

10

–10

GAIN (dB)

–20

–30

–40

–50

= 1.2V

V

GAIN

= 1.0V

V

GAIN

0

= 0.8V

V

GAIN

= 0.6V

V

GAIN

= 0.4V

V

GAIN

V

= 0.2V

GAIN

FREQUENCY (MHz)

Figure 26. Gain vs. Frequency (Using ETC1-1-13 Baluns)

10,00010 100 1,000

05134-025

10,00010 1,000100

05134-026

Rev. A | Page 10 of 24

Page 11

ADL5330

www.BDTIC.com/ADI

90

90

150

210

–10

–15

= 0.2V

60

300

30

330

0180

05134-028

150

210

–10

–15

120

450MHz

V

= 1.2V

GAIN

3GHz

1.9GHz

240

270

Figure 29. Output Impedance (Differential)

0

–5

V

GAIN

120

V

240

GAIN

3GHz

= 1.2V

V

1.9GHz

GAIN

= 0.2V

450MHz

270

60

300

30

330

0180

05134-027

Figure 27. Input Impedance (Differential)

0

–5

–20

S11 (dB)

–25

–30

–35

100 600 1100 1600 2100 2600

FREQUENCY (MHz)

Figure 28. Input Return Loss with ETC1-1-13 Baluns

05134-029

–20

S11 (dB)

–25

–30

–35

100 600 1100 1600 2100

FREQUENCY (MHz)

0

0

6

2

05134-030

Figure 30. Output Return Loss with ETC1-1-13 Baluns

Rev. A | Page 11 of 24

Page 12

ADL5330

www.BDTIC.com/ADI

THEORY OF OPERATION

The ADL5330 is a high performance, voltage-controlled

variable gain amplifier/attenuator for use in applications with

frequencies up to 3 GHz. This device is intended to serve as an

output variable gain amplifier (OVGA) for applications where a

reasonably constant input level is available and the output level

adjusts over a wide range. One aspect of an OVGA is the output

metrics, IP3 and P1dB, decrease with decreasing gain.

The signal path is fully differential throughout the device in

rder to provide the usual benefits of differential signaling,

o

including reduced radiation, reduced parasitic feedthrough, and

reduced susceptibility to common-mode interference with other

circuits. Figure 31 provides a simplified schematic of the

AD

L5330.

TRANSIMPEDANCE

AMPLIFIER

INHI

INLO

Gm STAGE

GAIN

CONTROL

Figure 31. Simplified Schematic

A controlled input impedance of 50 Ω is achieved through a

combination of passive and active (feedback-derived)

termination techniques in an input Gm stage. The input

compression point of the Gm stage is 1 dBm to 3 dBm,

depending on the input frequency.

Note that the inputs of the Gm stage are internally biased to a

vel, and dc blocking capacitors are generally needed on the

dc le

inputs to avoid upsetting operation of the device.

The currents from the Gm stage are then injected into a

ced ladder attenuator at a deliberately diffused location

balan

along the ladder, wherein the location of the centroid of the

injection region is dependent on the applied gain control

voltage. The steering of the current injection into the ladder is

accomplished by proprietary means to achieve linear-in-dB gain

control and low distortion.

OPHI

OPLO

05134-031

Linear-in-dB gain control is accomplished by the application of

oltage in the range of 0 Vdc to 1.4 Vdc to the gain control pin,

a v

with maximum gain occurring at the highest voltage.

The output of the ladder attenuator is passed into a fixed-gain

ransimpedance amplifier (TZA) to provide gain and buffer the

t

ladder terminating impedance from load variations. The TZA

uses feedback to improve linearity and to provide controlled

50 Ω differential output impedance. The quiescent current of

the output amplifier is adaptive; it is slaved to the gain control

voltage to conserve power at times when the gain (and hence,

output power) are low.

The outputs of the ADL5330 require external dc bias to the

p

ositive supply voltage. This bias is typically supplied through

external inductors. The outputs are best taken differentially to

avoid any common-mode noise that is present, but, if necessary,

can be taken single-ended from either output.

If only a single output is used, it is still necessary to provide

ias to the unused output pin, and it is advisable to arrange a

b

reasonably equivalent ac load on the unused output. Differential

output can be taken via a 1:1 balun into a 50 Ω environment. In

virtually all cases, it is necessary to use dc blocking in the

output signal path.

At high gain settings, the noise floor is set by the input stage, in

w

hich case the noise figure (NF) of the device is essentially

independent of the gain setting. Below a certain gain setting,

however, the input stage noise that reaches the output of the

attenuator falls below the input-equivalent noise of the output

stage. In such a case, the output noise is dominated by the

output stage itself; therefore, the overall NF of the device gets

worse on a dB-per-dB basis, because the gain is reduced below

the critical value.

th

is behavior.

Figure 9 through Figure 13 provide details of

Rev. A | Page 12 of 24

Page 13

ADL5330

www.BDTIC.com/ADI

APPLICATIONS

BASIC CONNECTIONS

Figure 32 shows the basic connections for operating the

ADL5330. There are two positive supplies, VPS1 and VPS2,

which must be connected to the same potential. Both COM1

and COM2 (common pins) should be connected to a low

impedance ground plane.

A power supply voltage between 4.75 V and 5.25 V should be

pplied to VPS1 and VPS2. Decoupling capacitors with 100 pF

a

and 0.1 μF power supplies should be connected close to each

power supply pin. The VPS2 pins (Pin 18 through Pin 22) can

share a pair of decoupling capacitors because of their proximity

to each other.

The outputs of the ADL5330, OPHI and OPLO, are open

co

llectors that need to be pulled up to the positive supply with

120 nH RF chokes. The ac-coupling capacitors and the RF

chokes are the principle limitations for operation at low

frequencies. For example, to operate down to 1 MHz, 0.1 μF accoupling capacitors and 1.5 μH RF chokes should be used. Note

that in some circumstances, the use of substantially larger

inductor values results in oscillations.

Since the differential outputs are biased to the positive supply,

ac-co

upling capacitors, preferably 100 pF, are needed between

the ADL5330 outputs and the next stage in the system.

Similarly, the INHI and INLO input pins are at bias voltages of

about 3.3 V above ground.

The nominal input and output impedance looking into each

ual RF input/output pin is 25 Ω. Consequently, the

individ

differential impedance is 50 Ω.

To enable the ADL5330, the ENBL pin must be pulled high.

aking ENBL low puts the ADL5330 in sleep mode, reducing

T

current consumption to 250 μA at ambient. The voltage on

ENBL must be greater than 1.7 V to enable the device. When

enabled, the device draws 100 mA at low gain to 215 mA at

maximum gain.

VPOS

C1

0.1μF

C2

100pF

GAIN

VPOS

0.1μF

RF INPUT RF OUTPUT

VPOS

C12

0.1μF

C12

100pF

C13

100pF

C14

100pF

C16

100pF

C11

VPS1

COM1

INHI

INLO

COM1

VPS1

C10

1nF

GAIN

VREF

VPS2

ENBL

ADL5330

OPBS

IPBS

C9

1nF

VPS2

COM1

VPS2

GNLO

VPS2

VPS2

COM2

OPHI

OPLO

COM2

VPS2

COM2

VPOS

L1

120nH

C7

100pF

C8

0.1μF

VPOS

C4

100pF

L2

120nH

C5

100pF

C6

100pF

C3

0.1μF

Figure 32. Basic Connections

05334-032

Rev. A | Page 13 of 24

Page 14

ADL5330

www.BDTIC.com/ADI

RF INPUT/OUTPUT INTERFACE

The ADL5330 is primarily designed for differential signals;

however, there are several configurations that can be

implemented to interface the ADL5330 to single-ended

applications.

ferential-to-single-ended interfaces. All three configurations

dif

use ac-coupling capacitors at the input/output and RF chokes at

the output.

RFIN

Figure 33 to Figure 35 show three options for

+5V

120nH

120nH

ADL5330

INHI

INLO

RF VGA

OPHI

OPLO

100pF

100pF

ETC1-1-13ETC1-1-13

+5V

100pF

100pF

Figure 33. Differential Operation with Balun Transformers

RFOUT

05134-033

band baluns can be used for applications requiring lower

insertion loss over smaller bandwidths.

The device can be driven single-ended with similar

rformance, as shown in Figure 34. The single-ended input

pe

terface can be implemented by driving one of the input

in

terminals and terminating the unused input to ground. To

achieve the optimal performance, the output must remain

balanced. In the case of

e output.

th

Figure 34, a transformer balun is used at

As an alternative to transformer baluns, lumped-element baluns

co

mprised of passive L and C components can be designed at

specific frequencies. Figure 35 illustrates differential balance at

th

e input and output of the ADL5330 using discrete lumpedelement baluns. The lumped-element baluns present 180° of

phase difference while also providing impedance

transformation from source to load, and vice versa.

ecommended passive values for various center frequencies

r

with single-ended impedances of 50 Ω. Agilent’s free

AppCAD

TM

program allows for simple calculation of passive

Tabl e 4 lists

components for lumped-element baluns.

120nH

120nH

100pF

100pF

ADL5330

RF VGA

INHI

INLO

OPHI

OPLO

100pF

100pF

ETC1-1-13

RFOUTRFIN

05134-041

Figure 34. Single-Ended Drive with Balanced Output

Figure 33 illustrates differential balance at the input and output

using a transformer balun. Input and output baluns are recommended for optimal performance. Much of the characterization

for the ADL5330 was completed using 1:1 baluns at the input

and output for single-ended 50 Ω match. Operation using

M/A-COM ETC1-1-13 transmission line transformer baluns

is recommended for a broadband interface; however, narrow-

L

i

C

RFIN

i

C

i

L

i

100pF

C

i

C

ip

100pFC

i

INHI

ADL5330

INLO

Figure 35. Differential Operation with Discrete LC Baluns

RF VGA

The lumped-element baluns offer ±0.5 dB flatness across

z for 900 MHz and 2200 MHz. At 2.7 GHz, the

50 MH

frequency band is limited by stray capacitances that dominate

the passive components in the lumped-element balun at these

high frequencies. Thus, PCB parasitics must be considered

during lumped-element balun design and board layout.

Table 4. Recommended Passive Values for Lumped-Element

Ba

lun, 50 Ω Impedance Match

Center

Frequency

C

Input Output

L

i

i

C

C

ip

o

Lo C

100 MHz 27 pF 82 nH 1 pF 33 pF 72 nH 3.3 pF

900 MHz 3.3 pF 9 nH 3.9 pF 8.7 nH 0.5 pF

2.2 GHz 1.5 pF 3.3 nH 16 nH 1.5 pF 3.6 nH

2.7 GHz 1.5 pF 2.4 nH 1.3 pF 2.7 nH 33 nH

+5V

120nH

120nH

L

o

C

o

C

o

o

RFOUT

C

o

L

o

05134-035

OPHI

OPLO

100pF

C

op

100pF C

op

27 nH

Rev. A | Page 14 of 24

Page 15

ADL5330

www.BDTIC.com/ADI

GAIN CONTROL INPUT

When the VGA is enabled, the voltage applied to the GAIN pin

sets the gain. The input impedance of the GAIN pin is 1 MΩ.

The gain control voltage range is between 0 V and +1.4 V, which

co

rresponds to a typical gain range between −38 dB and

+22 dB. The useful lower limit of the gain control voltage

increases at high frequencies to about 0.5 V and 0.6 V for

2.2 GHz and 2.7 GHz, respectively. The supply current to the

ADL5330 can vary from approximately 100 mA at low gain

control voltages to 215 mA at 1.4 V.

The 1 dB input compression point remains constant at 3 dBm

ough the majority of the gain control range, as shown in

thr

Figure 9 through Figure 13. The output compression point

i

ncreases dB for dB with increasing gain setting. The noise floor

is constant up to 1 V where it begins to rise.

The bandwidth on the gain control pin is approximately 3 MHz.

Figure 14 shows the response time of a pulse on the GAIN pin.

The detector’s error amplifier uses C

, a ground-referenced

FLT

capacitor pin, to integrate the error signal (in the form of a

current). A capacitor must be connected to C

to set the loop

FLT

bandwidth and to ensure loop stability.

+5V +5V

RFIN

DAC

VPOS COMM

INHI

ADL5330

INLO

LOG AMP OR

TRUPWR

DETECTOR

VSET RFIN

OPHI

OPLO

GAIN

VOUT

CLPF

DIRECTIONAL

COUPLER

ATTENUATOR

AUTOMATIC GAIN CONTROL

Although the ADL5330 provides accurate gain control, precise

regulation of output power can be achieved with an automatic

gain control (AGC) loop. Figure 36 shows the ADL5330 in an

A

GC loop. The addition of the log amp (AD8318/AD8315) or a

TruPwr™ detector (AD8362) allows the AGC to have improved

temperature stability over a wide output power control range.

To operate the ADL5330 in an AGC loop, a sample of the

o

utput RF must be fed back to the detector (typically using a

directional coupler and additional attenuation). A setpoint

voltage is applied to the VSET input of the detector while

VOUT is connected to the GAIN pin of the ADL5330. Based on

the detector’s defined linear-in-dB relationship between VOUT

and the RF input signal, the detector adjusts the voltage on the

GAIN pin (the detector’s VOUT pin is an error amplifier

output) until the level at the RF input corresponds to the

applied setpoint voltage. The GAIN setting settles to a value

that results in the correct balance between the input signal level

at the detector and the setpoint voltage.

Figure 36. ADL5330 in AGC Loop

The basic connections for operating the ADL5330 in an AGC

loop with the AD8318 are shown in Figure 37. The AD8318 is a

1 MH

z to 8 GHz precision demodulating logarithmic amplifier.

It offers a large detection range of 60 dB with ±0.5 dB temperature stability. This configuration is similar to Figure 36.

The gain of the ADL5330 is controlled by the output pin of the

AD8318. This vol

tage, VOUT, has a range of 0 V to near VPOS.

To avoid overdrive recovery issues, the AD8318 output voltage

can be scaled down using a resistive divider to interface with the

0 V to 1.4 V gain control range of ADL5330.

A coupler/attenuation of 23 dB is used to match the desired

aximum output power from the VGA to the top end of the

m

linear operating range of the AD8318 (at approximately −5 dBm

at 900 MHz).

05134-036

Rev. A | Page 15 of 24

Page 16

ADL5330

www.BDTIC.com/ADI

+5V

RF INPUT

SIGNAL

DAC

220pF

100pF

100pF

SETPOINT

VOLTAGE

VPOS COMM

INHI

ADL5330

INLO

GAIN

412Ω

1kΩ

VOUT VPOS

VSET INHI

AD8318

LOG AMP

COMM

OPHI

OPLO

Figure 37. ADL5330 Operating in an Automatic Gain Control Loop in Combination with the AD8318

Figure 38 shows the transfer function of the output power vs.

the VSET voltage over temperature for a 900 MHz sine wave

with an input power of −1.5 dBm. Note that the power control

of the AD8318 has a negative sense. Decreasing VSET, which

corresponds to demanding a higher signal from the ADL5330,

tends to increase GAIN.

The AGC loop is capable of controlling signals just under the

f

ull 60 dB gain control range of the ADL5330. The performance

over temperature is most accurate over the highest power range,

where it is generally most critical. Across the top 40 dB range of

output power, the linear conformance error is well within

±0.5 dB over temperature.

30

4

+5V

120nH

INLOCLPF

+5V

ATTENUATOR

RF OUTPUT

SIGNAL

05134-037

1nF

1nF

120nH

100pF

100pF

DIRECTIONAL

COUPLER

In order for the AGC loop to remain in equilibrium, the

AD8318 m

ust track the envelope of the ADL5330 output signal

and provide the necessary voltage levels to the ADL5330’s gain

control input. Figure 39 shows an oscilloscope screenshot of the

AG

C loop depicted in Figure 37. A 100 MHz sine wave with

50%

AM modulation is applied to the ADL5330. The output

signal from the ADL5330 is a constant envelope sine wave with

amplitude corresponding to a setpoint voltage at the AD8318 of

1.5 V. Also shown is the gain control response of the AD8318 to

the changing input envelope.

AM MODULATED INPUT

1

T

T

20

10

0

–10

–20

OUTPUT POWER (dBm)

–30

–40

–50

SETPOINT VOLTAGE (V)

3

2

1

0

–1

ERROR (dB)

–2

–3

–4

2.20.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

05134-038

Figure 38. ADL5330 Output Power vs. AD8318 Setpoint Voltage,

= −1.5 dBm

P

IN

The broadband noise added by the logarithmic amplifier is

negligible.

Rev. A | Page 16 of 24

AD8318 OUTPUT

3

ADL5330 OUTPUT

CH1 250mV Ω

CH3 250mV Ω

M2.00ms A CH4 1.80V

T 0.00000s

Figure 39. Oscilloscope Screenshot Showing an AM Modulated Input Signal

05134-039

Page 17

ADL5330

www.BDTIC.com/ADI

Figure 40 shows the response of the AGC RF output to a pulse

on VSET. As VSET decreases to 1 V, the AGC loop responds

with an RF burst. Response time and the amount of signal

integration are controlled by the capacitance at the AD8318 C

FLT

pin—a function analogous to the feedback capacitor around an

integrating amplifier. An increase in the capacitance results in

slower response time.

T

AD8318 WITH PULSED V

1

ADL5330 OUTPUT

2

CH1 2.00V CH2 50.0mVΩ M10.0μs A CH1 2.60V

SET

T 20.2000μs

T

05134-040

Figure 40. Oscilloscope Screenshot Showing the

esponse Time of the AGC Loop

R

More information on the use of AD8318 in an AGC application

can be found in the AD8318 data sheet.

INTERFACING TO AN IQ MODULATOR

The basic connections for interfacing the AD8349 with the

ADL5330 are shown in Figure 42. The AD8349 is an RF

uadrature modulator with an output frequency range of

q

700 MHz to 2.7 GHz. It offers excellent phase accuracy and

amplitude balance, enabling high performance direct RF

modulation for communication systems.

The output of the AD8349 is designed to drive 50 Ω loads and

easil

y interfaces with the ADL5330. The input to the ADL5330

can be driven single-ended, as shown in Figure 42. Similar conf

igurations are possible with the AD8345 (250 MHz to 1 GHz)

and AD8346 (800 MHz to 2.5 GHz) quadrature modulators.

Figure 41 shows how output power, EVM, ACPR, and noise

v

ary with the gain control voltage. V

is varied from 0 V to

GAIN

1.4 V. Figure 41 shows that the modulation generated by the

AD8349

is a 1 GHz 64 QAM waveform with a 1 MHz symbol

rate. The ACPR values are measured in 1 MHz bandwidths at

1.1 MHz and 2.2 MHz carrier offsets. Noise floor is measured at

a 20 MHz carrier offset.

20 4.5

0 4.0

–20 3.5

–40 3.0

–60 2.5

–80 2.0

–100 1.5

OUTPUT POWER (dBm)

–120 1.0

ACPR (dBm) (1MHz BANDWIDTH)

NOISE FLOOR

–140 0.5

NOISE (dBm/Hz) (20MHz CARRIER OFFSET)

–160 0

OUTPUT POWER

ACPR 1.1MHz OFFSET

ACPR 2.2MHz OFFSET

V

(V)

GAIN

EVM

1.40 0.2 0.4 0.80.6 1.0 1.2

Figure 41. AD8349 and ADL5330 Output Power, ACPR, EVM, and Noise vs.

for a 1 GHz 64 QAM Waveform with 1 MHz Symbol Rate

V

GAIN

The output of the AD8349 driving the ADL5330 should be

limited to the range that provides the optimal EVM and ACPR

performance. The power range is found by sweeping the output

power of the AD8349 to find the best compromise between

EVM and ACPR of the system. In

p

ower is set to −15 dBm.

Figure 41, the AD8349 output

+5V

EVM (%)

05134-042

+5V

COMMVPOS

AD8349

IQ MOD

200Ω

200Ω

V

OUT

DIFFERENTIAL I/Q

BASEBAND INPUTS

DAC

DAC

IBBP

IBBN

QBBP

QBBN

100pF

LO

100pF

ETC1-1-13

Figure 42. AD8349 Quadrature M

Rev. A | Page 17 of 24

+5V

COMMVPOS

100pF

100pF

ADL5330

INHI

RF VGA

INLO

GAIN CONTROL

OPHI

OPLO

odulator and ADL5330 Interface

120nH

120nH

100pF

100pF

ETC1-1-13

RF OUTPUT

05134-034

Page 18

ADL5330

www.BDTIC.com/ADI

WCDMA TRANSMIT APPLICATION

Figure 43 shows a plot of the output spectrum of the ADL5330

transmitting a single-carrier WCDMA signal (Test Model 1-64

at 2140 MHz). The carrier power output is approximately

−9.6 dBm. The gain control voltage is equal to 1.4 V giving a

gain of approximately 14.4 dB. At this power level, an adjacent

channel power ratio of −65.61 dBc is achieved. The alternate

channel power ratio of −71.37 dBc is dominated by the noise

floor of the ADL5330.

MARKER 1 [T1]

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

–120

REF LVL

–20dBm

0.4 dB OFFSET

1 AVG

CL2

CL2

–29.78dBm

2.13996994GHz

CL1

CL1

Figure 43. Single-Carrier WCDMA Spectrum at 2140 MHz;

= 1.4 V, PIN = −23 dBm

V

GAIN

Figure 44 shows how ACPR and noise vary with different input

power levels (gain control voltage is held at 1.4 V). At high

power levels, both adjacent and alternate channel power ratios

sharply increase. As output power drops, adjacent and alternate

channel power ratios both reach minima before the measurement becomes dominated by the noise floor of the ADL5330. At

this point, adjacent and alternate channel power ratios become

approximately equal.

RBW

30kHz

RF ATT

VBW

300kHz

SWT

100ms

1 [T1] –29.78 dBm

CH PWR –9.56 dBm

ACP Up –66.30 dB

ACP Low –65.61 dB

ALT1 Up –71.37 dB

ALT1 Low –72.79 dB

C0

C0

CU1

CU1

SPAN 24.6848MHzCENTER 2.14GHz 2.46848MHz/

0dB

UNIT

dBm

2.13996994 GHz

CU2

CU2

A

1RM

EXT

05134-043

–20

–30

–40

–50

–60

–70

POWER RATIO (dBc)

–80

ADJACENT/ALTERNATE CHANNEL

–90

–100

ACPR +5MHZ OFFSET

NOISE –50MHz OFFSET

OUTPUT POWER (dBm)

ACPR +10MHZ

OFFSET

–50

–55

–60

–65

–70

–75

–80

–85

–90

10–40 –35 –30 –25 –20 –15 –10 –5 0 5

Figure 44. ACPR and Noise vs. Output Power; Single-Carrier

Input (Test Model 1-64 at 2140 MHz), V

WCDMA

= 1.4 V (Fixed)

GAIN

Figure 45 shows how output power, ACPR, and noise vary with

the gain control voltage. V

is varied from 0 V to 1.4 V and

GAIN

input power is held constant at −19 dBm.

10

0

–10

–20

–30

–40

OUTPUT POWER (dBm)

–50

–60

–70

OUTPUT POWER

ACPR 5MHz

ACPR 10MHz

NOISE –50MHz OFFSET

(V)

V

GAIN

Figure 45. Output Power, ACPR, and Noise vs. V

Single-Carrier WCDMA ( Test Model 1-64 at 2140 MHz) Input at −19 dBm

GAIN

–20

–30

–40

–50

–60

–70

ACPR (dBc)

–80

–90

–100

1.40.4 0.5 0.6 0.7 0.8 0.9 1.0 1.1 1.2 1.3

;

OFFSET (1MHz BW)

NOISE – dBm @ 50MHz CARRIER

05134-044

NOISE @ 50MHz OFFSET (1MHz BW)

05134-045

As the output power drops, the noise floor, measured in dBm/

H

z at 50 MHz carrier offset, initially falls and then levels off.

Rev. A | Page 18 of 24

Page 19

ADL5330

www.BDTIC.com/ADI

CDMA2000 TRANSMIT APPLICATION

To test the compliance to the CDMA2000 base station standard,

an 880 MHz, three-carrier CDMA2000 test model signal

(forward pilot, sync, paging, and six traffic, as per 3GPP2

C.S0010-B, Table 6.5.2.1) was applied to the ADL5330. A cavitytuned filter with a 4.6 MHz pass band was used to reduce noise

from the signal source being applied to the device.

Figure 46 shows the spectrum of the output signal under

ominal conditions. Total P

n

equal to 0.46 dBm and V

channel power ratio is measured in a 30 kHz bandwidth at

750 kHz and 1.98 MHz carrier offset, respectively.

MARKER 1 [T1]

REF LVL

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

–10dBm

0.4 dB OFFSET

1 AVG

CL3

CL3

880.00000000MHz

CL2

CL2

Figure 46. 880 MHz Output Spectrum, Three-Carrier CDMA2000 Test Model

a

t −23 dBm Total Input Power, V

1.98 MHz Carrier Offset, Input Signal Filtered Using a Cavity Tuned Filter

In testing, by holding the gain control voltage steady at 1.4 V,

input power was swept. Figure 47 shows ACPR and noise floor

otal output power. Noise floor is measured at 1 MHz

vs. t

bandwidth at 4 MHz carrier offset.

–30

–40

–50

–60

–70

–80

–90

ACPR – dBc (30kHz RBW)

–100

–110

–120

Figure 47. ACPR vs. Total Output Power, 880 MHz Three-Carrier CDMA2000

Te

st Mod el; V

ACPR 750kHz OFFSET

ACPR 1.98MHz OFFSET

NOISE 4MHz OFFSET

TOTAL OUTPUT POWER (dBm)

= 1.4 V (Fixed), ACPR Measured in 30 kHz Bandwidth at

GAIN

750 kHz and 1.98 MHz Carrier Offset

of the three-carrier signal is

OUT

= 1.4 V. Adjacent and alternate

GAIN

–18.55dBm

CL1

CL1

RBW 30kHz

VBW 300kHz

SWT 200ms

1

C0

C0

CU1

CU1

= 1.4 V, ACPR Measured at 750 kHz and

GAIN

RF ATT 10dB

MIXER –10dBm

UNIT dBm

1 [T1] –18.55dBm

CH PWR 0.46dBm

ACP Up –65.13dB

ACP Low –64.40dB

ALT1 Up –89.05dB

ALT1 Low –83.68dB

ALT2 Up –80.72dB

ALT2 Low –81.24dB

CU2

CU2

CU3

SPAN 15MHzCENTER 880MHz 1.5MHz/

(Pass Band = 4.6 MHz)

CU3

880MHz

A

1RM

EXT

05134-046

–0

–10

–20

–30

–40

–50

–60

–70

–80

NOISE – dBm @ 4MHz CARRIER OFFSET

–90

15–30 –25 –20 –15 –10 –5 0 5 10

(1MHz RBW)

05134-047

The results show that up to a total output power of +8 dBm,

ACPR remains in compliance with the standard (<−45 dBc @

750 kHz and <−60 dBc @ 1.98 MHz). At low output power

levels, ACPR at 1.98 MHz carrier offset degrades as the noise

floor of the ADL5330 becomes the dominant contributor to

measured ACPR. Measured noise at 4 MHz carrier offset begins

to increase sharply above 0 dBm output power. This increase is

not due to noise but results from increased carrier-induced

distortion. As output power drops below 0 dBm total, the noise

floor drops towards −85 dBm.

With a fixed input power of −23 dBm, the output power was

a

gain swept by exercising the gain control input. V

GAIN

was

swept from 0 V to 1.4 V. The resulting total output power,

ACPR, and noise floor are shown in

10

0

–10

–20

–30

ACPR 1.98MHz OFFSET

–40

TOTAL OUTPUT POWER (dBm)

–50

–60

Figure 48. Total Output Power and ACPR vs. V

CDMA2000 Test Model at −23 dBm Total Input Power; ACPR Measured in

30 kHz Bandwidth at 750 kHz and 1.98 MHz Carrier Offset

Above V

= 0.4 V, the ACPR is still in compliance with the

GAIN

NOISE 4MHz OFFSET

V

GAIN

Figure 48.

OUTPUT POWER

ACPR 750kHz OFFSET

(V)

GAIN

–30

–40

–50

–60

–70

ACPR (dBc)

–80

–90

–100

1.40 0.2 0.4 0.6 0.8 1.0 1.2

, 880 MHz Three-Carrier

NOISE – 4MHz CARRIER OFFSET – (1MHz RBW)

standard. As the gain control input drops below 1.0 V, the noise

floor drops below −90 dBm.

SOLDERING INFORMATION

On the underside of the chip scale package, there is an exposed

compressed paddle. This paddle is internally connected to the

chip’s ground. Solder the paddle to the low impedance ground

plane on the printed circuit board to ensure specified electrical

performance and to provide thermal relief. It is also

recommended that the ground planes on all layers under the

paddle be stitched together with vias to reduce thermal

impedance.

05134-048

Rev. A | Page 19 of 24

Page 20

ADL5330

www.BDTIC.com/ADI

EVALUATION BOARD

Figure 49 shows the schematic of the ADL5330 evaluation

board. The silkscreen and layout of the component and circuit

sides are shown in Figure 50 through Figure 53. The board is

p

owered by a single-supply in the 4.75 V to 5.25 V range. The

power supply is decoupled by 100 pF and 0.1 μF capacitors at

each power supply pin. Additional decoupling, in the form of a

series resistor or inductor at the supply pins, can also be added.

Tabl e 5 details the various configuration options of the

aluation board.

ev

The output pins of the ADL5330 require supply biasing with

120 nH RF ch

differential impedances and must be ac-coupled. These pins are

converted to single-ended with a pair of baluns (M/A-COM

part number ETC1-1-13).

Instead of using balun transformers, lumped-element baluns

mprising passive L and C components can be designed.

co

Alternate input and output RF paths with component pads are

okes. Both the input and output pins have 50 Ω

available on the circuit side of the board. Components M1

through M9 are used for the input interface, and M10 through

M18 are used for the output interface. DC blocking capacitors

of 100 pF must be installed in C15 and C16 for the input and

C17 and C18 for the output. The C5, C6, C11, and C12

capacitors must be removed. An alternate set of SMA

connectors, INPUT2 and OUT2, are used for this

configuration.

The ADL5330 can be driven single-ended; use the RF input

ath on the circuit side of the board. A set of 100 pF dc blocking

p

capacitors must be installed in C15 and C16. C5 and C6 must

be removed. Use the INPUT2 SMA to drive one of the

differential input pins. The unused pin should be terminated to

ground, as shown in

The ADL5330 is enabled by applying a logic high voltage to the

ENBL pin

O position. Remove the jumper for disable. This pulls the ENBL

pin to ground through the 10 kΩ resistor.

by placing a jumper across the SW1 header in the

Figure 34.

Rev. A | Page 20 of 24

Page 21

ADL5330

www.BDTIC.com/ADI

VPOS

VPOS

VPOS

OPEN

OPEN

OPEN

OPLO

INLO

M13

M11

COM2

COM1

OUT2

OPEN

OPEN

M10

OPEN

VPS2

VPS1

C10

M17

M15

C18

100pF

R6

0Ω

COM2

GNLO

COM1

OPBS

IPBS

VREF

OPEN

OPEN

OPEN

M18

M16

OPEN

OPEN

C9

0.1μF

R15

VPOS

OPEN

IPBS

R9

0Ω

R11

1nF

1nF

R10

OUT

M14

M12

T2

C11

C14

0.1μF

C2

0.1μF

SW1

R1

SMA

C13

100pF

0Ω

R12

R2

0Ω

R13

10kΩ

0Ω

R3

0Ω

C1

L1

100pF

100pF

120nH

L2

VPS2

VPS2

VPS2

VPS2

ENBL

GAIN

C12

120nH

VPS2

VPS1

100pF

COM2

COM1

C17

OPHI

ADL5330

INHI

GAIN

C7

R5

0Ω

100pF

C8

0.1μF

VPOS

C5

100pFC6100pF

T1

INPUT

C15

M4

M1

Figure 49. Evaluation Board Schematic

OPEN

OPEN

OPEN

R4

0Ω

VPOS

M5

M3

C4

C3

M6

OPEN

OPEN

OPEN

INPUT2

100pF

0.1μF

C16

M9

M7

OPEN

OPEN

OPEN

M8

M2

R8

0Ω

VREF

OPEN

OPEN

R14

OPEN

R7

0Ω

IPBS

05134-049

Rev. A | Page 21 of 24

Page 22

ADL5330

www.BDTIC.com/ADI

Table 5. Evaluation Board Configuration Options

Components Function Default Conditions

C1 to C4, C7 to C10, C13,

C14, R2, R4, R5, R6, R12

T1, C5, C6

T2, C11, C12, L1, L2

SW1, R1, R13

C15 to C18, M1 to M18

Power Supply Decoupling. The nominal supply decoupling consists of

100 pF and 0.1 μF capacitors at each power supply pin (the VPS2 pins, Pin 18

to Pin 22, share a pair of decoupling capacitors because of their proximity). A

series inductor or small resistor can be placed between the capacitors for

additional decoupling.

Input Interface. The 1:1 balun transformer T1 converts a 50 Ω single-ended

input to the 50

Output Interface. The 1:1 balun transformer T2 converts the 50 Ω differential

output to 50

L4 provide dc biases for the output.

Enable Interface. The ADL5330 is enabled by applying a logic high voltage

e ENBL pin by placing a jumper across SW1 to the O position. Remove

to th

the jumper for disable. To exercise the enable function by applying an

external high or low voltage, use the pin labeled O on the SW1 header.

Alternate Input/Output Interface. The circuit side of the evaluation board

offers an alternate RF

can be built using L and C components instead of using the balun

transformer (see the Applications section). The components, M1 through

M9, are used for

To use the alternate RF paths, disconnect the dc blocking capacitors

(Capacitor C5 and Capacitor C6 for the input and Capacitor C11 and

Capacitor C12 for the output). Place 100 pF dc blocking capacitors on

C15, C16, C17, and C18. Use the alternate set of SMA connectors,

INPUT2 and OUT2.

Ω differential input. C5 and C6 are dc blocks.

Ω single-ended output. C11 and C2 are dc blocks. L3 and

input and output interface. A lumped-element balun

the input, and M10 through M18 are used for the output.

C1, C4, C7, C10, C13 = 100 pF

(size 0603)

C2, C3, C8, C9, C14 = 0.1 μF

(size 0603)

R2, R4, R5, R6, R12 = 0 Ω

(size 0402)

T1 = ETC1-1-13 (M/A-COM)

C5, C6 = 100 pF (size 0603)

T2 = ETC1-1-13 (M/A-COM)

C11, C12 = 100 pF (size 0603)

L1, L2 = 120 nH (size 0805)

SW1 = installed

R1 = 0 Ω (size 0402)

R13 = 10 kΩ (size 0402)

M1 to M18 = not installed

(size 0603)

C15 to C18 = not installed

(size 0603)

Rev. A | Page 22 of 24

Page 23

ADL5330

www.BDTIC.com/ADI

05134-053

Figure 50. Component Side Silkscreen

05134-051

Figure 52. Component Side Layout

05134-050

Figure 51. Circuit Side Silkscreen

Rev. A | Page 23 of 24

Figure 53. Circuit Side Layout

05134-052

Page 24

ADL5330

www.BDTIC.com/ADI

OUTLINE DIMENSIONS

0.60 MAX

19

18

EXPOSED

(BOTTOMVIEW)

13

12

PA D

24

6

7

1

2.50 REF

PIN 1

INDICATOR

*

2.45

2.30 SQ

2.15

0.23 MIN

PIN 1

INDICATOR

1.00

0.85

0.80

SEATING

PLANE

12° MAX

4.00

BSC SQ

TOP

VIEW

0.80 MAX

0.65 TYP

*

COMPLIANT TO JEDEC STANDARDS MO-220-VGGD-2

EXCEPT FOR EXPOSED PAD DIMENSION

0.30

0.23

0.18

3.75

BSC SQ

0.20 REF

0.60 MAX

0.05 MAX

0.02 NOM

COPLANARITY

BSC

0.08

0.50

0.50

0.40

0.30

Figure 54. 24-Lead Lead Frame Chip Scale Package [LFCSP_VQ]

mm × 4 mm Body, Very Thin Quad

4

(CP-24-2)

Dimensions shown in millimeters

ORDERING GUIDE

Package

Model Temperature Range Package Description

ADL5330ACPZ-WP

1, 2

−40°C to +85°C 24-Lead Lead Frame Chip Scale Package (LFCSP_VQ) CP-24-2 64

Option

ADL5330ACPZ-REEL71−40°C to +85°C 24-Lead Lead Frame Chip Scale Package (LFCSP_VQ) CP-24-2 1,500

ADL5330ACPZ-R2

1

−40°C to +85°C 24-Lead Lead Frame Chip Scale Package (LFCSP_VQ) CP-24-2 250

ADL5330-EVAL Evaluation Board 1

1

Z = Pb-free part.

2

WP = waffle pack.

Ordering

Quantity

© 2005 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D05134–0–6/05(A)

Rev. A | Page 24 of 24

Loading...

Loading...