Page 1

Precision Wide Range (3 nA to 3 mA)

FEATURES

Accurately mirrors input current (1:1 ratio) over 6 decades

Linearity 1% from 3 nA to 3 mA

Stable mirror input voltage

Voltage held 1 V below supply using internal reference

or can be set externally

Adjustable input current limit

2.7 V to 8 V single-supply operation

Miniature 8-lead LFCSP (2 mm × 3 mm)

APPLICATIONS

Optical power monitoring from a single photodiode

General voltage biasing with precision current monitoring

Voltage-to-current conversion

High-Side Current Mirror

ADL5315

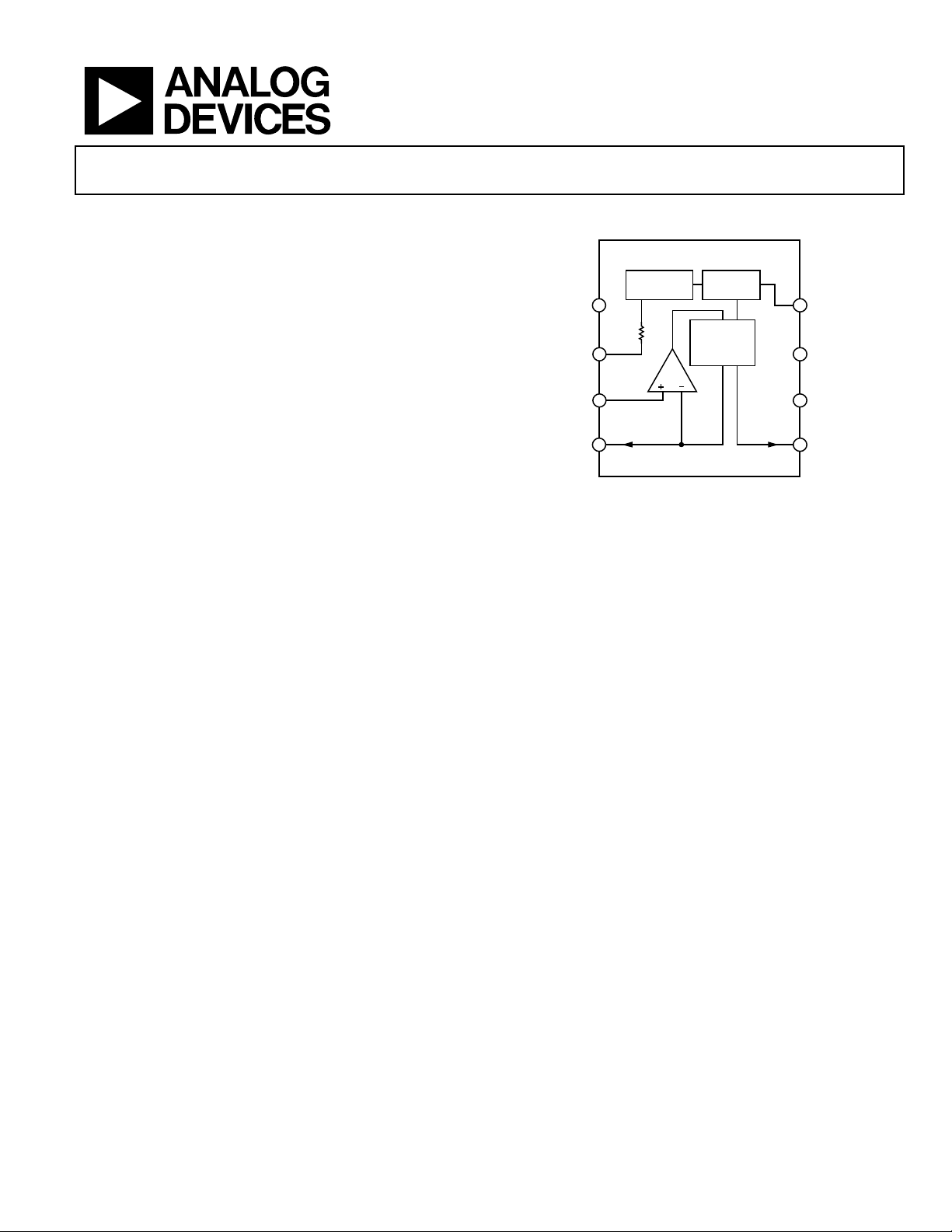

FUNCTIONAL BLOCK DIAGRAM

ADL5315

VOLTAGE

REFERENCE

4

COMM

20kΩ

3

SREF

VSET NC

2 7

INPT

1

I

PD

CURRENT

LIMITING

CURRENT

MIRROR

1:1

Figure 1.

RLIM

VPOS

IOUT

I

PD

5

6

8

05694-001

GENERAL DESCRIPTION

The ADL5315 is a wide input current range, precision high-side

current mirror featuring a stable and user-adjustable input

voltage. It is optimized for use with PIN photodiodes, but its

flexibility and wide operating range make it suitable for a broad

array of additional applications. Over the 3 nA to 3 mA range,

the current sourced from the INPT pin is accurately mirrored

with a 1:1 ratio and sourced from the IOUT output pin. In a

typical photodiode application, the output drives a currentinput logarithmic amplifier to produce a linear-in-dB output

representing the optical power incident upon the photodiode.

For linear voltage output, a single resistor to ground is all that is

required. The photodiode anode can be connected to a high

speed transimpedance amplifier for the extraction of the data

stream. The voltage at the INPT pin is temperature stable with

respect to the voltage at the VSET input pin, which it tracks. A

temperature stable reference voltage is provided at the SREF

pin, which, when tied to VSET, fixes the voltage at INPT 1.0 V

below VPOS. VSET can also be driven from an external source.

The VSET input has very low input current and can be driven

as low as the bottom rail, facilitating nonloading voltage-tocurrent conversion as well as minimizing dark current in

photodiode applications.

The ADL5315 also features adjustable input current limiting

using an external resistor from RLIM to VPOS. The maximum

current sourced by INPT (and IOUT) can be set between 1 mA

and 16 mA, beyond which the voltage at INPT falls rapidly

from its setpoint. Connecting RLIM directly to VPOS provides

basic input short-circuit protection with the default current

limit of 16 mA typical.

The ADL5315 is available in a 2 mm × 3 mm, 8-lead LFCSP and

is specified for operation from −40°C to +85°C.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

Page 2

ADL5315

TABLE OF CONTENTS

Features.............................................................................................. 1

Noise Performance..................................................................... 10

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 4

ESD Caution.................................................................................. 4

Pin Configuration and Function Descriptions............................. 5

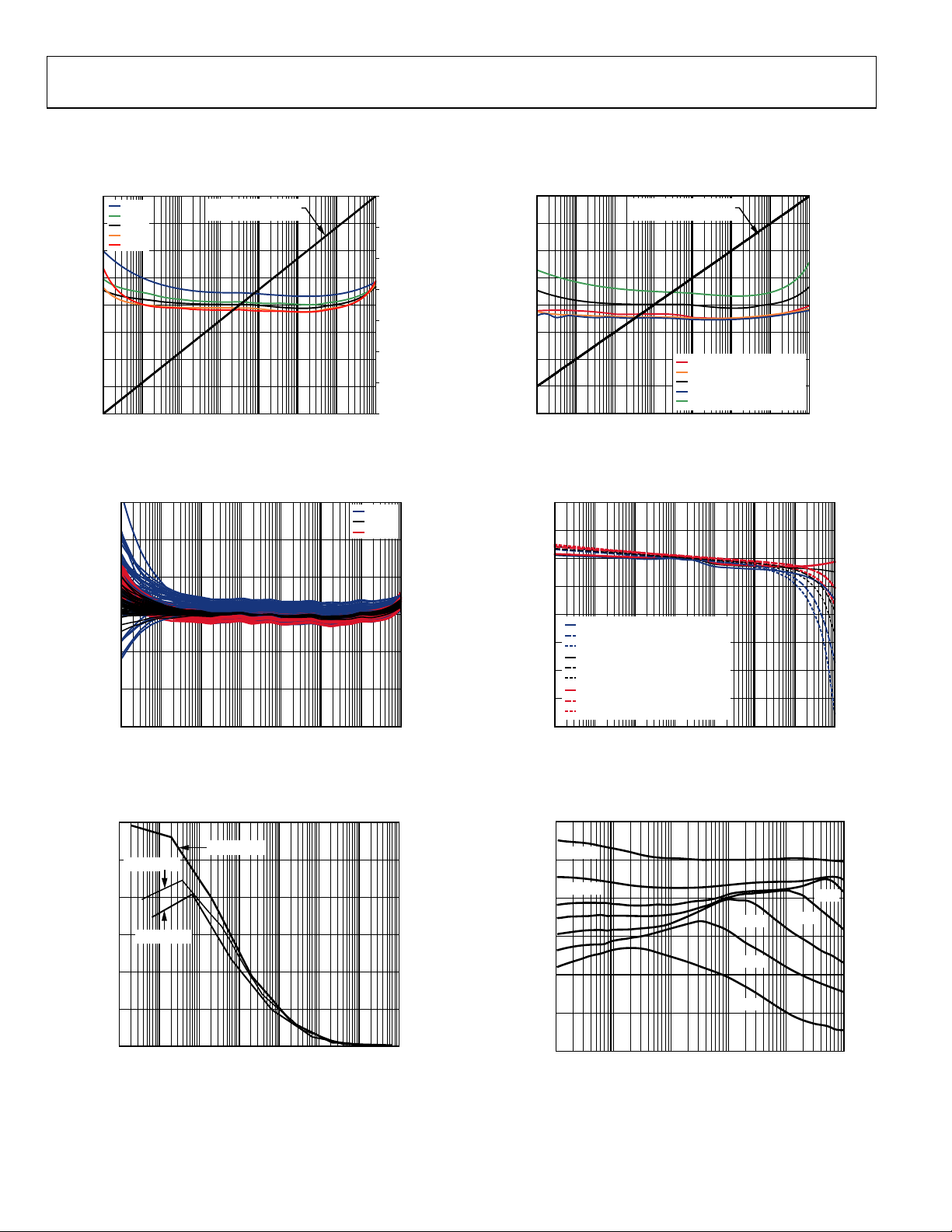

Typical Performance Characteristics ............................................. 6

Theory of Operation ........................................................................ 9

Bias Control Interface.................................................................. 9

REVISION HISTORY

10/05—Revision 0: Initial Version

Mirror Response Time............................................................... 10

Input Current Limiting.............................................................. 10

Applications..................................................................................... 11

Average Power Monitoring ....................................................... 11

Translinear Log Amp Interfacing............................................. 12

Extended Operating Range....................................................... 13

Using RLIM as a Secondary Monitor...................................... 13

Characterization Methods ........................................................ 14

Evaluation Board............................................................................ 16

Outline Dimensions....................................................................... 17

Ordering Guide .......................................................................... 17

Rev. 0 | Page 2 of 20

Page 3

ADL5315

SPECIFICATIONS

V

= 5 V, V

POS

Table 1.

Parameter Conditions Min Typ Max Unit

CURRENT MIRROR OUTPUT IOUT (Pin 8)

Current Gain from INPT to IOUT 0.99 1.00 1.01

Current Gain from INPT to IOUT

Nonlinearity 3 nA < IPD < 3 mA 0.25 1.00 %

Small Signal Bandwidth I

I

Wideband Noise at IPDM

Specified Output Voltage Range 0 V

I

× R

OUT

MIRROR INPUT, VOLTAGE CONTROL INPT (Pin 1), VSET (Pin 2), SREF (Pin 3)

Specified Input Current Range, I

Specified VSET Voltage Range 2.7 V < V

6.5 V < V

Incremental Gain from VSET to INPT 0.2 V < V

Incremental Input Resistance at VSET V

Input Bias Current at VSET V

SREF Voltage, Relative to V

OVERCURRENT PROTECTION

INPT Current Limit V

V

POWER SUPPLY VPOS (Pin 6)

Supply Voltage Range 2.7 8 V

Quiescent Current I

I

= 4 V, I

SET

Product I

OUT

= 3 µA, TA = 25°C, unless otherwise noted.

INPT

INPT

POS

−40°C < TA < +85°C

= 3 nA 1 kHz

INPT

= 3 μA 1 MHz

INPT

I

= 3 μA, C

INPT

= 3 μA 900

INPT

= 2.2 nF 20 nA rms

SET

0.97 1.00 1.03 A/A

− 1 V

POS

Flows from INPT pin 3n 3m A

< 6.5 V 0 V

POS

< 8 V V

POS

< 7.0 V 0.98 1 1.02 V/V

SET

= 4.0 V >100 GΩ

SET

= 4.0 V <30 pA

SET

2.7 V < V

INPT

INPT

INPT

INPT

< 8 V −1.04 −1.0 −0.97 V

POS

drops to 0 V, R

drops to 0 V, R

= 0 Ω 16 mA

LIM

= 3 kΩ 6.4 8 9.6 mA

LIM

= 3 μA 1.8 2.2 mA

= 3 mA 8.3 10.2 mA

− 6.5 V

POS

− 1 V

POS

− 1 V

POS

V

Rev. 0 | Page 3 of 20

Page 4

ADL5315

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage 8 V

Input Current at INPT 20 mA

Internal Power Dissipation 500 mW

θJA (Soldered Exposed Paddle) 80°C/W

Maximum Junction Temperature 125°C

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Lead Temperature (Soldering 60 sec) 300°C

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rev. 0 | Page 4 of 20

Page 5

ADL5315

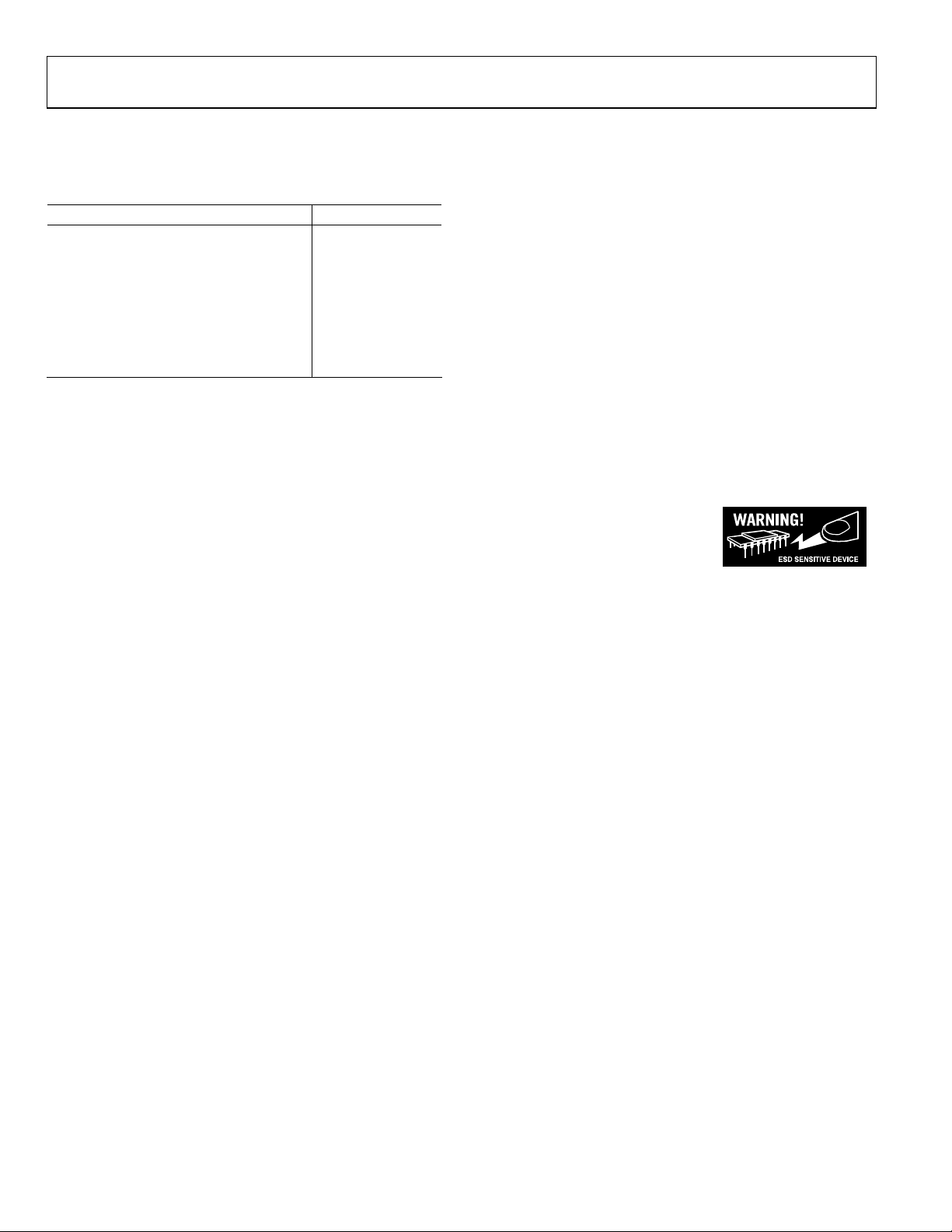

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1INPT

2VSET

ADL5315

TOP VIEW

3SREF

(Not to Scale)

4COMM

NC = NO CONNECT

8 IOUT

7NC

6 VPOS

5 RLIM

05694-002

Figure 2. 8-Lead LFCSP

Table 3. Pin Function Descriptions

Pin No. Mnemonic Description

1 INPT Input Current. Pin sources current only.

2 VSET

3 SREF

Sets Voltage at INPT (Gain = 1). Range 0 V to V

V

− 1 V. Optional shielding of INPT trace.

POS

Reference Voltage for VSET. Internally generated at V

− 1.0 V for V

POS

POS

< 6.5 V. For V

POS

POS

− 1.0 V through 20 kΩ. Can be shorted to VSET for

standard mirror operation.

4 COMM Analog Ground.

5 RLIM External Resistor to VPOS. Sets current limit at INPT from 1 mA to 16 mA. I

= 48 V/(R

LIM

6 VPOS Positive Supply (2.7 V to 8.0 V).

7 N/C Optional Shielding of IOUT Trace. No connection to die.

8 IOUT Output Current. Mirrors current at INPT with a gain of 1.0. Sources current only.

PADDLE Internally connected to COMM, solder to ground.

≥ 6.5 V range, V

+ 3 kΩ).

LIM

− 6.5 V to

POS

Rev. 0 | Page 5 of 20

Page 6

ADL5315

TYPICAL PERFORMANCE CHARACTERISTICS

V

= 5 V, V

POS

2.0

1.5

1.0

0.5

0

–0.5

LINEARITY (%)

–1.0

–1.5

–2.0

1n 10m

= V

, V

SET

SREF

–40°C

0°C

+25°C

+70°C

+85°C

10n 100n 1μ 10μ 100μ 1m

Figure 3. I

Linearity vs. I

OUT

= 0 V, TA = 25°C, unless otherwise noted.

OUT

+25°C, +70°C, +85°C,

0°C, –40°C

I

(A)

INPT

for Multiple Temperatures,

INPT

Normalized to 25°C and I

3

2

1

INPT

= 3 µA

10m

1m

100μ

10μ

1μ

100n

10n

1n

–40°C

+25°C

+85°C

(A)

I

2.0

1.5

1.0

0.5

OUT

05694-003

0

–0.5

LINEARITY (%)

–1.0

–1.5

–2.0

10n 100n 1μ 10μ 100μ 1m

1n 10m

Figure 6. I

Linearity vs. I

OUT

Normalized to V

40

20

0

–20

I

VS. I

INPT

VOLTAGE CONDITIONS

I

INPT

= 5 V, V

POS

, ALL

OUT

V

= 2.7V, V

POS

V

= 5V, V

POS

V

= 5V, V

POS

V

= 8V, V

POS

= 8V, V

V

POS

(A)

for Multiple Supply Conditions,

INPT

= V

SET

SREF

SET

SET

SET

SET

, and I

SET

= V

= 2V

= V

= 2V

= V

INPT

SREF

SREF

SREF

= 3 µA

10m

1m

100μ

10μ

1μ

100n

10n

1n

(A)

OUT

I

05694-006

LINEARITY (%)

WIDEBAND CURRENT NOISE (%)

3.0

2.5

2.0

1.5

1.0

0.5

0

–1

–2

–3

1n

Figure 4. I

10n 100n

Linearity vs. I

OUT

I

INPT

for Multiple Temperatures and

INPT

Devices Normalized to 25°C and I

V

= 3.0V

V

= 4.6V

POS

V

= 7.8V

POS

0

1n

10n 100n 1μ 10μ 100μ 1m

POS

I

INPT

(A)

(A)

INPT

= 3 µA

10m1μ 10μ 100μ 1m

10m

05694-021

05694-016

–40

VARIATION (mV)

–60

INPT

V

–80

–100

–120

Figure 7. V

1nA

100pA

10pA

1pA

NSD (A rms/√Hz)

100fA

10fA

1fA

–40°C, V

–40°C, V

–40°C, V

+25°C, V

+25°C, V

+25°C, V

+85°C, V

+85°C, V

+85°C, V

1n

10n 100n

Variation vs. I

INPT

Normalized to V

3.6mA

360μA

100Hz

1kHz 10kHz 100kHz 1MHz

POS

POS

POS

POS

POS

POS

POS

POS

POS

POS

= 2.7V, V

= 5V, V

= 5V, V

= 2.7V, V

= 5V, V

= 5V, V

= 2.7V, V

= 5V, V

= 5V, V

= 5 V, V

= V

SET

SREF

= 0V

SET

= V

SET

SREF

= V

SET

SREF

= 0V

SET

= V

SET

SREF

= V

SET

SREF

= 0V

SET

= V

SET

SREF

I

(A)

INPT

for Multiple Temperatures and Voltage,

INPT

= V

, I

SREF

INPT

= 3 µA and 25°C

SET

360nA

36nA

3.6nA

FREQUENCY

3.6μA

10m1μ 10μ 100μ 1m

36μA

10MHz

05694-005

05694-007

Figure 5. Output Wideband Current Noise as a Percentage of I

for Multiple Values of V

I

INPT

, C

= 2.2 nF, BW = 10 MHz

POS

SET

vs.

OUT

Rev. 0 | Page 6 of 20

Figure 8. Output Current Noise Density vs. Frequency for

Multiple Values of I

INPT

, V

POS

= 4.6 V, V

= V

, C

SREF

= 2.2 nF

SET

SET

Page 7

ADL5315

20

20

15

+3 SIGMA

10

5

AVERAGE

0

DRIFT (mV)

–5

INPT

V

–10

–3 SIGMA

–15

–20

–40

–30 –20 –10 0 10 20 30 40 50 60 70 80

Figure 9. Temperature Drift of V

10

5

0

–5

30nA

–10

–15

3nA

–20

–25

NORMALIZED RESPONSE (dB)

–30

–35

–40

100

1k 10k 100k 1M 10M 100M

Figure 10. Small-Signal AC Response of I

Decades from 3 nA to 3 mA

TEMPERATURE (°C)

with V

INPT

= V

SET

SREF

3μA 300μA

300nA

FREQUENCY (Hz)

90

, 3-σ to Either Side of Mean

3mA

30μA

1000M

to I

for I

INPT

OUT

INPT

in

05694-019

05694-008

15

10

+3 SIGMA

5

AVERAGE

0

DRIFT (mV)

–5

INPT

V

–10

–3 SIGMA

–15

–20

–40

–30 –20 –10 0 10 20 30 40 50 60 70 80

Figure 12. Temperature Drift of V

TEMPERATURE (°C)

with V

INPT

= 4 V (External Voltage Source),

SET

90

05694-022

3-σ to Either Side of Mean

10m

1m

100μ

10μ

(A)

OUT

I

1μ

100n

10n

1n

0

Figure 13. Pulse Response of I

300μA TO 3mA: T-RISE =

<10ns, T-FALL = <300ns

30μA TO 300μA: T-RISE =

<10ns, T-FALL = <300ns

3μA TO 30μA: T-RISE =

<10ns, T-FALL = <1μs

300nA TO 3nA: T-RISE =

<20ns, T-FALL = <5μs

30nA TO 300nA: T-RISE =

<5μs, T-FALL = <25μs

3nA TO 30nA: T-RISE =

<100μs, T-FALL = <200μs

50 100 150 200 250 300 350

TIME (μs)

to I

for I

INPT

OUT

in Decades from 3 nA to 3 mA

OUT

400

05694-017

4.5

T-RISE FOR ALL CURRENTS ≤ 200ns

4.0

3.5

3.0

2.5

2.0

(V)

INPT

1.5

V

1.0

0.5

–0.5

–1.0

0

0

123456789

1mA

T-FALL≤ 600ns

Figure 11. Pulse Response of V

(V

Pulsed from 0 V to 4 V) for Multiple Values of I

SET

100nA

T-FALL≤ 9.5ms

10μA

T-FALL≤ 180μs

TIME (ms)

10

I

= 48/(R

LIM

8

6

4

2

0

–2

–4

–6

–8

ERROR FROM CALCULATED CURRENT LIMIT (%)

10

05694-018

to V

INPT

INPT

SET

–10

0

Figure 14. Current Limit Error in Percent vs. R

+ 3kΩ)

LIM

V

= 5V, V

POS

10 20 30 40 50 60 70 80 90

SET

V

= V

POS

R

SREF

LIM

= 2.7V, V

V

POS

(kΩ)

= V

SET

SREF

= 8V, V

= V

SET

SREF

for Multiple Voltages

LIM

100

05694-020

Rev. 0 | Page 7 of 20

Page 8

ADL5315

1.010

1.005

(V)

INPT

1.000

– V

POS

V

0.995

+85

+25

–40

(%)

35

30

25

20

15

10

5

N = 2027

MEAN = –1.00696

SD = 0.00389073

0.990

2

Figure 15. V

25

20

15

(%)

10

5

0

0.99

Figure 16. Distribution of I

3

0.993 0.996 0.999 1.002 1.005 1.008

4567

− V

POS

INPT

OUT/IINPT

(V)

V

POS

vs. V

for Multiple Temperatures

POS

I

(A/A)

OUT/IINPT

for V

= 5 V, V

POS

N = 2014

MEAN = 1.00251

SD = 0.00175921

= 4 V, and I

SET

INPT

8

05694-004

05694-032

= 3 µA

0

–0.97

–0.98 –0.99 –1.00 –1.01 –1.02

Figure 17. Distribution of V

25

20

15

(%)

10

5

0

–0.03

–0.02 –0.01 0 0.01 0.02

Figure 18. Distribution of V

V

– V

− V

for V

– V

POS

POS

for V

INPT

POS

(V)

POS

(V)

= 5 V, V

= 5 V and I

N = 2034

MEAN = 0.00122744

SD = 0.00403179

= 4 V, and I

SET

SREF

SREF

V

SET

− V

SET

INPT

INPT

–1.03

= 3 µA

0.03

INPT

05694-033

05694-034

= 3 A

Rev. 0 | Page 8 of 20

Page 9

ADL5315

T

T

THEORY OF OPERATION

The ADL5315 addresses the need for precision high-side

monitoring of photodiode current in fiber optic systems and is

useful in many nonoptical applications as well. It is optimized

for use with ADI’s family of translinear logarithmic amplifiers,

which take advantage of the wide input current range of the

ADL5315. This arrangement allows the anode of the photodiode to connect directly to a transimpedance amplifier for the

extraction of the data stream without the need for a separate

optical power monitoring tap.

Figure 19 shows the basic

connections for the ADL5315.

ADL5315

2.2nF

4

COMM

3

SREF

2 7

VSET NC

1

INPT

4kΩ

390pF

Figure 19. Basic Connections

RLIM

VPOS

IOUT

5

R

6

8

MIRROR

CURRENT

OUTPUT

LIM

VOLTAGE

SUPPLY

0.01μF0.1μF

At the heart of the ADL5315 is a precision 1:1 current

mirror with a voltage following characteristic that provides an

adjustable bias voltage at the mirror input. This architecture

uses a JFET input amplifier to drive the bipolar mirror and

maintain stable V

voltage, while offering very low leakage

INPT

current at the INPT pin. The current sourced by the low

impedance INPT pin is mirrored and sourced by the high

impedance IOUT pin.

BIAS CONTROL INTERFACE

The voltage at the INPT pin, V

voltage applied to VSET by the mirror-biasing loop. The V

voltage range extends down to ground, allowing the ADL5315

to be used as a voltage-to-current converter with a single resistor

from INPT to ground. This capability allows dark current to be

minimized in PIN photodiode systems by maintaining a small

voltage bias. The VSET control also allows V

approximately equal to the load voltage at IOUT. Balancing

the mirror voltages in this way provides inherently superior

linearity over the widest current range independent of the

supply voltage. Only leakage currents from the JFET op amp

and ESD devices remain as significant sources of nonlinearity

at very low currents. The voltage at VSET can also be used to

shield the highly sensitive INPT pin and its board trace from

leakage currents, because the two pins operate at approximately

the same potential. Care must be taken to provide a low noise

V

signal, since voltage noise at VSET also appears at INPT

SET

and is transformed by the input compensation network into

current noise.

, is forced to be equal to the

INPT

to be set

INPT

SET

05694-023

The ADL5315 provides a setpoint reference pin, SREF,

which can be connected to VSET for standard 2-port

mirror operation. V

is maintained 1.0 V below V

SREF

POS

over

temperature and is independent of input current. When using

SREF to set the input voltage, a capacitor should be placed

between SREF and ground to filter noise from SREF as well

as improve power supply rejection over frequency. A value of

2.2 nF, for example, combined with the 20 kΩ output resistance

at SREF, creates a pole at approximately 3 kHz.

The voltage at the SREF pin can be lowered to a desired fixed

value with the use of a single external resistor from SREF to

ground. Mismatch between on-chip and external resistors

limits the accuracy of the resultant voltage. In addition, internal

clamping to protect the precision bias limits the range.

Figure 20

shows an equivalent circuit model of the SREF biasing. The

Schottky diode clamp protects the 50 µA current source when

SREF is pulled to ground. When V

is 1.2 V or higher, the

SREF

50 µA current flows to the SREF pin. The current is shunted

away and does not appear at the SREF pin for V

< 0.6 V.

SREF

The transition region is between 0.6 V and 1.2 V with a large

uncertainty in the pull-down current. It is recommended that a

2-resistor divider from VPOS (with no connection to SREF) or

another external bias be used to bias VREF in this transition

region.

Equations for the SREF voltage with an external pull-down R

EXT

follow:

R

V

SREF

V

=

SREF

EXT

=

R

EX

R

EXT

R

EX

()

k2

0≥−+

VV

k2

0≤+

SREFPOS

VV

SREFPOS

V

6.0,

V 1V 1

2.,0.

where the 20 kΩ is the process-dependent internal resistor.

V

POS

ADL5315

Figure 20. Model of SREF Bias Source with External Pull-Down

20kΩ

0.9V

VSET

SREF

50μA

R

C

SET

EXT

05964-029

Rev. 0 | Page 9 of 20

Page 10

ADL5315

The VSET control is intended primarily to provide a dc bias

voltage for the mirror input, but it is also well behaved in the

presence of the V

transients. The rise time of V

SET

is largely

INPT

independent of input current because the mirror is capable of

sourcing large currents to pull up the INPT pin. The fall time,

however, is inversely proportional to I

because only I

INPT

INPT

is

available to discharge the input compensation capacitor and

other parasitics (see

vary significantly from zero to several milliamps until V

Figure 11). The mirror output current can

is

INPT

fully settled.

NOISE PERFORMANCE

The noise performance for the ADL5315, defined as the rms

noise current as a fraction of the output dc current, generally

improves with increasing signal current. This partially results

from the relationship between the quiescent collector current

and the shot noise in the bipolar transistors. At lower signal

current levels, the noise contribution from the JFET amplifier

and other voltage noise sources appearing at INPT contribute

significantly to the current noise. Filtering noise at VSET,

whether provided by SREF or generated externally, as well as

selecting optimal external compensation components on INPT,

minimizes the amount of current noise at IOUT generated by

the voltage noise at INPT.

MIRROR RESPONSE TIME

The response time of I

function of input current, with small-signal bandwidth increasing

roughly in proportion to I

external compensating capacitor on INPT strongly affects the

I

response time (as well as the V

OUT

in the

Bias Control Interface section), although the value must

be chosen to maintain stability and prevent noise peaking.

to changes in I

OUT

(see Figure 10). The value of the

INPT

SET

is fundamentally a

INPT

to V

fall time, as noted

INPT

INPUT CURRENT LIMITING

The ADL5315 provides a resistor-programmable input current

limit with a fixed maximum of 16 mA for the RLIM pin tied to

VPOS. The fixed maximum provides input short-circuit protection

to ground. The current limit is defined as the current that forces

V

to 0 V (when using a current source on the INPT pin).

INPT

Resistor R

current limit according to

over an R

to 1 mA. Larger values of R

1 mA (down to approximately 250 µA) with some degradation

in accuracy. See

between the VPOS and RLIM pins controls the

LIM

=

I

LIM

LIM

V 48

k3

+

R

LIM

range of 0 to 45 kΩ, corresponding to 16 mA down

can be used for currents below

LIM

Figure 14 for more performance detail.

Rev. 0 | Page 10 of 20

Page 11

ADL5315

APPLICATIONS

The ADL5315 is primarily designed for wide dynamic range

applications, simplifying power monitoring designs where

access is only permitted to the cathode of a PIN photodiode or

receiver module.

Figure 22 shows a typical application where

the ADL5315 is used to provide an accurate bias to a PIN diode

while simultaneously mirroring the diode current to be

measured by a translinear logarithmic amplifier.

In this application, the ADL5315 sets the bias voltage on the

PIN diode. This voltage is delivered at the INPT pin and is

controlled by the voltage at the VSET pin. VSET is driven by

the on-board reference V

The input current, I

INPT

, which is equal to V

SREF

, is precisely mirrored at a ratio of 1:1 to

− 1 V.

POS

the IOUT pin. This interface is optimized for use with any of

ADI’s translinear logarithmic amplifiers (for example, the

AD8304 or AD8305) to offer a precise, wide dynamic range

measurement of the optical power incident upon the PIN.

If a linear voltage output is preferred at IOUT, a single external

resistor to ground is all that is necessary to perform the

conversion.

AVERAGE POWER MONITORING

In applications where a modulated signal is incident upon the

photodiode, the average power of the signal can be measured.

Figure 21 shows the connections necessary for using the

ADL5315 in such a measurement system.

The value of the capacitor to ground should be selected to

eliminate errors due to modulation of the ADL5315 input

current.

VOLTAGE

REFERENCE

4

COMM

20kΩ

3

C

PIN

SREF

SET

VSET NC

2 7

INPT

1

I

PD

CURRENT

CURRENT

MIRROR

ADL5315

LIMITING

1:1

I

PD

RLIM

VPOS

IOUT

V

POS

5

6

LINEAR

8

VOLTAGE

OUTPUT

TIA

DATA PATH

05694-010

Figure 21. Average Power Monitoring Using the ADL5315

V

POS

– 3kΩ

LIM

THIS CONNECTION IS NOT NECESSARY,

BUT REDUCES ERRORS DUE TO LEAKAGE

CURRENTS AT LOW SIGNAL LEVELS.

INPT

TRANSLINEAR LOG AMP

AD8304, AD8305, ETC.

OPTICAL

POWER

05694-009

NODE VOLTAGES

V

= V

SET

= V

POS

PIN

– 1V

INPT

SREF

V

ADL5315

VOLTAGE

REFERENCE

4

COMM

20kΩ

3

SREF

VSET NC

2 7

INPT

1

I

PD

TIA

DATA PATH

CURRENT

LIMITING

CURRENT

MIRROR

1:1

I

PD

RLIM

VPOS

IOUT

R

5

6

8

LIM

I

LIM =

= 48V

I

LIM

R

1mA – 16mA

VSUM

Figure 22. Typical Application Using the ADL5315

Rev. 0 | Page 11 of 20

Page 12

ADL5315

TRANSLINEAR LOG AMP INTERFACING

The mirror current output, IOUT, of the ADL5315 is designed

to interface directly to an Analog Devices translinear

logarithmic amplifier, such as the

ADL5306.

Figure 24 shows the basic connections necessary for interfacing

the ADL5315 to the AD8305. In this configuration, the designer

can use the full current mirror range of the ADL5315 for high

accuracy power monitoring.

The measured rms noise voltage at the output of the AD8305 vs.

the input current is shown in

itself and in cascade with the ADL5315. The relatively low noise

produced by the ADL5315, combined with the additional noise

filtering inherent in the frequency response characteristics of

the AD8305, results in minimal degradation to the noise

performance of the AD8305.

AD8304, AD8305, or

Figure 23, both for the AD8305 by

Careful consideration should be made to the layout of the

circuit board in this configuration. Leakage current paths in the

board itself could lead to measurement errors at the output of

the translinear log amp, particularly when measuring the low

end of the ADL5315’s dynamic range. It is recommended that

when designing such an interface that a guard potential be used

to minimize this leakage. This can be done by connecting the

translinear log amp’s VSUM pin to the NC pin of the ADL5315,

with the VSUM guard trace running on both sides of the IOUT

trace. Additional details on using VSUM can be found in the

AD8304 or AD8305 data sheets. The VSET pin of the ADL5315

can be used in a similar fashion to guard the INPT trace.

5.5m

5.0m

4.5m

4.0m

3.5m

3.0m

2.5m

NOISE (V rms)

2.0m

1.5m

1.0m

0.5m

0

1n

10n 100n 1μ 10μ 100μ

Figure 23. Measured RMS Noise of AD8305 vs. AD8305

AD8305 AND

ADL5315

AD8305 ONLY

I

(A)

INPT

Cascaded with ADL5315

1m

05694-012

VOLTAGE

REFERENCE

4

COMM

20kΩ

3

C

SREF

SET

VSET NC

2 7

INPT

1

I

PD

PIN

TIA

DATA PATH

CURRENT

CURRENT

MIRROR

Figure 24. Interfacing the ADL5315 to the AD8305 for High Accuracy PIN Power Monitoring

ADL5315

LIMITING

1:1

I

PD

RLIM

VPOS

IOUT

R

= 48V

LIM

I

5

I

1mA – 16mA

LIM =

6

8

1nF

AD8305 INPUT

COMPENSATION

NETWORK

LIM

R

1kΩ

LIM

– 3kΩ

V

POS

14

15

16

M

4.7nF

200kΩ

2kΩ

1

VRDZ

2

VREF

3

IREF

4

INPT

0.1μF

COMM

COM

COMM13COMM

AD8305

VSUM6VNEG7VNEG8VPOS

5

3V TO 12V

VOUT

SCAL

BFIN

VLOG

12

11

10

9

OUTPUT

V

= 0.2 × LOG10 (I

OUT

PDM

/1nA)

05694-011

Rev. 0 | Page 12 of 20

Page 13

ADL5315

M

EXTENDED OPERATING RANGE

The ADL5315 is specified over an input current range of 3 nA

to 3 mA, but the device remains fully functional over the full

eight decade range specified for ADI’s flagship translinear

logarithmic amplifier, the

25

and Figure 26 show the performance of the ADL5315 for this

extended operating range vs. various temperature and supply

conditions.

AD8304 (100 pA to 10 mA). Figure

USING RLIM AS A SECONDARY MONITOR

The RLIM pin can be used as a secondary linear output for

monitoring input currents near the upper end of the ADL5315

current range. The RLIM pin sinks a current approximately

equal to I

the series combination of an internal 3 kΩ resistor and the

external R

the mirror bias to limit I

/40. The voltage generated by this current through

INPT

is compared to a 1.2 V threshold and fed back to

LIM

.

INPT

This extended dynamic range capability allows the ADL5315 to

be used in optical power measurement systems, precision test

equipment, or any other system that requires accurate, high

dynamic range current monitoring.

2.0

1.5

1.0

0.5

0

–0.5

LINEARITY (%)

–1.0

–1.5

–2.0

–40°C

0°C

+25°C

+70°C

+85°C

10n 100n 1μ 10μ 100μ 1m

1n100p

+25°C, +70°C, +85°C,

0°C, –40°C

I

(A)

INPT

Figure 25. Extended Operating Range of 100 pA to 10 mA for Multiple

2.0

1.5

1.0

0.5

0

–0.5

LINEARITY (%)

–1.0

–1.5

–2.0

Temperatures, Normalized to 25°C and I

I

VS. I

(A)

V

V

V

V

V

OUT

POS

POS

POS

POS

POS

, ALL

= 2.7V, V

= 5V, V

= 5V, V

= 8V, V

= 8V, V

INPT

VOLTAGE CONDITIONS

1n 10m

10n 100n100p 1μ 10μ 100μ 1m

I

INPT

SET

SET

SET

SET

SET

INPT

= V

= 2V

= V

= 2V

= V

Figure 26. Extended Operating Range of 100 pA to 10 mA for Multiple Supply

Conditions, Normalized to V

= 5 V, V

POS

= V

and I

SET

SREF

= 3 µA

SREF

SREF

SREF

INPT

10m

1m

100μ

10μ

1μ

100n

10n

1n

100p

10m

10m

1m

100μ

10μ

1μ

100n

10n

1n

100p

= 3 µA

(A)

OUT

I

(A)

OUT

I

Figure 27 shows the equivalent circuit and one method for

using RLIM to form a V

bias proportional to I

SET

INPT

, also

referred to as automatic photodiode biasing. This configuration

is useful in PIN photodiode systems to compensate for photodiode equivalent series resistance (ESR) while maintaining low

reverse bias at low signal levels to minimize dark current.

Choosing R2 >> R

minimizes impact on I

LIM

and allows

LIM

the resistor ratio, R2/R1, to be calculated based on maximum

photodiode ESR using the following simplified equation.

R2

R1

where

For zero bias at zero input current, the sum of R

equal R1. For positive bias at zero input current, the sum of R

and R3 should be greater than R1. The ratio of V

05694-030

varies directly.

For example, choosing R

R40

PDmax

R

LI

R

is the maximum ESR of the photodiode.

PDmax

= 1.82 kΩ (10 mA I

LIM

LIM

=>>= ,,

R3R1RR2

and R3 must

LIM

LIM

to V

SET

LIM

POS

),

R2 = 100 kΩ, and R1 = 18.2 kΩ compensates for photodiode

ESR up to 250 Ω.

A simple low voltage drop current mirror with a load resistor

can replace the differential amplifier shown in

Figure 27,

although the resulting input current limit is less accurate and

will vary with temperature.

V

POS

VPOS

RLIM

RLIM

I

3kΩ

INPT

/40

R3R1

05694-031

R2R2

VSET

Figure 27. Providing Automatic Photodiode Voltage Biasing Using RLIM Pin

MIRROR

BIAS

1.2V

05964-035

Rev. 0 | Page 13 of 20

Page 14

ADL5315

2.2

2.0

1.8

1.6

1.4

1.2

1.0

VOLTAGE (V)

0.8

SET

V

0.6

0.4

0.2

0

100p 1n

10n 100n

Figure 28. V

I

INPT

Voltage vs. I

SET

(A)

INPT

when

10m1μ 10μ 100μ 1m

05694-036

RLIM Is Configured for Automatic Photodiode Biasing

2.2

2.0

1.8

1.6

1.4

1.2

1.0

VOLTAGE (V)

0.8

SET

V

0.6

0.4

0.2

0

021

34 5 67

I

INPT

Figure 29. V

Voltage vs. I

SET

(mA)

INPT

1098

05694-037

when

RLIM Is Configured for Automatic Photodiode Biasing

Figure 28 and Figure 29 show the performance of the circuit in

Figure 27. The reverse bias across the photodiode is held at a

low value for small input currents to minimize dark current.

The V

voltage increases in a linear manner at the higher input

SET

currents to maintain accurate photodiode responsivity. The

minimum bias level for the configuration above is ~200 mV.

CHARACTERIZATION METHODS

During characterization, the ADL5315 was treated as a

precision 1:1 current mirror. To make accurate measurements

throughout the six-decade current range, calibrated Keithley

236 current sources were used to create and measure the test

currents. Measurements at low currents are very susceptible to

leakage to the ground plane. To minimize leakage on the

characterization board, the VSET pin is connected to traces that

buffer V

triax guard connector to provide buffering along the cabling.

The primary characterization setup shown in

to perform all static measurements, including mirror linearity

between I

I

INPT

board is similar to that of the evaluation board, except that triax

connectors are used instead of SMA. To measure pulse response,

noise, and small signal bandwidth, more specialized test setups

are used.

The setup in Figure 31 is used to measure the output current

noise of the ADL5315. Batteries are used in numerous places to

minimize introduced noise and remove the uncertainty

resulting from the use of multiple dc supplies. In application,

properly bypassed dc supplies provide similar results. The load

resistor is chosen for each current to maximize signal-to-noise

ratio while maintaining measurement system bandwidth (when

combined with the low capacitance JFET buffer). The custom

LNA is used to overcome noise floor limitations in the

HP89410A signal analyzer.

from ground. These traces are connected to the

INPT

Figure 30 is used

INPT

and I

OUT

, V

INPT

variation vs. I

, supply current, and

INPT

current limiting. Component selection of the characterization

ADL5315

CHARACTERIZATION BOARD

VPOS VSET SREF COMM

DC SUPPLIES/DMM

INPT

IOUT

Figure 30. Primary Characterization Setup

KEITHLEY 236

KEITHLEY 236

05694-025

Rev. 0 | Page 14 of 20

Page 15

ADL5315

+

1.5V

–

+

1.5V

–

+

1.5V

–

VPOS SREF VSET

ADL5315

INPT IOUT

R

INPUT

R

Figure 31. Configuration for Noise Spectral Density and Wideband Current Noise

Figure 32 shows the configuration used to measure the pulse

response of I

INPT

to I

. To create the test current pulse, Q1 is

OUT

used in a common base configuration with the Agilent 33250A

pulse generator. The output of the 33250A is a negative biased

square wave with an amplitude that results in a one decade

current step at I

R

is chosen according to what current range is desired. For

C

30 µA and lower, the

.

OUT

AD8067 FET input op amp is used in a

transimpedance amplifier configuration to allow for viewing on

the TDS5104 oscilloscope. For signals greater than 30 µA, the

ADA4899-1 replaced the AD8067 to avoid limiting the

bandwidth of the ADL5315.

The configuration in

V

is pulsed. Q1 and RC are used to generate the operating

SET

Figure 33 is used to measure V

INPT

while

current on the INPT pin. An Agilent 33250A pulse generator is

used on the VSET pin to create a 0.0 V to 4.0 V square wave.

The setup in

response from I

Figure 34 was used to measure the small signal ac

to I

INPT

. The AD8138 differential amplifier

OUT

was used to couple the ac and dc signals together. The ac signal

was modulated to a depth of 5% of full scale over frequency.

The voltage across R

values of R

are chosen to result in decade changes in I

F

sets the dc operating point of I

F

INPT

. The

INPT

. The

ADA4899-1 op amp is used as a transimpedance amplifier for

all current conditions.

+

9V

–

FET BUFFER

LOAD

2.2nF

+12V

–

9V

+

Q1

AGILENT 33250A

PULSE GENERATOR

–12V

R

C

Figure 32. Configuration for Pulse Response of I

TDS5104

OSCILLOSCOPE

Q1

R

C

Figure 33. Configuration for Pulse Response from V

NETWORK ANALYZER

OUTPUT R BA

POWER

SPLITTER

++

AD8138

EVAL BOARD

––

Figure 34. Configuration for Small-Signal AC Response

HP89410A

VECTOR SIGNAL

ANALYZER

LNA

ADL5315

EVALUATION BOARD

INPT

VPOS VSET SREF COMM

DC SUPPLIES/DMM

ADL5315

EVALUATION BOARD

INPT

VPOS SREF COMM

DC SUPPLIES/DMM

INPT

EVALUATION BOARD

VPOS VSET SREF COMM

R

F

50Ω

DC SUPPLIES/DMM

IOUT

VSET

IOUT

ADL5315

05694-028

R

C

PULSE GENERATOR

IOUT

TDS5104

OSCILLOSCOPE

to I

INPT

OUT

AGILENT 33250A

KEITHLEY 236

to V

SET

INPT

R

F

05694-024

05694-026

05694-027

Rev. 0 | Page 15 of 20

Page 16

ADL5315

EVALUATION BOARD

GND

PD

L1

0Ω

C4

OPEN

390pF

V

SET

C3

R4

4kΩ

SW1

R1

100Ω

S

REF

ADL5315

1

INPTI

2

VSET

3 6

SREF VPOS V

4

COMM

8

IOUT I

NC

RLIM

R5

OPEN

7

R3

0Ω

R2

10kΩ

5

C1

0.01μF

OUT

C2

0.01μF

POS

05694-013

Figure 35. Evaluation Board Schematic (Rev. A)

Table 4. Evaluation Board (Rev. A) Configuration Options

Component Function Default Conditions

VPOS, GND Supply and ground connections. Not applicable

INPUT, L1, C4

Input Interface: The evaluation board is configured to accept an input current at the

SMA connector labeled INPUT. Filtering of this current can be done using L1 and C4.

L1 = 0 Ω (size 0805)

C4 = open (size 00603)

R4, C3 Input Compensation. Provides essential HF compensation at the INPT pin. C3 = 390 pF (size 0805)

R4 = 4.02 kΩ (size 0402)

SREF, VSET, SW1,

R1, R6, R7

IOUT, R5

INPT Bias Voltage. The dc voltage applied to VSET determines the voltage at INPT,

V

= V

SET

. Connecting SREF to VSET sets the bias at INPT to be 1 V below V

INPT

POS

.

Opening SW1 allows for VSET to be driven externally via the SMA connector.

Output/Mirror Current Interface: The output current at the SMA connector labeled IOUT is

SW1 = closed

R1 = 100 Ω (size 0402)

R6 = R7 = 0 Ω (size 0402)

R5 = open (size 0603)

equal to the value at INPT. R5 allows a resistor to be installed for applications where a

scaled voltage referenced to IPD is desirable instead of a current.

R2

Current Limiting. An external resistor to VPOS sets the current limit at INPT from

1 mA to 16 mA. I

= 3.7 mA.

I

LIM

= 48 V/(R

LIM

+ 3 kΩ). The evaluation board is configured such that

LIM

R2 = 10 kΩ (size 0402)

C1, C2, R3 Supply Filtering/Decoupling. C1 = 0.01 μF (size 0402)

C2 = 0.1 μF (size 0603)

R3 = 0 Ω (size 0805)

Figure 36. Component Side Layout

05694-014

Figure 37. Component Side Silkscreen

Rev. 0 | Page 16 of 20

05694-015

Page 17

ADL5315

R

OUTLINE DIMENSIONS

1.89

1.74

1.59

58

BOTTOM VIEW

EXPOSED PAD

4 1

*

0.25

0.20

0.15

0.15

0.10

0.05

0.55

0.40

0.30

PIN 1

INDICATO

1.00

0.85

0.80

SEATING

3.25

3.00

1.95

1.75

1.55

PLANE

12° MAX

2.75

TOP VIEW

2.95

2.75

2.55

0.30

0.23

0.18

0.80 MAX

0.65 TYP

2.25

2.00

1.75

0.20 REF

0.60

0.45

0.30

0.50 BSC

0.05 MAX

0.02 NOM

Figure 38. 8-Lead Lead Frame Chip Scale Package [LFCSP_VD]

2 mm × 3 mm Body, Very Thin, Dual Lead

(CP-8-1)

Dimensions shown in millimeters

ORDERING GUIDE

Model Temperature Range Package Description Package Option Branding

ADL5315ACPZ-R7

ADL5315ACPZ-WP

ADL5315-EVAL Evaluation Board

1

Z = Pb-free part.

2

WP = Waffle pack

1

1, 2

–40°C to +85°C 8-Lead LFCSP_VD CP-8-1 Q0

–40°C to +85°C 8-Lead LFCSP_VD CP-8-1 Q0

Rev. 0 | Page 17 of 20

Page 18

ADL5315

NOTES

Rev. 0 | Page 18 of 20

Page 19

ADL5315

NOTES

Rev. 0 | Page 19 of 20

Page 20

ADL5315

NOTES

© 2005 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D05694–0–10/05(0)

Rev. 0 | Page 20 of 20

Loading...

Loading...