Page 1

V

www.BDTIC.com/ADI

4.0 Gbps Dual Driver

FEATURES

>4.0 Gbps (2 V swings)

120 ps rise time/fall time (2 V swings)

<1.0 W for dual driver (<500 mW/channel)

−1 V to +3.5 V range

Fast termination mode (VTx)

Cable loss compensation

APPLICATIONS

Automatic test equipment

Semiconductor test systems

Board test systems

Instrumentation and characterization equipment

High speed memory testing (DDR2/DDR3/DDR4)

HDMI testing

GENERAL DESCRIPTION

The ADATE209 is a dual pin driver designed for testing DDR2,

DDR3, and DDR4. It can also be used for high speed SoC applications, such as testing PCI Express 1.0 and HDMI™. The device is a

three-level driver capable of high fidelity swings from 200 mV

to 4 V over a −1 V to +3.5 V range. It has rise/fall times (20% to

80%) under 120 ps for a 2 V programmed swing and 150 ps for

ADATE209

FUNCTIONAL BLOCK DIAGRAM

H1

VL1

VT1

DA1

DB1

TERM1

DA2

DB2

TERM2

Figure 1.

a 3 V programmed swing, and is capable of supporting data

rates of 4.4 Gbps and 3.2 Gbps, respectively.

The device is capable of high speed transitions into and out of

termination mode. It also contains peaking/pre-emphasis circuitry.

The ADATE209 is available in an 8 mm × 8 mm, 49-ball

CSP_BGA.

CLC1EN

VH2

VL2

CLC2EN

VT2

DROUT1

DROUT2

07277-001

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

Page 2

ADATE209

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Electrical Characteristics ............................................................. 3

Absolute Maximum Ratings ............................................................ 6

Thermal Resistance ...................................................................... 6

Explanation of Test Levels ........................................................... 6

REVISION HISTORY

5/08—Revision 0: Initial Version

ESD Caution...................................................................................6

Pin Configuration and Function Descriptions ..............................7

Typical Performance Characteristics ..............................................9

Applications Information .............................................................. 14

Data Inputs .................................................................................. 14

Thermal Diode String ................................................................ 14

Cable Loss Compensation/Peaking Circuitry ........................ 14

Default Test Conditions ............................................................. 14

Outline Dimensions ....................................................................... 15

Ordering Guide .......................................................................... 15

Rev. 0 | Page 2 of 16

Page 3

ADATE209

www.BDTIC.com/ADI

SPECIFICATIONS

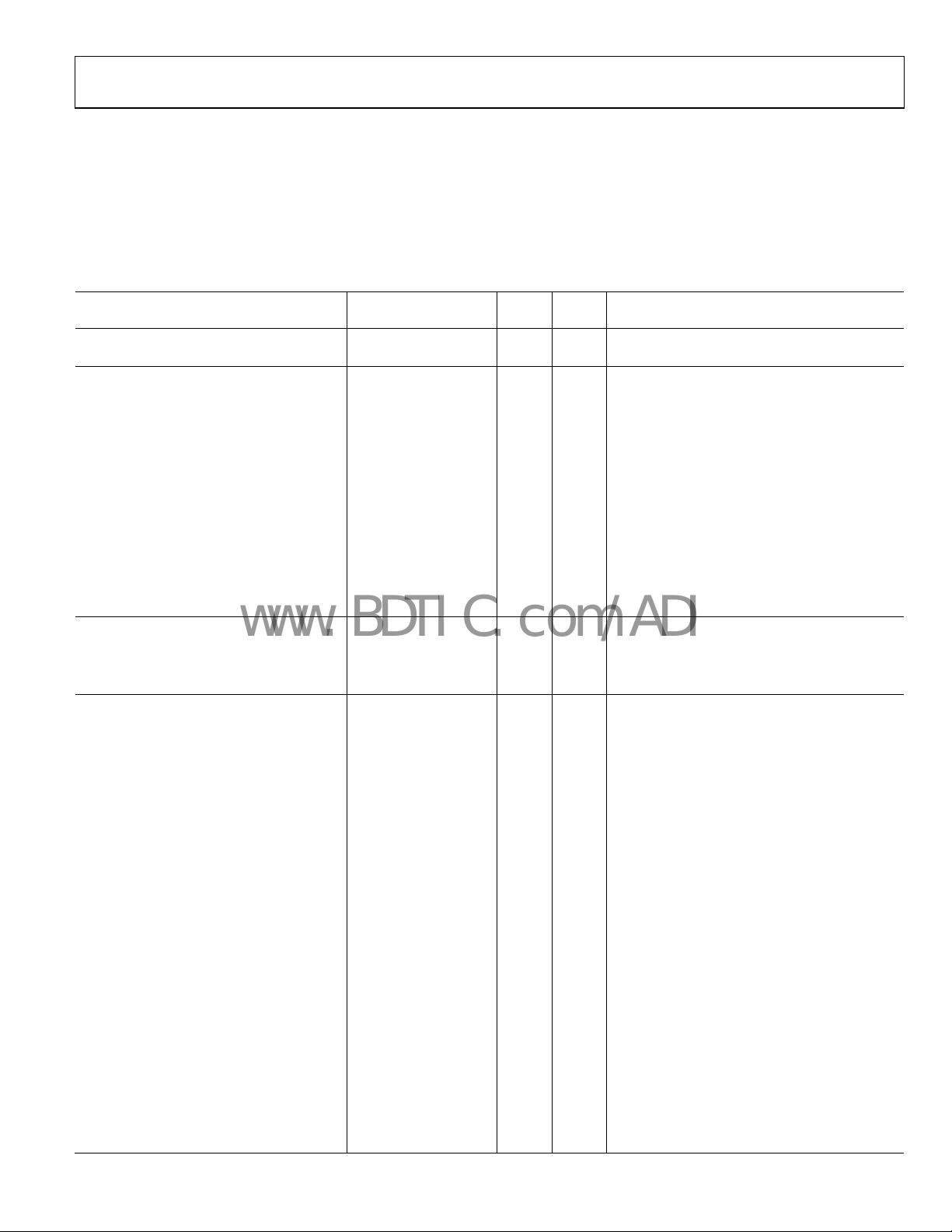

ELECTRICAL CHARACTERISTICS

VCC = 7.0 V, VEE = −4.5 V, GND = 0.0 V; all test conditions are as defined in Table 7, unless otherwise specified. All specified values are at

= 70°C, where TJ corresponds to the internal temperature sensor, unless otherwise noted. Temperature coefficients are measured at TJ =

T

J

70°C ± 20°C, unless otherwise noted. Typical values are based on design, simulation analyses, and/or limited bench evaluations. Typical

values are not tested or guaranteed.

Table 1.

Te st

Parameter Min Typ Max Unit

TOTAL FUNCTION

DROUTx Pin Range −1.0 +3.5 V I

POWER SUPPLIES

Positive Supply, VCC 6.65 7.0 7.35 V I Defines PSRR conditions

Negative Supply, VEE −4.73 −4.5 −4.28 V I Defines PSRR conditions

Data and Termination, V

Data and Termination, I

Positive Supply Current, ICC 50 76 100 mA II

Negative Supply Current, IEE 60 80 110 mA II

Total Power Dissipation 0.5 0.87 1.3 W II

0.97 W III

TEMPERATURE MONITORS

Temperature Sensor Gain −4.7

Temperature Sensor Offset 3.1 V III Voltage reading at 30°C

DRIVER DC SPECIFICATIONS

High Speed Differential Logic Input

Characteristics (DAx, DBx, TERMx)

Input Termination Resistance 45 48 55 Ω II

Input Voltage Differential 0.25 0.8 V IV

Common-Mode Voltage −1.0 +3.3 V IV

Input Bias Current −10 +1.2 +10 μA II

Pin Output Characteristics

Output High Range, VHx −0.9 +3.5 V I

Output Low Range, VLx −1.0 +3.4 V I

Output Termination Range, VTx −1.0 +3.5 V I

Output High Range, VHx −0.9 +4.0 V I VCC = 7.5 V, this range is not production tested

Output Low Range, VLx −1.0 +3.9 V I VCC = 7.5 V, this range is not production tested

Output Termination Range, VTx −1.0 +4.0 V I VCC = 7.5 V, this range is not production tested

Functional Amplitude (VHx − VLx) 0.2 4.5 V I

DC Output Current-Limit Source 50 60 70 mA II

DAx

DAx

, V

, V

DBx

, I

DBx

−1 +1.3 +3.3 V I

TERMx

, I

40 mA I

TERMx

mV/°C

Rev. 0 | Page 3 of 16

Level1 Test Conditions/Comments

Exceeding 40 mA through any input

termination resistor may cause damage to the

device or cause long-term reliability concerns

Quiescent; excludes current draw through data

input termination resistors

VLx = 0.0 V, VHx = 2.0 V; driver toggling into

open circuit; excludes current draw through

data input termination resistors

III

9 mA pushed into DAxB/DBxB/TERMxB signal,

0.6 V forced on DAx/DBx/TERMx signal; DAxT,

DBxT, TERMxT open; measure voltage from

DAx/DBx/ TERMx signal to DAxB/DBxB/TERMxB

signal, calculate resistance (ΔV/ΔI)

Each pin tested at −1.0 V and +3.3 V, while other

high speed pins (DAxB, DBx, DBxB, TERMx,

TERMxB) are left open, termination pins (DAxT,

DBxT, TERMxT ) open

Amplitude can be programmed to VHx = VLx,

accuracy specifications apply when VHx − VLx ≥

200 mV

Driver high, VHx = 3.5 V, short DROUTx pin to

−1.0 V, then measure current

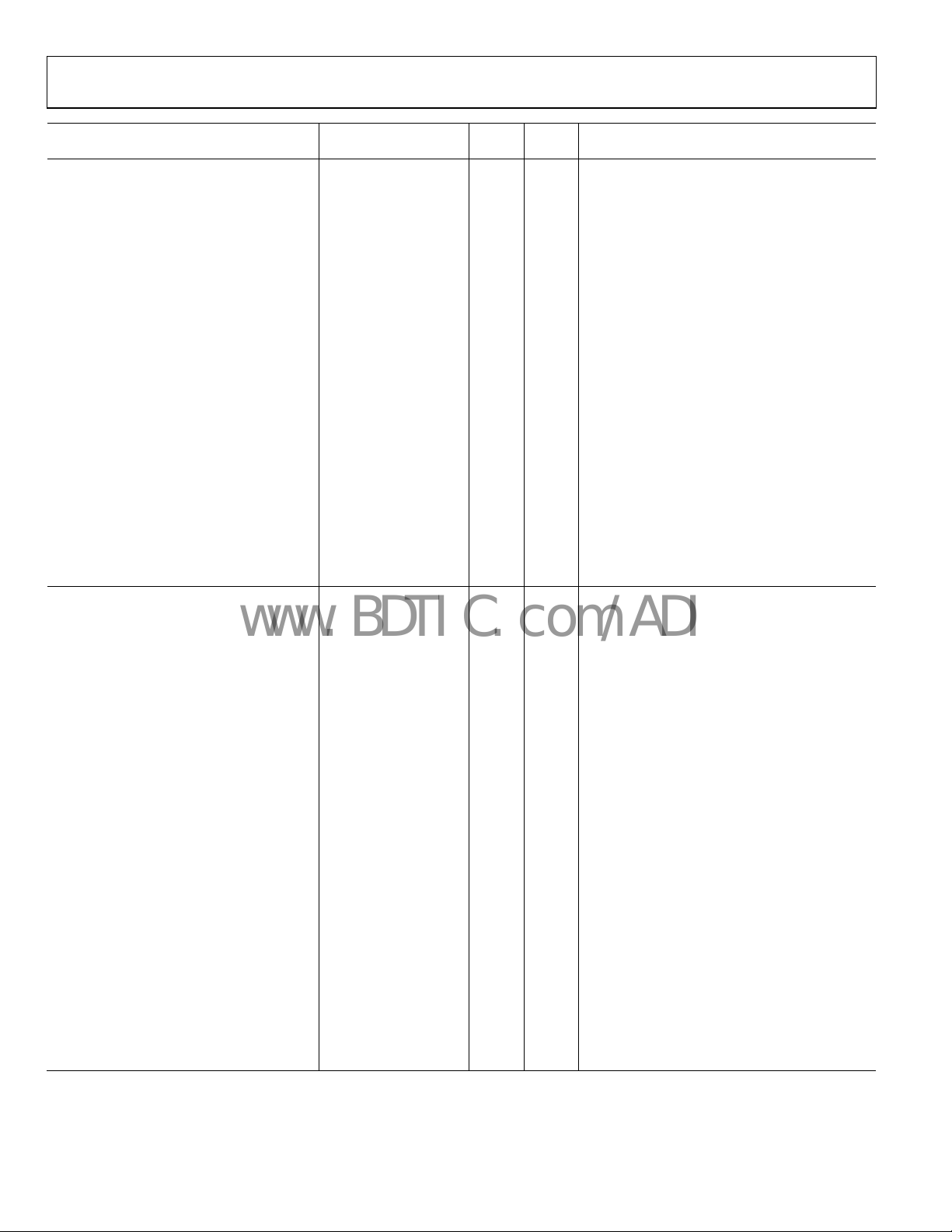

Page 4

ADATE209

www.BDTIC.com/ADI

Te st

Parameter Min Typ Max Unit

DC Output Current-Limit Sink −70 −60 −50 mA II

Output Resistance, ±30 mA 46.5 48.5 50.5 Ω II

Absolute Accuracy

VHx, VLx, VTx Offset −150 +20 +150 mV II Measured at 0.0 V, target: improve offset

VHx, VLx, VTx Offset Temperature

Coefficient

VHx, VLx, VTx Gain 0.97 1.02 1.03 %FSR II Relative to straight line from 0.0 V to 2.0 V

VHx, VLx, VTx Linearity −15 ±2.4 +15 mV II

VLx, VHx, VTx Interaction 0.3 mV III

VHx, VLx, VTx DC PSRR −36 +24 +36 mV/V II

VHx, VLx, VTx Input Bias Current −10 +1 +10 μA II

DRIVER AC SPECIFICATIONS

Rise/Fall Times Toggle DAx inputs

0.2 V Programmed Swing 115 ps V VHx = 0.2 V, VLx = 0.0 V, terminated, 20% to 80%

0.5 V Programmed Swing 90 ps V VHx = 0.5 V, VLx = 0.0 V, terminated, 20% to 80%

1.0 V Programmed Swing 90 ps V VHx = 1.0 V, VLx = 0.0 V, terminated, 20% to 80%

2.0 V Programmed Swing 90 110 130 ps II/V VHx = 2.0 V, VLx = 0.0 V, terminated, 20% to 80%

3.0 V Programmed Swing 150 ps V VHx = 3.0 V, VLx = 0.0 V, terminated, 20% to 80%

4.0 V Programmed Swing 190 ps V VHx = 3.5 V, VLx = −0.5 V, terminated, 20% to 80%

Rise-to-Fall Matching 10 ps V

Minimum Pulse Width Toggle both DAx and DBx inputs

0.2 V Programmed Swing 200 ps V

0.5 V Programmed Swing 180 ps V

1.0 V Programmed Swing 180 ps V

2.0 V Programmed Swing 200 ps V

3.0 V Programmed Swing 300 ps V

Maximum Toggle Rate 2.5 GHz V

2.2 GHz V

1.8 GHz V

270 μV/°C III Measured at calibration points, 0.0 V and 2.0 V

Level1 Test Conditions/Comments

Driver high, VHx = −1.0 V, short DROUTx pin to

3.5 V, then measure current

Source: driver high, VHx = 3.0 V, I

9 mA; sink: driver low, VLx = 0.0 V, I

/ΔI

and −9 mA; ΔV

VHx tests conducted with VLx = −1.0 V and

VTx = −1.0 V; VLx tests conducted with VHx =

3.5 V and VTx = 3.5 V; VTx tests conducted with

VLx = −1.0 V and VHx = 3.5 V

After two-point gain/offset calibration, relative

to straight line from 0.0 V to 2.0 V

VLx = −1.0 V, VHx swept from −0.9 V to +3.5 V,

VTx swept from −1.0 V to 3.5 V,

VHx = 3.5 V, VLx swept from −1.0 V to +3.4 V,

VTx swept from −0.8 V to +3.5 V,

VTx = 1.5 V, VLx swept from −1.0 V to +3.5 V,

VHx swept from −1.0 V to +3.5 V

Change in output voltage as power supplies are

moved by ±5%; measured at calibration points,

0.0 V and 2.0 V

VHx = 1.0 V, VLx = 0.0 V, terminated; rise to fall

within one channel

VHx = 0.2 V, VLx = 0.0 V, terminated, timing error

less than ±25 ps

VHx = 0.5 V, VLx = 0.0 V, terminated, timing error

less than ±25 ps

VHx = 1.0 V, VLx = 0.0 V, terminated, timing error

less than ±25 ps

VHx = 2.0 V, VLx = 0.0 V, terminated, timing error

less than ±25 ps

VHx = 3.0 V, VLx = 0.0 V, terminated, timing error

less than ±25 ps

VHx = 1.0 V, VLx = 0.0 V, terminated, 10%

amplitude degradation

VHx = 2.0 V, VLx = 0.0 V, terminated, 10%

amplitude degradation

VHx = 3.0 V, VLx = 0.0 V, terminated, 10%

amplitude degradation

DROUTx

DROUTx

= 1 mA and

DUT

= −1 mA

DUT

Rev. 0 | Page 4 of 16

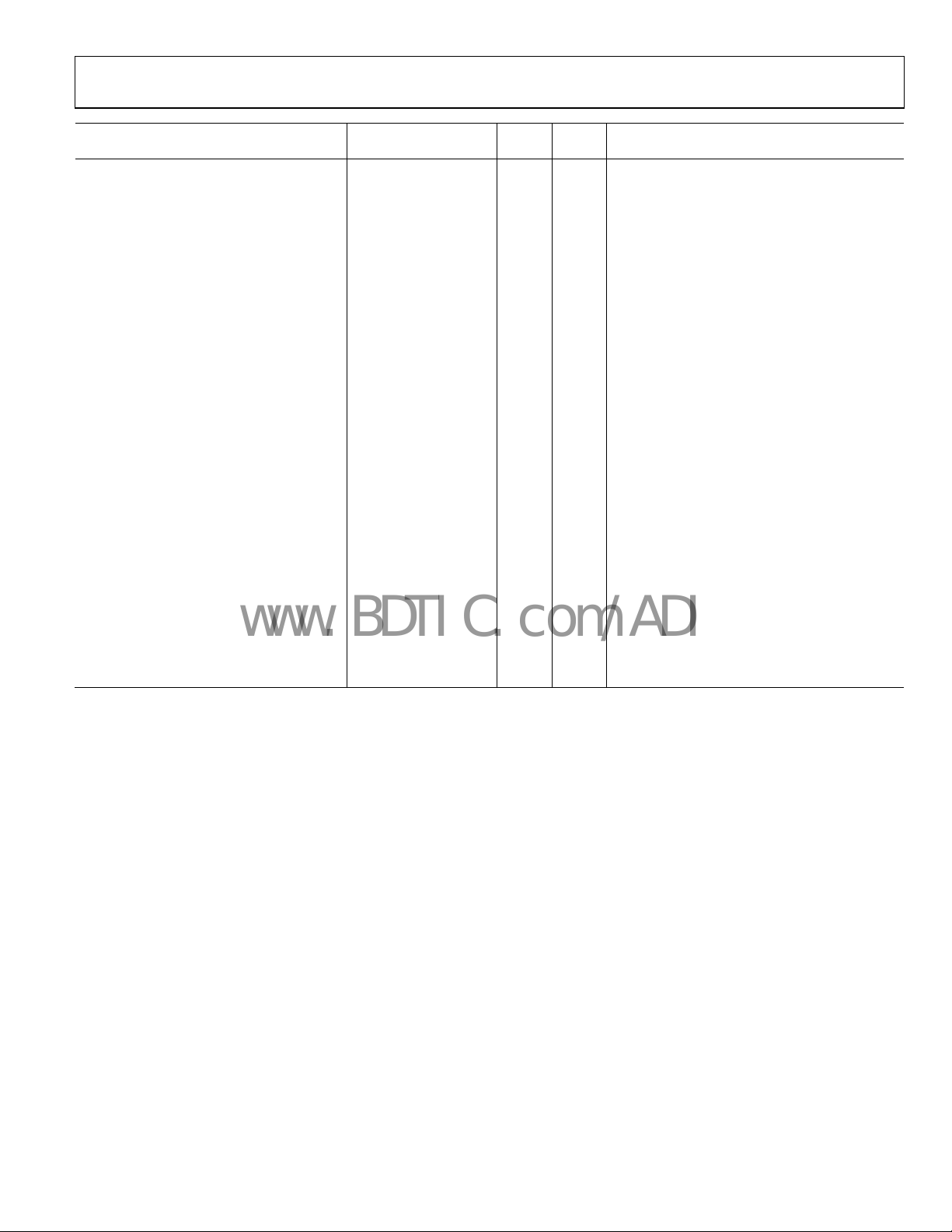

Page 5

ADATE209

www.BDTIC.com/ADI

Te st

Parameter Min Typ Max Unit

Dynamic Performance, Drive (VHx to VLx) Toggle DAx inputs

Propagation Delay Time 300 660 1400 ps II/V VHx = 2.0 V, VLx = 0.0 V, terminated

Propagation Delay Temperature

Coefficient

Delay Matching, Edge to Edge ±15 ps V VHx = 2.0 V, VLx = 0.0 V, terminated, rising vs. falling

Delay Change vs. Duty Cycle ±10 ps V

Preshoot and Undershoot 10 mV V VHx = 2.0 V, VLx = 0.0 V, terminated

Settling Time (VHx to VLx) Toggle DAx Inputs

To Within 3% of Final Value 0.4 ns V VHx = 2.0 V, VLx = 0.0 V, terminated

To Within 1% of Final Value 2 ns V VHx = 2.0 V, VLx = 0.0 V, terminated

Rise/Fall Times (VTx to/from VHx/VLx) Toggle DAx inputs

1.0 V Programmed Swing 110 ps V

2.0 V Programmed Swing 170 ps V

Dynamic Performance, V

(VHx or VLx to/from VTx)

Propagation Delay Time 720 ns V VHx = 3.0 V, VTx = 1.5 V, VLx = 0.0 V, terminated

Cable Loss Compensation

Logic Control Inputs, CLCxEN 0 3.3 V I

Logic High

Logic Low

I

CLCxEN

Compensation Constants

Boost Time Constant

Boost Peaking Amplifier 18 % V

1

See the Explanation of Test Levels section.

TERM

0.7 ps/ºC III VHx = 2.0 V, VLx = 0.0 V, terminated

Toggle TERMx inputs

0.9 3.3 V IV

0 0.7 V IV

−10 ±1.2 +10 μA II VIN = 0.0 V and 3.3 V

275 ps V

Level1 Test Conditions/Comments

VHx = 2.0 V, VLx = 0.0 V, terminated, 5% to 95%

duty cycle

VHx = 1.0 V, VTx = 0.5V, VLx = 0.0 V, terminated,

20% to 80%

VHx = 2.0 V, VTx = 1.0 V, VLx = 0.0 V, terminated,

20% to 80%

CLCxEN = 3.3 V, VHx = 1.0 V, VLx = 0.0 V,

terminated

CLCxEN = 3.3 V, VHx = 1.0 V, VLx = 0.0 V,

terminated

Rev. 0 | Page 5 of 16

Page 6

ADATE209

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltages

Positive Supply Voltage (VCC to GND) −0.5 V to +8.0 V

Negative Supply Voltage (VEE to GND) −5.0 V to +0.5 V

Supply Voltage Difference (VCC to VEE) −1.0 V to +13 V

Reference Ground (DUTGND to GND) −0.5 V to +0.5 V

Input Voltages

Input Common-Mode Voltage VEE to VCC

Short-Circuit Voltage (RL = 0 Ω, V

Continuous Short-Circuit Condition)

High Speed Input Voltage

(Data and Termination Inputs, DAx, DBx,

and TERMx)

High Speed Differential Input Voltage

(DAx, DBx, TERMx to Termination Pin

DAxT, DBxT, TERMxT)

VHx, VLx, VTx −2 V to +4.5 V

CLCxEN −1 V to +3.5 V

DROUTx I/O Pin Current

DCL Maximum Short-Circuit Current

RL = 0 Ω, V

(

Current Limit)

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

= −1.5 V to +4 V; DCL

DUT

DUT

−1.5 V to +4.0 V

−1.5 V to +3.9 V

2 V

±100 mA

THERMAL RESISTANCE

θJA is specified for the following conditions: JEDEC 4L PCB,

50°C, and 100 LFM forced convection. θ

cold plate and 50°C ambient temperature.

Table 3. Thermal Resistance

Package Type θJA θ

49-Ball CSP_BGA 48.4 3.9 °C/W

is specified for a 50°C

JC

Unit

JC

EXPLANATION OF TEST LEVELS

I. Definition.

II. 100% Production Tested.

III. Characterized on Tester.

IV. Functionally Checked During Production Test.

V. Characterized on Bench.

ESD CAUTION

Rev. 0 | Page 6 of 16

Page 7

ADATE209

www.BDTIC.com/ADI

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1234567

GND VEE DROUT2 GND DROUT1 VEE G ND

A

TERM2

B

TERM2B

C

DA2 DA2T

D

DA2B

E

DB2 DB2T

F

DB2B CLC2EN VT2

G

TERM2T

VCC

GND

VEE GND VEE VCC TERM1

VCC GND VCC TERM1T TERM1B

GND

VH2

VL2

Figure 2. Pin Configuration

GND GND DA1T DA1

GND VH1 GND DA1B

VCCTHERM VL1 DB1T DB1

THERM

VT1 CLC1EN DB1B

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

A1 GND Ground.

A2 VEE Negative Power Supply, −4.5 V.

A3 DROUT2 Driver Output, Channel 2.

A4 GND Ground.

A5 DROUT1 Driver Output, Channel 1.

A6 VEE Negative Power Supply, −4.5 V.

A7 GND Ground.

B1 TERM2 Termination Mode Data Input. Noninverting input for Channel 2.

B2 VCC Positive Power Supply, 7.0 V.

B3 VEE Negative Power Supply, −4.5 V.

B4 GND Ground.

B5 VEE Negative Power Supply, − 4.5 V.

B6 VCC Positive Power Supply, 7.0 V.

B7 TERM1 Termination Mode Data Input. Noninverting input for Channel 1.

C1 TERM2B Termination Mode Data Input. Inverting input for Channel 2.

C2 TERM2T Termination Pin for Termination Mode Data Input, Channel 2.

C3 VCC Positive Power Supply, 7.0 V.

C4 GND Ground.

C5 VCC Positive Power Supply, 7.0 V.

C6 TERM1T Termination Pin for Termination Mode Data Input, Channel 1.

C7 TERM1B Termination Mode Data Input. Inverting input for Channel 1.

D1 DA2 Data Input A. Noninverting input for Channel 2.

D2 DA2T Termination for Data Input A, Channel 2.

D3 GND Ground.

Rev. 0 | Page 7 of 16

07277-002

Page 8

ADATE209

www.BDTIC.com/ADI

Pin No. Mnemonic Description

D4 GND Ground.

D5 GND Ground.

D6 DA1T Termination for Data Input A, Channel 1.

D7 DA1 Data Input A. Noninverting input for Channel 1.

E1 DA2B Data Input A. Inverting input for Channel 2.

E2 GND Ground.

E3 VH2 VH Input, Channel 2.

E4 GND Ground.

E5 VH1 VH Input, Channel 1.

E6 GND Ground.

E7 DA1B Data Input A. Inverting input for Channel 1.

F1 DB2 Data Input B. Noninverting input for Channel 2.

F2 DB2T Termination for Data Input B, Channel 2.

F3 VL2 VL Input, Channel 2.

F4 VCCTHERM Positive Power Supply for Thermal Diode String, 7.0 V.

F5 VL1 VL Input, Channel 1.

F6 DB1T Termination for Data Input B, Channel 1.

F7 DB1 Data Input B. Noninverting input for Channel 1.

G1 DB2B Data Input B. Inverting input for Channel 2.

G2 CLC2EN Cable-Loss Compensation Control Pin, Channel 2.

G3 VT2 VT Input, Channel 2.

G4 THERM Thermal Diode Connection.

G5 VT1 VT Input, Channel 1.

G6 CLC1EN Cable-Loss Compensation Control Pin, Channel 1.

G7 DB1B Data Input B. Inverting input for Channel 1.

Rev. 0 | Page 8 of 16

Page 9

ADATE209

www.BDTIC.com/ADI

TYPICAL PERFORMANCE CHARACTERISTICS

0.30

0.25

0.5V

1.2

1.0

0.20

0.15

0.10

VOLTAGE (V)

0.05

–0.05

0

0

0.29

0.2V

0.58

0.87

1.16

1.45

1.74

2.03

2.32

2.61

2.90

3.19

3.48

3.77

4.06

4.35

4.64

TIME (ns)

4.93

Figure 3. Small Signal Response, VHx = 500 mV, 200 mV, VLx = 0.0 V

1.8

1.6

1.4

1.2

1.0

0.8

0.6

VOLTAGE (V)

0.4

0.2

0

–0.2

0

0.29

0.58

0.87

1.16

1.45

1.74

2.03

2.32

2.61

2.90

3.19

3.48

3.77

4.06

4.35

4.64

TIME (ns)

4.93

Figure 4. Large Signal Response, VHx = 3.0 V, 2.0 V, 1.0 V, VLx = 0.0 V

0.8

0.6

0.4

VOLTAGE (V)

0.2

0

CLC ENABLED

–0.2

07277-015

CLC DISABLED

0

0.116

0.232

0.348

0.464

0.580

0.696

0.812

0.928

TIME (ns)

1.040

1.160

1.280

1.390

1.510

1.620

1.740

1.860

1.970

07277-009

Figure 6. VHx = 2.0 V, VLx = 0.0 V, 1.5 GHz Waveform,

CLC Disabled and Enabled

1.2

CLC ENABLED

CLC DISABLED

1.0

0.8

0.6

0.4

VOLTAGE (V)

0.2

0

–0.2

0

0.058

0.116

0.174

0.232

0.290

0.348

0.406

0.464

0.522

0.580

0.638

0.696

0.754

0.812

0.870

0.928

07277-013

TIME (ns)

0.986

07277-010

Figure 7. VHx = 2.0 V, VLx = 0.0 V, 2.0 GHz Waveform,

CLC Disabled And Enabled

2.0

1.5

1.0

0.5

VOLTAGE (V)

0

–0.5

0

0.29

0.58

0.87

1.16

1.45

1.74

2.03

2.32

2.61

TIME (ns)

2.90

3.19

CLC ENABLED

CLC DISABLED

3.48

3.77

4.06

4.35

4.64

4.93

07277-014

Figure 5. Large Signal Response, VHx = 3.0 V, 2.0 V, 1.0 V, VLx = 0.0 V,

CLC Disabled and Enabled

Rev. 0 | Page 9 of 16

1.4

CLC ENABLED

CLC DISABLED

1.2

1.0

0.8

0.6

VOLTAGE (V)

0.4

0.2

0

–0.2

0

0.116

0.232

0.348

0.464

0.580

0.696

0.812

0.928

1.040

1.160

TIME (ns)

1.280

Figure 8. VHx = 2.0 V, VLx = 0.0 V, 1.0 GHz Waveform,

CLC Disabled and Enabled

1.390

1.510

1.620

1.740

1.860

1.970

07277-008

Page 10

ADATE209

www.BDTIC.com/ADI

1.2

1.0

0.8

0.6

0.4

VOLTAGE (V)

0.2

0

–0.2

CLC ENABLED

CLC DISABLED

–0.4

0

0.385

0.770

1.160

1.540

1.930

2.310

2.700

3.080

TIME (ns)

3.470

Figure 9. VHx = 2.0 V, VLx = 0.0 V, 500 MHz Waveform,

CLC Disabled and Enabled

0.6

3.850

4.240

4.620

07277-011

0.7

CLC ENABLED

CLC DISABLED

0.6

0.5

0.4

0.3

0.2

VOLTAGE (V)

0.1

0

–0.1

–0.2

0

0.116

0.232

0.348

0.464

0.580

0.696

0.812

0.928

1.040

1.160

TIME (ns)

1.280

Figure 12. VHx = 1.0 V, VLx = 0.0 V, 1.0 GHz Waveform,

CLC Disabled and Enabled

0.6

1.390

1.510

1.620

1.740

1.860

1.970

07277-003

0.5

0.4

0.3

0.2

VOLTAGE (V)

0.1

0

–0.1

CLC ENABLED

CLC DISABLED

–0.2

0

0.29

0.58

0.87

1.16

1.45

1.74

2.03

2.32

2.61

2.90

3.19

TIME (ns)

3.48

Figure 10. VHx = 1.0 V, VLx = 0.0 V, 500 MHz Waveform,

CLC Disabled and Enabled

0.6

0.5

0.4

0.3

0.2

VOLTAGE (V)

0.1

0.5

0.4

0.3

0.2

VOLTAGE (V)

0.1

0

–0.1

CLC ENABLED

CLC DISABLED

–0.2

3.77

4.06

4.35

4.64

4.93

07277-006

0

0.116

0.232

0.348

0.464

0.580

0.696

0.812

0.928

1.040

1.160

1.280

1.390

1.510

1.620

1.740

1.860

1.970

TIME (ns)

07277-004

Figure 13. VHx = 1.0 V, VLx = 0.0 V, 1.5 GHz Waveform,

CLC Disabled and Enabled

0.6

0.5

0.4

0.3

0.2

VOLTAGE (V)

0.1

0

CLC ENABLED

CLC DISABLED

–0.1

0

0.058

0.116

0.174

0.232

0.290

0.348

0.406

0.464

0.522

0.580

0.638

0.696

0.754

0.812

0.870

0.928

0.986

TIME (ns)

07277-005

Figure 11. VHx = 1.0 V, VLx = 0.0 V, 2.0 GHz Waveform,

CLC Disabled and Enabled

Rev. 0 | Page 10 of 16

0

–0.1

0

0.116

0.232

0.348

0.464

0.580

0.696

0.812

0.928

1.040

TIME (ns)

Figure 14. VHx = 1.0 V, VTx = 0.5 V, VLx = 0.0 V,

Transitions Between VHx/VLx and VTx

1.160

1.280

1.390

1.510

1.620

1.740

1.860

1.970

07277-007

Page 11

ADATE209

www.BDTIC.com/ADI

1.2

1.0

0.8

0.6

0.4

VOLTAGE (V)

0.2

0

–0.2

0

0.116

0.232

0.348

0.464

0.580

0.696

0.812

0.928

1.040

1.160

1.280

1.390

1.510

1.620

1.740

1.860

1.970

TIME (ns)

07277-012

Figure 15. VHx = 2.0 V, VTx = 1.0 V, VLx = 0.0 V,

30

20

10

0

–10

TRAILING EDGE ERROR (ps)

–20

–30

0.1 1 10

NEGATIVE PULSE

PULSE WIDTH (ns)

POSITIVE PULSE

07277-018

Figure 18. 3 V Minimum Pulse Width (VHx = 3.0 V, VLx = 0.0 V), CLC Disabled

Transitions Between VHx/VLx and VTx

30

20

10

0

NEGATIVE PUL SE

5

0

–5

–10

–10

TRAILING EDGE ERROR (ps)

–20

–30

0.1 1 10

POSITIVE PULSE

PULSE WIDTH (ns)

07277-016

Figure 16. 1 V Minimum Pulse Width (VHx = 1.0 V, VLx = 0.0 V), CLC Disabled

30

20

10

0

–10

TRAILING EDGE ERROR (ps)

–20

–30

0.1 1 10

POSITIVE PULSE

NEGATIVE PULSE

PULSE WIDTH (ns)

07277-017

Figure 17. 2 V Minimum Pulse Width (VHx = 2.0 V, VLx = 0.0 V), CLC Disabled

–15

LINEARITY ERROR (mV)

–20

–25

50°C

70°C

90°C

–2 –1 0 1 2 3 4

VHx (V)

Figure 19. Driver Linearity (VHx), VLx = −1.1 V, VTx = 1.0 V

4

3

2

1

0

–1

LINEARITY ERROR (mV)

–2

–3

–2 –1 0 1 2 3 4

VLx (V)

Figure 20. Driver Linearity (VLx), VHx = 3.6 V, VTx = 1.0 V

90°C

70°C

50°C

07277-019

07277-020

Rev. 0 | Page 11 of 16

Page 12

ADATE209

V

www.BDTIC.com/ADI

1.5

1.0

0.5

0

–0.5

–1.0

–1.5

–2.0

LINEARITY ERROR (mV)

50°C

–2.5

–3.0

–3.5

–2 –1 0 1 2 3 4

VTx (V)

90°C

Figure 21. Driver Linearity (VTx), VHx = 2.0 V, VLx = 0.0 V

70°C

07277-021

3.10

3.05

3.00

2.95

2.90

2.85

THERM VOLTAGE (V)

2.80

2.75

2.70

0 20406080100120

TEMPERATURE (° C)

Figure 24. Temperature Sensor Output Voltage vs. Temperature

07277-024

1.040

1.035

1.030

1.025

GAIN (%FSR)

1.020

1.015

1.010

40 100

50 60 8070 90

TEMPERATURE (°C)

GAIN VHx CH1

GAIN VHx CH2

Figure 22. Gain of VHx

10

5

0

–5

–10

DRIVER OFFSET (µ V)

–15

CH2 OFFSET

CH1 OFFSET

61.18mV/DIV

07277-022

200ps/DIV

07277-025

Figure 25. VHx = 1.8 V, VLx = 0.0 V, PRBS31, 1.6 Gbps, CLC Disabled

100mV/DI

–20

–25

50 60 8070 90

40 100

TEMPERATURE (° C)

07277-023

Figure 23. Driver Offset vs. Temperature

Rev. 0 | Page 12 of 16

200ps/DIV

07277-026

Figure 26. VHx = 1.8 V, VLx = 0.0 V, PRBS31, 2.1 Gbps, CLC Disabled

Page 13

ADATE209

V

V

V

www.BDTIC.com/ADI

100mV/DI

100ps/DIV

Figure 27. VHx = 1.5 V, VLx = 0.0 V, PRBS31, 3.2 Gbps, CLC Disabled

100mV/DIV

100ps/DIV

Figure 28. VHx = 1.5 V, VLx = 0.0 V, PRBS31, 4.0 Gbps, CLC Disabled

50mV/DI

07277-027

Figure 29. VHx = 0.5 V, VLx = 0.0 V, PRBS31, 5.0 Gbps, CLC Disabled

50mV/DI

07277-028

Figure 30. VHx = 0.5 V, VLx = 0.0 V, PRBS31, 5.0 Gbps, CLC Enabled

50ps/DIV

50ps/DIV

07277-029

07277-030

Rev. 0 | Page 13 of 16

Page 14

ADATE209

V

www.BDTIC.com/ADI

APPLICATIONS INFORMATION

DATA INPUTS

The ADATE209 contains three high speed differential inputs

for each channel. Two of the inputs, combined in an on-chip

exclusive-OR gate, control the VHx/VLx transitions. The

exclusive-OR gate can be used as a data mux or for data inversion.

The third input is used to control the transitions to the VTx level.

Table 5. Logic Truth Table

DAx DBx TERMx DROUTx

Low Low Low VL

High Low Low VH

Low High Low VH

High High Low VL

X1 X

1

X = don’t care.

1

High VT

The high speed inputs are designed to be compatible with most

types of differential inputs. Each side of the differential inputs is

terminated through 50 Ω to a common point. For connection to

PECL inputs, connect the DAxT/DBxT/TERMxT input

termination to V

− 2.0 V (VCC of the input signal, not of the

CC

ADATE209) or to an appropriate resistor to ground. For connection to LVDS, do not connect DAxT/DBxT/TERMxT. For

connection to CML signals, either leave DAxT/DBxT/TERMxT

open or connect DAxT/DBxT/TERMxT to the appropriate

V

CC/VDD

level.

DAxT, DBxT,

TERMxT

CABLE LOSS COMPENSATION/PEAKING CIRCUITRY

The ADATE209 has two different CLC/peaking modes: nominal

and boost. In nominal mode, a small amount of high frequency

energy is injected in the driver output signal to compensate for

high frequency losses in the test interface. In boost mode, a

much larger percentage of high frequency energy is injected in

the driver output signal. The two modes are controlled through

the CLCxEN signal.

Table 6.

CLCxEN CLC/Peaking Mode

Logic low Nominal

Logic high Boost

For applications using very short path lengths, very high fidelity

cables and connectors, and/or lower data rates, nominal mode

should be used. For applications using lower fidelity cables and

connectors (and often lower cost) and/or at higher data rates,

use boost mode.

CCTHERM

40Ω

THERM

GND

Figure 32. Thermal Diode String Schematic

ADATE209

07277-032

50Ω

DAx, DBx,

TERMx

DAxB, DBxB,

TERMxB

Figure 31. Input Termination Schematic Diagram

50Ω

07277-031

THERMAL DIODE STRING

Figure 32 shows a simplified schematic of the thermal diode

string. To use the diode string, connect VCCTHERM to 7.0 V

and measure the voltage at THERM. The nominal gain of the

thermal diode string is −4.7 mV/°C.

DEFAULT TEST CONDITIONS

Table 7 lists the default test conditions.

Table 7.

Name Default Test Condition

DB1/DB1B Logic high

DB2/DB2B Logic high

DA1T/DA2T/DB1T/DB2T 1.3 V

VHx 2.0 V

VLx 0.0 V

VTx 1.0 V

Rev. 0 | Page 14 of 16

Page 15

ADATE209

www.BDTIC.com/ADI

OUTLINE DIMENSIONS

8.10

8.00 SQ

A1 BALL

CORNER

7.90

TOP VIEW

3.275

REF

3.225

REF

6.00

BSC SQ

1.00

BSC

7654 231

BOTTOM VIEW

A

B

C

D

E

F

G

A1 BALL

CORNER

0.68

0.63

0.58

0.305 REF

0.100 REF

COPLANARITY

0.10

030408-A

*

1.60 MAX

1.21 NOM

DETAIL A

0.60

0.56

0.52

0.55

0.50

0.45

SEATING

PLANE

*

COMPLIANT TO JEDEC ST ANDARDS MO-192-ABB-1 W ITH

EXCEPTIO N TO PACKAGE HEI GHT.

DETAIL A

BALL DIAMET ER

Figure 33. 49-Ball Chip Scale Package Ball Grid Array [CSP_BGA]

(BC-49-4)

Dimensions shown in millimeters

ORDERING GUIDE

Model Temperature Range Package Description Package Option

ADATE209BBCZ1 −40°C to +85°C 49-Ball Chip Scale Package Ball Grid Array [CSP_BGA] BC-49-4

1

Z = RoHS Compliant Part.

Rev. 0 | Page 15 of 16

Page 16

ADATE209

www.BDTIC.com/ADI

NOTES

©2008 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D07277-0-5/08(0)

Rev. 0 | Page 16 of 16

Loading...

Loading...