Page 1

A

Mixed-Signal Front-End (MxFE™) Baseband

Transceiver for Broadband Applications

FEATURES

Receive path includes dual 10-bit analog-to-digital

converters with internal or external reference, 50 MSPS

and 80 MSPS versions

Transmit path includes dual 10-bit, 200 MSPS digital-to-

analog converters with 1×, 2×, or 4× interpolation and

programmable gain control

Internal clock distribution block includes a programmable

phase-locked loop and timing generation circuitry,

allowing single-reference clock operation

20-pin flexible I/O data interface allows various interleaved

or noninterleaved data transfers in half-duplex mode and

interleaved data transfers in full-duplex mode

Configurable through register programmability or

optionally limited programmability through mode pins

Independent Rx and Tx power-down control pins

64-lead LFCSP package (9 mm × 9 mm footprint)

3 configurable auxiliary converter pins

APPLICATIONS

Broadband access

Broadband LAN

Communications (modems)

GENERAL DESCRIPTION

The AD9861 is a member of the MxFE family—a group of

integrated converters for the communications market. The

AD9861 integrates dual 10-bit analog-to-digital converters

(ADC) and dual 10-bit digital-to-analog converters (TxDAC®).

Two speed grades are available, -50 and -80. The -50 is optimized for ADC sampling of 50 MSPS and less, while the -80 is

optimized for ADC sample rates between 50 MSPS and 80 MSPS.

The dual TxDACs operate at speeds up to 200 MHz and

include a bypassable 2× or 4× interpolation filter. Three

auxiliary converters are also available to provide required

system level control voltages or to monitor system signals. The

AD9861 is optimized for high performance, low power, small

form factor, and to provide a cost-effective solution for the

broadband communication market.

The AD9861 uses a single input clock pin (CLKIN) to generate

all system clocks. The ADC and TxDAC clocks are generated

within a timing generation block that provides user programmable options such as divide circuits, PLL multipliers, and switches.

A flexible, bidirectional 20-bit I/O bus accommodates a variety

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

AD9861

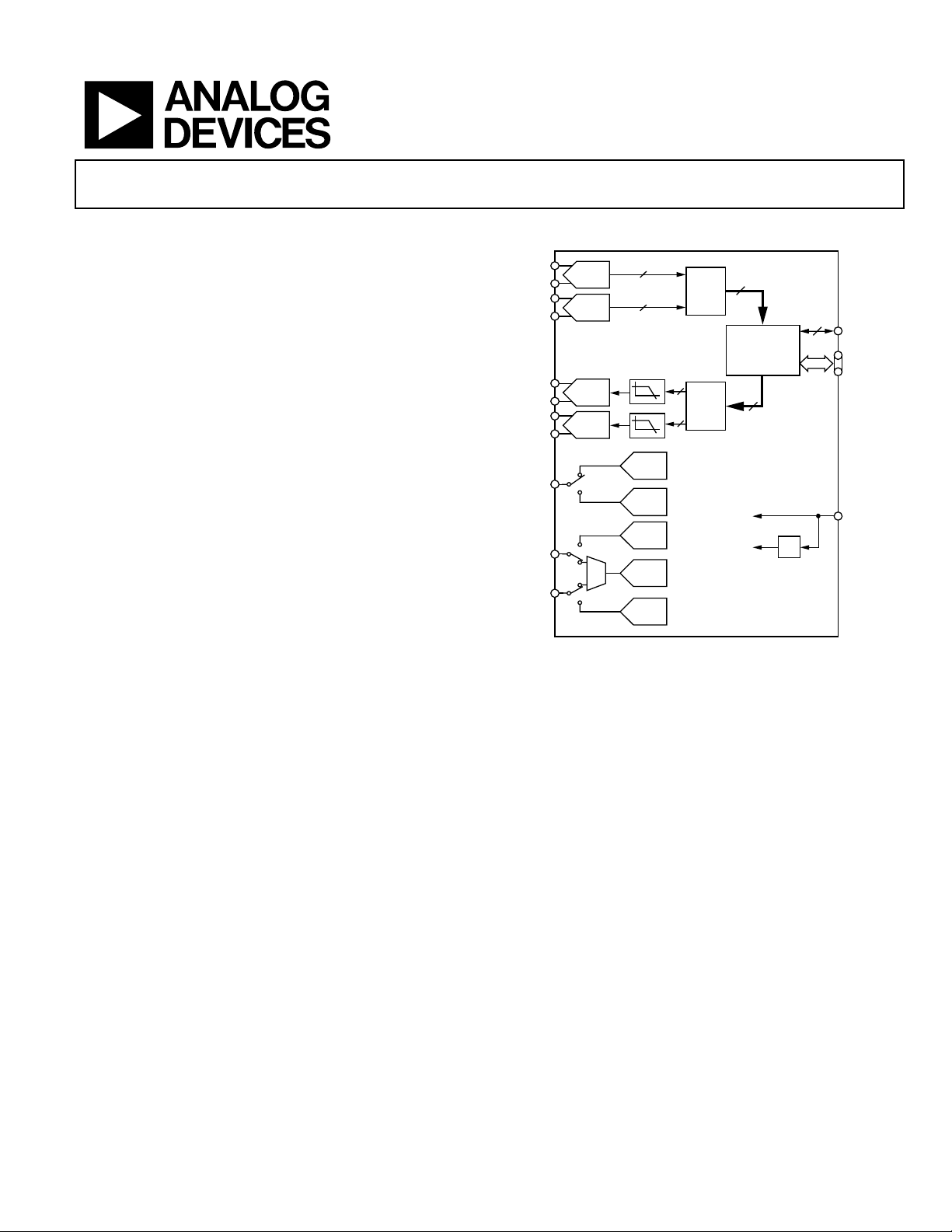

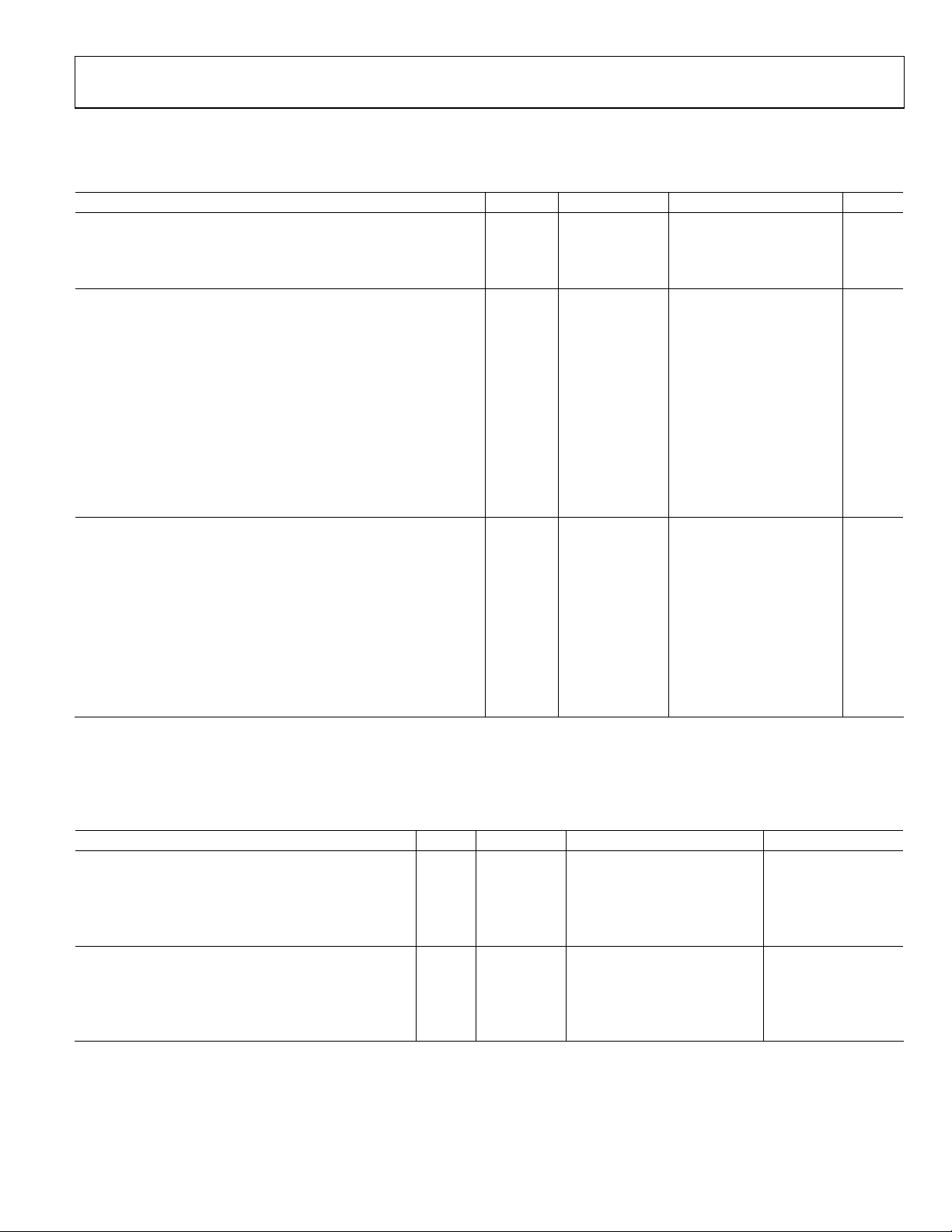

FUNCTIONAL BLOCK DIAGRAM

VIN+A

VIN–A

VIN+B

VIN–B

IOUT+

IOUT–A

IOUT+B

IOUT–B

of custom digital back ends or open market DSPs.

In half-duplex systems, the interface supports 20-bit parallel

transfers or 10-bit interleaved transfers. In full-duplex systems,

the interface supports an interleaved 10-bit ADC bus and an

interleaved 10-bit TxDAC bus. The flexible I/O bus reduces pin

count and, therefore, reduces the required package size on the

AD9861 and the device to which it connects.

The AD9861 can use either mode pins or a serial programmable interface (SPI) to configure the interface bus, operate the

ADC in a low power mode, configure the TxDAC interpolation

rate, and control ADC and TxDAC power-down. The SPI

provides more programmable options for both the TxDAC path

(for example, coarse and fine gain control and offset control for

channel matching) and the ADC path (for example, the internal

duty cycle stabilizer, and twos complement data format).

The AD9861 is packaged in a 64-lead LFCSP (low profile, fine

pitched, chip scale package). The 64-lead LFCSP footprint is

only 9 mm × 9 mm, and is less than 0.9 mm high, fitting into

tightly spaced applications such as PCMCIA cards

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2003 Analog Devices, Inc. All rights reserved.

ADC

ADC

DAC

DAC

LOW-PASS

INTERPOLATION

FILTER

AUX

ADC

AUX

DAC

AUX

DAC

AUX

ADC

AUX

DAC

DATA

MUX

AND

LATCH

DATA

LATCH

AND

DEMUX

DAC CLOCK PLL

Rx DATA

I/O

INTERFACE

CONFIGURATION

BLOCK

Tx DATA

AD9861

03606-0-001

Figure 1.

www.analog.com

I/O

INTERFACE

CONTROL

FLEXIBLE

I/O BUS

[0:19]

CLKINADC CLOCK

Page 2

AD9861

TABLE OF CONTENTS

Tx Path Specifications...................................................................... 3

Theory of Operation...................................................................... 22

Rx Path Specifications...................................................................... 4

Power Specifications......................................................................... 5

Digital Specifications........................................................................ 5

Timing Specifications....................................................................... 6

Absolute Maximum Ratings............................................................ 7

ESD Caution.................................................................................. 7

Pin Configuration and Pin Function Descriptions...................... 8

Typical Performance Characteristics ........................................... 10

Te r m in o l o g y .................................................................................... 21

REVISION HISTORY

Revision 0: Initial Version

System Block ............................................................................... 22

Rx Path Block.............................................................................. 22

Tx Path Block.............................................................................. 24

Auxiliary Converters.................................................................. 27

Digital Block................................................................................ 30

Programmable Registers............................................................ 42

Clock Distribution Block .......................................................... 45

Outline Dimensions....................................................................... 49

Ordering Guide .......................................................................... 50

Rev. 0 | Page 2 of 52

Page 3

AD9861

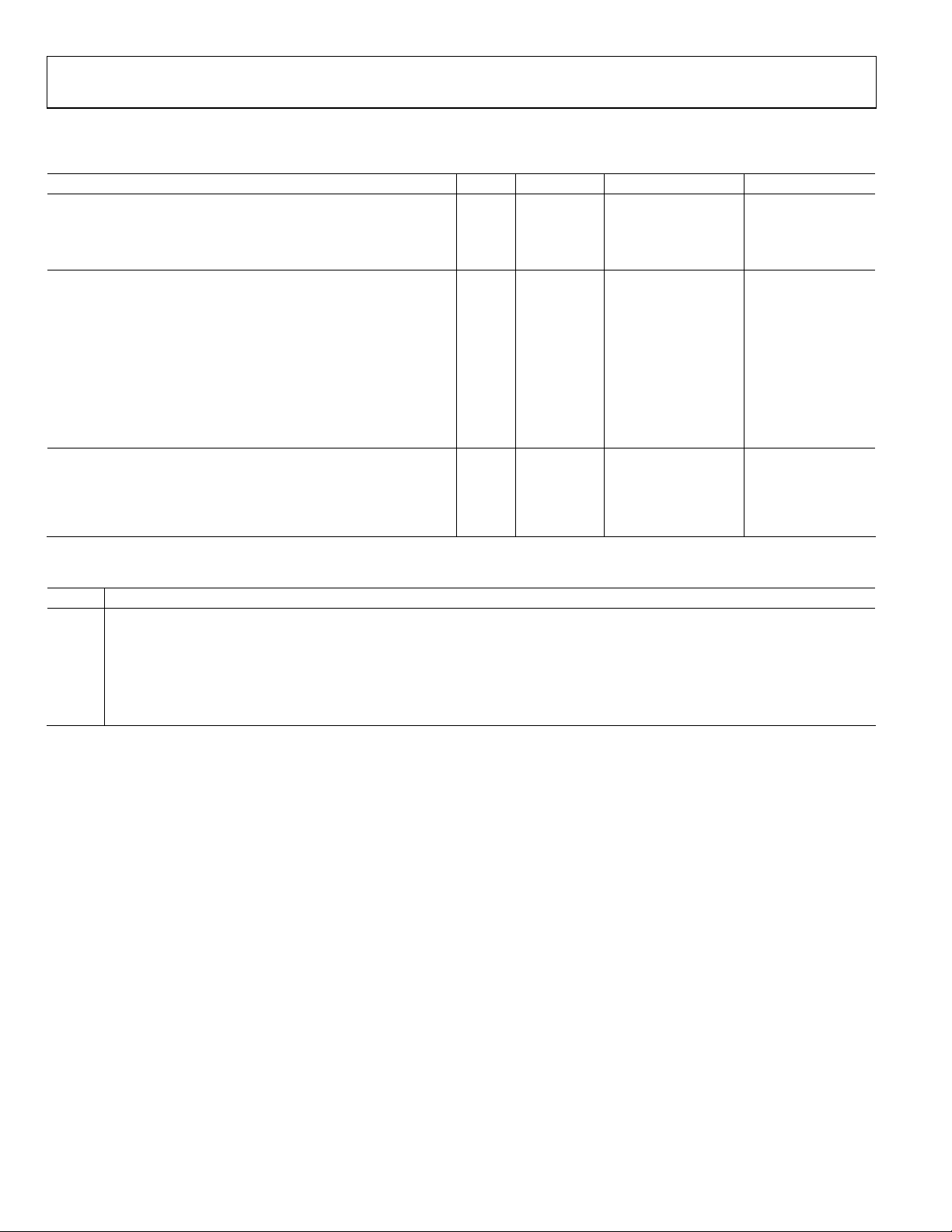

Tx PATH SPECIFICATIONS

Table 1. AD9861-50 and AD9861-80

= 200 MSPS; 4× interpolation; R

F

DAC

unless otherwise noted

Parameter Temp Test Level Min Typ Max Unit

Tx PATH GENERAL

Resolution Full IV 10 Bits

Maximum DAC Update Rate Full IV 200 MHz

Maximum Full-Scale Output Current Full IV 20 mA

Full-Scale Error Full V 1%

Gain Mismatch Error 25°C IV –3.5 +3.5 % FS

Offset Mismatch Error Full IV –0.1 +0.1 % FS

Reference Voltage Full V 1.23 V

Output Capacitance Full V 5 pF

Phase Noise (1 kHz Offset, 6 MHz Tone) 25°C V –115 dBc/Hz

Output Voltage Compliance Range Full IV –1.0 +1.0 V

TxPGA Gain Range Full V 20 dB

TxPGA Step Size Full V 0.10 dB

Tx PATH DYNAMIC PERFORMANCE

(I

= 20 mA; F

OUTFS

= 1 MHz)

OUT

SNR Full IV 60.2 60.8 dB

SINAD Full IV 59.7 60.7 dB

THD Full IV −77.5 −65.8 dBc

SFDR, Wideband (DC to Nyquist) Full IV 64.6 76.0 dBc

SFDR, Narrowband (1 MHz Window) Full IV 72.5 81.0 dBc

1

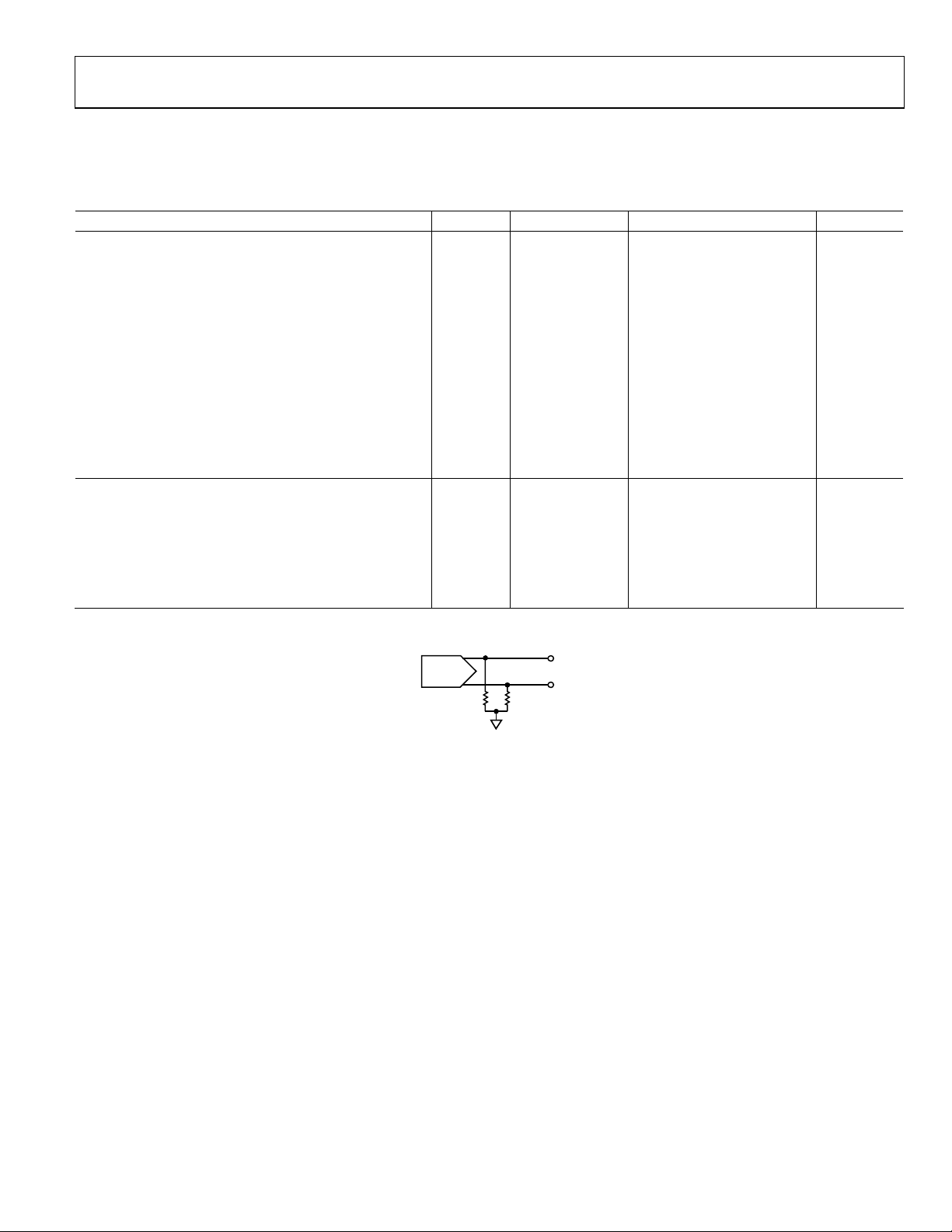

See Figure 2 for description of the TxDAC termination scheme.

= 4.02 kΩ; differential load resistance of 100 Ω1; TxPGA = 20 dB, AVDD = DVDD = 3.3 V,

SET

TxDAC

50Ω 50Ω

03606-0-030

Figure 2. Diagram Showing Termination of 100 Ω Differential

Load for Some TxDAC Measurements

Rev. 0 | Page 3 of 52

Page 4

AD9861

Rx PATH SPECIFICATIONS

Table 2. AD9861-50 and AD9861-80

= 50 MSPS for the AD9861-50, 80 MSPS for the AD9861-80; internal reference; differential analog inputs,

F

ADC

ADC_AVDD = DVDD = 3.3V, unless otherwise noted

Parameter Temp Test Level Min Typ Max Unit

Rx PATH GENERAL

Resolution Full V 10 Bits

Maximum ADC Sample Rate Full IV 50/80 MSPS

Gain Mismatch Error Full V

Offset Mismatch Error Full V

Reference Voltage Full V 1.0 V

Reference Voltage (REFT–REFB) Error Full IV –30

Input Resistance (Differential) Full V 2 kΩ

Input Capacitance Full V 5 pF

Input Bandwidth Full V 30 MHz

Differential Analog Input Voltage Range Full V 2 V p-p differential

Rx PATH DC ACCURACY

Integral Nonlinearity (INL) 25°C V

Differential Nonlinearity (DNL) 25°C V

Aperature Delay 25°C V 2.0 ns

Aperature Uncertainty (Jitter) 25°C V 1.2 ps rms

Input Referred Noise 25°C V 450 uV

AD9861-50 Rx PATH DYNAMIC PERFORMANCE

(V

= –0.5 dBFS; FIN = 10 MHz)

IN

SNR Full IV 55.5 60 dBc

SINAD Full IV 55.6 60 dBc

SINAD 25°C IV 58.5 60 dBc

THD (Second to Ninth Harmonics) Full IV −71.5 −64.6 dBc

SFDR, Wideband (DC to Nyquist) Full IV 65.7 73.5 dBc

Crosstalk between ADC Inputs Full V 80 dB

AD9861-80 Rx PATH DYNAMIC PERFORMANCE

(V

= –0.5 dBFS; FIN = 10 MHz)

IN

SNR Full IV 55.4 59.5 dBc

SINAD Full IV 52.7 59.0 dBc

THD (Second to Ninth Harmonics) Full IV −67 dBc

SFDR, Wideband (DC to Nyquist) Full IV 67 dBc

Crosstalk between ADC Inputs Full V 80 dB

±0.2

±0.1

±6

±0.75

±0.75

% FS

% FS

+30 mV

LSB

LSB

Rev. 0 | Page 4 of 52

Page 5

AD9861

POWER SPECIFICATIONS

Table 3. AD9861-50 and AD9861-80

Analog and digital supplies = 3.3 V; F

Parameter Temp Test Level Min Typ Max Unit

POWER SUPPLY RANGE

Analog Supply Voltage (AVDD) Full IV 2.7 3.6 V

Digital Supply Voltage (DVDD) Full IV 2.7 3.6 V

Driver Supply Voltage (DRVDD)

ANALOG SUPPLY CURRENTS

TxPath (20 mA Full-Scale Outputs) Full V 70 mA

TxPath (2 mA Full-Scale Outputs) Full V 20 mA

Rx Path (-80, at 80 MSPS) Full V 165 mA

RxPath (-80, at 40 MSPS, Low Power Mode) Full V 82 mA

RxPath (-80, at 20 MSPS, Ultralow Power Mode) Full V 35 mA

Rx Path (-50, at 50 MSPS) Full V 103 mA

RxPath (-50, at 50 MSPS, Low Power Mode) Full V 69 mA

RxPath (-50, at 16 MSPS, Ultralow Power Mode) Full V 28 mA

TxPath, Power-Down Mode Full V 2 mA

RxPath, Power-Down Mode Full V 5 mA

PLL Full V 12 mA

DIGITAL SUPPLY CURRENTS

TxPath, 1× Interpolation,

50 MSPS DAC Update for Both DACs,

Half-Duplex 24 Mode

TxPath, 2× Interpolation,

100 MSPS DAC Update for Both DACs,

Half-Duplex 24 Mode

TxPath, 4× Interpolation,

200 MSPS DAC Update for Both DACs,

Half-Duplex 24 Mode

RxPath Digital, Half-Duplex 24 Mode Full V 15 mA

= 50 MHz; PLL 4× setting; normal timing mode

CLKIN

Full IV 2.7 3.6 V

Full V 20 mA

Full V 50 mA

Full V 80 mA

DIGITAL SPECIFICATIONS

Table 4. AD9861-50 and AD9861-80

Parameter Temp Test Level Min Typ Max Unit

LOGIC LEVELS

Input Logic High Voltage, V

Input Logic Low Voltage, V

Output Logic High Voltage, VOH (1 mA Load) Full IV DRVDD – 0.6 V

Output Logic Low Voltage, VOL (1 mA Load) Full IV 0.4 V

DIGITAL PIN

Input Leakage Current Full IV 12 µA

Input Capacitance Full IV 3 pF

Minimum RESET Low Pulse Width Full IV 5 Input Clock Cycles

Digital Output Rise/Fall Time Full IV 2.8 4 ns

IH

IL

Full IV DRVDD – 0.7 V

Full IV 0.4 V

Rev. 0 | Page 5 of 52

Page 6

AD9861

TIMING SPECIFICATIONS

Table 5. AD9861-50 and AD9861-80

Parameter Temp Test Level Min Typ Max Unit

INPUT CLOCK

CLKIN Clock Rate (PLL Bypassed) Full IV 1 200 MHz

PLL Input Frequency Full IV 16 200 MHz

PLL Ouput Frequency Full IV 32 350 MHz

TxPATH DATA

Setup Time (HD20 Mode, Time Required Before Data Latching

Edge)

Hold Time (HD20 Mode, Time Required After Data Latching

Edge)

Latency 1× Interpolation (data in until peak output response) Full V 7 DAC Clock Cycles

Latency 2× Interpolation (data in until peak output response) Full V 35 DAC Clock Cycles

Latency 4× Interpolation (data in until peak output response) Full V 83 DAC Clock Cycles

RxPATH DATA

Output Delay (HD20 Mode, tOD) Full V –1.5

Latency Full V 5 ADC Clock Cycles

Table 6. Explanation of Test Levels

Level Description

I 100% production tested.

II

III Sample tested only.

IV Parameter is guaranteed by design and characterization testing.

V Parameter is a typical value only.

VI

100% production tested at 25°C and guaranteed by design and characterization at specified temperatures.

100% production tested at 25°C and guaranteed by design and characterization for industrial temperature range.

Full V 5

Full V –1.5

ns (see Clock

Distribution Block

section)

ns (see Clock

Distribution Block

section)

ns (see Clock

Distribution Block

section)

Rev. 0 | Page 6 of 52

Page 7

AD9861

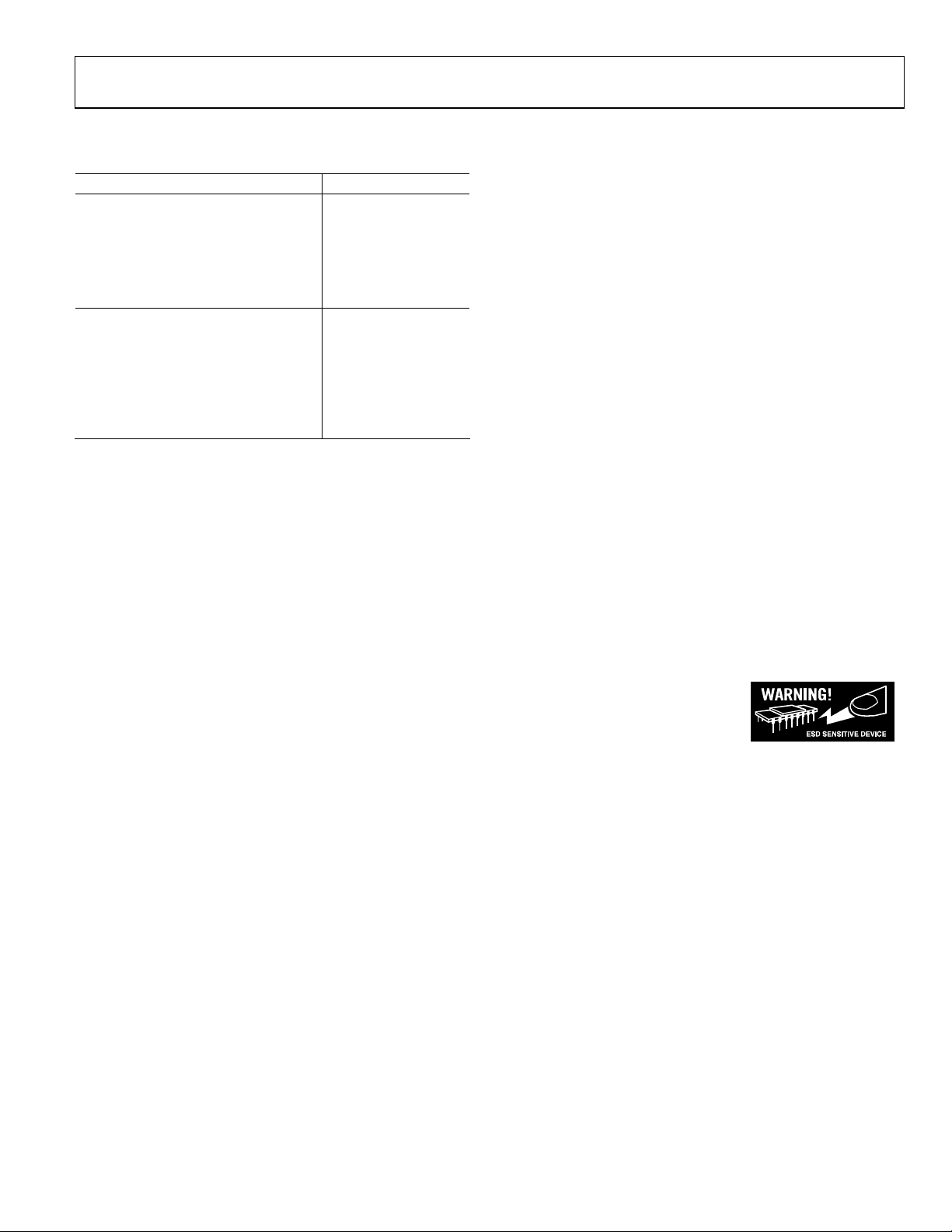

ABSOLUTE MAXIMUM RATINGS

Table 7.

Parameter Rating

Electrical

AVDD Voltage 3.9 V max

DRVDD Voltage 3.9 V max

Analog Input Voltage –0.3 V to AVDD + 0.3 V

Digital Input Voltage –0.3 V to DVDD – 0.3 V

Digital Output Current 5 mA max

Environmental

Operating Temperature Range

(Ambient)

Maximum Junction Temperature

Lead Temperature (Soldering, 10 sec)

Storage Temperature Range

(Ambient)

–40°C to +85°C

150°C

300°C

–65°C to +150°C

Stresses above those listed under the Absolute Maximum

Ratings may cause permanent damage to the device. This is a

stress rating only; functional operation of the device at these or

any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Thermal Resistance

64-lead LFCSP (4-layer board):

= 24.2 (paddle soldered to ground plan, 0 LPM Air)

θ

JA

= 30.8 (paddle not soldered to ground plan, 0 LPM Air)

θ

JA

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the

human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. 0 | Page 7 of 52

Page 8

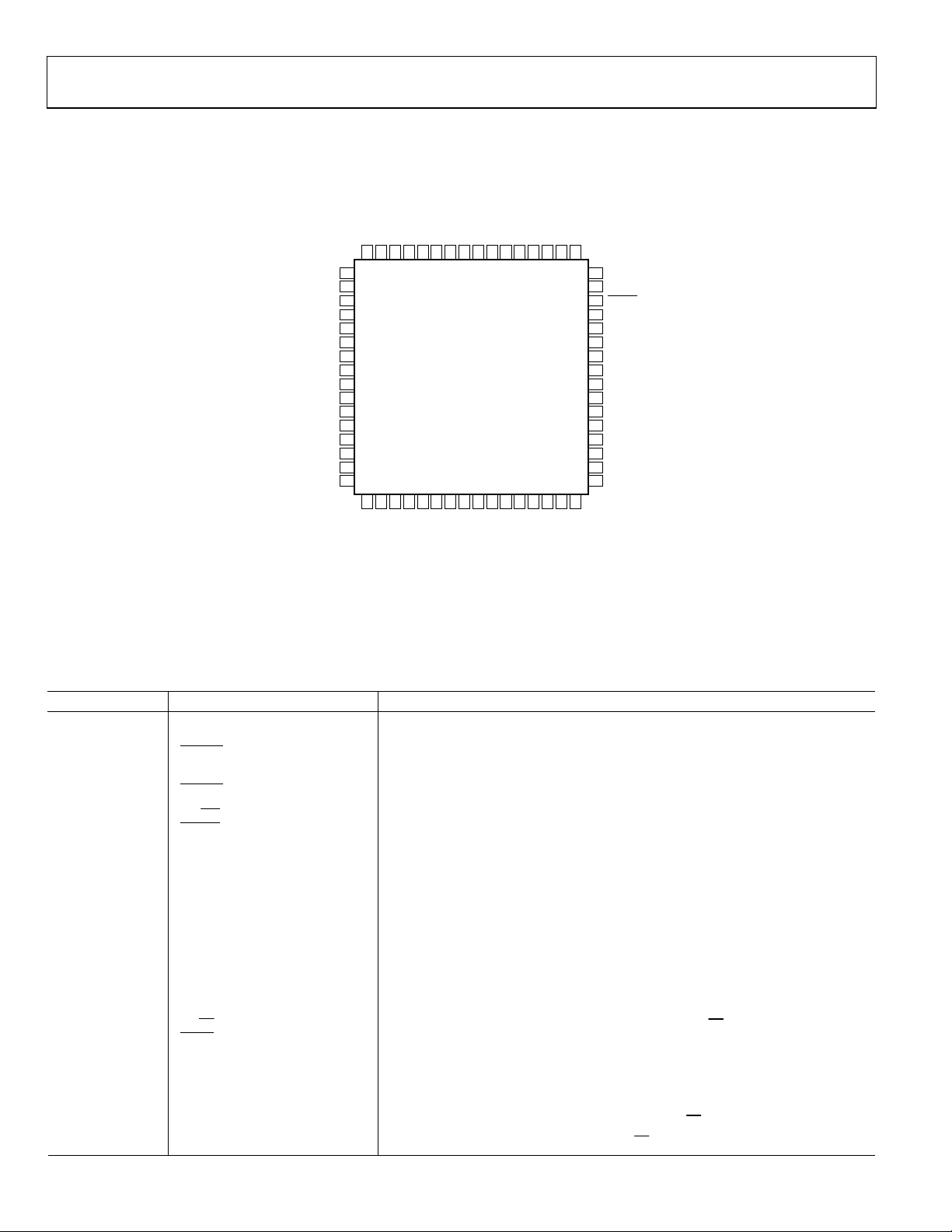

AD9861

PIN CONFIGURATION AND PIN FUNCTION DESCRIPTIONS

SPI_DIO

SPI_CLK

SPI_SDO/AUX_SPI_SDO

ADC_LO_PWR/AUX_SPI_CS

DVDD

DVSS

AVDD

IOUT–A

IOUT+A

AGND

REFIO

FSADJ

AGND

IOUT+B

IOUT–B

AVDD

SPI_CS64TxPWRDWN63RxPWRDWN62ADC_AVDD61REFT60ADC_AVSS59VIN+A58VIN–A57VREF56VIN–B55VIN+B54ADC_AVSS53REFB52ADC_AVDD51PLL_AVDD50PLL_AVSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

18U919U820U721U622U523U424U325U226U127U028

IFACE217IFACE3

AD9861

TOP VIEW

(Not to Scale)

Figure 3. Pin Configuration

30

31

DRVDD

AUX_DACA/AUX_ADCA229AUX_DACB/AUX_ADCA1

49

CLKIN

48

AUXADC_REF

47

46

RESET

AUX_DACC/AUX_ADCB

45

L0

44

43

L1

L2

42

L3

41

40

L4

L5

39

L6

38

37

L7

L8

36

L9

35

34

AUX_SPI_CLK

IFACE1

33

32

DRVSS

03606-0-019

Table 8. Pin Function Descriptions

Pin No. Name

1 SPI_DIO

2 SPI_CLK

3 SPI_SDO/AUXSPI_SDO

1

(

Interp1)

(

Interp0)

FD/HD)

(

Description

SPI: Serial Port Data Input.

No SPI: Tx Interpolation Pin, MSB.

SPI: Serial Port Shift Clock.

No SPI: Tx Interpolation Pin, LSB.

SPI: 4-Wire Serial Port Data Output/Data Output Pin for AuxSPI.

No SPI: Configures Full-Duplex or Half-Duplex Mode.

2, 3

4 ADC_LO_PWR/AUX_SPI_CS ADC Low Power Mode Enable. Defined at power-up. CS for AuxSPI.

5, 31 DVDD Digital Supply.

6, 32 DVSS Digital Ground.

7, 16, 50, 51, 61 AVDD Analog Supply.

8, 9 IOUT–A, IOUT+A DAC A Differential Output.

10, 13, 49, 53, 59 AGND, AVSS Analog Ground.

11 REFIO Tx DAC Band Gap Reference Decoupling Pin.

12 FSADJ Tx DAC Full-Scale Adjust Pin.

14, 15 IOUT+B, IOUT−B DAC B Differential Output.

17 IFACE2

(10/20)

SPI: Buffered CLKIN. Can be configured as system clock output.

No SPI: For FD: Buffered CLKIN; For HD20 or HD10 : 10/

20 Configuration Pin.

18 IFACE3 Clock Output.

19–28 U9–U0 Upper Data Bit 9 to Upper Data Bit 0.

29 AUX1 Configurable as either AuxADC_A2 or AuxDAC_A.

30 AUX2 Configurable as either AuxADC_A1 or AuxDAC_B.

33 IFACE1

SPI: For FD: TxSYNC; For HD20, HD10, or Clone: Tx/Rx.

No SPI: FD >> TxSYNC; HD20 or HD10: Tx/Rx.

Rev. 0 | Page 8 of 52

Page 9

AD9861

Pin No. Name

1

Description

2, 3

34 AUX_SPI_CLK CLK for AuxSPI.

35–44 L9–L0 Lower Data Bit 9 to Lower Data Bit 0.

45 AUX3 Configurable as either AuxADC_B or AuxDAC_C.

46

RESET

Chip Reset When Low.

47 AUX_ADC_REF Decoupling for AuxADC On-Chip Reference.

48 CLKIN Clock Input.

52 REFB ADC Bottom Reference.

54, 55 VIN+B, VIN−B ADC B Differential Input.

56 VREF ADC Band Gap Reference.

57, 58 VIN−A, VIN+A ADC A Differential Input.

60 REFT ADC Top Reference.

62 RxPwrDwn Rx Analog Power-Down Control.

63 TxPwrDwn Tx Analog Power-Down Control.

64 SPI_CS

1

Underlined pin names and descriptions apply when the device is configured without a serial port interface, referred to as no SPI mode.

2

Pin function depends if the serial port is used to configure the AD9861 (called SPI mode) or if mode pins are used to configure the AD9861 (called No SPI mode). The

differences are indicated by the SPI and No SPI labels in the description column.

3

Some pin descriptions depend on the interface configuration, full-duplex (FD), half-duplex interleaved data (HD10), half-duplex parallel data (HD20), and a half-duplex

interface similar to the AD9860 and AD9862 data interface called clone mode (Clone). Clone mode requires a serial port interface.

SPI: Serial Port Chip Select. At power-up or reset, this must be high.

No SPI: Tie low to disable SPI and use mode pins. This pin must be tied low.

Rev. 0 | Page 9 of 52

Page 10

AD9861

TYPICAL PERFORMANCE CHARACTERISTICS

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0510

FREQUENCY (MHz)

15 20 25

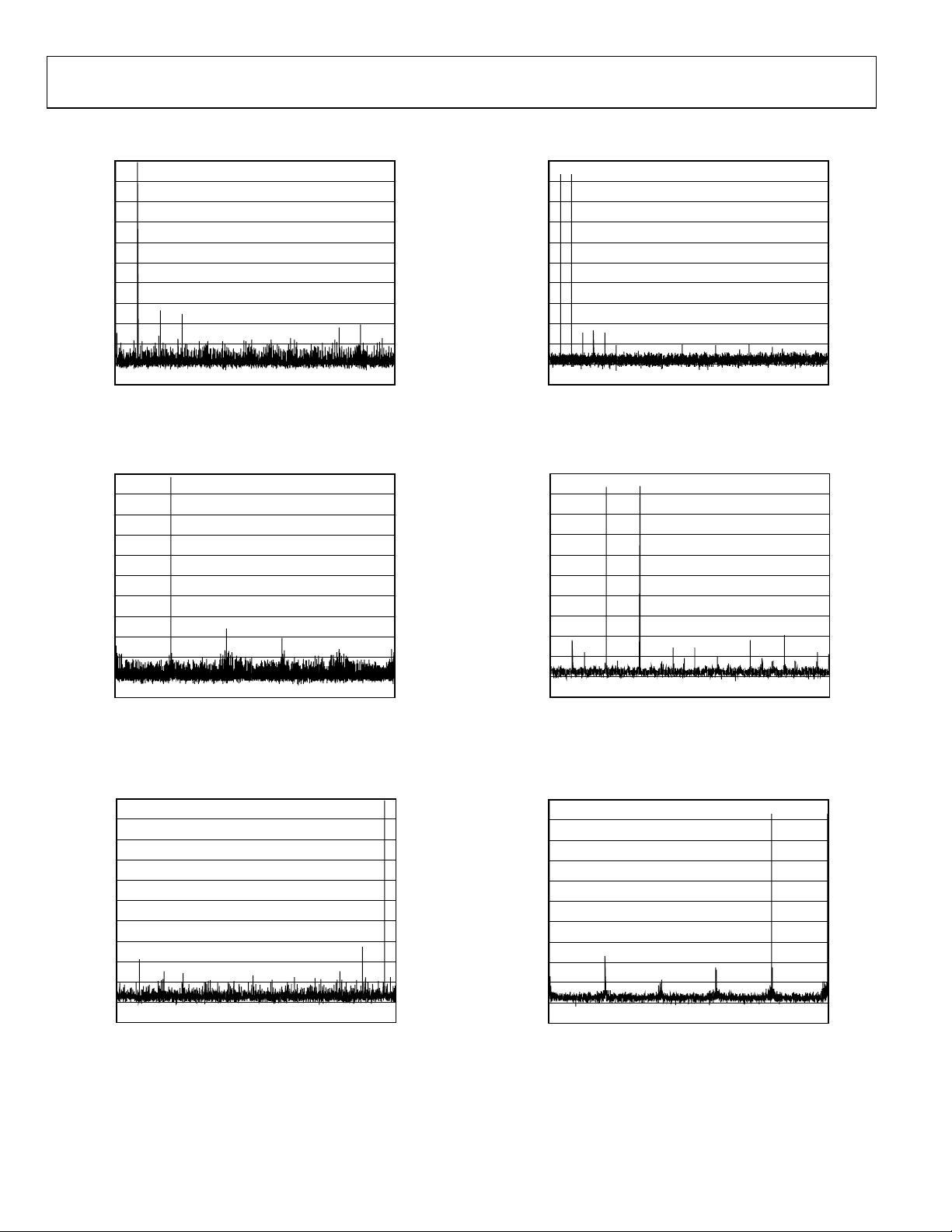

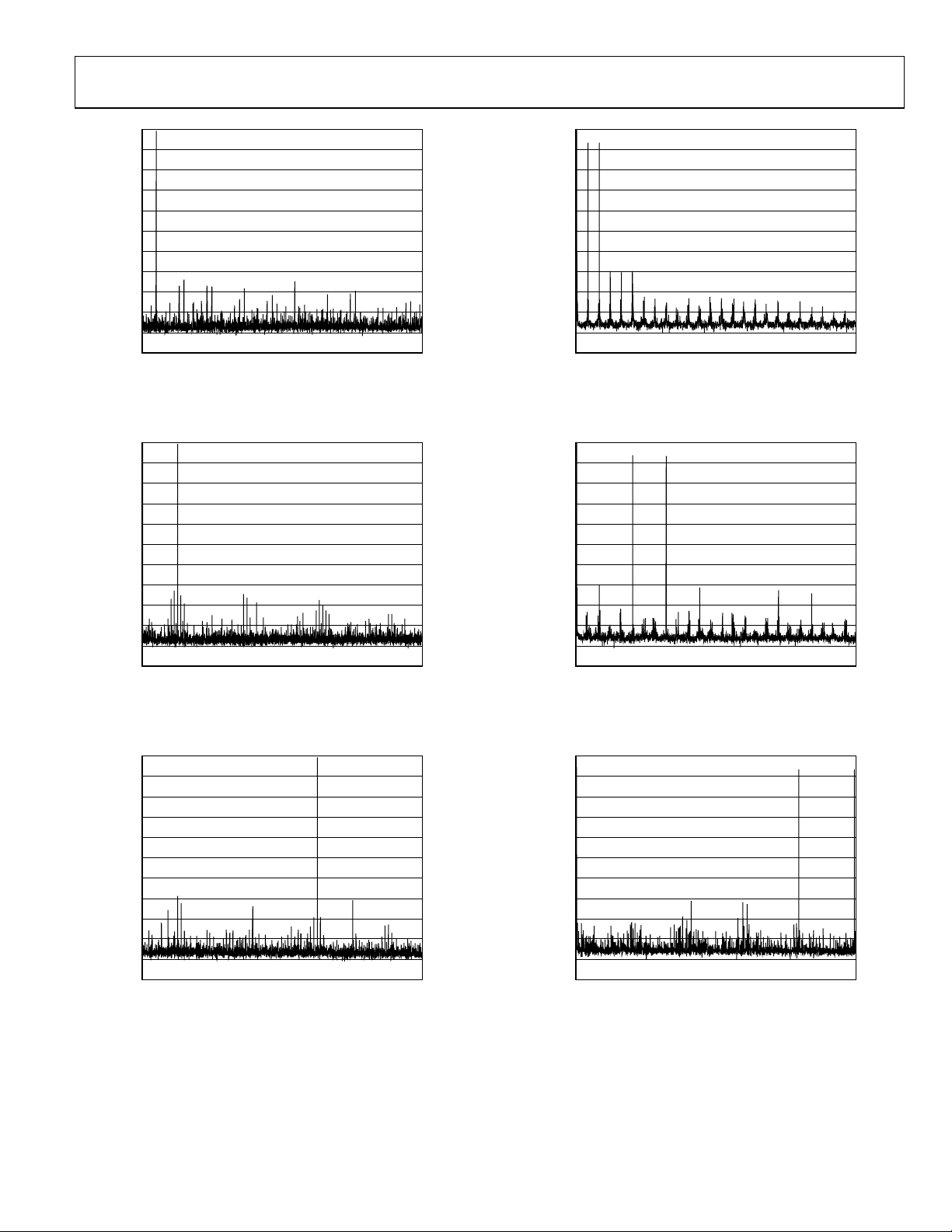

Figure 4. AD9861-50 Rx Path Single-Tone FFT of Rx Channel B Path

Digitizing 2 MHz Tone

03606-0-031

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0510

FREQUENCY (MHz)

15 20 25

Figure 7. AD9861-50 Rx Path Dual-Tone FFT of Rx Channel A Path

Digitizing 1 MHz and 2 MHz Tones

03606-0-032

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0510

FREQUENCY (MHz)

15 20 25

Figure 5. AD9861-50 Rx Path Single-Tone FFT of Rx Channel B Path

Digitizing 5 MHz Tone

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0510

FREQUENCY (MHz)

15 20 25

Figure 6. AD9861-50 Rx Path Single-Tone FFT of Rx Channel B Path

Digitizing 24 MHz Tone

03606-0-033

03606-0-035

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0510

FREQUENCY (MHz)

15 20 25

Figure 8. AD9861-50 Rx Path Dual-Tone FFT of Rx Channel A Path

Digitizing 5 MHz and 8 MHz Tones

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0510

FREQUENCY (MHz)

15 20 25

Figure 9. AD9861-50 Rx Path Dual-Tone FFT of Rx Channel A Path

Digitizing 20 MHz and 25 MHz Tones

03606-0-034

03606-0-036

Rev. 0 | Page 10 of 52

Page 11

AD9861

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0510

FREQUENCY (MHz)

15 20 25

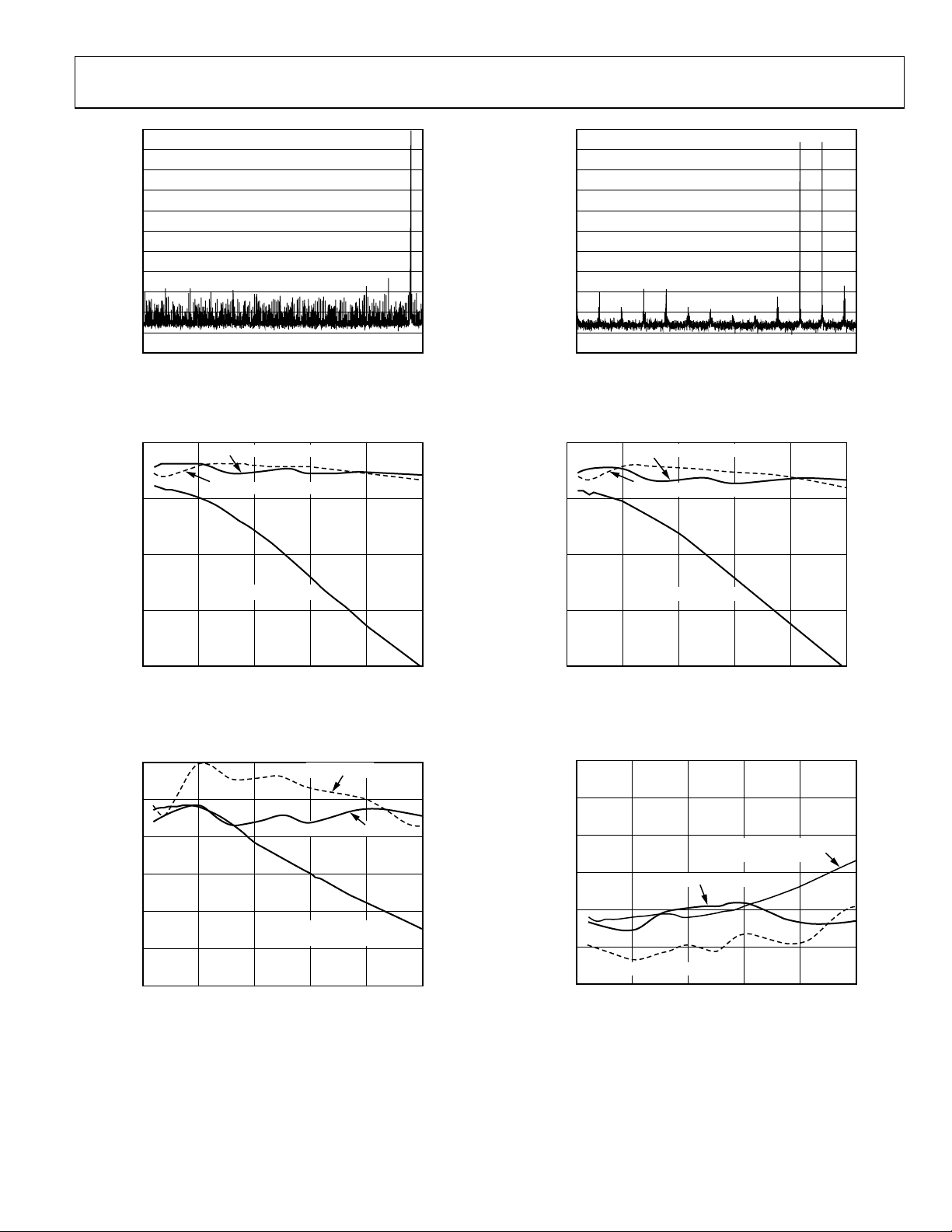

Figure 10. AD9861-50 Rx Path Single-Tone FFT of Rx Channel B Path

Digitizing 76 MHz Tone

62

59

56

SNR (dBc)

53

50

0510

NORMAL POWER @ 50MSPS

LOW POWER ADC @ 25MSPS

ULTRALOW POWER ADC

@ 16MSPS

INPUT FREQUENCY (MHz)

15 20 25

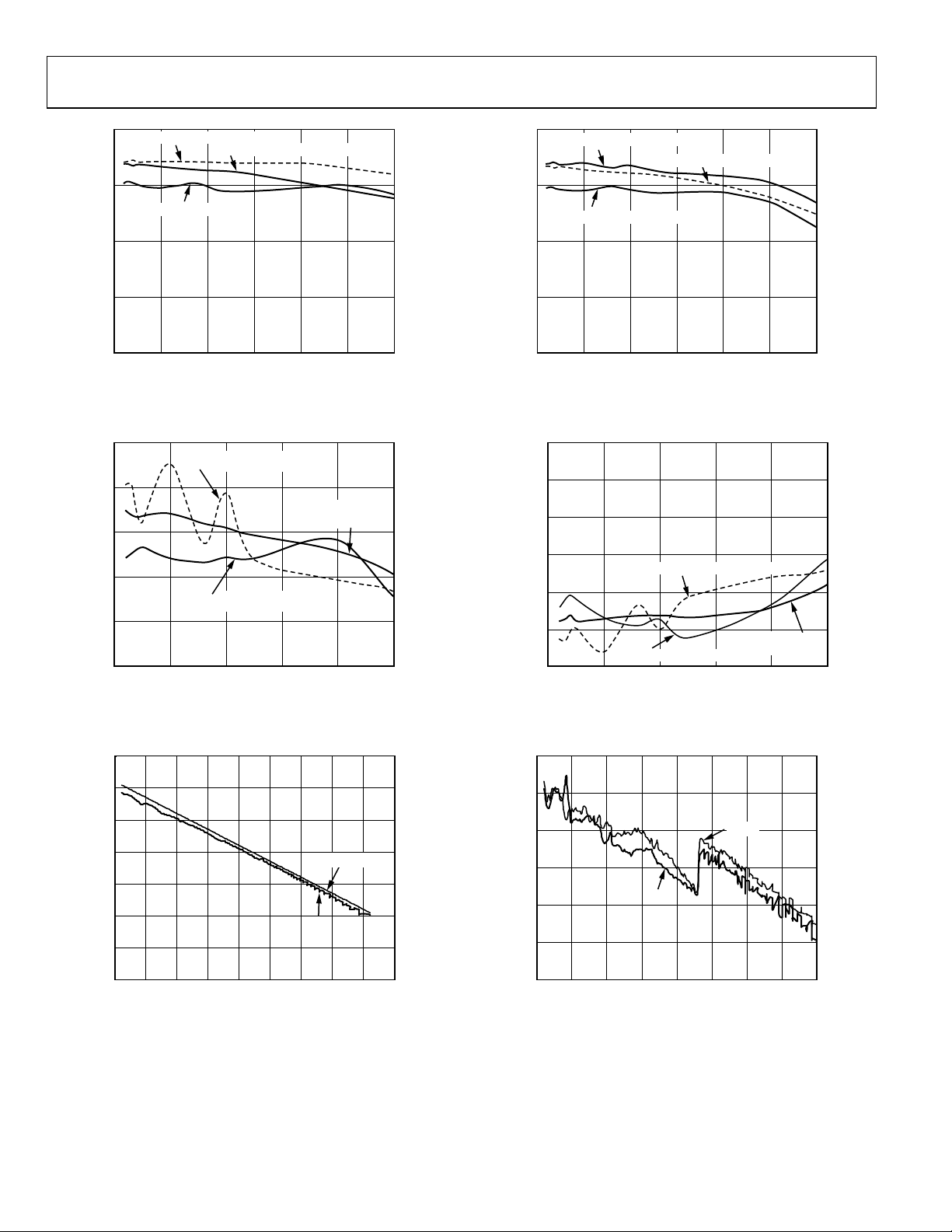

Figure 11. AD9861-50 Rx Path at 50 MSPS, 10 MHz Input Tone

SNR Performance vs. Input Frequency

03606-0-037

03606-0-039

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0510

FREQUENCY (MHz)

15 20 25

Figure 13. AD9861-50 Rx Path Dual-Tone FFT of Rx Channel A Path

Digitizing 70 MHz and 72 MHz Tones

62

59

56

SINAD (dBc)

53

50

0510

NORMAL POWER @ 50MSPS

LOW POWER ADC @ 25MSPS

ULTRALOW POWER ADC

@ 16MSPS

INPUT FREQUENCY (MHz)

15 20 25

Figure 14. AD9861-50 Rx Path at 50 MSPS, 10 MHz Input Tone

SINAD Performance vs. Input Frequency

10.0

9.8

9.6

9.4

9.2

9.0

8.8

8.6

8.4

8.2

8.0

03606-0-038

ENOB (Bits)

03606-0-040

80

75

70

65

SFDR (dBc)

60

55

50

0510

INPUT FREQUENCY (MHz)

LOW POWER ADC @ 25MSPS

NORMAL POWER @ 50MSPS

ULTRALOW POWER ADC

@ 16MSPS

15 20 25

Figure 12. AD9861-50 Rx Path at 50 MSPS, 10 MHz Input Tone

SFDR Performance vs. Input Frequency

03606-0-041

Rev. 0 | Page 11 of 52

–50

–55

–60

–65

THD (dBc)

–70

–75

–80

0510

NORMAL POWER @ 50MSPS

LOW POWER ADC @ 25MSPS

INPUT FREQUENCY (MHz)

ULTRALOW POWER ADC

@ 16MSPS

15 20 25

Figure 15. AD9861-50 Rx Path at 50 MSPS, 10 MHz Input Tone

THD Performance vs. Input Frequency

03606-0-042

Page 12

AD9861

70

60

50

40

30

SNR (dBc)

20

10

0

0 –5 –10 –15 –20 –25 –30 –35

INPUT AMPLITUDE (dBFS)

SNR

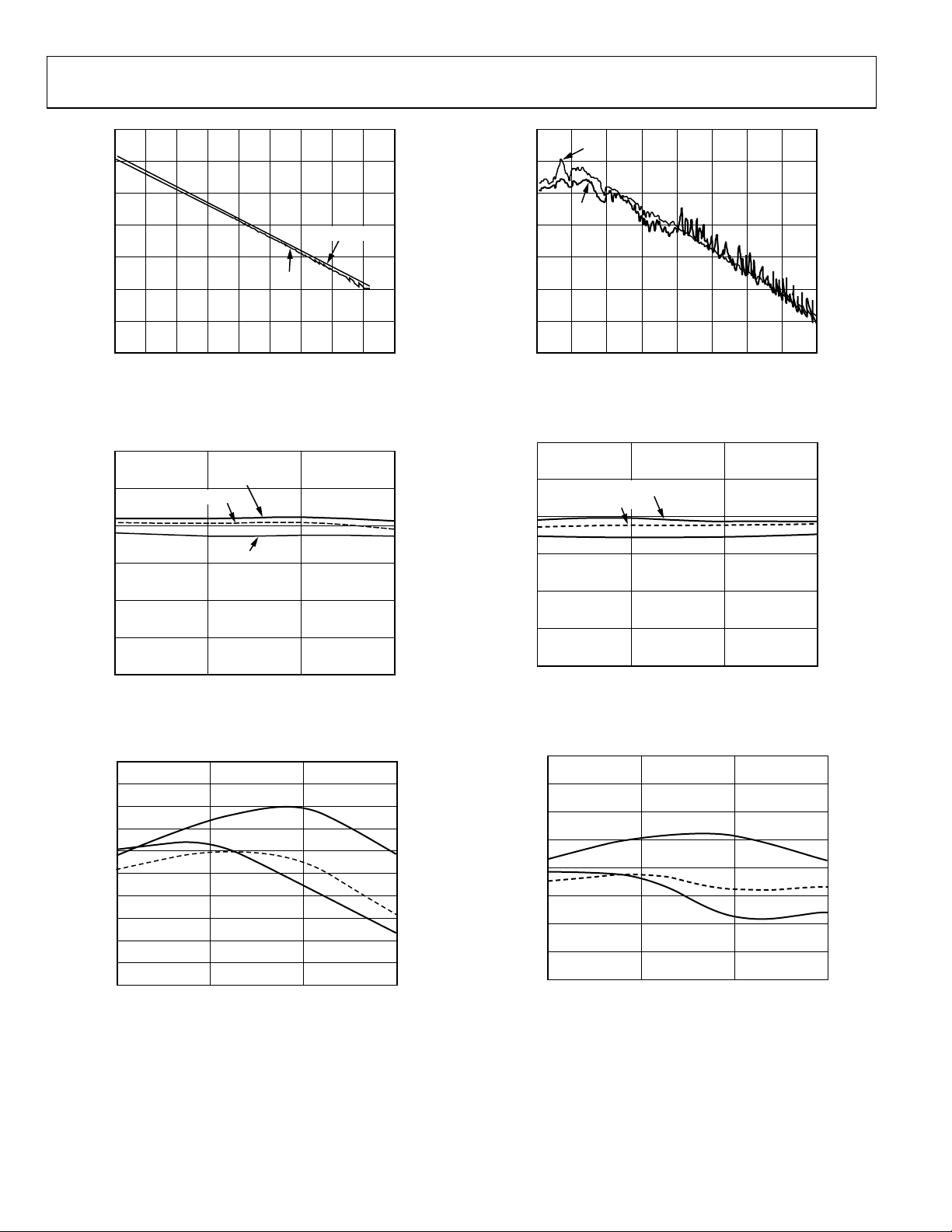

Figure 16. AD9861-50 Rx Path at 50 MSPS, 10 MHz Input Tone

SNR Performance vs. Input Amplitude

62

AVE (–40

°

AVE (+85

C)

°

C)

61

60

59

SNR (dBc)

58

57

56

2.7 3.0 3.3 3.6

AVE (+25°C)

ADC_AVDD VOLTAGE (V)

Figure 17. AD9861-50 Rx Path at 50 MSPS, 10 MHz Input Tone

SNR Performance vs. ADC_AVDD and Temperature

IDEAL SNR

–40

–45

03606-0-043

03606-0-045

90 –90

80

70

60

50

SFDR (dBFS)

40

30

20

SFDR

THD

0 –5 –10 –15 –20 –25 –30 –35

INPUT AMPLITUDE (dBFS)

Figure 19. AD9861-50 Rx Path at 50 MSPS, 10 MHz Input Tone

THD and SFDR Performance vs. Input Amplitude

62

61

60

59

SINAD (dBc)

58

57

56

2.7 3.0 3.3

AVE (–40°C)

AVE (+25°C)

AVE (+85°C)

ADC_AVDD VOLTAGE (V)

Figure 20. AD9861-50 Rx Path at 50 MSPS, 10 MHz Input Tone

SINAD Performance vs. ADC_AVDD and Temperature

–40

3.6

–80

–70

–60

–50

–40

–30

–20

10.0

9.9

9.8

9.7

9.6

9.5

9.4

9.3

9.2

9.1

9.0

THD (dBFS)

03606-0-044

ENOB (Bits)

03606-0-046

–70.0

–70.5

–71.0

–71.5

–72.0

–72.5

THD (dBc)

–73.0

–73.5

–74.0

–74.5

–75.0

3.6 3.3 3.0 2.7

INPUT AMPLITUDE (dBFS)

AVE (+25°C)

AVE (–40

AVE (+85

°

C)

°

Figure 18. AD9861-50 Rx Path Single-Tone THD Performance vs.

ADC_AVDD and Temperature

C)

03606-0-047

Rev. 0 | Page 12 of 52

70

71

72

73

74

SFDR (dBc)

75

76

77

78

3.6 3.3 3.0

INPUT AMPLITUDE (dBFS)

AVE (+85°C)

AVE (+25°C)

AVE (–40°C)

2.7

Figure 21. AD9861-50 Rx Path Single-Tone SFDR Performance vs.

ADC_AVDD and Temperature

03606-0-048

Page 13

AD9861

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0 5 10 15 20 25 30 35

FREQUENCY (MHz)

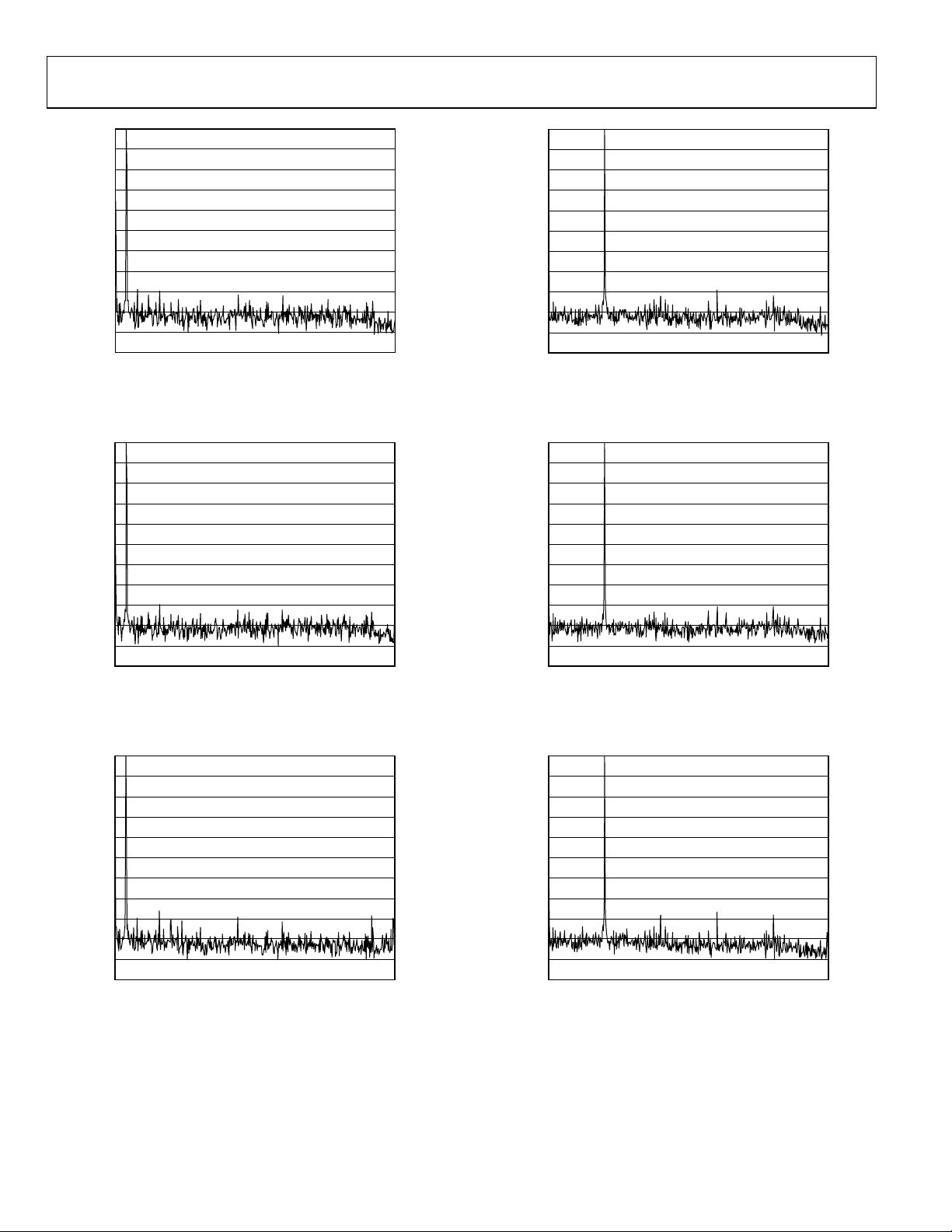

Figure 22. AD9861-80 Rx Path Single-Tone FFT of Rx Channel B Path

Digitizing 2 MHz Tone

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0 5 10 15 20 25 30 35

FREQUENCY (MHz)

Figure 23. AD9861-80 Rx Path Single-Tone FFT of Rx Channel B Path

Digitizing 5 MHz Tone

40

40

03606-0-049

03606-0-051

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0 5 10 15 20

FREQUENCY (MHz)

25

Figure 25. AD9861-80 Rx Path Dual-Tone FFT of Rx Channel A Path

Digitizing 1 MHz and 2 MHz Tones

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0 5 10 15 20

FREQUENCY (MHz)

25

Figure 26. AD9861-80 Rx Path Dual-Tone FFT of Rx Channel A Path

Digitizing 5 MHz and 8 MHz Tones

03606-0-050

03606-0-052

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0 5 10 15 20 25 30 35

FREQUENCY (MHz)

40

Figure 24. AD9861-80 Rx Path Single-Tone FFT of Rx Channel B Path

Digitizing 24 MHz Tone

03606-0-053

Rev. 0 | Page 13 of 52

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBFS)

–80

–90

–100

–110

0 5 10 15 20

FREQUENCY (MHz)

25

Figure 27. AD9861-80 Rx Path Dual-Tone FFT of Rx Channel A Path

Digitizing 20 MHz and 25 MHz Tones

03606-0-054

Page 14

AD9861

62

LOW POWER ADC @ 40MSPS

59

NORMAL POWER @ 80MSPS

56

SNR (dBc)

53

50

0 5 10 15 20

Figure 28. AD9861-80 Rx Path at 80 MSPS, 10 MHz Input Tone

SNR Performance vs. Input Frequency and Power Setting

ULTRALOW POWER ADC @ 16MSPS

INPUT FREQUENCY (MHz)

3025

03606-0-055

62 10.0

LOW POWER ADC @ 40MSPS

ULTRALOW POWER ADC @ 16MSPS

59

NORMAL POWER @ 80MSPS

56

SINAD (dBc)

53

50

0 5 10 15 20

INPUT FREQUENCY (MHz)

Figure 31. AD9861-80 Rx Path at 80 MSPS, 10 MHz Input Tone

SINAD Performance vs. Input Frequency and Power Setting

9.8

9.6

9.4

9.2

9.0

8.8

ENOB (Bits)

8.6

8.4

8.2

03606-0-056

8.0

3025

85

LOW POWER ADC @ 40MSPS

80

ULTRALOW POWER

75

70

SFDR (dBc)

NORMAL POWER @ 80MSPS

65

60

0 5 10 15 20

INPUT FREQUENCY (MHz)

ADC @ 16MSPS

Figure 29. AD9861-80 Rx Path at 80 MSPS, 10 MHz Input Tone

SFDR Performance vs. Input Frequency and Power Setting

70

60

50

40

30

SNR (dBc)

20

10

IDEAL SNR

SNR

25

03606-0-057

–50

–55

–60

–65

THD (dBc)

–70

–75

–80

0 5 10 15 20

LOW POWER ADC @ 40MSPS

NORMAL POWER @ 80MSPS

INPUT FREQUENCY (MHz)

ULTRALOW POWER

ADC @ 16MSPS

Figure 32. AD9861-80 Rx Path at 80 MSPS, 10 MHz Input Tone

THD Performance vs. Input Frequency and Power Setting

–80 80

–70

–60

–50

THD (dBFS)

–40

–30

THD

SFDR

25

70

60

50

40

30

03606-0-058

SFDR (dBFS)

0

0 –5 –10 –15 –20 –25 –30 –35

INPUT AMPLITUDE (dBFS)

–40

Figure 30. AD9861-80 Rx Path at 80 MSPS, 10 MHz Input Tone

SNR Performance vs. Input Amplitude

03606-0-059

–45

Rev. 0 | Page 14 of 52

–20

0 –5 –10 –15 –20 –25 –30 –35

INPUT AMPLITUDE (dBFS)

Figure 33. AD9861-80 Rx Path at 80 MSPS, 10 MHz Input Tone

THD Performance vs. Input Amplitude

–40

03606-0-060

20

Page 15

AD9861

62

61

60

59

SNR (dBc)

58

57

56

2.7 3.0 3.3 3.6

AVE (+85°C)

AVE (+25°C)

ADC_AVDD VOLTAGE (V)

AVE (–40°C)

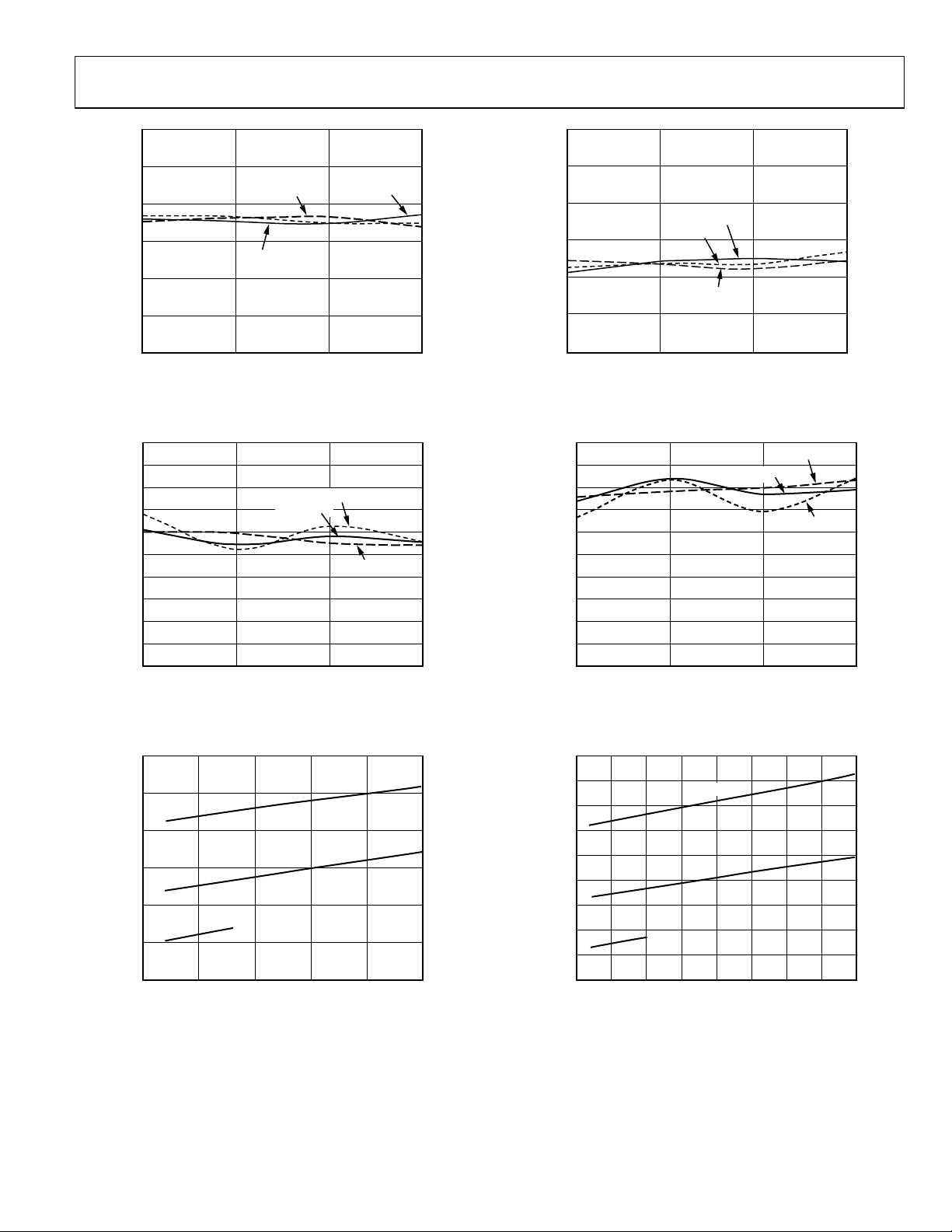

Figure 34. AD9861-80 Rx Path at 80 MSPS, 10 MHz Input Tone

SNR Performance vs. AVDD and Temperature

03606-0-065

62

61

60

59

SINAD (dBc)

58

57

56

2.7 3.0 3.3

AVE (+25°C)

ADC_AVDD VOLTAGE (V)

AVE (+85

AVE (–40

°

C)

°

C)

Figure 37. AD9861-80 Rx Path at 80 MSPS, 10 MHz Input Tone

SINAD Performance vs. AVDD and Temperature

3.6

10.0

9.9

9.8

9.7

9.6

9.5

9.4

9.3

9.2

9.1

9.0

ENOB (Bits)

03606-0-066

70

69

68

67

66

65

THD (dBc)

64

63

62

61

60

2.7 3.0 3.3 3.6

ADC_AVDD VOLTAGE (V)

AVE (+25°C)

AVE (–40°C)

AVE (+85°C)

Figure 35. AD9861-80 Rx Path at 80 MSPS, 10 MHz Input Tone

THD Performance vs. AVDD and Temperature

120

100

80

60

40

ADC AVDD CURRENT (mA)

20

0

04302010

ULP

LP

(MHz)

F

CLK

NORM

0

Figure 36. AD9861-50 ADC_AVDD Current vs. Sampling Rate for

Different ADC Power Levels

50

03606-0-061

03606-0-063

65

66

67

68

69

70

71

SFDR (dBc)

72

73

74

75

2.7 3.0 3.3 3.6

ADC_AVDD VOLTAGE (V)

AVE (+85°C)

AVE (–40°C)

AVE (+25°C)

Figure 38. AD9861-80 Rx Path at 80 MSPS, 10 MHz Input Tone

SFDR Performance vs. AVDD and Temperature

180

160

140

120

100

80

60

ADC AVDD CURRENT (mA)

40

20

0

ULP

0 40506070302010

F

CLK

NORM

LP

80

(MHz)

Figure 39. AD9861-80 ADC_AVDD Current vs. ADC Sampling Rate for

Different ADC Power Levels

03606-0-062

03606-0-064

Rev. 0 | Page 15 of 52

Page 16

AD9861

AMPLITUDE (dBc)

–100

–110

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

0 1015205

FREQUENCY (MHz)

Figure 40. AD9861 Tx Path 1 MHz Single-Tone Output FFT of Tx Path

with 20 mA Full-Scale Output into 33 Ω Differential Load

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBc)

–80

–90

–100

–110

01015205

FREQUENCY (MHz)

Figure 41. AD9861 Tx Path 1 MHz Single-Tone Output FFT of Tx Path

with 20 mA Full-Scale Output into 60 Ω Differential Load

25

25

03606-0-068

03606-0-070

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBc)

–80

–90

–100

–110

01015205

FREQUENCY (MHz)

25

Figure 43. AD9861 Tx Path 5 MHz Single-Tone Output FFT of Tx Path

with 20 mA Full-Scale Output into 33 Ω Differential Load

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBc)

–80

–90

–100

–110

01015205

FREQUENCY (MHz)

25

Figure 44. AD9861 Tx Path 5 MHz Single-Tone Output FFT of Tx Path

with 20 mA Full-Scale Output into 60 Ω Differential Load

03606-0-069

03606-0-071

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBc)

–80

–90

–100

–110

01015205

FREQUENCY (MHz)

25

Figure 42. AD9861 Tx Path 1 MHz Single-Tone Output FFT of Tx Path

with 2 mA Full-Scale Output into 600 Ω Differential Load

03606-0-072

Rev. 0 | Page 16 of 52

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dBc)

–80

–90

–100

–110

01015205

FREQUENCY (MHz)

25

Figure 45. AD9861 Tx Path 5 MHz Single-Tone Output FFT of Tx Path

with 2 mA Full-Scale Output into 600 Ω Differential Load

03606-0-073

Page 17

AD9861

–50

–50

–60

–70

THD (dBc)

–80

–90

–100

01015205

OUTPUT FREQUENCY (MHz)

25

Figure 46. AD9861 Tx Path THD vs. Output Frequency of Tx Path with

20 mA Full-Scale Output into 60 Ω Differential Load

62

61

60

59

SINAD (dBc)

58

03606-0-074

–60

–70

THD (dBc)

–80

–90

–100

01015205

OUTPUT FREQUENCY (MHz)

Figure 49. AD9861 Tx Path THD vs. Output Frequency of Tx Path

with 2 mA Full-Scale Output into 600 Ω Differential Load

62

61

60

59

SINAD (dBc)

58

25

03606-0-075

57

56

01015205

OUTPUT FREQUENCY (MHz)

25

03606-0-076

Figure 47. AD9861 Tx Path SINAD vs. Output Frequency of Tx Path, with

20 mA Full-Scale Output into 60 Ω Differential Load

–70

–75

–80

IMD (dBc)

–85

–90

–95

01015205

OUTPUT FREQUENCY (MHz)

25

03606-0-078

Figure 48. AD9861 Tx Path Dual-Tone (0.5 MHz Spacing) IMD vs.

Output Frequency of Tx Path, with

20 mA Full-Scale Output into 60 Ω Differential Load

57

56

01015205

Figure 50. AD9861 Tx Path SINAD vs. Output Frequency of Tx Path, with

OUTPUT FREQUENCY (MHz)

25

03606-0-077

2 mA Full-Scale Output into 600 Ω Differential Load

–70

–75

–80

IMD (dBc)

–85

–90

–95

01015205

Figure 51. AD9861 Tx Path Dual-Tone (0.5 MHz Spacing) IMD vs.

OUTPUT FREQUENCY (MHz)

25

03606-0-079

Output Frequency of Tx Path, with

2 mA Full-Scale Output into 600 Ω Differential Load

Rev. 0 | Page 17 of 52

Page 18

AD9861

Figure 52 to Figure 57 use the same input data to the Tx path, a 64-carrier OFDM signal over a 20 MHz bandwidth, centered at 20 MHz.

The center two carriers are removed from the signal to observe the in-band intermodulation distortion (IMD) from the DAC output.

–30

–40

–50

–60

–70

–80

–90

AMPLITUDE (dBc)

–100

–110

–120

–130

7.5 17.5 22.5 27.512.5

FREQUENCY (MHz)

Figure 52. AD9861 Tx Path FFT, 64-Carrier (Center Two Carriers Removed)

32.5

03606-0-080

OFDM Signal over 20 MHz Bandwidth, Centered at 20 MHz, with

20 mA Full-Scale Output into 60 Ω Differential Load

–30

–40

–50

–60

–70

–80

–90

AMPLITUDE (dBc)

–100

–110

–120

–130

18.75 19.75 20.25 20.7519.25

FREQUENCY (MHz)

Figure 55. AD9861 Tx Path FFT, In-Band IMD Products of

OFDM Signal in Figure 52

21.25

03606-0-081

–30

–40

–50

–60

–70

–80

–90

AMPLITUDE (dBc)

–100

–110

–120

–130

7.5 8.0 8.5 9.0 9.5 10.0 10.5 11.0 11.5 12.0

FREQUENCY (MHz)

Figure 53. AD9861 Tx Path FFT, Lower-Band IMD Products of

OFDM Signal in Figure 52

–30

–40

–50

–60

–70

–80

–90

AMPLITUDE (dBc)

–100

–110

–120

–130

0 10203040506070

FREQUENCY (MHz)

Figure 54. AD9861 Tx Path FFT of OFDM Signal in Figure 52,

with 1× Interpolation

12.5

80

03606-0-082

03606-0-084

–30

–40

–50

–60

–70

–80

–90

AMPLITUDE (dBc)

–100

–110

–120

–130

27.5 28.0 28.5 29.0 29.5 30.0 30.5 31.0 31.5 32.0

FREQUENCY (MHz)

Figure 56. AD9861 Tx Path FFT, Upper-Band IMD Products of

OFDM Signal in Figure 52

–30

–40

–50

–60

–70

–80

–90

AMPLITUDE (dBc)

–100

–110

–120

–130

0 10203040506070

FREQUENCY (MHz)

Figure 57. AD9861 Tx Path FFT of OFDM Signal in Figure 52,

with 4× Interpolation

32.5

80

03606-0-083

03606-0-085

Rev. 0 | Page 18 of 52

Page 19

AD9861

Figure 58 to Figure 63 use the same input data to the Tx path, a 256-carrier OFDM signal over a 1.75 MHz bandwidth, centered at 7 MHz.

The center four carriers are removed from the signal to observe the in-band intermodulation distortion (IMD) from the DAC output.

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dBc)

–110

–120

–130

–140

6.0 6.2 6.4 6.6 6.8 7.0 7.2 7.4 7.6 7.8

FREQUENCY (MHz)

Figure 58. AD9861 Tx Path FFT, 256-Carrier (Center Four Carriers Removed)

8.0

03606-0-086

OFDM Signal over 1.75 MHz Bandwidth, Centered at 7 MHz, with

20 mA Full-Scale Output into 60 Ω Differential Load

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dBc)

–110

–120

–130

–140

6.06 6.08 6.10 6.12 6.14 6.16

FREQUENCY (MHz)

Figure 59. AD9861 Tx Path FFT, Lower-Band IMD Products of

6.18

03606-0-088

OFDM Signal in Figure 58

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dBc)

–110

–120

–130

–140

6.97 6.98 6.99 7.00 7.01 7.02

FREQUENCY (MHz)

Figure 61. AD9861 Tx Path FFT, In-Band IMD Products of

OFDM Signal in Figure 58

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dBc)

–110

–120

–130

–140

7.81 7.83 7.85 7.87 7.89 7.91

FREQUENCY (MHz)

Figure 62. AD9861 Tx Path FFT, Upper-Band IMD Products of

OFDM Signal in Figure 52

7.93

7.03

03606-0-087

03606-0-089

–30

–40

–50

–60

–70

–80

–90

AMPLITUDE (dBc)

–100

–110

–120

–130

0 5 10 15 20 25

FREQUENCY (MHz)

Figure 60. AD9861 Tx Path FFT of OFDM Signal in Figure 52,

with 1× Interpolation

03606-0-090

Rev. 0 | Page 19 of 52

–30

–40

–50

–60

–70

–80

–90

AMPLITUDE (dBc)

–100

–110

–120

–130

0 5 10 15 20 25

FREQUENCY (MHz)

Figure 63. AD9861 Tx Path FFT of OFDM Signal in Figure 52,

with 4× Interpolation

03606-0-091

Page 20

AD9861

Figure 64 to Figure 69 use the same input data to the Tx path, a 256-carrier OFDM signal over a 23 MHz bandwidth, centered at 23 MHz.

The center four carriers are removed from the signal to observe the in-band intermodulation distortion (IMD) from the DAC output.

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dBc)

–110

–120

–130

–140

9 1419242934

FREQUENCY (MHz)

Figure 64. AD9861 Tx Path FFT, 256-Carrier (Center Four Carriers Removed)

03606-0-092

OFDM Signal over 23 MHz Bandwidth, Centered at 7 MHz, with

20 mA Full-Scale Output into 60 Ω Differential Load

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dBc)

–110

–120

–130

–140

10.5 10.7 10.9 11.1 11.3 11.5 11.7 11.9 12.1 12.3 12.5

FREQUENCY (MHz)

Figure 65. AD9861 Tx Path FFT, Lower-Band IMD Products of

03606-0-094

OFDM Signal in Figure 64

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dBc)

–110

–120

–130

–140

22.6 22.7 22.8 22.9 23.0 23.1 23.2 23.3 23.4

FREQUENCY (MHz)

Figure 67. AD9861 Tx Path FFT, In-Band IMD Products of

OFDM Signal in Figure 64

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dBc)

–110

–120

–130

–140

33.5 33.7 33.9 34.1 34.3 34.5 34.7 34.9 35.1 35.3 35.5

FREQUENCY (MHz)

Figure 68. AD9861 Tx Path FFT, Upper-Band IMD Products of

OFDM Signal in Figure 64

03606-0-093

03606-0-095

–30

–40

–50

–60

–70

–80

–90

AMPLITUDE (dBc)

–100

–110

–120

–130

0 102030405060708090

FREQUENCY (MHz)

Figure 66. AD9861 Tx Path FFT of OFDM Signal in Figure 52

with 1× Interpolation

03606-0-096

Rev. 0 | Page 20 of 52

–30

–40

–50

–60

–70

–80

–90

AMPLITUDE (dBc)

–100

–110

–120

–130

0 102030405060708090

FREQUENCY (MHz)

Figure 69. AD9861 Tx Path FFT of OFDM Signal in Figure 52

with 4× Interpolation

03606-0-097

Page 21

AD9861

TERMINOLOGY

Input Bandwidth

The analog input frequency at which the spectral power of the

fundamental frequency (as determined by the FFT analysis) is

reduced by 3 dB.

Aperture Delay

The delay between the 50% point of the rising edge of the

CLKIN signal and the instant at which the analog input is

actually sampled.

Aperture Uncertainty (Jitter)

The sample-to-sample variation in aperture delay.

Harmonic Distortion, Second

The ratio of the rms signal amplitude to the rms value of the

second harmonic component, reported in dBc.

Harmonic Distortion, Third

The ratio of the rms signal amplitude to the rms value of the

third harmonic component, reported in dBc.

Integral Nonlinearity

The deviation of the transfer function from a reference line

measured in fractions of an LSB using a “best straight line”

determined by a least square curve fit.

Crosstalk

Coupling onto one channel being driven by a –0.5 dBFS signal

when the adjacent interfering channel is driven by a full-scale

signal.

Differential Analog Input Voltage Range

The peak-to-peak differential voltage that must be applied to

the converter to generate a full-scale response. Peak differential

voltage is computed by observing the voltage on a single pin

and subtracting the voltage from the other pin, which is 180°

out of phase. Peak-to-peak differential is computed by rotating

the input phase 180° and taking the peak measurement again.

Then the difference is computed between both peak

measurements.

Differential Nonlinearity

The deviation of any code width from an ideal 1 LSB step.

Effective Number of Bits (ENOB)

The effective number of bits is calculated from the measured

SNR based on the following equation:

76.1 dBSNR

ENOB

=

MEASURED

−

02.6

Pulse Width/Duty Cycle

Pulse width high is the minimum amount of time that a signal

should be left in the logic high state to achieve rated performance; pulse width low is the minimum time a signal should be

left in the low state, logic low.

Full-Scale Input Power

Expressed in dBm, full-scale input power is computed using the

following equation:

2

⎛

⎜

Power

FULLSCALE

log10

=

⎜

⎝

−

RMSFULLSCALE

001.0

ZV

INPUT

⎞

⎟

⎟

⎠

Gain Error

Gain error is the difference between the measured and ideal

full-scale input voltage range of the ADC.

Minimum Conversion Rate

The encode rate at which the SNR of the lowest analog signal

frequency drops by no more than 3 dB below the guaranteed

limit.

Maximum Conversion Rate

The encode rate at which parametric testing is performed.

Output Propagation Delay

The delay between a differential crossing of CLK+ and CLK−

and the time when all output data bits are within valid logic

levels.

Power Supply Rejection Ratio

The ratio of a change in input offset voltage to a change in

power supply voltage.

Signal-to-Noise and Distortion (SINAD)

The ratio of the rms signal amplitude (set 1 dB below full-scale)

to the rms value of the sum of all other spectral components,

including harmonics, but excluding dc.

Signal-to-Noise Ratio (without Harmonics)

The ratio of the rms signal amplitude (set at 1 dB below full

scale) to the rms value of the sum of all other spectral

components, excluding the first five harmonics and dc.

Spurious-Free Dynamic Range (SFDR)

The ratio of the rms signal amplitude to the rms value of the

peak spurious spectral component. The peak spurious

component may or may not be a harmonic. It also may be

reported in dBc (i.e., degrades as signal level is lowered) or

dBFS (i.e., always related back to converter full scale). SFDR

does not include harmonic distortion components.

Worst Oth e r S p u r

The ratio of the rms signal amplitude to the rms value of the

worst spurious component (excluding the second and third

harmonics) reported in dBc.

Rev. 0 | Page 21 of 52

Page 22

AD9861

THEORY OF OPERATION

SYSTEM BLOCK

The AD9861 is targeted to cover the mixed-signal front end

needs of multiple wireless communication systems. It features a

receive path that consists of dual 10-bit receive ADCs, and a

transmit path that consists of dual 10-bit transmit DACs

(TxDAC). The AD9861 integrates additional functionality

typically required in most systems, such as power scalability,

additional auxiliary converters, Tx gain control, and clock

multiplication circuitry.

The AD9861 minimizes both size and power consumption to

address the needs of a range of applications from the low power

portable market to the high performance base station market.

The part is provided in a 64-lead lead frame chip scale package

(LFCSP) that has a footprint of only 9 mm × 9 mm. Power

consumption can be optimized to suit the particular application

beyond just a speed grade option by incorporating power-down

controls, low power ADC modes, TxDAC power scaling, and a

half-duplex mode, which automatically disables the unused

digital path.

The AD9861 uses two 10-bit buses to transfer Rx path data and

Tx path data. These two buses support 20-bit parallel data

transfers or 10-bit interleaved data transfers. The bus is

configurable through either external mode pins or through

internal registers settings. The registers allow many more

options for configuring the entire device.

The following sections discuss the various blocks of the AD9861:

Rx block, Tx block, the auxiliary converters, the digital block,

programmable registers and the clock distribution block.

Rx PATH BLOCK

Rx Path General Description

The AD9861 Rx path consists of two 10-bit, 50 MSPS (for the

AD9861-50) or 80 MSPS (for the AD9861-80) analog-to-digital

converters (ADCs). The dual ADC paths share the same

clocking and reference circuitry to provide optimal matching

characteristics. Each of the ADCs consists of a 9-stage differential pipelined switched capacitor architecture with output error

correction logic.

The pipelined architecture permits the first stage to operate on a

new input sample, while the remaining stages operate on

preceding samples. Sampling occurs on the falling edge of the

input clock. Each stage of the pipeline, excluding the last,

consists of a low resolution flash ADC and a residual multiplier

to drive the next stage of the pipeline. The residual multiplier

uses the flash ADC output to control a switched capacitor

digital-to-analog converter (DAC) of the same resolution. The

DAC output is subtracted from the stage’s input signal, and the

residual is amplified (multiplied) to drive the next pipeline

stage. The residual multiplier stage is also called a multiplying

DAC (MDAC). One bit of redundancy is used in each one of

the stages to facilitate digital correction of flash errors. The last

stage simply consists of a flash ADC.

The differential input stage is dc self-biased and allows

differential or single-ended inputs. The output-staging block

aligns the data, carries out the error correction, and passes the

data to the output buffers.

The latency of the Rx path is about 5 clock cycles.

Rx Path Analog Input Equivalent Circuit

The Rx path analog inputs of the AD9861 incorporate a novel

structure that merges the function of the input sample-andhold amplifiers (SHAs) and the first pipeline residue amplifiers

into a single, compact switched capacitor circuit. This structure

achieves considerable noise and power savings over a conventional implementation that uses separate amplifiers by eliminating

one amplifier in the pipeline.

Figure 70 illustrates the equivalent analog inputs of the AD9861

(a switched capacitor input). Bringing CLK to logic high opens

switch S3 and closes switches S1 and S2; this is the sample mode

of the input circuit. The input source connected to VIN+ and

VIN− must charge capacitor C

during this time. Bringing CLK

H

to a logic low opens S2, and then switch S1 opens followed by

closing S3. This puts the input circuit into hold mode.

VIN+

VIN–

S1

R

IN

R

IN

Figure 70. Differential Input Architecture

C

IN

V

CM

C

IN

C

H

S3 S2

C

H

+

–

03606-0-002

The structure of the input SHA places certain requirements on

the input drive source. The differential input resistors are

typically 2 kΩ each. The combination of the pin capacitance,

C

, and the hold capacitance, CH, is typically less than 5 pF. The

IN

input source must be able to charge or discharge this capacitance to 10-bit accuracy in one-half of a clock cycle. When the

SHA goes into sample mode, the input source must charge or

discharge capacitor C

from the voltage already stored on it to

H

the new voltage. In the worst case, a full-scale voltage step on

the input source must provide the charging current through the

R

of switch S1 (typically 100 Ω) to a settled voltage within

ON

one-half of the ADC sample period. This situation corresponds

to driving a low input impedance. On the other hand, when the

source voltage equals the value previously stored on C

, the

H

hold capacitor requires no input current and the equivalent

input impedance is extremely high.

Rev. 0 | Page 22 of 52

Page 23

AD9861

Rx Path Application Section

Adding series resistance between the output of the signal source

and the VIN pins reduces the drive requirements placed on the

signal source. Figure 71 shows this configuration.

AD9861

R

SERIES

C

SHUNT

R

SERIES

Figure 71. Typical Input

VIN+

VIN–

03606-0-003

The bandwidth of the particular application limits the size of

this resistor. For applications with signal bandwidths less than

10 MHz, the user may insert series input resistors and a shunt

capacitor to produce a low-pass filter for the input signal.

Additionally, adding a shunt capacitance between the VIN pins

can lower the ac load impedance. The value of this capacitance

depends on the source resistance and the required signal

bandwidth.

The Rx input pins are self-biased to provide this midsupply,

common-mode bias voltage, so it is recommended to ac couple

the signal to the inputs using dc blocking capacitors. In systems

that must use dc coupling, use an op amp to comply with the

input requirements of the AD9861. The inputs accept a signal

with a 2 V p-p differential input swing centered about one-half

of the supply voltage (AVDD/2). If the dc bias is supplied externally, the internal input bias circuit should be powered down by

writing to registers Rx_A dc bias [Register 0x3, Bit 6] and Rx_B

dc bias [Register 0x4, Bit 7].

The ADCs in the AD9861 are designed to sample differential

input signals. The differential input provides improved noise

immunity and better THD and SFDR performance for the Rx

path. In systems that use single-ended signals, these inputs can

be digitized, but it is recommended that a single-ended-todifferential conversion be performed. A single-ended-todifferential conversion can be performed by using a transformer

coupling circuit (typically for signals above 10 MHz) or by

using an operational amplifier, such as the AD8138 (typically

for signals below 10 MHz).

ADC Voltage References

The AD9861 10-bit ADCs use internal references that are

designed to provide for a 2 V p-p differential input range. The

internal band gap reference generates a stable 1 V reference level

and is decoupled through the VREF pin. REFT and REFB are

the differential references generated based on the voltage level

of VREF. Figure 72 shows the proper decoupling of the reference pins VREF, REFT, and REFB when using the internal

reference. Decoupling capacitors should be placed as close to

the reference pins as possible.

External references REFT and REFB are centered at AVDD/2

with a differential voltage equal to the voltage at VREF (by

default 1 V when using the internal reference), allowing a peakto-peak differential voltage swing of 2× VREF. For example, the

default 1 V VREF reference accepts a 2 V p-p differential input

swing and the offset voltage should be

REFT = AVDD/2 + 0.5 V

REFB = AVDD/2 – 0.5 V

10µF

AD9861

TO ADCs

VREF

0.1µF

Figure 72. Typical Rx Path Decoupling

0.5V

REFT

REFB

0.1µF

0.1µF

0.1µF

10µF

03606-0-020

An external reference may be used for systems that require a

different input voltage range, high accuracy gain matching

between multiple devices, or improvements in temperature drift

and noise characteristics. When an external reference is desired,

the internal Rx band gap reference must be powered down

using the VREF2 register [Register 0x5, Bit 4] and the external

reference driving the voltage level on the VREF pin. The

external voltage level should be one-half of the desired peak-topeak differential voltage swing. The result is that the differential

voltage references are driven to new voltages:

REFT = AVDD/2 +V

REFB = AVDD/2 – V

REF

REF

/2 V

/2 V

If an external reference is used, it is recommended not to exceed

a differential offset voltage for the reference greater than 1 V.

Clock Input and Considerations

Typical high speed ADCs use both clock edges to generate a

variety of internal timing signals and, as a result, may be

sensitive to clock duty cycle. Commonly, a 5% tolerance is

required on the clock duty cycle to maintain dynamic performance characteristics. The AD9861 contains clock duty cycle

stabilizer circuitry (DCS). The DCS retimes the internal ADC

clock (nonsampling edge) and provides the ADC with a

nominal 50% duty cycle. Input clock rates of over 40 MHz can

use the DCS so that a wide range of input clock duty cycles can be

accommodated. Conversely, DCS should not be used for Rx

sampling below 40 MSPS. Maintaining a 50% duty cycle clock is

particularly important in high speed applications when proper

sample-and-hold times for the converter are required to

maintain high performance. The DCS can be enabled by writing

highs to the Rx_A/Rx_B CLK duty register bits [Register

0x06/0x07, Bit 4].

The duty cycle stabilizer uses a delay-locked loop to create the

nonsampling edge. As a result, any changes to the sampling

frequency require approximately 2 µs to 3 µs to allow the DLL

to adjust to the new rate and settle. High speed, high resolution

ADCs are sensitive to the quality of the clock input. The

Rev. 0 | Page 23 of 52

Page 24

AD9861

degradation in SNR at a given full-scale input frequency (f

due only to aperture jitter (t

), can be calculated with the

A

following equation:

SNR degradation = 20 log [(½)πFINt

In the equation, the rms aperture jitter,

t

, represents the root-

A

)]

A

sum-square of all jitter sources, which includes the clock input,

analog input signal, and ADC aperture jitter specification.

Undersampling applications are particularly sensitive to jitter.

The clock input is a digital signal that should be treated as an

analog signal with logic level threshold voltages, especially in

cases where aperture jitter may affect the dynamic range of the

AD9861. Power supplies for clock drivers should be separated

from the ADC output driver supplies to avoid modulating the

clock signal with digital noise. Low jitter crystal-controlled

oscillators make the best clock sources. If the clock is generated

from another type of source (by gating, dividing, or other methods), it should be retimed by the original clock at the last step.

Power Dissipation and Standby Mode

The power dissipation of the AD9861 Rx path is proportional to

its sampling rate. The Rx path portion of the digital (DRVDD)

power dissipation is determined primarily by the strength of the

digital drivers and the load on each output bit. The digital drive

current can be calculated by

I

= V

DRVDD

where

N is the number of bits changing and C

DRVDD

× C

LOAD

× f

CLOCK

× N

is the average

LOAD

load on the digital pins that changed.

The analog circuitry is optimally biased so that each speed

grade provides excellent performance while affording reduced

power consumption. Each speed grade dissipates a baseline

power at low sample rates, which increases with clock frequency.

The baseline power dissipation for either speed grade can be

reduced by asserting the ADC_LO_PWR pin, which reduces

internal ADC bias currents by half, in some case resulting in

degraded performance.

To further reduce power consumption of the ADC, the

ADC_LO_PWR pin can be combined with a serial programmable

register setting to configure an ultralow power mode. The

ultralow power mode reduces the power consumption by a

fourth of the normal power consumption. The ultralow power

mode can be used at slower sampling frequencies or if reduced

performance is acceptable. To configure the ultralow power

mode, assert the ADC_LO_PWR pin and write the following

register settings:

Register 0x08 (MSB) ‘0000 1100’

Register 0x09 (MSB) ‘0111 0000’

Register 0x0A (MSB) ‘0111 0000’

Either of the ADCs in the AD9861 Rx path can be placed in

standby mode independently by writing to the appropriate SPI

register bits in Registers 3, 4, and 5. The minimum standby

power is achieved when both channels are placed in full powerdown mode using the appropriate SPI register bits in Registers

INPUT

),

3, 4, and 5. Under this condition, the internal references are

powered down. When either or both of the channel paths are

enabled after a power-down, the wake-up time is directly related

to the recharging of the REFT and REFB decoupling capacitors

and the duration of the power-down. Typically, it takes approximately 5 ms to restore full operation with fully discharged 0.1 µF

and 10 µF decoupling capacitors on REFT and REFB.

Tx PATH BLOCK

The AD9861 transmit (Tx) path includes dual interpolating

10-bit current output DACs that can be operated independently

or can be coupled to form a complex spectrum in an image

reject transmit architecture. Each channel includes two FIR

filters, making the AD9861 capable of 1×, 2×, or 4× interpolation. High speed input and output data rates can be achieved

within the limitations of Table 9.

Table 9. AD9861 Tx Path Maximum Data Rate

Input Data

Rate per

Interpolation

Rate

1×

2×

4×

20-Bit Interface

Mode

FD, HD10, Clone 80 80

HD20 160 160

FD, HD10, Clone 80 160

HD20 80 160

FD, HD10, Clone 50 200

HD20 50 200

Channel

(MSPS)

By using the dual DAC outputs to form a complex signal, an

external analog quadrature modulator, such as the Analog

Devices AD8349, can enable an image rejection architecture.

(Note: the AD9861 evaluation board includes a quadrature

modulator in the Tx path that accommodates the AD8345,

AD8346 and the AD8345 footprints.) To optimize the image

rejection capability, as well as LO feedthrough suppression in

this architecture, the AD9861 offers programmable (via the SPI

port) fine (trim) gain and offset adjustment for each DAC.

Also included in the AD9861 are a phase-locked loop (PLL)

clock multiplier and a 1.2 V band gap voltage reference. With

the PLL enabled, a clock applied to the CLKIN input is multiplied internally and generates all necessary internal synchronization

clocks. Each 10-bit DAC provides two complementary current

outputs whose full-scale currents can be determined from a

single external resistor.

An external pin, TxPWRDWN, can be used to power down the

Tx path, when not used, to optimize system power consumption.

Using the TxPWRDWN pin disables clocks and some analog

circuitry, saving both digital and analog power. The power-down

mode leaves the biases enabled to facilitate a quick recovery

time, typically <10 µs. Additionally, a sleep mode is available,

which turns off the DAC output current, but leaves all other

circuits active, for a modest power savings. An SPI compliant

serial port is used to program the many features of the AD9861.

Note that in power-down mode, the SPI port is still active.

DAC

Sampling

Rate

(MSPS)

Rev. 0 | Page 24 of 52

Page 25

AD9861

DAC Equivalent Circuits

The AD9861 Tx path consisting of dual 10-bit DACs is shown

in Figure 73. The DACs integrate a high performance TxDAC

core, a programmable gain control through a programmable

gain amplifier (TxPGA), coarse gain control, and offset adjustment and fine gain control to compensate for system mismatches.

Coarse gain applies a gross scaling to either DAC by 1×, (1/2)×,

or (1/11)×. The TxPGA provides gain control from 0 dB to

–20 dB in steps of 0.1 dB and is controlled via the 8-bit TxPGA

setting. A fine gain adjustment of ±4% for each channel is controlled through a 6-bit fine gain register. By default, coarse gain

is 1×, the TxPGA is set to 0 dB, and the fine gain is set to 0%.

The TxDAC core of the AD9861 provides dual, differential,

complementary current outputs generated from the 10-bit data.

The 10-bit dual DACs support update rates up to 200 MSPS.

The differential outputs (IOUT+ and IOUT–) of each dual DAC

are complementary, meaning that they always add up to the fullscale current output of the DAC, I

. Optimum ac per for manc e

OUTFS

loads or a transformer.

OFFSET

DAC

+

TxDAC

REFERENCE

BIAS

TxDAC

Figure 73. TxDAC Output Structure Block Diagram

PGA

PGA

OFFSET

DAC

+

+

+

+

+

+

+

IOUT+A

IOUT–A

IOUT+B

IOUT–B

03606-0-004

The fine gain control provides improved balance of QAM

modulated signals, resulting in improved modulation accuracy

and image rejection.

REFIO

FSADJ

≥

0.1µFR

4kΩ

SET

Figure 74. Reference Circuitry

Referring to the transfer function of the following equation,

I

is the maximum current output of the DAC with the

OUTFSMAX

default gain setting (0 dB), and is based on a reference current,

I

. I

is set by the internal 1.2 V reference and the external

REF

REF

resistor.

R

SET

I

Typical l y, R

= 64 × (REFIO/R

OUTFSMAX

SET

is 4 kΩ, which sets I

optimal dynamic setting for the TxDACs. Increasing R

factor of 2 proportionally decreases I

I

of each DAC can be rescaled either simultaneously

OUTFSMAX

using the TxPGA gain register or independently using the

DAC A/DAC B coarse gain registers.

The TxPGA function provides 20 dB of simultaneous gain

range for both DACs, and is controlled by writing to the SPI

register TxPGA gain for a programmable full-scale output of

10% to 100% of I

OUTFSMAX

steps of about 0.1 dB. Internally, the gain is controlled by

changing the main DAC bias currents with an internal TxPGA

DAC whose output is heavily filtered via an on-chip R-C filter

to provide continuous gain transitions. Note that the settling

time and bandwidth of the TxPGA DAC can be improved by a

factor of 2 by writing to the TxPGA fast register.

Each DAC has independent coarse gain control. Coarse gain

control can be used to accommodate different I

dual DACs. The coarse full-scale output control can be adjusted

by using the DAC A/DAC B coarse gain registers to 1/2 or 1/11

of the nominal full-scale current.

1.2V

REFERENCE

SET

DAC A AND DAC B

REFERENCE BIASES

)

OUTFSMAX

OUTFSMAX

CURRENT

SOURCE ARRAY

I

REF

to 20 mA, the

by a factor of 2.

I

OUTFSMAX

03606-0-005

by a

SET

. The gain curve is linear in dB, with

from the

OUTFS

The independent DAC A and DAC B offset control adds a small

dc current to either IOUT+ or IOUT– (not both). The selection

of which IOUT this offset current is directed toward is

programmable via register setting. Offset control can be used

for suppression of an LO leakage signal that typically results at

the output of the modulator. If the AD9861 is dc-coupled to an

external modulator, this feature can be used to cancel the output

offset on the AD9861 as well as the input offset on the modulator.

The reference circuitry is shown in Figure 74.

Rev. 0 | Page 25 of 52

Fine gain controls and dc offset controls can be used to

compensate for mismatches (for system level calibration),

allowing improved matching characteristics of the two Tx

channels and aiding in suppressing LO feedthrough. This is

especially useful in image rejection architectures. The 10-bit dc

offset control of each DAC can be used independently to

provide an offset of up to ±12% of I

to either differential

OUTFSMAX

pin, thus allowing calibration of any system offsets. The fine

gain control with 5-bit resolution allows the I

OUTFSMAX

of each

DAC to be varied over a ±4% range, allowing compensation of

any DAC or system gain mismatches. Fine gain control is set

through the DAC A/DAC B fine gain registers, and the offset

control of each DAC is accomplished using the DAC A/DAC B

offset registers.

Page 26

AD9861

Clock Input Configuration

The quality of the clock and data input signals is important in

achieving optimum performance. The external clock driver

circuitry provides the AD9861 with a low jitter clock input that

meets the min/max logic levels while providing fast edges.

When a driver is used to buffer the clock input, it should be

placed very close to the AD9861 clock input, thereby negating

any transmission line effects such as reflections due to

mismatch.

Programmable PLL

CLKIN can function either as an input data rate clock (PLL

enabled) or as a DAC data rate clock (PLL disabled).

The PLL clock multiplier and distribution circuitry produce the

necessary internal timing to synchronize the rising edge triggered latches for the enabled interpolation filters and DACs.

This circuitry consists of a phase detector, charge pump, voltage

controlled oscillator (VCO), and clock distribution block, all

under SPI port control. The charge pump, phase detector, and

VCO are powered from PLL_AVDD, while the clock distribution circuits are powered from the DVDD supply.

To ensure optimum phase noise performance from the PLL

clock multiplier circuits, PLL_AVDD should originate from a

clean analog supply. The speed of the VCO within the PLL also

has an effect on phase noise.

The PLL locks with VCO speeds as low as 32 MHz up to

350 MHz, but optimal phase noise with respect to VCO speed is

achieved by running it in the range of 64 MHz to 200 MHz.

Power Dissipation

The AD9861 Tx path power is derived from three voltage

supplies: AVDD, DVDD, and DRVDD.

IDRVDD and IDVDD are very dependent on the input data

rate, the interpolation rate, and the activation of the internal

digital modulator. IAVDD has the same type of sensitivity to

data, inter polation rate, and the modulator function, but to a

much lesser degree (< 10%).

Sleep/Power-Down Modes

The AD9861 provides multiple methods for programming

power saving modes. The externally controlled TxPWRDWN

or SPI programmed sleep mode and full power-down mode are

the main options.

TxPWRDWN is used to disable all clocks and much of the

analog circuitry in the Tx path when asserted. In this mode, the

biases remain active, therefore reducing the time required for

re-enabling the Tx path. The time of recovery from powerdown for this mode is typically less than 10 µs.

The sleep mode, when activated, turns off the DAC output

currents, but the rest of the chip remains functioning. When

coming out of sleep mode, the AD9861 immediately returns to

full operation.

A full power-down mode can be enabled through the SPI

register, which turns off all Tx path related analog and digital

circuitry in the AD9861. When returning from full power-down

mode, enough clock cycles must be allowed to flush the digital

filters of random data acquired during the power-down cycle.

Interpolation Stage

Interpolation filters are available for use in the AD9861 transmit

path, providing 1× (bypassed), 2×, or 4× interpolation.

The interpolation filters effectively increase the Tx data rate

while suppressing the original images. The interpolation filters

digitally shift the worst-case image further away from the

desired signal, thus reducing the requirements on the analog

output reconstruction filter.

There are two 2× interpolation filters available in the Tx path.

An interpolation rate of 4× is achieved using both interpolation

filters; an interpolation rate of 2× is achieved by enabling only

the first 2× interpolation filter.

The first interpolation filter provides 2× interpolation using a

39-tap filter. It suppresses out-of-band signals by 60 dB or more

and has a flat pass-band response (less than 0.1 dB ripple)

extending to 38% of the input Tx data rate (19% of the DAC

update rate, f

). The maximum input data rate is 80 MSPS per

DAC

channel when using 2× interpolation.

The second interpolation filter provides an additional 2× interpolation for an overall 4× interpolation. The second filter is a 15-tap

filter, which suppresses out-of-band signals by 60 dB or more.

The flat pass-band response (less than 0.1 dB attenuation) is

38% of the Tx input data rate (9.5% of f

). The maximum

DAC

input data rate per channel is 50 MSPS per channel when using

4× interpolation.

Latch/Demultiplexer

Data for the dual-channel Tx path can be latched in parallel

through two ports in half-duplex operations (HD20 mode) or

through a single port by interleaving the data (FD, HD10, and

Clone modes). See the Flexible I/O Interface Options section in

the Digital Block description and the Clock Distribution Block

section for further descriptions of each mode.

Rev. 0 | Page 26 of 52

Page 27

AD9861

AUXILIARY CONVERTERS

The AD9861 contains auxiliary analog-to-digital converters

(AuxADCs) and auxiliary digital-to-analog converters

(AuxDACs). These auxiliary converters can be used to measure

or force system-wide control signals.

Update C, B, and A]. Slave mode is enabled by writing a high to

the slave mode register bit [Register 0x28, Bit 7, Slave Enable].

Another synchronization mode allows any combination of

AuxDACs to be updated along with an externally applied rising

edge to the TxPwrDwn pin.

By default, the auxiliary converters are disabled and powered

down. Enabling and controlling the auxiliary converters is

achieved through the serial programmable registers.

Pins 29, 30, and 46 are configurable either as AuxDAC outputs

or as AuxADC inputs. The respective AuxADC inputs are

connected to the external pin when a conversion is initiated and

are disconnected when the conversion is complete. The

AuxDAC outputs are enabled by writing to the respective

power-up registers in Register 0x29.

• Pin 29 can be connected to AuxDAC_A and/or

AuxADC_A Channel 2.

• Pin 30 can be connected to AuxDAC_B and/or

AuxADC_A Channel 1.

• Pin 46 can be connected to AuxDAC_C and/or

AuxADC_B.

Auxiliary DACs

The AD9861 integrates three 8-bit voltage output auxiliary

digital-to-analog converters (AuxDACs), which can be used for

supplying various control voltages throughout the system such

as a VCXO voltage control or external VGA gain control. The

AuxDACs have a programmable full-scale output voltage, V

and can be synchronized to update with a single register write