Page 1

Low Distortion 750 MHz

1

2

3

4

8

7

6

5

NC = NO CONNECT

AD9630

***

NC

**

INPUT

+V

S

NC

–V

S

OUTPUT

NOTE: FOR BEST SETTLING TIME PERFORMANCE USE

OPTIONAL POWER SUPPLIES. ALL SPECIFICATIONS

ARE BASED ON USING SINGLE 6V

S

CONNECTIONS,

EXCEPT FOR SETTLING TIME TO 0.02% AND SMALL

SIGNAL S21. CONSULT THE FACTORY FOR VERSIONS

WITH OPTIONAL POWER SUPPLY PINS DISCONNECTED

INTERNAL TO THE PACKAGE.

**OPTIONAL +V

S

***OPTIONAL –V

S

a

FEATURES

Excellent Gain Accuracy: 0.99 V/V

Wide Bandwidth: 750 MHz

Slew Rate: 1200 V/s

Low Distortion

–65 dBc @ 20 MHz

–80 dBc @ 4.3 MHz

Settling Time

5 ns to 0.1%

8 ns to 0.02%

Low Noise: 2.4 nV/√Hz

Improved Source for CLC-110

APPLICATIONS

IF/Communications

Impedance Transformations

Drives Flash ADCs

Line Driving

GENERAL DESCRIPTION

The AD9630 is a monolithic buffer amplifier that utilizes a

patented, innovative, closed-loop design technique to achieve

exceptional gain accuracy, wide bandwidth, and low distortion.

Slew rate limiting has been overcome as indicated by the

1200 V/µs slew rate; this improvement allows the user greater

flexibility in wideband and pulse applications. The second harmonic distortion terms for an analog input tone of 4.3 MHz

and 20 MHz are –80 dBc and –66 dBc, respectively. Clearly,

the AD9630 establishes a new standard by combining outstanding dc and dynamic performance in one part.

Closed-Loop Buffer Amp

AD9630*

PIN CONFIGURATION

The large signal bandwidth, low distortion over frequency, and

drive capabilities of the AD9630 make the buffer an ideal flash

ADC driver. The AD9630 provides better signal fidelity than

many of the flash ADCs that it has been designed to drive.

Other applications that require increased current drive at unity

voltage gain (such as cable driving) benefit from the AD9630’s

performance.

The AD9630 is available in plastic DIP (N) and SOIC (R).

*Protected under U.S. patent numbers 5,150,074 and 5,537,079.

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1999

Page 2

AD9630–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

(unless otherwise noted, ⴞVS = ⴞ5 V; RIN = 50 ⍀, R

= 100 ⍀)

LOAD

Test AD9630AN/AR

Parameter Conditions Temp Level Min Typ Max Units

DC SPECIFICATIONS

Output Offset Voltage +25°CI–8±3+8mV

Offset Voltage TC Full IV –40 ±8 +40 µV/°C

Input Bias Current +25°C I –25 ±2 +25 µA

Bias Current TC Full IV –100 ±20 +100 nA/°C

Input Resistance +25 to T

T

MIN

MAX

II 300 450 kΩ

VI 150 250 kΩ

Input Capacitance +25°CV 1.0 pF

Gain V

= 2 V p-p +25 to T

OUT

= 2 V p-p T

V

OUT

MAX

MIN

II 0.983 0.990 V/V

VI 0.980 0.985 V/V

Output Voltage Range Full VI +3.2 ±3.6 –3.2 V

Output Current (50 Ω Load) +25 to T

T

MIN

MAX

II 50 mA

VI 40 mA

Output Impedance At DC +25°CV 0.6 Ω

PSRR ∆V

= ±5% Full VI 44 55 dB

S

DC Nonlinearity ±2 V Full Scale +25°C V 0.03 %

FREQUENCY DOMAIN

Bandwidth (–3 dB)

Small Signal V

Large Signal V

≤ 0.7 V p-p T

O

≤ 0.7 V p-p T

V

O

= 5 V p-p T

O

= 5 V p-p T

V

O

to +25 II 400 750 MHz

MIN

MAX

to +25 V 120 MHz

MIN

MAX

II 330 550 MHz

V 105 MHz

Output Peaking ≤200 MHz Full II 0.4 1.2 dB

Output Rolloff ≤200 MHz Full II 0 0.3 dB

Group Delay DC to 150 MHz +25°CV 0.7 ns

Linear Phase Deviation DC to 150 MHz +25°C V 0.7 Degrees

2nd Harmonic Distortion 2 V p-p; 4.3 MHz Full IV –80 –73 dBc

2 V p-p; 20 MHz Full IV –66 –58 dBc

2 V p-p; 50 MHz Full II –52 –43 dBc

3rd Harmonic Distortion 2 V p-p; 4.3 MHz Full IV –86 –79 dBc

2 V p-p; 20 MHz Full IV –75 –68 dBc

2 V p-p; 50 MHz T

2 V p-p; 50 MHz T

to +25 II –47 –41 dBc

MIN

MAX

II –46 –40 dBc

Spectral Input Noise Voltage 10 MHz +25°C V 2.4 nV/√Hz

Integrated Output Noise 100 kHz – 200 MHz +25°CV 32 µV

TIME DOMAIN

Slew Rate V

Rise/Fall Time V

Overshoot Amplitude V

= 5 V Step +25°C IV 700 1200 V/µs

OUT

= 1 V Step +25°CIV 1.11.7ns

OUT

= 1 V Step T

V

OUT

= 5 V Step +25°CIV 4.25.7ns

V

OUT

= 5 V Step T

V

OUT

= 2 V Step Full IV 2 12 %

OUT

MIN

MIN

to T

to T

MAX

MAX

IV 1.3 1.9 ns

IV 5.0 6.5 ns

Settling Time

To 0.1% V

To 0.02%

4

= 2 V Step T

OUT

= 2 V Step T

V

OUT

V

= 2 V Step T

OUT

= 2 V Step T

V

OUT

to +25 IV 6 10 ns

MIN

MAX

to +25 IV 8 ns

MIN

MAX

IV 7 12 ns

V12ns

Differential Gain 4.4 MHz +25°C V 0.015 %

Differential Phase 4.4 MHz +25°C V 0.025 Degree

SUPPLY CURRENTS

(+IS)V

V

CC

VEE (–IS)V

NOTES

1

Short-term settling with 50 Ω source impedance.

Specifications subject to change without notice.

= +5 V Full II 19 26 mA

CC

= –5 V Full II 19 26 mA

EE

–2–

REV. B

Page 3

AD9630

1

2

3

4

8

7

6

5

TOP VIEW

(Not to Scale)

NC = NO CONNECT

AD9630

NC

NC

NC

NC

100V

(5%, 0.25W)

24V

(5%, 0.25W)

+5V

–5.2V

0.1mF

0.1mF

CL – pF

50

40

0

0

10020

R

SERIES

– V

40 60 80

30

20

10

7

R

S

C

L

200V

"R"

NO R

S

NEEDED

WHEN

C

L

< 7pF;

FOR

C

L

> 30pF, "R"

CAN

BE OMITTED

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

Supply Voltages (±VS) . . . . . . . . . . . . . . . . . . . . . . . . . . . ±7 V

Continuous Output Current

2

. . . . . . . . . . . . . . . . . . . . . 70 mA

1

Temperature Range over Which Specifications Apply

°

AD9630AN/AR . . . . . . . . . . . . . . . . . . . . . –40

C to +85°C

Lead Soldering Temperature (10 sec) . . . . . . . . . . . . . +300°C

Storage Temperature

AD9630AN/AR . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Junction Temperature

3

AD9630AN/AR . . . . . . . . . . . . . . . . . . . . . . . . . . . . +150°C

NOTES

1

Absolute maximum ratings are limiting values to be applied individually, and

beyond which the serviceability of the circuit may be impaired. Functional

operability is not necessarily implied. Exposure to absolute maximum rating

conditions for an extended period of time may affect device reliability.

2

Output is short-circuit protected to ground, but not to supplies. Prolonged short

circuit to ground may affect device reliability.

3

Typical thermal impedances (part soldered onto board): Plastic DIP (N): θ

110°C/W; θJC = 30°C/W; SOIC (R): θJA = 155°C/W; θJC = 40°C/W.

=

JA

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

AD9630AN –40°C to +85°C 8-Lead Plastic DIP N-8

AD9630AR –40°C to +85°C 8-Lead SOIC SO-8

AD9630AR-REEL –40°C to +85°C13" Tape and Reel SO-8

EXPLANATION OF TEST LEVELS

Test Level

I 100% Production tested.

II 100% Production tested at +25°C and sample tested at

specified temperatures. AC testing of AN and AR grades

done on sample basis only.

III Sample tested only.

IV Parameter is guaranteed by design and characterization

testing.

V Typical value.

VI S Versions are 100% production tested at temperature

extremes. Other grades are sample tested at extremes.

AD9630 Burn-In Circuit

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9630 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

THEORY OF OPERATION

The AD9630 is a wide-bandwidth, closed-loop, unity-gain

buffer that makes use of a new voltage-feedback architecture.

This architecture brings together wide bandwidth and high slew

rate along with exceptional dc linearity. Most previous widebandwidth buffers achieved their bandwidth by utilizing an

open-loop topology which sacrificed both dc linearity and fre-

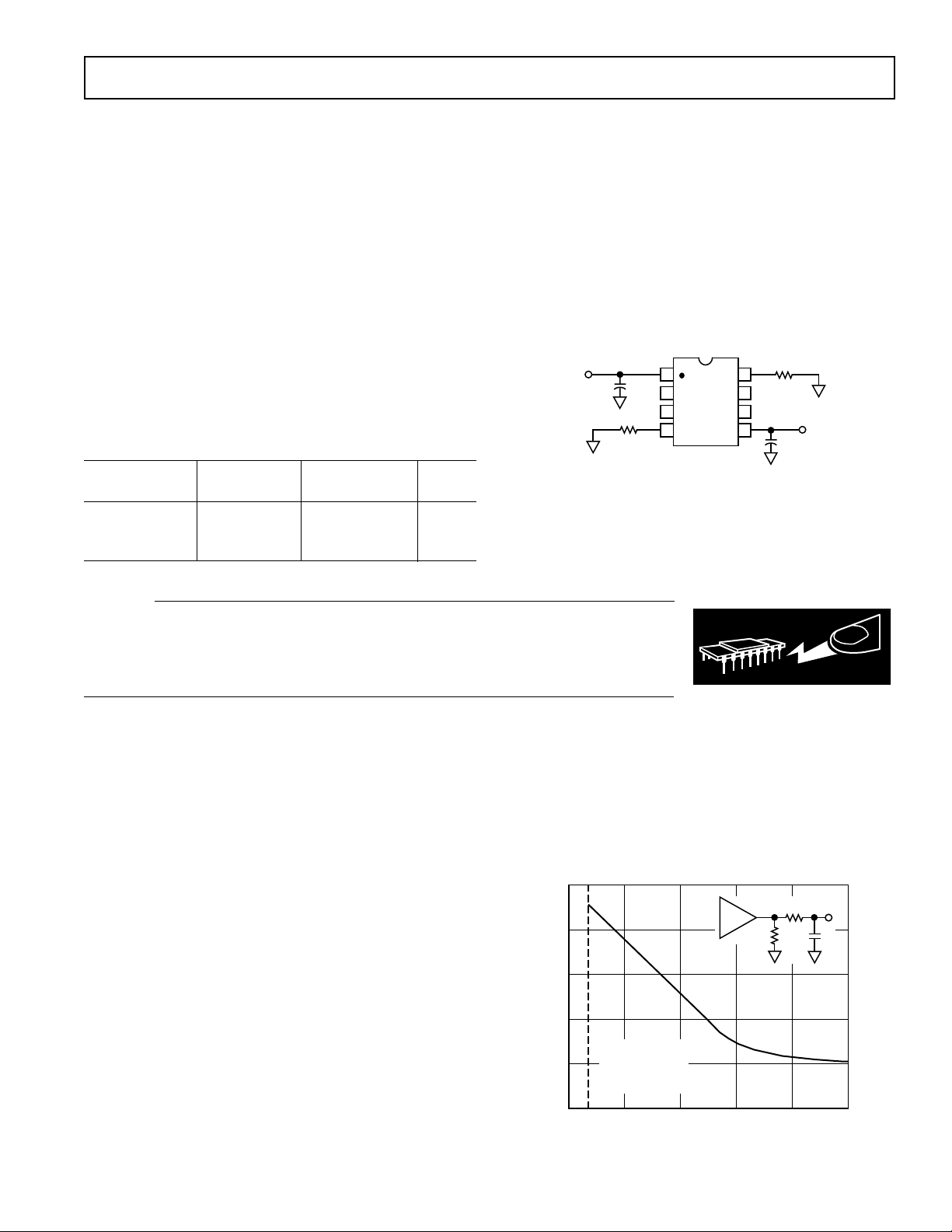

Parasitic or load capacitance (>7 pF) connected directly to the

AD9630 output will result in frequency peaking. A small series

resistor (R

) connected between the buffer output and capaci-

S

tive load will negate this effect. Figure 1 shows the optimal value

as a function of CL to obtain the flattest frequency re-

of R

S

sponse. Figure 2 illustrates frequency response for various

capacitive loads utilizing the recommended R

.

S

quency distortion when driven into low load impedances. The

design’s high loop correction factor radically improves dc linearity and distortion characteristics without diminishing

bandwidth. This, in combination with high slew rate, results in

exceptionally low distortion over a wide frequency range.

The AD9630 is an excellent choice to drive high speed and high

resolution analog-to-digital converters. Its output stage is designed to drive high speed flash converters with minimal or no

series resistance. A current booster built into the output driver

helps to maintain low distortion.

REV. B

Figure 1. Recommended RS vs. C

L

–3–

Page 4

AD9630

2

1

0

–1

–2

–3

–4

–5

FREQUENCY RESPONSE – dB

–6

–7

–8

<0.1MHz

100MHz 200MHz 300MHz

C

L

Figure 2. Frequency Response vs. C

with Recommended R

S

10pF

25pF

50pF

L

In pulse mode applications, with RS equal to approximately

12 Ω, capacitive loads of up to 50 pF can be driven with mini-

mal settling time degradation.

The output stage has short circuit protection to ground. The

output driver will shut down if more than approximately

130 mA of instantaneous sink or source current is reached. This

level of current ensures that output clipping will not result when

driving heavy capacitive loads during high slew conditions,

although average load currents above 70 mA may reduce device

reliability.

LAYOUT CONSIDERATIONS

Due to the high frequency operation of the AD9630 attention to

board layout is necessary to achieve optimum dynamic performance. A two ounce copper ground plane on the top side of the

board is recommended; it should cover as much of the board as

possible with appropriate openings for supply decoupling capacitors as well as for load and source termination resistors, (see

Figure 3).

Optimum settling time and ac performance results will be

achieved with surface mount 0.1 µF supply decoupling ceramic

chip capacitors mounted within 50 mils of the corresponding

device pins with the other side soldered directly to the ground

plane. For best high resolution (<0.02%) settling times, the optional power supply pins should be decoupled as shown above.

If the optional power supply pins are not used, they should be

left open.

If surface mount capacitors cannot be used, radial lead ceramic

capacitors with leads less than 30 mils long are recommended.

Low frequency power supply decoupling is necessary and can be

accomplished with 4.7 µF tantalum capacitors mounted within

0.5 inches of the supply pins. Due to the series inductance of

these capacitors interacting with the 0.1 µF capacitors and

power supply leads, high frequency oscillations might appear on

the device output. To avoid this occurrence, the power supply

leads should be tightly twisted (if appropriate). Ferrite beads

mounted between the tantalum and ceramic capacitors will

serve the same purpose.

All unused pins (except the optional power supply pins) should

be connected to ground to reduce pin-to-pin capacitive coupling

and prevent external RF interference. If the source and drive

electronics require “remote” operation (> 1 inch from the

AD9630), the PC board line impedances should be matched

with the buffer input and output resistances. Basic microstrip

techniques should be observed. RIN and RS should be connected

as close to the AD9630 as possible.

With only minimal pulse overshoot and ringing, the AD9630

can drive terminated cables directly without the use of an output

termination resistor (R

). Termination resistors (RS and RIN)

S

can be either standard carbon composition or microwave type.

For matching characteristic impedances, precision microwave

resistors of 1% or better tolerance are preferred.

The AD9630 should be soldered directly to the PC board with

as little vertical clearance as possible. The use of zero insertion

sockets is strongly discouraged because of the high effective pin

inductances. Use of this type socket will result in peaking and

possibly induce oscillation.

+V

4.7mF

S

0.1mF

0.1mF

1

*

V

IN

R

IN

AD9630

5

–V

S

*SEE PINOUTS

**SEE FIGURE 1

2

6

*

0.1mF

0.1mF

4.7mF

RS**

8

V

OUT

Figure 3. AD9630 Application Circuit

–4–

REV. B

Page 5

Typical Performance Curves –

V – |Zo|

FREQUENCY – Hz

30

25

0

1M 10M 1G

100M

15

10

5

20

PHASE – Degrees

100

80

40

20

0

60

|Zo|

CASE TEMPERATURE – 8C

10

–10

–2

–4

–6

–8

–55 25 125

OFFSET VOLTAGE – mV

50

40

–50

–10

–20

–30

–40

20

0

10

30

BIAS CURRENT – mA

8

4

0

2

6

BIAS CURRENT

OFFSET VOLTAGE

AD9630

0

–100

–200

–300

–400

–500

ppm

–600

–700

–800

–900

–1000

–3 –2 3

RL = 200V

RL = 100V

–1 0 1 2

VOLTS

Figure 4. Endpoint DC Linearity

50

40

30

20

PSRR – dB

10

1M

100k

10k

V

1k

100

10

1

1M

10M 100M 1G

FREQUENCY – Hz

Figure 5. Input Impedance

50

40

TEST

30

20

INTERCEPT – +dBm

10

CIRCUIT

Figure 6. Output Impedance

50V

50V

0

1M 10M 1G

FREQUENCY – Hz

Figure 7. PSRR vs. Frequency

2

1

0

–1

–2

–3

PHASE

–4

MAGNITUDE – dB

–5

–6

–7

–8

0M 1G200M 400M 600M 800M

VIN = 100mV

VIN = 750mV

VIN = 100mV

FREQUENCY – Hz

Figure 10 . Forward Gain and Phase

REV. B

100M

GAIN

0

–45

–90

PHASE – Degrees

–135

–180

0

dc 250

50 100 150 200

FREQUENCY – MHz

Figure 8. 2-Tone Intermodulation

Distortion

3

2

1

0

–1

–2

–3

MAGNITUDE – dB

–4

–5

–6

–7

40 80 120 160

0 200

FREQUENCY – MHz

RL = 200V

RL = 50V

RL = 100V

Figure 11. Frequency Response vs.

R

LOAD

–5–

Figure 9. Offset Voltage and Bias

Current vs. Temperature

0.5

0.25

0

VOLTS

–0.25

–0.5

TEST CIRCUIT

50V

50V

2ns/DIVISION

6pF

Figure 12. Small-Signal Pulse

Response

Page 6

AD9630

–0.5

5ns/DIVISION

VOLTS

50V

6pF

50V

TEST CIRCUIT

3.0

0

1.5

2.5

2.0

1.0

0.5

–1.0

–1.5

–2.0

–2.5

–3.0

0.1

0.08

0.06

0.04

0.02

0

–0.02

–0.04

–0.06

SETTLING PERCENTAGE – %

–0.08

–0.1

10 20 30 40 50

TEST CIRCUIT

100V

V

OUT

TIME – ns

6pF

= 2V STEP

Figure 13. Short-Term Settling Time

40

RL = 100V

dBc

50

60

70

80

2nd

3rd

0.1

0.08

0.06

0.04

0.02

0

–0.02

–0.04

–0.06

SETTLING PERCENTAGE – %

–0.08

–0.1

10 100 1k 10k 100k

1

TEST CIRCUIT

100V

V

TIME – ns

= 2V STEP

OUT

6pF

Figure 14. Long-Term Settling Time

40

RL = 100V

50

60

2nd

3rd

dBc

70

80

Figure 15. Large-Signal Pulse

Response

90

100

110

FREQUENCY – MHz

Figure 16. Harmonic Distortion

V

= 4 V p-p

OUT

100

90

100

110

FREQUENCY – MHz

Figure 17. Harmonic Distortion

V

= 2 V p-p

OUT

–6–

100

REV. B

Page 7

OUTLINE DIMENSIONS

0.0098 (0.25)

0.0075 (0.19)

0.0500 (1.27)

0.0160 (0.41)

88

08

0.0196 (0.50)

0.0099 (0.25)

3 458

85

41

0.1 968 (5.00)

0.1 890 (4.80)

0.2440 (6.20)

0.2284 (5.80)

PIN 1

0.1574 (4.00)

0.1497 (3.80)

0.0500 (1.27)

BSC

0.0688 (1.75)

0.0532 (1.35)

SEATING

PLANE

0.0098 (0.25)

0.0040 (0.10)

0.0192 (0.49)

0.0138 (0.35)

Dimensions shown in inches and (mm).

AD9630

PIN 1

0.210

(5.33)

MAX

0.160 (4.06)

0.115 (2.93)

0.022 (0.558)

0.014 (0.356)

8-Lead Plastic DIP

0.430 (10.92)

0.348 (8.84)

8

0.100 (2.54)

5

0.280 (7.11)

14

BSC

0.240 (6.10)

0.060 (1.52)

0.015 (0.38)

0.070 (1.77)

0.045 (1.15)

(N-8)

0.130

(3.30)

MIN

SEATING

PLANE

0.325 (8.25)

0.300 (7.62)

0.015 (0.381)

0.008 (0.204)

0.195 ( 4.95)

0.115 (2.93)

8-Lead SOIC

(SO-8)

C1401a–0–12/99 (rev. B)

REV. B

PRINTED IN U.S.A.

–7–

Loading...

Loading...