Page 1

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

A

High Performance, Low Power

Preliminary Technical Data

FEATURES

General

Low power HDMI/DVI transmitter ideal for portable

applications

Compatible with HDMI v. 1.3, DVI v. 1.0, and HDCP v. 1.2

Single 1.8 V power supply

Video/audio inputs accept logic levels from 1.8 V to 3.3 V

64-lead LFCSP, Pb-free package

76-ball CSP_BGA, Pb-free package

Digital video

80 MHz operation supports all resolutions from 480i to

1080i and XGA at 75 Hz

Programmable 2-way color space converter

Supports RGB, YCbCr, and DDR

Supports ITU656-based embedded syncs

Automatic input video format timing detection (CEA-861D)

Digital audio

Supports standard S/PDIF for stereo LPCM or compressed

audio up to 192 kHz

8-channel, uncompressed LPCM I

Special features for easy system design

On-chip MPU with I

2

C® master to perform HDCP

operations and EDID reading operations

5 V tolerant I

2

C and HPD I/Os, no extra device needed

No audio master clock needed for supporting S/PDIF

2

and I

S

On-chip MPU reports HDMI events through interrupts and

registers

2

S audio up to 192 kHz

CLK

VSYNC

HSYNC

DE

D[23:0]

S/PDIF

MCLK

I2S[3:0]

LRCLK

SCLK

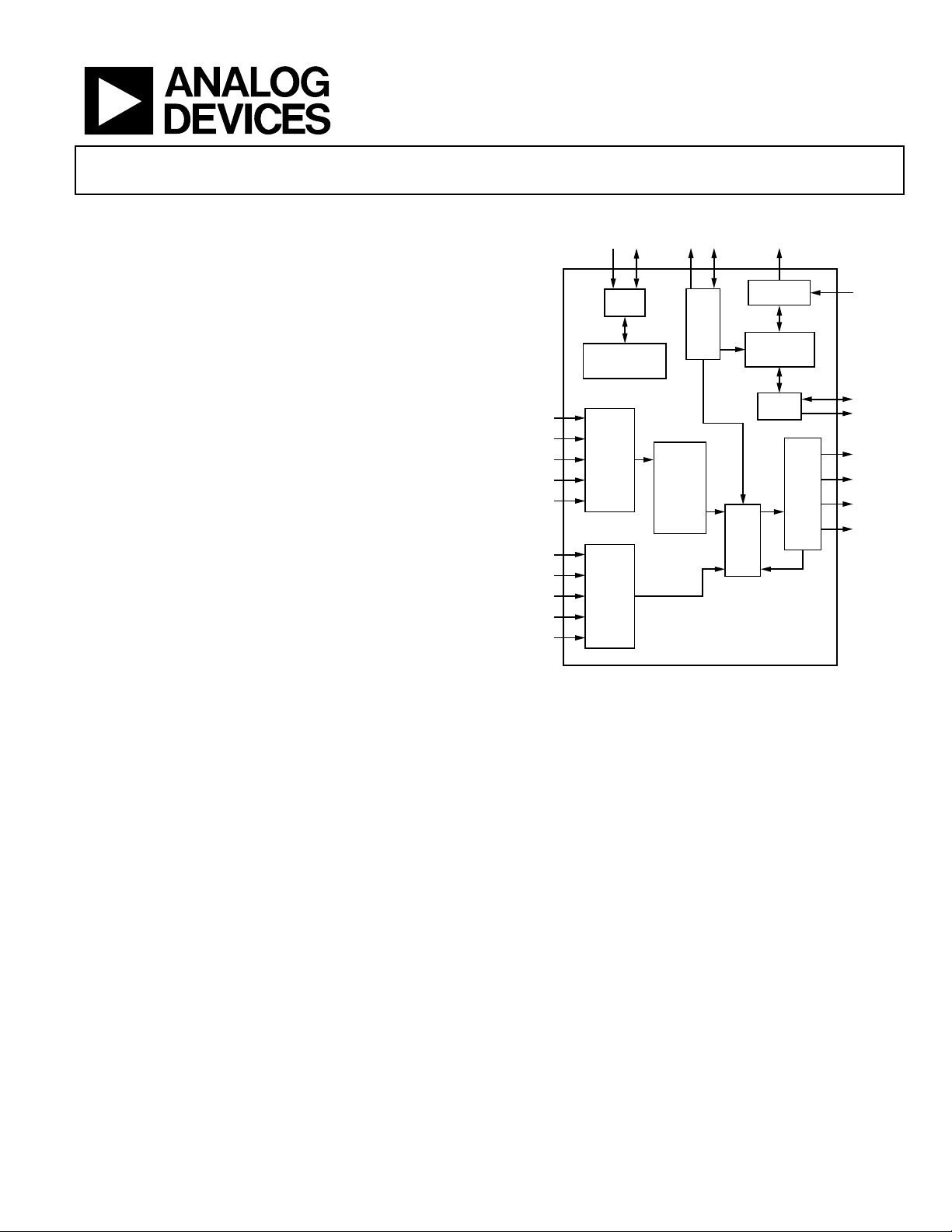

HDMI™/DVI Transmitter

AD9387NK

FUNCTIONAL BLOCK DIAGRAM

SD

SCL

I2C

SLAVE

REGISTER

CONFIGURATION

LOGIC

VIDEO

DATA

CAPTURE

AUDIO

DATA

CAPTURE

COLOR

SPACE

CONVER-

SION

4:2:2 TO

4:4:4

CONVER-

SION

Figure 1.

MDAMCL

HDCP

CORE

INT

INTERRUPT

HANDLER

HDCP-EDID

MICRO-

CONTROLLER

I2C

MASTER

XOR

MASK

AD9387NK

HDMI

Tx

CORE

HPD

DDCSDA

DDCSCL

Tx0[1:0]

Tx1[1:0]

Tx2[1:0]

TxC[1:0]

06507-001

APPLICATIONS

Digital video cameras

Digital still cameras

Personal media players

Cellular handsets

DVD players and recorders

Digital set-top boxes

A/V receivers

HDMI repeater/splitter

GENERAL DESCRIPTION

The AD9387NK is an 80 MHz, high definition multimedia

interface (HDMI) v.1.3 transmitter. It supports HDTV formats

up to 720p and 1080i and computer graphic resolutions up to

XGA (1024 × 768 @ 75Hz). With the inclusion of HDCP, the

AD9387NK allows the secure transmission of protected content,

as specified by the HDCP v.1.1 protocol.

Rev. PrA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

The AD9387NK supports both S/PDIF and 8-channel I2S audio.

2

Its high fidelity, 8-channel I

S can transmit either stereo or 7.1

surround audio at 192 kHz. The S/PDIF can carry stereo LPCM

audio or compressed audio, including Dolby® Digital, DTS®,

and THX®.

The AD9387NK helps reduce system design complexity and cost

by incorporating such features as an internal MPU for HDCP

operations, an I

supply, and 5 V tolerance on the I

2

C master for EDID reading, a single 1.8 V power

2

C and hot plug detect pins.

Fabricated in an advanced CMOS process, the AD9387NK

is available in a space saving, 76-ball CSP_BGA or 64-lead LFCSP

surface-mount package. Both packages are available as Pb-free

parts and are specified from −25°C to +85°C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

Page 2

AD9387NK Preliminary Technical Data

TABLE OF CONTENTS

Features .............................................................................................. 1

Design Resources ..........................................................................7

Applications....................................................................................... 1

General Description......................................................................... 1

Functional Block Diagram .............................................................. 1

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 4

Explanation of Test Levels........................................................... 4

ESD Caution.................................................................................. 4

Pin Configuration and Function Descriptions............................. 5

Applications Information ................................................................ 7

Document Conventions ...............................................................7

PCB Layout Recommendations.......................................................8

Power Supply Bypassing ...............................................................8

Digital Inputs .................................................................................8

External Swing Resistor................................................................8

Output Signals ...............................................................................8

Outline Dimensions ..........................................................................9

Ordering Guide .............................................................................9

Rev. PrA | Page 2 of 12

Page 3

Preliminary Technical Data AD9387NK

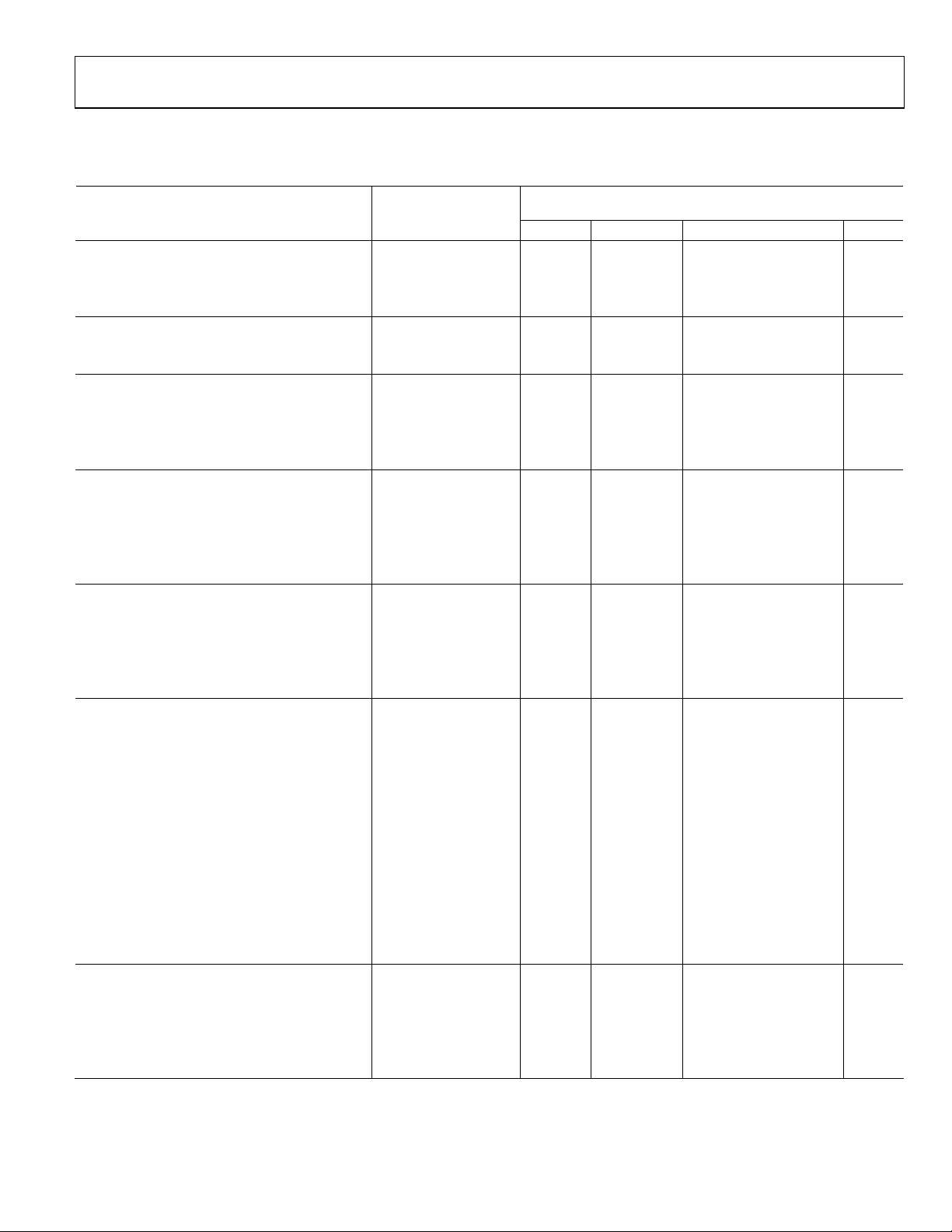

SPECIFICATIONS

Table 1.

AD9387NK-BCPZ-80/AD9387NK-BBCZ-80

Parameter Conditions

Temp Test Leve l

1

Min Typ Max Unit

DIGITAL INPUTS

Input Voltage, High (VIH) Full VI 1.4 3.5 V

Input Voltage, Low (VIL) Full VI 0.7 V

Input Capacitance 25°C V 3 pF

DIGITAL OUTPUTS

Output Voltage, High (VOH) Full VI VDD − 0.1 V

Output Voltage, Low (VOL) Full VI 0.4 V

THERMAL CHARACTERISTICS

Thermal Resistance

θJC Junction-to-Case V 15.2 °C/W

θJA Junction-to-Ambient V 59 °C/W

Ambient Temperature Full V −25 +25 +85 °C

DC SPECIFICATIONS

Input Leakage Current (IIL) 25°C VI −10 +10 A

Input Clamp Voltage −16 mA 25°C V −0.8 V

+16 mA 25°C V +0.8 V

Differential High Level Output Voltage V AVCC V

Differential Output Short-Circuit Current IV 10 µA

POWER SUPPLY

VDD (All) Supply Voltage Full IV 1.71 1.8 1.89 V

VDD Supply Voltage Noise Full V 50 mV p-p

Power-Down Current 25°C IV 10 µA

Transmitter Supply Current

2

25°C IV 55 mA

Transmitter Total Power Full VI 100 mW

AC SPECIFICATIONS

CLK Frequency 25°C IV 13.5 80 MHz

TMDS Output CLK Duty Cycle 25°C IV 48 52 %

Worst Case CLK Input Jitter Full IV 2 ns

Input Data Setup Time Full IV 1 ns

Input Data Hold Time Full IV 1 ns

TMDS Differential Swing VI 800 1000 1200 mV

VSYNC and HSYNC Delay from DE Falling Edge VI 1 UI

VSYNC and HSYNC Delay to DE Rising Edge VI 1 UI

DE High Time 25°C VI 8191 UI

DE Low Time 25°C VI 138 UI

3

3

3

3

Differential Output Swing

Low-to-High Transition Time 25°C VII 75 490 Ps

High-to-Low Transition Time 25°C VII 75 490 Ps

AUDIO AC TIMING

Sample Rate I2S and S/PDIF Full IV 32 192 kHz

I2S Cycle Time 25°C IV 1 UI

3

I2S Setup Time 25°C IV 15 ns

I2S Hold Time 25°C IV 0 ns

Audio Pipeline Delay 25°C IV 75 µs

1

See the Explanation of Test Levels section.

2

Using low output drive strength.

3

UI = unit interval.

Rev. PrA | Page 3 of 12

Page 4

AD9387NK Preliminary Technical Data

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Digital Inputs 5 V to 0.0 V

Digital Output Current 20 mA

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Maximum Junction Temperature 150°C

Maximum Case Temperature 150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

EXPLANATION OF TEST LEVELS

I. 100% production tested.

II. 100% production tested at 25°C and sample tested at

specified temperatures.

III. Sample tested only.

IV. Parameter is guaranteed by design and characterization

testing.

V. Parameter is a typical value only.

VI. 100% production tested at 25°C; guaranteed by design

and characterization testing.

VII. Limits defined by HDMI specification; guaranteed by

design and characterization testing.

ESD CAUTION

Rev. PrA | Page 4 of 12

Page 5

Preliminary Technical Data AD9387NK

V

C

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

DGNDD1D2D3D4D5D6D7D8D9D10

646362616059585756555453525150

D11

D12

D13

D14

DVDD

49

DVDD

DE

HSYNC

SYN

CLK

S/PDIF

MCLK

2

I

2

I

2

I

2

I

SCLK

LRCLK

PVDD

PVDD

PIN 1

1

D0

S0

10

S1

11

S2

12

S3

13

14

15

16

INDICATOR

2

3

4

5

6

7

8

9

NOTES

1. GND PADDLE ON BOTTO M OF PACKAGE.

+

AD9387NK

TOP VIEW

(Not to S cale)

171819202122232425262728293031

HPD

Tx0–

Tx1–

Tx0+

TxC–

PVDD

TxC+

AVDD

AVDD

EXT_SWG

Tx1+

PD/A0

AVDD

Tx2–

Figure 2. 64-Lead LFCSP Pin Configuration (Top View)

Tx2+

48

DVDD

47

D15

46

D16

45

D17

44

D18

43

D19

42

D20

41

D21

40

D22

39

D23

38

MCL

37

MDA

36

SDA

35

SCL

34

DDCSDA

33

DDCSCL

32

INT

06507-002

10 8 7 6 3 2 1954

BOTTOM VIEW

(Not to Scale)

A

B

C

D

E

F

G

H

J

K

6507-003

Figure 3. 76-Ball BGA Configuration (Top View)

Table 3. Pin Function Descriptions

Pin No.

1

BGA LFCSP

A1 to A10,

B1 to B10, C9,

39 to 47,

50 to 63, 2

Mnemonic Type

D[23:0] I

Description

Video Data Input. Digital input in RGB or YCbCr format. Supports CMOS logic levels

from 1.8 V to 3.3 V.

C10, D9, D10

D1 6 CLK I Video Clock Input. Supports CMOS logic levels from 1.8 V to 3.3 V.

C2 3 DE I Data Enable Bit for Digital Video. Supports CMOS logic levels from 1.8 V to 3.3 V.

C1 4 HSYNC I Horizontal Sync Input. Supports CMOS logic levels from 1.8 V to 3.3 V.

D2 5 VSYNC I Vertical Sync Input. Supports CMOS logic levels from 1.8 V to 3.3 V.

J3 18 EXT_SWG I

Sets internal reference currents. Place 887 Ω resistor (1% tolerance) between this

pin and ground.

K3 20 HPD I

Hot Plug Detect Signal. This indicates to the interface if the receiver is

connected. Supports CMOS logic levels from 1.8 V to 5.0 V.

E2 7 S/PDIF I

S/PDIF (Sony/Philips Digital Interface) Audio Input. This is the audio input from a

Sony/Philips digital interface. Supports CMOS logic levels from 1.8 V to 3.3 V.

E1 8 MCLK I

Audio Reference Clock. 128 × N × f

frequency (f

), 256 × fS, 384 × fS, or 512 × fS. Supports CMOS logic levels from 1.8

S

with N = 1, 2, 3, or 4. Set to 128 × sampling

S

V to 3.3 V.

F2, F1, G2, G1 9 to 12 I2S[3:0] I

2

S Audio Data Inputs. These represent the eight channels of audio (two per

I

input) available through I

2

S. Supports CMOS logic levels from 1.8 V to 3.3 V.

H2 13 SCLK I I2S Audio Clock. Supports CMOS logic levels from 1.8 V to 3.3 V.

H1 14 LRCLK I Left/Right Channel Selection. Supports CMOS logic levels from 1.8 V to 3.3 V.

J7 26 PD/A0 I

Power-Down Control and I

2

C Address Selection. The I2C address and the PD

polarity are set by the PD/A0 pin state when the supplies are applied to the

AD9387NK. Supports CMOS logic levels from 1.8 V to 3.3 V.

K1, K2 21, 22 TxC−/TxC+ O

Differential Clock Output. Differential clock output at pixel clock rate; TMDS

logic level.

K10, J10 30, 31 Tx2−/Tx2+ O

Differential Output Channel 2. Differential output of the red data at 10× the pixel

clock rate; TMDS logic level.

Rev. PrA | Page 5 of 12

Page 6

AD9387NK Preliminary Technical Data

Pin No.

BGA LFCSP

Mnemonic Type

K7, K8 27, 28 Tx1−/Tx1+ O

K4, K5 24, 25 Tx0−/Tx0+ O

H10 32 INT O

J2, J5, J8, K9

D5, D6, D7, E7

G4, G5, J1

D4, E4, F4, J4,

G6, J6, K6, F7,

G7, H9, J9

19, 23, 29

1,48,49

15, 16, 17

64, Paddle

on bottom

side

AVDD P 1.8 V Power Supply for TMDS Outputs.

DVDD P

PVDD P

GND P

F9 36 SDA C

F10 35 SCL C

E10 37 MDA C

E9 38 MCL C

G9 34 DDCSDA C

G10 33 DDCSCL C

1

I = input, O = output, P = power supply, C = control.

2

For a full description of the 2-wire serial interface and its functionality, obtain documentation by contacting NDA from flatpanel_apps@analog.com.

1

Description

Differential Output Channel 1. Differential output of the green data at 10× the

pixel clock rate; TMDS logic level.

Differential Output Channel 0. Differential output of the blue data at 10× the

pixel clock rate; TMDS logic level.

Interrupt. Open drain. A 2 kΩ pull-up resistor to the microcontroller I/O supply is

recommended.

1.8 V Power Supply for Digital and I/O Power Supply. These pins supply power to

the digital logic and I/Os. They should be filtered and as quiet as possible.

1.8 V PLL Power Supply. The most sensitive portion of the AD9387NK is the clock

generation circuitry. These pins provide power to the clock PLL. The designer

should provide quiet, noise-free power to these pins.

Ground. The ground return for all circuitry on-chip. It is recommended that the

AD9387NK be assembled on a single, solid ground plane with careful attention

given to ground current paths.

2

Serial Port Data I/O. This pin serves as the serial port data I/O slave for register

access. Supports CMOS logic levels from 1.8V to 3.3V.

2

Serial Port Data Clock. This pin serves as the serial port data clock slave for

register access. Supports CMOS logic levels from 1.8V to 3.3V.

2

Serial Port Data I/O Master to HDCP Key EEPROM. Supports CMOS logic levels

from 1.8 V to 3.3 V.

2

Serial Port Data Clock Master to HDCP Key EEPROM. Supports CMOS logic levels

from 1.8 V to 3.3 V.

2

Serial Port Data I/O to Receiver. This pin serves as the master to the DDC bus.

Supports 5 V CMOS logic level.

2

Serial Port Data Clock to Receiver. This pin serves as the master clock for the DDC

bus. Supports 5 V CMOS logic level.

Rev. PrA | Page 6 of 12

Page 7

Preliminary Technical Data AD9387NK

APPLICATIONS INFORMATION

DESIGN RESOURCES

Analog Devices, Inc. evaluation kits, reference design schematics,

and other support documentation are available under NDA

flatpanel_apps@analog.com.

from

Other resources include the following:

• EIA/CEA-861D, a technical specifications document that

describes audio and video infoframes, as well as the E-EDID

structure for HDMI. It is available from the Consumer

Electronics Association (CEA).

• HDMI v. 1.3, a defining document for HDMI 1.3, and

HDMI Compliance Test Specification v. 1.3. They are

available from HDMI Licensing, LLC.

• HDCP Specification v1.1, the defining technical specifications

document for the HDCP v. 1.1. It is available from Digital

Content Protection, LLC.

DOCUMENT CONVENTIONS

In this data sheet, data is represented using the conventions

described in

Table 4. Document Conventions

Data

Type

0xNN

0bNN

NN

Bit

Tabl e 4.

Format

Hexadecimal (Base 16) numbers are represented using

the C language notation, preceded by 0x.

Binary (Base 2) numbers are represented using the C

language notation, preceded by 0b.

Decimal (Base 10) numbers are represented using no

additional prefixes or suffixes.

Bits are numbered in little endian format; that is, the

least significant bit of a byte or word is referred to as Bit 0.

Rev. PrA | Page 7 of 12

Page 8

AD9387NK

PCB LAYOUT RECOMMENDATIONS

The AD9387NK is a high precision, high speed analog device.

For maximum performance, it is important that board layout

be optimized.

Other Input Signals

The HPD must be connected to the HDMI connector. A 10 kΩ

pull-down resistor to ground is also recommended.

POWER SUPPLY BYPASSING

It is recommended that each power supply pin be bypassed

with a 0.1 µF capacitor. The exception is when two or more

supply pins are adjacent to each other. For these groupings of

powers and grounds, it is necessary to have only one bypass

capacitor. The fundamental idea is to have a bypass capacitor

within about 0.5 cm of each power pin. Avoid placing the

capacitor on the opposite side of the PC board from the

AD9387NK, as doing so interposes resistive vias in the path.

The bypass capacitors should be located between the power plane

and the power pin. Current should flow from the power plane

to the capacitor to the power pin. Do not make a power connection

between the capacitor and the power pin. Placing a via underneath

the capacitor pads, down to the power plane, is generally the

best approach.

It is particularly important to maintain low noise and good

stability of PVDD (the PLL supply). Abrupt changes in PVDD

can result in similarly abrupt changes in sampling clock phase

and frequency. Such changes can be avoided by careful attention

to regulation, filtering, and bypassing. It is best practice to provide

separate regulated supplies for each of the analog circuitry

groups (AVDD and PVDD).

It is also recommended that a single ground plane be used

for the entire board. Experience has repeatedly shown that

the noise performance is the same or better with a single

ground plane. Using multiple ground planes can be detrimental because each separate ground plane is smaller, and

long ground loops can result.

DIGITAL INPUTS

Video and Audio Data Input Signals

The digital inputs on the AD9387NK are designed to work with

signals ranging from 1.8 V to 3.3 V logic level. Therefore, no extra

components need to be added when using 3.3 V logic. Any

noise that gets onto the clock input (labeled CLK) trace adds

jitter to the system. Therefore, minimize the video clock input

(Pin 6, CLK) trace length, and do not run any digital or other

high frequency traces near it. Make sure to match the length of

the input data signals to optimize data capture, especially for

high frequency modes, such as 720p or XGA at 75 Hz and

double data rate input formats.

The PD/A0 input pin can be connected to GND or supply

(through a resistor or a control signal). The device address and

power-down polarity are set by the state of the PD/A0 pin when

the AD9387NK supplies are applied/enabled. For example, if

the PD/A0 pin is low (when the supplies are turned on), then

the device address is 0x72 and the power-down is active high.

If the PD/A0 pin is high (when the supplies are turned on),

the device address is 0x7A and the power down is active low.

2

The SCL and SDA pins should be connected to the I

A pull-up resistor of 2 k to 1.8 V or 3.3 V is recommended.

C master.

EXTERNAL SWING RESISTOR

The external swing resistor must be connected directly to the

EXT_SWG pin and ground. The external swing resistor must

have a value of 887 Ω (±1% tolerance). Avoid running any high

speed ac or noisy signals next to, or close to, the EXT_SWG pin.

OUTPUT SIGNALS

TMDS Output Signals

The AD9387NK has three TMDS data channels (0, 1, and 2)

that output signals up to 800 MHz, as well as the TMDS output

data clock. To minimize the channel-to-channel skew, make the

trace length of these signals the same. Also, these traces need

a 50 characteristic impedance and should be routed as 100

differential pairs. Best practice recommends routing these lines on

the top PCB layer, avoiding the use of vias.

Other Output Signals (non TMDS)

DDCSCL and DDCSDA

The DDCSCL and DDCSDA outputs need a minimum amount

of capacitance loading to ensure the best signal integrity. The

DDCSCL and DDCSDA capacitance loading must be less than

50 pF to meet the HDMI compliance specification. The DDCSCL

and DDCSDA must be connected to the HDMI connector, and

a pull-up resistor to 5 V is required. The pull-up resistor must

have a value between 1.5 kΩ and 2 kΩ.

INT Pin

The INT pin is an output that should be connected to the system

microcontroller. A pull-up resistor to 1.8 V or 3.3 V is required

for proper operation; the recommended value is 2 kΩ.

MCL and MDA

The MCL and MDA outputs should be connected to the EEPROM

containing the HDCP key (if HDCP is implemented). Pull-up

resistors of 2 kΩ are recommended.

Rev. PrA | Page 8 of 12

Page 9

Preliminary Technical Data AD9387NK

A

OUTLINE DIMENSIONS

0.30

0.25

0.18

PIN 1

64

INDICATOR

1

+

4.85

4.70 SQ*

4.55

BSC SQ

PIN 1

INDICATOR

VIEW

9.00

TOP

8.75

BSC SQ

0.60 MAX

49

48

0.60 MAX

EXPOSED PAD**

(BOTTOM VIEW)

1.00

0.85

0.80

12° MAX

SEATING

PLANE

0.45

0.40

0.35

0.80 MAX

0.65 TYP

0.50 BSC

64 LFCSP (LEAD FRAME CHIP SCALE PACKAGE)

*

COMPLIANT T O JEDEC STANDARDS M O -220-VMMD

EXCEPT FOR EXPOSED PAD DIMENSION

**Note: PAD is CONNECTED to GND

DIMENSIO N S in Millim e ters

0.20 REF

0.05 MAX

0.02 NOM

33

32

7.50

REF

16

17

Figure 4. 64-Lead Lead Frame Chip Scale Package [LFCSP]

(CP-64)

Dimensions shown in millimeters

6.10

*

1.40 MAX

6.00 SQ

5.90

BALL A1

PAD CORNER

TOP VIEW

DETAIL A

4.50

BSC SQ

0.15 MIN

BSC

0.50

0.75

REF

10 8 7 6

9

BOTTOM VIEW

DETAILA

1 CORNER

INDEX AREA

3

5

2

4

1

A

B

C

D

E

F

G

H

J

K

0.65 MIN

COPLANARITY

0.35

0.30

0.25

BALL DIAMET E R

*

COMPLIANT TO JEDEC STANDARDS MO-225

WITH THE EXCEPTION TO PACKAGE HE IGHT.

SEATING

PLANE

0.08 MAX

012006-0

Figure 5. 76-Ball Chip Scale Package Ball Grid Array [CSP_BGA]

6 mm × 6 mm × 1.4 mm

(BC-76)

Dimensions shown in millimeters

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD9387NKBCPZ-80

AD9387NKBBCZ-80

1

1

AD9387NKBBCZRL-80

AD9387NK/PCB Evaluation Board

1

Z = Pb-free part.

−25°C to +85°C 64-Lead Formed Chip Scale Package

−25°C to +85°C 76-Ball Chip Scale Package Ball Grid Array [CSP_BGA] BC-76

1

−25°C to +85°C 76-Ball Chip Scale Package Ball Grid Array [CSP_BGA] BC-76

Rev. PrA | Page 9 of 12

CP-64

Page 10

AD9387NK

NOTES

Rev. PrA | Page 10 of 12

Page 11

Preliminary Technical Data AD9387NK

NOTES

Rev. PrA | Page 11 of 12

Page 12

AD9387NK

NOTES

Purchase of licensed I2C components of Analog Devices or one of its sublicensed Associated Companies conveys a license for the purchaser under the Philips I2C Patent

Rights to use these components in an I

2

C system, provided that the system conforms to the I2C Standard Specification as defined by Philips.

©2006 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

PR06507-0-12/06(PrA)

Rev. PrA | Page 12 of 12

Loading...

Loading...