Page 1

10-Bit 40 MSPS

a

FEATURES

Low Power: 940 mW

53 dB SNR @ 10 MHz A

On-Chip T/H, Reference

CMOS-Compatible

2 V p-p Analog Input

Fully Characterized Dynamic Performance

APPLICATIONS

Ultrasound Medical Imaging

Digital Oscilloscopes

Professional Video

Digital Communications

Advanced Television (MUSE Decoders)

Instrumentation

GENERAL DESCRIPTION

The AD9040A is a complete 10-bit monolithic sampling analogto-digital converter (ADC) with on-board track-and-hold and

reference. The unit is designed for low cost, high performance

applications and requires only an encode signal to achieve

40 MSPS sample rates with 10-bit resolution.

Digital inputs and outputs are CMOS compatible; the analog

input requires a signal of 2 V p-p amplitude. The two-step

architecture used in the AD9040A is optimized to provide the

best dynamic performance available while maintaining low

power requirements of only 940 mW typically; maximum dissipation is 1.1 watt at 40 MSPS.

The signal-to-noise ratio (SNR), including harmonics, is 53 dB,

or 8.5 ENOB, when sampling an analog input of 10.3 MHz at

40 MSPS. Competitive devices perform at less than 7.5 ENOB

and require external references and larger input signals.

The AD9040A A/D converter is available as either a 28-lead

plastic DIP or a 28-lead SOIC. The two models operate over a

commercial temperature range of 0°C to +70°C. Contact the

factory regarding availability of ceramic military temperature

range devices.

IN

A/D Converter

AD9040A

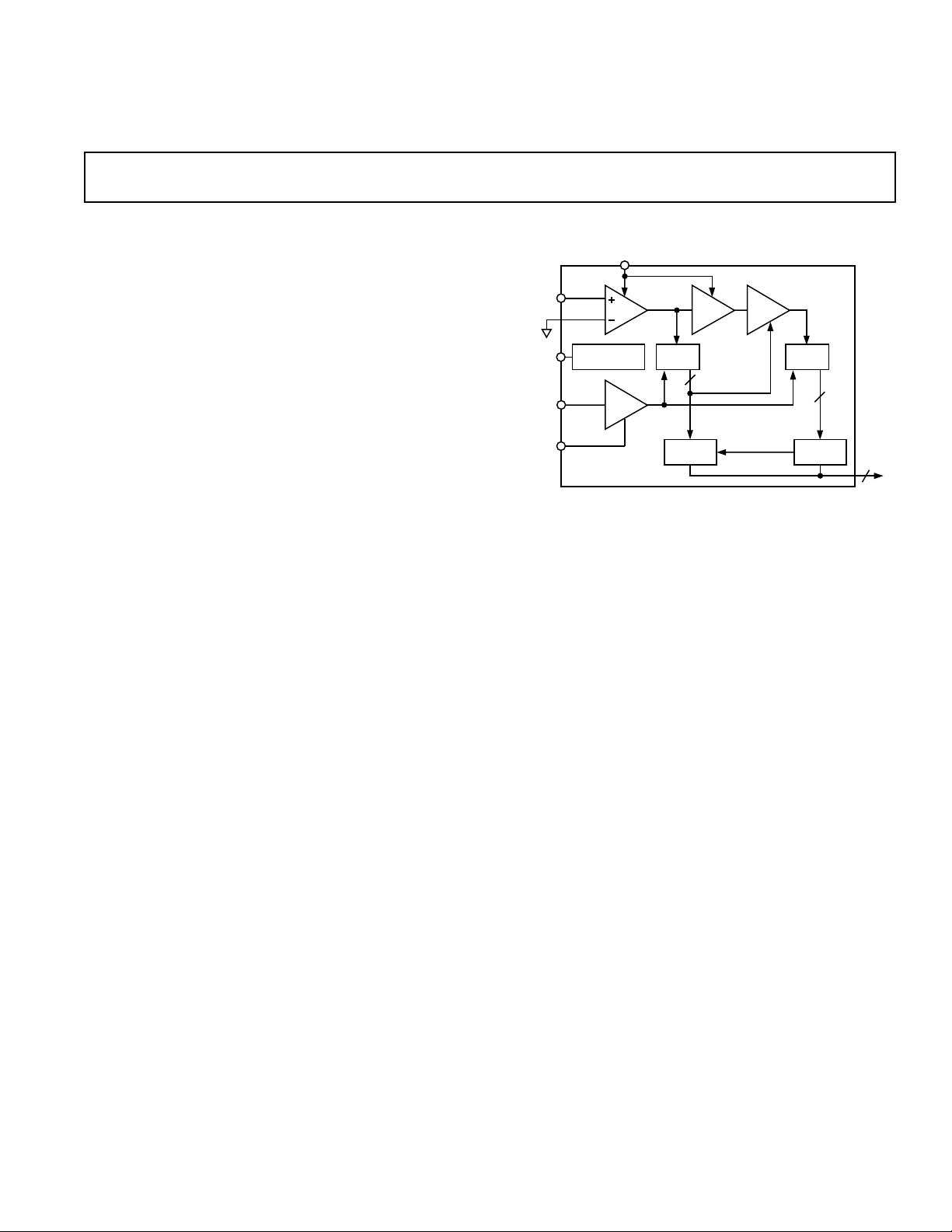

FUNCTIONAL BLOCK DIAGRAM

ENCODE

AMP

A

GND

BP

IN

V

OUT

V

REF

REF

T/H T/H

BANDGAP

REFERENCE

REF

AMP

AD9040A

5-BIT

ADC

DECODE

LOGIC

PRODUCT HIGHLIGHTS

1. CMOS compatible logic for direct interface to ASICs.

2. On-board T/H provides excellent high frequency performance on analog inputs, critical for communications and

medical imaging applications.

3. High input impedance and 2 volt p-p input range reduce

need for external amplifiers.

4. Easy to use; no cumbersome external voltage references

required, allowing denser packing of ADCs for multichannel

applications.

5. Available in 28-lead plastic DIP and SOIC packages.

6. Evaluation board includes AD9040AJR, reconstruction

DAC, and latches. Space is available near the analog input

and digital outputs of the converter for additional circuits.

Order as part number AD9040A/PCB (schematic shown in

data sheet).

ARRAY

ERROR

CORRECTION

6-BIT

ADC

DECODE

LOGIC

10

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

Page 2

AD9040A–SPECIFICATIONS

(+VS = VD = +5 V; –VS = –5 V; internal reference: ENCODE = 40.5 MSPS unless

ELECTRICAL CHARACTERISTICS

Parameter (Conditions) Temp Level Min Typ Max Units

RESOLUTION 10 Bits

DC ACCURACY

Differential Nonlinearity +25°C I 1.0 2.0 LSB

Integral Nonlinearity +25°C I 1.0 2.0 LSB

No Missing Codes Full VI Guaranteed

Gain Error +25°CI ±0.5 ±1.5 % FS

Gain Tempco

ANALOG INPUT

Input Voltage Range +25°C V 2 V p-p

Input Offset Voltage +25°CI ±2 ±25 mV

Input Bias Current +25°CI 7 15 µA

Input Resistance +25°C I 200 350 kΩ

Input Capacitance +25°CV 5 pF

Analog Bandwidth +25°C V 48 MHz

BANDGAP REFERENCE

Output Voltage Full VI 2.4 2.6 V

Temperature Coefficient

SWITCHING PERFORMANCE

Maximum Conversion Rate +25°C I 40 MSPS

Minimum Conversion Rate +25°C IV 2 10 MSPS

Aperture Delay (t

Aperture Uncertainty (Jitter) +25°C V 7 ps, rms

Output Propagation Delay (t

DYNAMIC PERFORMANCE

Transient Response +25°CV 25 ns

Overvoltage Recovery Time +25°CV 40 ns

Signal-to-Noise Ratio

f

= 2.3 MHz +25°C I 51 54 dB

IN

f

= 10.3 MHz +25°C I 50 53 dB

IN

Signal-to-Noise Ratio

(Without Harmonics)

f

IN

f

IN

Signal-to-Noise Ratio

f

= = 2.3 MHz +25°C I 52 56 dB

IN

f

= = 10.3 MHz +25°C I 51 55 dB

IN

Signal-to-Noise Ratio

(Without Harmonics)

f

IN

f

IN

2nd Harmonic Distortion

f

= 2.3 MHz +25°C I 56 67 dBc

IN

f

= 10.3 MHz +25°C I 56 65 dBc

IN

3rd Harmonic Distortion

f

= 2.3 MHz +25°C I 58 73 dBc

IN

f

= 10.3 MHz +25°C I 58 70 dBc

IN

Two-Tone Intermodulation +25°C V 62 dBc

Distortion Rejections

Differential Phase +25°C III 0.15 0.5 Degrees

Differential Gain +25°C III 0.25 1.0 %

1

1

) +25°C V 1.9 ns

A

2

)

PD

3

3

= 2.3 MHz +25°C I 52 55 dB

= 10.3 MHz +25°C I 51 54 dB

3, 4

3, 4

= 2.3 MHz +25°C I 53 57 dB

= 10.3 MHz +25°C I 53 56 dB

otherwise noted)

Test AD9040AJN/JR

Full VI 2.5 LSB

Full VI 2.5 LSB

Full VI ±2% FS

Full V ±70 ppm/°C

Full VI ±30 mV

Full VI 25 µA

Full V ±40 ppm/°C

+25°C I 7.5 10 12 ns

Full IV 6 14 ns

–2–

REV. B

Page 3

AD9040A

Test AD9040AJN/JR

Parameter (Conditions) Temp Level Min Typ Max Units

ENCODE INPUT

Logic “1” Voltage Full VI 4.0 V

Logic “0” Voltage Full VI 1.0 V

Logic “1” Current Full VI ±1 µA

Logic “0” Current Full VI ±1 µA

Input Capacitance +25°CV 14 pF

Encode Pulsewidth (High) (t

Encode Pulsewidth (Low) (tEL)

DIGITAL OUTPUTS

Logic “1” Voltage Full VI 4.95 V

Logic “0” Voltage Full VI 0.05 V

Output Coding Offset Binary

POWER SUPPLY

V

Supply Current Full VI 13 20 mA

D

+V

Supply Current Full VI 89 110 mA

S

–V

Supply Current Full VI 87 105 mA

S

Power Dissipation Full VI 0.94 1.2 W

Power Supply

Rejection Ratio (PSRR)

NOTES

1

“Gain Tempco” is for converter using internal reference; “Temperature

Coefficient” is for bandgap reference only.

2

Output propagation delay (tPD) is measured from the 50% point of the falling

edge of the encode command to the min/max voltage levels of the digital

outputs with 10 pF maximum loads.

3

RMS signal to rms noise with analog input signal 1 dB below full scale at

specified frequency.

4

ENCODE = 32 MSPS.

5

3rd order intermodulation measured with analog input frequencies of 2.3 MHz

and 2.4 MHz at 7 dB below full scale.

6

For rated performance at 40 MSPS, duty cycle of encode command should be

50% ±10%.

7

Measured as the ratio of the change in offset voltage for a 5% change in +V

or –VS.

Specifications subject to change without notice.

EXPLANATION OF TEST LEVELS

Test Level

I – 100% Production Tested.

II – 100% production tested at +25°C, and sample tested at

specified temperatures. AC testing done on sample basis.

III – Sample Tested Only.

IV – Parameter is guaranteed by design and characterization

testing.

V – Parameter is a typical value only.

VI – All devices are 100% production tested at +25°C. 100%

production tested at temperature extremes for military

temperature devices; guaranteed by design and character-

ization testing for industrial devices.

6

)

EH

6

7

+25°C IV 10 100 ns

+25°C IV 10 100 ns

+25°CI ±15 mV/V

ABSOLUTE MAXIMUM RATINGS

1

±VS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±7 V

V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +7 V

D

ANALOG IN . . . . . . . . . . . . . . . . . . . . . . . . . . . . –V

to +V

S

DIGITAL INPUTS . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to +V

V

Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to +V

REF

Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . . 20 mA

Operating Temperature

AD9040AJN/JR . . . . . . . . . . . . . . . . . . . . . . . .0°C to +70°C

S

Maximum Junction Temperature

Storage Temperature . . . . . . . . . . . . . . . . . –65°C to +150°C

2

(JN/JR Suffixes) . . . +150°C

Lead Soldering Temp (10 sec) . . . . . . . . . . . . . . . . . . . +300°C

NOTES

1

Absolute maximum ratings are limiting values to be applied individually, and

beyond which the serviceability of the circuit may be impaired. Functional

operability is not necessarily implied. Exposure to absolute maximum rating

conditions for an extended period of time may affect device reliability.

2

Typical thermal impedances (parts soldered to board):

N Package (Plastic DIP): θJA = 42°C/W; θJC = 10°C/W.

R Package (SOIC): θJA = 47°C/W; θJC = 10°C/W.

S

S

S

REV. B

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD9040AJN 0°C to +70°C 28-Lead Plastic DIP N-28

AD9040AJR 0°C to +70°C 28-Lead SOIC Package R-28

AD9040A/PWB Printed Circuit Board (Only) of Evaluation Circuit

AD9040A/PCB Complete Evaluation Board, Assembled and Tested,

Including AD9040AJR

–3–

Page 4

AD9040A

A

ENCODE

DIGITAL

OUTPUTS

N

IN

N + 1

t

A

tEHt

EL

t

PD

N – 3 N – 2 N – 1

#2 #3

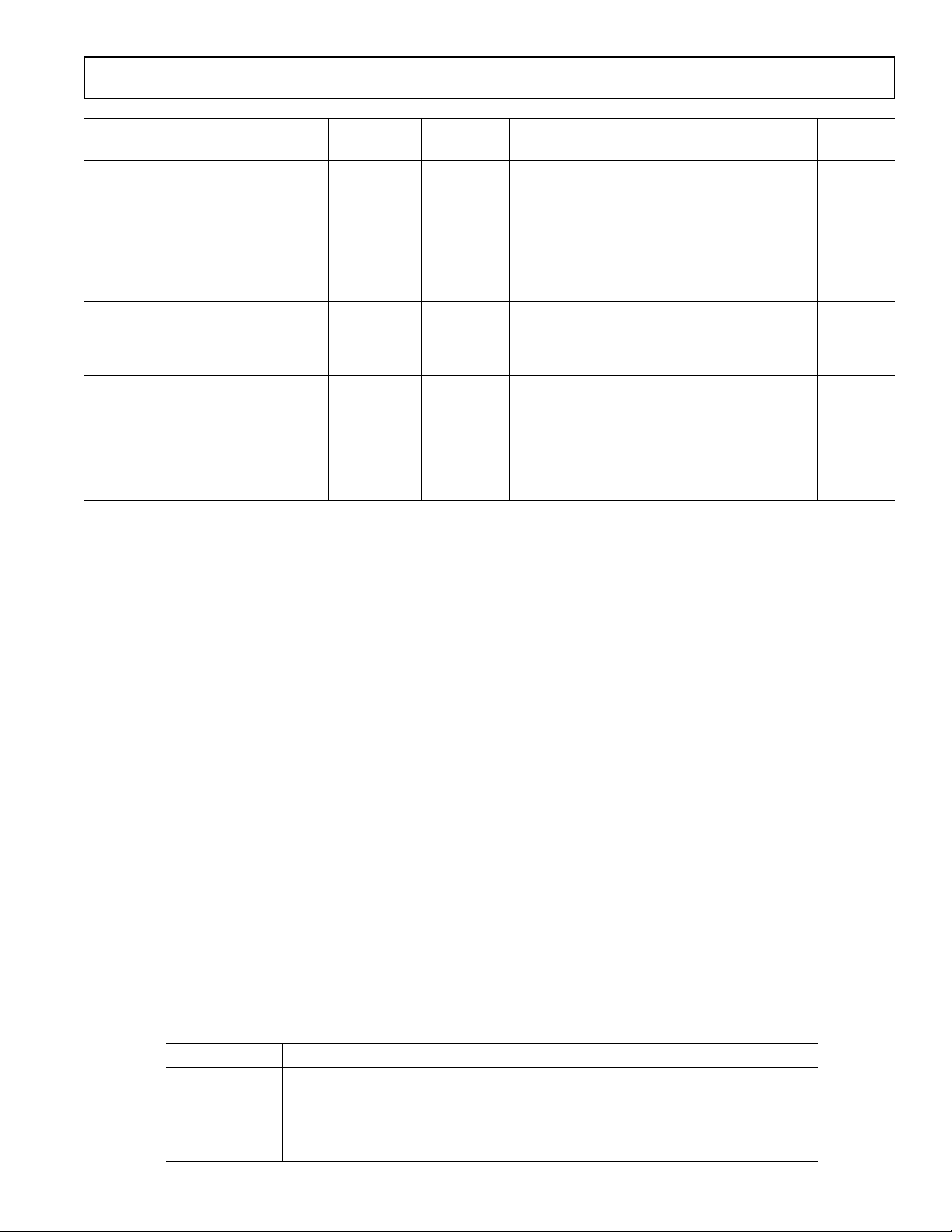

Figure 1. Timing Diagram

t

APERTURE DELAY

A

t

PULSEWIDTH HIGH

EH

t

PULSEWIDTH LOW

EL

OUTPUT PROP DELAY

t

PD

MIN TYP MAX

1.9

10

10 100

7.5

10ns

100

12

PIN FUNCTION DESCRIPTIONS

Pin No. Name Function

1, 12, 21 –V

S

5 V Power Supply

2, 4, 11, 14, 22 GND Ground

3, 10 +V

5V

S

OUT

Analog +5 V Power Supply

Internal Bandgap Voltage

Reference (Nominally +2.5 V)

6V

REF

Noninverting Input to Reference

Amplifier. Voltage reference for

ADC is connected here.

7BP

REF

External Connection for (0.1 µF)

Reference Bypass Capacitor

8 NC No Connection Internally

9 ENCODE Encode Clock Input to ADC.

Internal T/H placed in hold mode

(ADC is encoding) on rising edge.

13 A

IN

Noninverting Input to T/H

Amplifier

15 OR Out-of-Range Condition Output.

Active high when analog input

exceeds input range of ADC by

1 LSB (<FS –1 LSB or >+FS

+ 1 LSB).

16 D9 (MSB) Most Significant Bit of ADC

Output; TTL/CMOS Compatible

17–20 D8–D5 Digital Output Bits of ADC; TTL/

CMOS Compatible

23 V

D

Digital +5 V Power Supply

24–27 D4–D1 Digital Output Bits of ADC;

TTL/CMOSL Compatible

28 D0 (LSB) Least Significant Bit of ADC

Output; TTL/CMOS Compatible

–V

GND

+V

GND

V

OUT

V

REF

BP

REF

NC

ENCODE

+V

GND

–V

A

GND

1

S

2

3

S

4

5

6

AD9040A

7

TOP VIEW

(Not to Scale)

8

9

10

S

11

12

S

13

IN

14

NC = NO CONNECT

28

27

26

25

24

23

22

21

20

19

18

17

16

15

D0 (LSB)

D1

D2

D3

D4

V

D

GND

–V

S

D5

D6

D7

D8

D9 (MSB)

OR

PDIP and SOIC Pinouts

S

IN

GND

GND

–V

A

+V

S

ENCODE

NC

BP

REF

V

REF

V

OUT

GND

S

+V

D6

–V

DGND

D8

D7

D5

S

V

D

D4

D3

D2

D1

OR

D9 (MSB)

S

–V

D0 (LSB)

GND

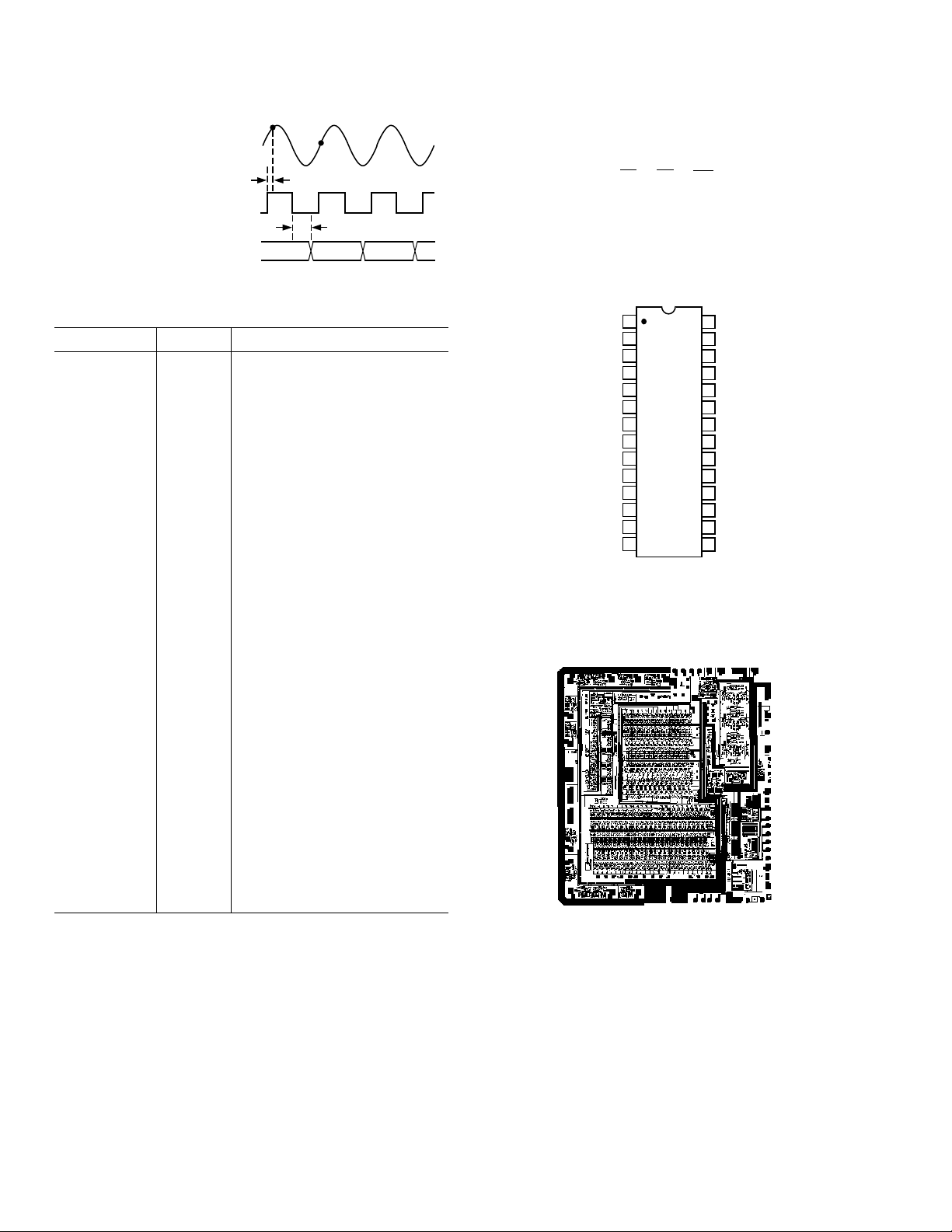

DIE LAYOUT AND MECHANICAL INFORMATION

Die Dimensions . . . . . . . . . . . . . . . . . 204 × 185 × 21 (±1) mils

Pad Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 × 4 mils

Metalization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Aluminum

Backing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . None

Substrate Potential . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .–V

Transistor Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5,070

Passivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Oxynitride

Die Attach (JN/JR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . Epoxy

Bond Wire (JN/JR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Gold

S

–4–

REV. B

Page 5

AD9040A

DEFINITIONS OF SPECIFICATIONS

Analog Bandwidth

The analog input frequency at which the spectral power of the

fundamental frequency (as determined by FFT analysis) is

reduced by 3 dB.

Aperture Delay

The delay between the rising edge of the ENCODE command

and the instant at which the analog input is sampled.

Aperture Uncertainty (Jitter)

The sample-to-sample variation in aperture delay.

Differential Gain

The percentage of amplitude change of a small high frequency

sine wave (3.58 MHz) superimposed on a low frequency signal

(15.734 kHz).

Differential Nonlinearity

The deviation of any code from an ideal 1 LSB step.

Differential Phase

The phase change of a small high frequency sine wave (3.58 MHz)

superimposed on a low frequency signal (15.734 kHz).

Harmonic Distortion

The rms value of the fundamental divided by the rms value of

the harmonic.

Integral Nonlinearity

The deviation of the transfer function from a reference line

measured in fractions of 1 LSB using a “best straight line” determined by a least square curve fit.

Minimum Conversion Rate

The encode rate at which the SNR of the lowest analog signal

frequency tested drops by no more than 3 dB below the guaranteed limit.

Maximum Conversion Rate

The encode rate at which parametric testing is performed.

Output Propagation Delay

The delay between the 50% point of the falling edge of the

ENCODE command and the 1 V/4 V points of output data.

Overvoltage Recovery Time

The amount of time required for the converter to recover to

10-bit accuracy after an analog input signal 150% of full scale is

reduced to the full-scale range of the converter.

Power Supply Rejection Ratio (PSRR)

The ratio of a change in input offset voltage to a change in

power supply voltage.

Signal-to-Noise Ratio (SNR)

The ratio of the rms signal amplitude to the rms value of

“noise,” which is defined as the sum of all other spectral components, including harmonics but excluding dc, with an analog

input signal 1 dB below full scale.

Signal-to-Noise Ratio (Without Harmonics)

The ratio of the rms signal amplitude to the rms value of

“noise,” which is defined as the sum of all other spectral components, excluding the first eight harmonics and dc, with an

analog input signal 1 dB below full scale.

Transient Response

The time required for the converter to achieve 10-bit accuracy

when a step function is applied to the analog input.

Two-Tone Intermodulation Distortion (IMD) Rejection

The ratio of the power of either of two input signals to the

power of the strongest third-order IMD signal.

A

IN

V

1kV

2kV

V

ANALOG INPUT

V

CC

CC

1kV

1mA1mA

SS

1kV

V

REF

GND

REFERENCE CIRCUIT

6.8kV

1kV

V

CC

GND

V

OUT

R

L

R

L

2.5kV

BP

REF

V

SS

BANDGAP OUTPUT

V

CC

GND

CMOS OUTPUT

D0-9

Figure 2. Equivalent Circuits

REV. B

–5–

Page 6

AD9040A

THEORY OF OPERATION

Refer to the block diagram.

The AD9040A employs subranging architecture and digital error

correction. This combination of design techniques insures true

10-bit accuracy at the digital outputs of the converter.

At the input, the analog signal is applied to a track-and-hold

(T/H) that holds the analog value which is present when the

unit is strobed with an ENCODE command. The conversion

process begins on the rising edge of this pulse, which should

have a 50% (±10%) duty cycle. Minimum encode rate of the

AD9040A is 10 MSPS because of the use of three internal T/H

devices.

The held analog value of the first track-and-hold is applied to a

5-bit flash converter and a pair of internal T/Hs (shown in the

block diagram as a single unit). The T/Hs pipeline the analog

signal to the amplifier array through a residue ladder and switch ing circuit while the 5-bit flash converter resolves the most

significant bits (MSBs) of the held analog voltage.

When the 5-bit flash converter has completed its cycle, its output activates 1-of-32 ladder switches; these, in turn, cause the

correct residue signal to be applied to the error amplifier array.

The output of the error amplifier is applied to a 6-bit flash converter whose output supplies the five least significant bits (LSBs)

of the digital output along with one bit of error correction for

the 5-bit main range converter.

Decode logic aligns the data from the two converters and presents the result as a 10-bit parallel digital word. The output

stage of the AD9040A is CMOS. Output data are strobed on

the trailing edge of the ENCODE command.

Full-scale range of the AD9040A is determined by the reference

voltage applied to the V

(Pin 6) input. This voltage sets the

RFF

internal flash and residue ladder voltage drops; these establish

the value of the LSB. Because of headroom restraints, the fullscale range cannot be increased by applying a higher-than

specified reference voltage. Conversely, a lower reference voltage will reduce the full-scale range of the converter, but will also

decrease its performance. An internal bandgap reference voltage

of +2.5 V is provided to assure optimum performance over the

operating temperature range.

USING THE AD9040A

Timing

The duty cycle of the encode clock for the AD9040A is critical

for obtaining rated performance of the ADC. Internal pulse

widths within the track-and-hold are established by the encode

command pulse width; to ensure rated performance, the duty

cycle should be held at 50%. Duty cycle variations of less than

±10% will cause no degradation in performance.

Operation at encode rates less than 10 MSPS is not recommended. The internal track-and-hold saturates, causing erroneous conversions. This T/H saturation precludes clocking the

AD9040A in burst mode. The 50% duty cycle must be maintained even for sample rates down to 10 MSPS.

The AD9040A provides latched data outputs, with 2 1/2 pipeline delays. Data outputs are available one propagation delay

(t

) after the falling edge of the encode command (refer to

PD

AD9040A Timing Diagram). The length of the output data

lines and the loads placed on them should be minimized to

reduce transients within the AD9040A; these transients can

detract from the converter’s dynamic performance.

Voltage Reference

A stable voltage reference is required to establish the 2-V p-p

range of the AD9040A. There are two options for creating this

reference. The easiest and least expensive way to implement it is

to use the (+2.5 V) bandgap voltage reference which is internal

to the ADC. Figure 3 illustrates the connections for using the

internal reference. The internal reference has 500 µA of extra

drive current which can be used for other circuits.

AD9040A

V

–V

0.1mF

S

BP

OUT

V

REF

REF

+2.5V

REF

AMP

BANDGAP

REFERENCE

REFERENCE

Figure 3. Using Internal Reference

Some applications may require greater accuracy, improved

temperature performance, or adjustment of the gain (input

range) of the AD9040A which cannot be obtained by using the

internal reference. For these applications, an external +2.5 V

reference can be used, as shown in Figure 4. The V

REF

input

requires 5 µA of drive current.

AD9040A

BANDGAP

REFERENCE

REF

AMP

REFERENCE

REFERENCE

–V

0.1mF

S

V

OUT

V

0.1mF

BP

REF

REF

Figure 4. Using External Reference

–6–

REV. B

Page 7

AD9040A

AD9040A

MARCONI 2030

SYNTHESIZER

REF

MARCONI 2030

SYNTHESIZER

REF

19.9609375 MHz

40 MHz

FLAT PULSE

NETWORK

SINE

TO

CMOS

ANALOG

IN

ENCODE

OUTPUT

In applications using multiple AD9040As, slaving the reference

inputs to a single reference output will improve gain tracking

among the ADCs, as shown in Figure 5.

AD9040A

V

OUT

V

0.1mF

REF

0.1mF

–V

S

AD9040A

V

0.1mF

REF

0.1mF

–V

S

AD9040A

V

0.1mF

REF

0.1mF

–V

S

Figure 5. Slaving Multiple AD9040As to a Single Internal

Reference

In the specifications table, the Gain Tempco parameter under

DC ACCURACY applies to the ADC when the internal reference is being used. If an external reference is used, its temperature coefficient must be taken into account to determine overall

temperature performance.

The input range can be varied by adjusting the reference voltage

applied to the AD9040A. By decreasing the reference voltage,

the gain can be reduced approximately 10% with no degradation in performance. Increasing the reference voltage increases

the gain; but for proper operation, the reference voltage should

not exceed +2.6 V.

Time-Gain Control ADC

Ultrasound and sonar systems require an increase in gain versus

time. This allows the system to correct for attenuation of return

pulses. Figure 6 shows the AD600/AD602 amplifier and the

AD9040A ADC configured as a time-gain control analog-todigital converter. The control voltage ramps from –625 mV to

+625 mV, permitting 40 dB of gain-control range. The voltage

used for gain control can be either a linear ramp, or the output

of a voltage-output DAC such as the AD7242.

GAIN CONTROL

–625mV

A

IN

VOLTAGE

AD600/602

+625mV

AD9040A

Figure 6. Ultrasound/Sonar Time-Gain Control ADC

Using X-AMPs™

Transient Response

Figure 7 illustrates the method for evaluating ADC transient

performance. Two synthesizers are locked in synchronization,

but tuned to frequencies which are slightly offset from a 2-to-1

submultiple.

One synthesizer clocks a flat pulse network at a frequency of

19.9609375 MHz to provide the analog input signal; the other

synthesizer output is shaped to provide a CMOS 40 MHz sampling clock. At the output of the AD9040A, output data reflects

an interleaved alias of the input pulse. The repetitive sampling

allows the measurement of ADC transient response as shown in

performance graphs elsewhere in this data sheet.

REV. B

Figure 7. Transient Response Test

X-AMP is a trademark of Analog Devices, Inc.

–7–

Page 8

AD9040A

Layout Information

Preserving the accuracy and dynamic performance of the

AD9040A requires that designers pay special attention to the

layout of the printed circuit board.

Analog paths should be kept as short as possible and be properly

terminated to avoid reflections. The analog input and reference

voltage connections should be kept away from digital signal

paths; this reduces the amount of digital switching noise which

is capacitively coupled into the analog section. Digital signal

paths should also be kept short, and run lengths should be

matched to avoid propagation delay mismatch. The AD9040A

digital outputs should be buffered or latched close to the device

(<2 cm). This prevents load transients which may feedback into

the device.

In high speed circuits, layout of the ground is critical. A single,

low impedance ground plane on the component side of the

board is recommended. Power supplies should be capacitively

coupled to the ground plane with high quality chip capacitors to

reduce noise in the circuit. Multilayer boards allow designers to

lay out signal traces without interrupting the ground plane, and

provide low impedance ground planes. In systems with dedicated analog and digital grounds, all grounds of the AD9040A

should be connected to the analog ground plane.

The power supplies of the AD9040A should be isolated from

the supplies used for external devices; this reduces the amount

of noise coupled into the ADC. The digital +5 volt connection

of the device (V

be connected to the same supply as +V

necting V

, Pin 23) powers the digital outputs and should

D

to a system digital supply may couple noise into the

D

(Pins 3 and 10). Con-

S

device. Sockets limit dynamic performance and are not recommended for use with the AD9040A.

performance without (or prior to) developing a user-specific

printed circuit board. The two-sided board includes a reconstruction DAC and digital output interface, and uses the layout

and applications suggestions outlined above. It is available from

Analog Devices at nominal cost.

Generous space is provided near the analog input and digital

outputs to support additional signal processing components the

user may wish to add. This prototyping area includes through

holes with 100-mil centers to support a variety of component

additions.

Input/Output/Supply Information

Power supply, analog input, clock connections, and reconstructed output (RC OUTPUT) are identified by labels on the

evaluation board. Operation of the evaluation board should

conform to the following characteristics:

Table I. Evaluation Board Characteristics

Parameter Typical Units

Supply Current

+5 V 250 mA

–5.2 V 300 mA

A

IN

Impedance 51 Ω

Voltage Range ±1.0 V

CLOCK

Impedance 51 Ω

Frequency 40 MSPS

RC OUTPUT

Impedance 51 Ω

Voltage Range 0 V to –1 V V

EVALUATION BOARD

The evaluation board for the AD9040A (AD9040A/PCB) provides an easy and flexible method for evaluating the ADC’s

Analog Input

Analog input signals can be fed directly into the Device Under

Test input (A

). The AIN input is terminated at the device with

IN

a 51 Ω resistor.

–8–

REV. B

Page 9

AD9040A

Figure 8. PCB Top View

DAC Reconstruction

The AD9040A evaluation board provides an onboard AD9721

reconstruction DAC for observing the digitized analog input

signal. The AD9721 is terminated into 51 ohms to provide a

1 V p-p signal at the output (RC OUTPUT).

Output Data

The output data bits are latched with a CMOS 74AC574 which

drives a 40-pin connector (AMP p/n 102153-9). The data and

clock signals are available on the connector per the pin assignments shown on the schematic of the evaluation board. Output

data are available on the falling edge of the clock.

Figure 9. PCB Bottom View

Table II. Digital Coding

Analog Voltage Out-ofInput Level Range Digital Output

MSB . . . LSB

+1.002 V Positive Full Scale + 1 LSB 1 1111111111

+1 V

+1/2 V

0 V Bipolar Zero

–1/2 V

–1 V

–1.002 V Negative Full Scale – 1 LSB 1 0000000000

Positive Full Scale 0 1111111111

Full Scale – 1 LSB 0 1111111110

Positive 1/2 Scale 0 1100000000

1/2 Scale – 1 LSB 0 1011111111

0 10000000000

0

1/2 Scale + 1 LSB 0 0100000000

Negative 1/2 Scale 0 0011111111

Full Scale + 1 LSB 0 0000000001

Negative Full Scale 0 0000000000

01111111111

REV. B

–9–

Page 10

AD9040A

AIN

BNC

J1

R1

51V

BNC

J2

R2

51V

CLK

J7

J8

J9

+5V

C2

0.1mF

C4

0.1mF

U1

74HC86

9

74HC86

1

2

74HC86

4

5

74HC86

C3

10mF

C5

10mF

U1

U1

U1

–5V

8

3

6

11

CLK

+5V

–5V

GND

–5V

C14

0.1mF

10

+5V

12

13

C7

0.1mFC80.1mFC90.1mF

–5V

–5V

–5V

+5V

+5V

+5V

GND

GND

GND

GND

GND

C1

0.1mF

AD9040AJR

A

IN

V

REF

V

OUT

ENC

–V

S

–V

S

–V

S

+V

S

+V

S

+V

D

GND

GND

GND

GND

GND

BPREF

C15

0.1mF

C10

0.1mF

U2

(MSB)

OR

D9

D7

D3

D2

D0

(LSB)

NC

C16

0.1mF

C11

0.1mF

U4

74AC574

2

3

4

5

6

7

8

9

D8

D6

D5

D4

D1

C17

0.1mF

C12

0.1mF

9

8

7

6

5

4

3

2

1D

1Q

2D

2Q

3D

3Q

4D

4Q

5D

5Q

6D

6Q

7D

7Q

8D

8Q

CK

OE

11

U3

74AC574

8D

7D

6D

5D

4D

3D

2D

1D

CK

OE

11

C13

0.1mF

C18

0.1mF

8Q

7Q

6Q

5Q

4Q

3Q

2Q

1Q

19

18

17

E1

16

15

14

13

12

1

12

13

14

15

16

17

18

19

1

CLK

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

H40DMC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

R18 100V

R17 100V

R16 100V

R15 100V

R14 100V

R13 100V

R12 100V

R11 100V

R10 100V

R9 100V

J3

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AD9721BR

D1 (MSB)

D2

D3

D4

D5

D6

D7

D8

D9

D10 (LSB)

CLOCK

INVERT

H3#4H4

U5

GND

–5V

–5V

GND

CAMP IN

REF OUT

CAMP OUT

REF IN

IOUT

IOUT

ANA RET

RSET

–5V

GND

+5V

H5#4H6

#4

GND

–5V

–5V

GND

C21

10mF

–5V

–5V

C6

0.1mF

R6

51V

R5

51V

–5V

GND

+5V

#4

H1 H2

R7

2kV

RC

OUTPUT

BNC

J5

Figure 10. PCB Schematic

–10–

REV. B

Page 11

1.2

1.0

0.8

0.6

DISSIPATION – Watts

0.4

1 2 4 6 10 20 40 60

CLOCK RATE – MSPS

Figure 11. Power Dissipation vs.

Clock Rate

–73

ENCODE = 40.5 MSPS

HARMONIC

–68

DISTORTION

–63

SNR

–58

–53

HARMONIC DISTORTION – dBc

–48

1 10 100246 204060

FREQUENCY – MHz

Figure 12. Harmonic Distortion

and SNR vs. Analog Input

66

60

54

48

42

66

60

54

48

42

SIGNAL-TO-NOISE RATIO – dB

SIGNAL-TO-NOISE RATIO – dB

Figure 13. SNR vs. Clock Rate

AD9040A

A = 10.3 MHz

IN

CLOCK RATE – MSPS

362820124

1.0

0.5

LEAST SIGNIFICANT BITS – LSBs

0

CLOCK RATE – MSPS

Figure 14. Differential Nonlinearity

vs. Clock Rate

60

ENCODE = 32.2 MSPS

55

50

45

SIGNAL-TO-NOISE RATIO – dB

40

–55

ENCODE = 40.5 MSPS

AIN = 10.3 MHz

85 1056545255–15–35

TEMPERATURE – 8C

Figure 17. SNR vs. Temperature

400302010

125

1024

896

768

640

512

384

256

128

AD9040A DIGITAL OUTPUT CODE

0

51015 202530354045500

TIME – ns

Figure 15. Transient Response

0

–65

dBc

0 8.0 16.1

ENCODE = 32.2 MSPS

ANALOG IN = 2.3 MHz

SNR = 56.79 dB

SNR (w/o har.) = 57.58 dB

2nd HARMONIC = –68.5 dB

3rd HARMONIC = 80.7 dB

FREQUENCY – MHz

Figure 18.

1024

992

960

928

96

64

32

AD9040A DIGITAL OUTPUT CODE

0

51015202530354045500

TIME – ns

Figure 16. Transient Response

(Expanded View)

0

ENCODE = 32.2 MSPS

ANALOG IN = 10.3 MHZ

SNR = 55.37 dB

SNR (w/o har.) = 56.77 dB

2nd HARMONIC = –63.3 dB

3rd HARMONIC = –75.4 dB

–65

dBc

0 8.0

8.0

FREQUENCY – MHz

Figure 19.

16.1

0

–65

dBc

0 2.5 5.0

FREQUENCY – MHz

ENCODE = 40.5 MSPS

f1 IN = 2.25 MHz @ –7 dBFS

f2 IN = 2.35 MHz @ –7 dBFS

2f1 – f2 = –69.4 dBFS

2f2 – f1 = –69.2 dBFS

Figure 20.

REV. B

0

–65

dBc

0 10.1 20.2

ENCODE = 40.5 MSPS

ANALOG IN = 2.3 MHz

SNR = 55.20 dB

SNR (w/o har.) = 55.90 dB

2nd HARMONIC = –75.1 dB

3rd HARMONIC = –73.2 dB

FREQUENCY – MHz

Figure 21.

–11–

0

–65

dBc

0 10.1

ENCODE = 40.5 MSPS

ANALOG IN = 10.3 MHz

SNR = 53.38 dB

SNR (w/o har.) = 54.31 dB

2nd HARMONIC = –64.7 dB

3rd HARMONIC = –73.7 dB

FREQUENCY – MHz

Figure 22.

20.2

Page 12

AD9040A

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm)

0.250

(6.35)

MAX

28-Lead Plastic DIP

(N-28)

1.565 (39.70)

1.380 (35.10)

28

1

PIN 1

0.022 (0.558)

0.014 (0.356)

0.625 (15.87)

0.600 (15.24)

0.100

(2.54)

BSC

0.015 (0.381)

0.008 (0.204)

0.070

(1.77)

MAX

15

0.550 (13.97)

0.530 (13.46)

14

0.015 (0.38)

MIN

SEATING

PLANE

0.140

(3.55)

MIN

28-Lead SOIC Package

(R-28)

14 1

0.712 (18.08)

0.700 (17.78)

0.012 (0.30)

0.004 (0.10)

0.013 (0.33)

0.009 (0.23)

0.050

(1.27)

BSC

0.019 (0.48)

0.014 (0.36)

PIN 1

2815

0.04 (1.02)

0.024 (0.61)

0.300 (7.60)

0.292 (7.40)

0.419 (10.64)

0.104 (2.64)

0.093 (2.36)

0.393 (9.98)

C1835a–0–5/99

–12–

PRINTED IN U.S.A.

REV. B

Loading...

Loading...