Page 1

CMOS Single Supply

SDA

SDB

5

6

V–

+IN B

4

7

OUT A

–IN A

+IN A

V+

OUT B

1

2

3

10

9

8

–IN B

AD8592

(Not to Scale)

TOP VIEW

(Not to Scale)

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

NC = NO CONNECT

OUT A

2IN A

V1

1IN A

1IN B

2IN B

OUT B

NC

OUT D

2IN D

1IN D

V2

1IN C

2IN C

OUT C

SD

AD8594

Rail-to-Rail Input/Output

a

FEATURES

Single Supply Operation: +2.5 V to +6 V

High Output Current: ⴞ250 mA

Extremely Low Shutdown Supply Current: 100 nA

Low Supply Current: 750 A/Amp

Wide Bandwidth: 3 MHz

Slew Rate: 5 V/s

No Phase Reversal

Very Low Input Bias Current

High Impedance Outputs When in Shutdown Mode

Unity Gain Stable

APPLICATIONS

Mobile Communication Handset Audio

PC Audio

PCMCIA/Modem Line Driving

Battery Powered Instrumentation

Data Acquisition

ASIC Input or Output Amplifier

LCD Display Reference Level Driver

GENERAL DESCRIPTION

The AD8591, AD8592 and AD8594 are single, dual and quad

rail-to-rail input and output single supply amplifiers featuring

250 mA output drive current and a power saving shutdown

mode. The AD8592 includes an independent shutdown function for each amplifier. When both amplifiers are in shutdown

mode the total supply current is reduced to less than 1 µA. The

AD8591 and AD8594 include a single master shutdown func-

tion that reduces total supply current to less than 1 µA. All

amplifier outputs are in a high impedance state when in shutdown mode.

These amplifiers have very low input bias currents, making them

suitable for integrators and diode amplification. Outputs are

stable with virtually any capacitive load. Supply current is less

than 750 µA per amplifier in active mode.

Applications for these amplifiers include audio amplification for

portable computers, portable phone headsets, sound ports, sound

cards and set-top boxes. The AD859x family is capable of driving

heavy capacitive loads such as LCD panel reference levels.

The ability to swing rail-to-rail at both the input and output

enables designers to buffer CMOS DACs, ASICs and other

wide output swing devices in single supply systems.

The AD8591, AD8592 and AD8594 are specified over the indus-

trial (–40°C to +85°C) temperature range. The AD8591, single,

is available in the tiny 6-lead SOT package. The AD8592, dual, is

available in the 10-lead µSOIC surface mount package. The

AD8594, quad, is available in 16-lead narrow SOIC and 16-lead

TSSOP packages.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

Operational Amplifiers with Shutdown

AD8591/AD8592/AD8594

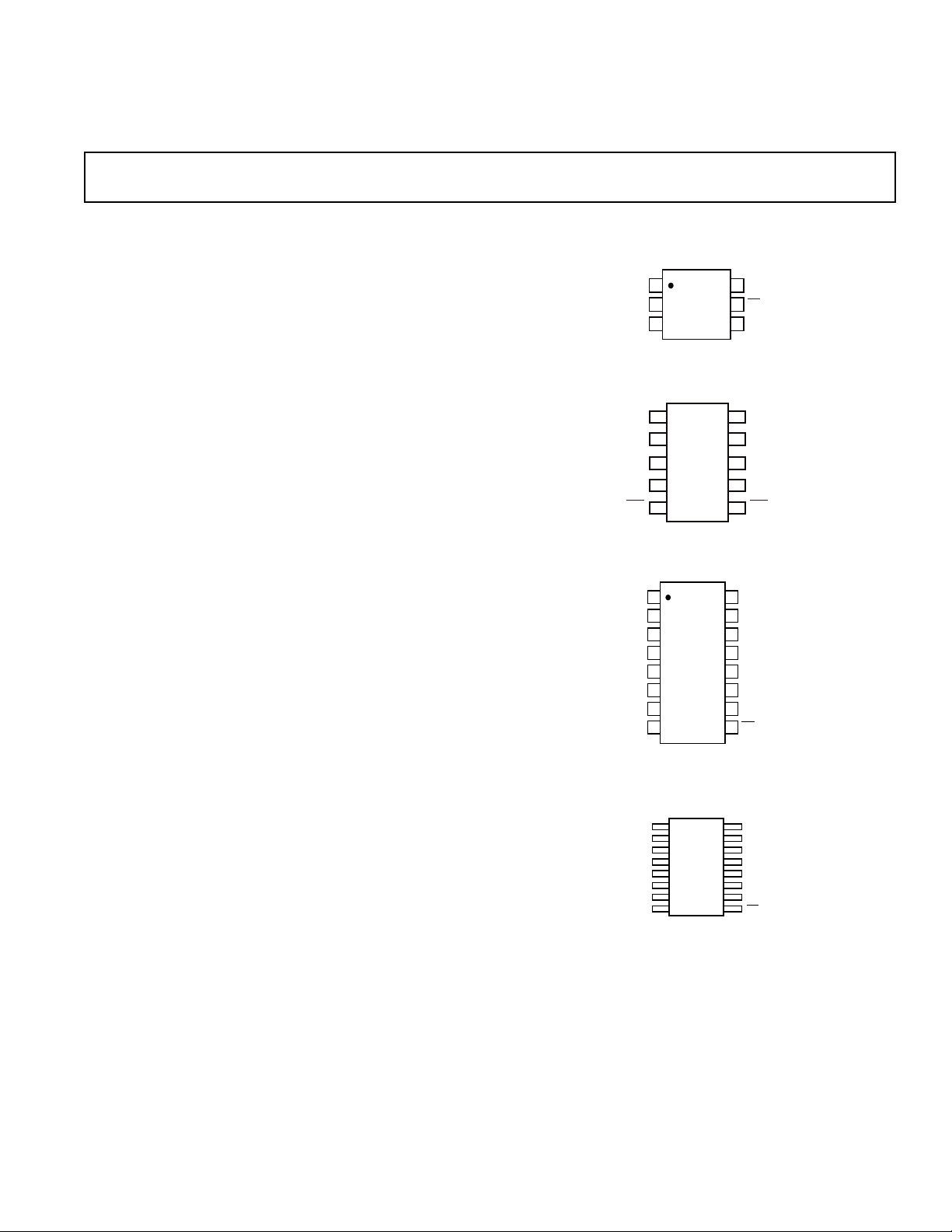

PIN CONFIGURATIONS

6-Lead SOT

(RT Suffix)

1

OUT A

2

V2

AD8591

3

1IN A

10-Lead SOIC

(RM Suffix)

16-Lead Narrow SOIC

(R Suffix)

16-Lead TSSOP

(RU Suffix)

1

OUT A

2IN A

1IN A

1IN B

2IN B

OUT B

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

1

V1

AD8594

89

NC

NC = NO CONNECT

6

V1

5

SD

2IN A

4

OUT D

16

2IN D

1IN D

V2

+IN C

2IN C

OUT C

SD

Page 2

AD8591/AD8592/AD8594–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

(VS = +2.7 V, VCM = +1.35 V, TA = +25ⴗC unless otherwise noted)

Parameter Symbol Conditions Min Typ Max Units

INPUT CHARACTERISTICS␣

Offset Voltage V

Input Bias Current I

Input Offset Current I

B

OS

OS

–40°C < T

–40°C < T

–40°C < T

< +85°C30mV

A

< +85°C60pA

A

< +85°C30pA

A

25 mV

550 pA

125 pA

Input Voltage Range 0 +2.7 V

Common-Mode Rejection Ratio CMRR V

Large Signal Voltage Gain A

Offset Voltage Drift ∆V

Bias Current Drift ∆I

VO

/∆T20µV/°C

OS

/∆T 50 fA/°C

B

= 0 V to +2.7 V 38 45 dB

CM

R

= 2 kΩ , V

L

= +0.3 V to +2.4 V 25 V/mV

O

Offset Current Drift ∆IOS/∆T 20 fA/°C

OUTPUT CHARACTERISTICS

Output Voltage High V

OH

IL = 10 mA +2.55 +2.61 V

–40°C to +85°C +2.5 V

Output Voltage Low V

OL

IL = 10 mA 60 100 mV

–40°C to +85°C 125 mV

Output Current I

Open-Loop Impedance Z

OUT

OUT

f = 1 MHz, A

= 1 60 Ω

V

±250 mA

POWER SUPPLY␣

Power Supply Rejection Ratio PSRR VS = +2.5 V to +6 V 45 55 dB

Supply Current/Amplifier I

Supply Current Shutdown Mode I

I

I

SY

SD

SD1

SD2

VO = 0 V 1 mA

–40°C < T

< +85°C 1.25 mA

A

All Amplifiers Shut Down 0.1 1 µA

–40°C < T

< +85°C1µA

A

Amplifier 1 Shut Down (AD8592) 1.4 mA

Amplifier 2 Shut Down (AD8592) 1.4 mA

SHUTDOWN INPUTS

Logic High Voltage V

Logic Low Voltage V

Logic Input Current I

INH

INL

IN

–40°C < TA < +85°C +1.6 V

–40°C < TA < +85°C +0.5 V

–40°C < TA < +85°C1µA

DYNAMIC PERFORMANCE␣

Slew Rate SR R

Settling Time t

S

= 2 kΩ 3.5 V/µs

L

To 0.01% 1.4 µs

Gain Bandwidth Product GBP 2.2 MHz

Phase Margin Φo 67 Degrees

Channel Separation CS f = 1 kHz, R

= 2 kΩ 65 dB

L

NOISE PERFORMANCE␣

Voltage Noise Density e

n

f = 1 kHz 45 nV/√Hz

f = 10 kHz 30 nV/√Hz

Current Noise Density i

Specifications subject to change without notice.

n

f = 1 kHz 0.05 pA/√Hz

–2–

REV. A

Page 3

AD8591/AD8592/AD8594

ELECTRICAL CHARACTERISTICS

(VS = +5.0 V, VCM = +2.5 V, TA = +25ⴗC unless otherwise noted)

Parameter Symbol Conditions Min Typ Max Units

INPUT CHARACTERISTICS␣

Offset Voltage V

Input Bias Current I

Input Offset Current I

B

OS

OS

–40°C < T

–40°C < T

–40°C < T

< +85°C30mV

A

< +85°C60pA

A

< +85°C30pA

A

225 mV

550 pA

125 pA

Input Voltage Range 0+5V

Common-Mode Rejection Ratio CMRR V

Large Signal Voltage Gain A

Offset Voltage Drift ∆V

Bias Current Drift ∆I

VO

/∆T –40°C < TA < +85°C20µV/°C

OS

/∆T 50 fA/°C

B

= 0 V to +5 V 38 47 dB

CM

R

= 2 kΩ , V

L

= +0.5 V to +4.5 V 15 30 V/mV

O

Offset Current Drift ∆IOS/∆T 20 fA/°C

OUTPUT CHARACTERISTICS

Output Voltage High V

OH

IL = 10 mA +4.9 +4.94 V

–40°C to +85°C +4.85 V

Output Voltage Low V

OL

IL = 10 mA 50 100 mV

–40°C to +85°C 125 mV

Output Current I

Open-Loop Impedance Z

OUT

OUT

f = 1 MHz, A

= 1 40 Ω

V

±250 mA

POWER SUPPLY␣

Power Supply Rejection Ratio PSRR VS = +2.5 V to +6 V 45 55 dB

Supply Current/Amplifier I

Supply Current-Shutdown Mode I

I

I

SY

SD

SD1

SD2

VO = 0 V 1.25 mA

–40°C < T

< +85°C 1.75 mA

A

All Amplifiers Shut Down 0.1 1 µA

–40°C < T

< +85°C1µA

A

Amplifier 1 Shut Down (AD8592) 1.6 mA

Amplifier 2 Shut Down (AD8592) 1.6 mA

SHUTDOWN INPUTS

Logic High Voltage V

Logic Low Voltage V

Logic Input Current I

INH

INL

IN

–40°C < TA < +85°C +2.4 V

–40°C < TA < +85°C +0.8 V

–40°C < TA < +85°C1µA

DYNAMIC PERFORMANCE␣

Slew Rate SR R

Full-Power Bandwidth BW

Settling Time t

P

S

= 2 kΩ 5V/µs

L

1% Distortion 325 kHz

To 0.01% 1.6 µs

Gain Bandwidth Product GBP 3 MHz

Phase Margin Φo 70 Degrees

Channel Separation CS f = 1 kHz, R

= 10 kΩ 65 dB

L

NOISE PERFORMANCE␣

Voltage Noise Density e

n

f = 1 kHz 45 nV/√Hz

f = 10 kHz 30 nV/√Hz

Current Noise Density i

Specifications subject to change without notice.

n

f = 1 kHz 0.05 pA/√Hz

–3–REV. A

Page 4

AD8591/AD8592/AD8594

WARNING!

ESD SENSITIVE DEVICE

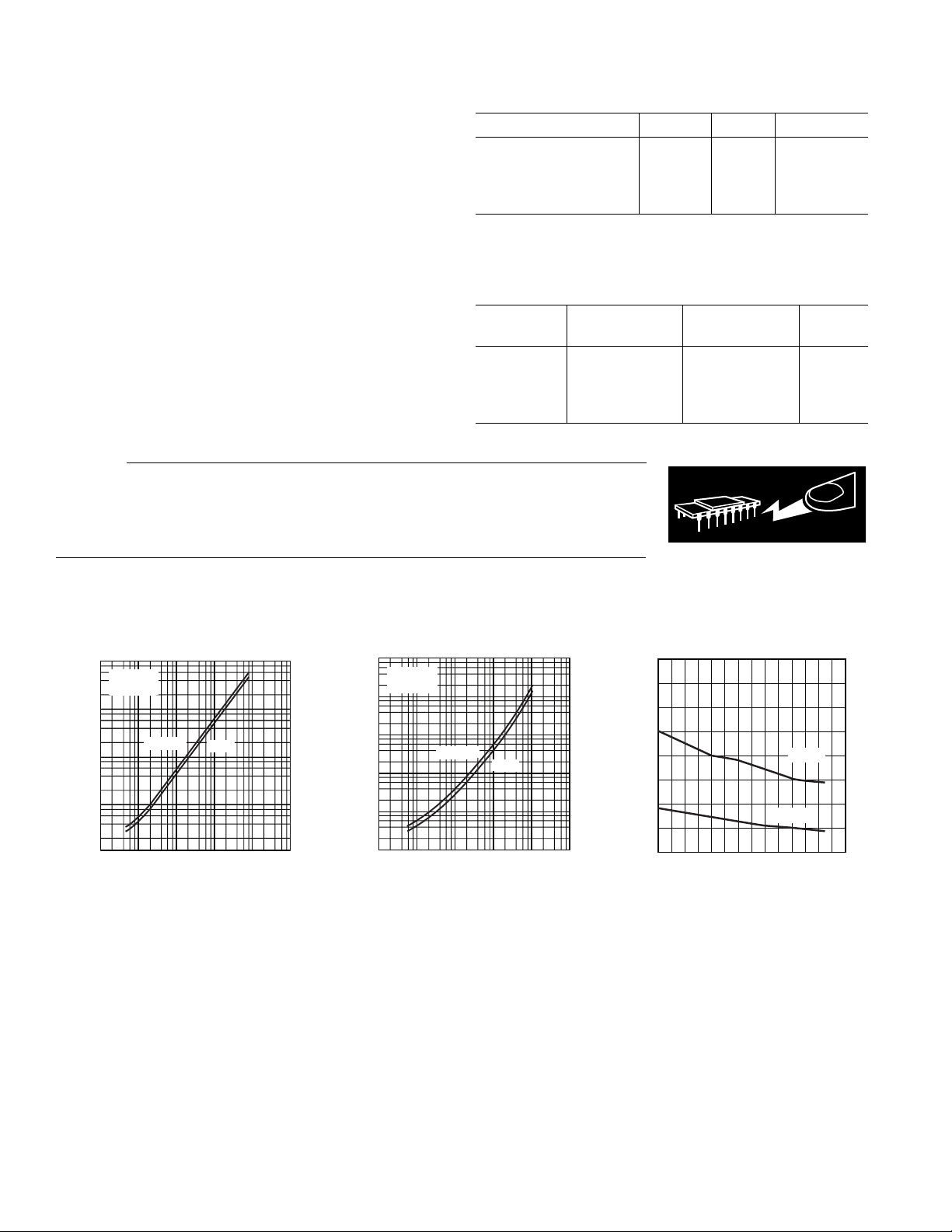

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +6 V

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND to V

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . ±6 V

Output Short Circuit

Duration to GND

2

. . . . . . . . . . . . Observe Derating Curves

Storage Temperature Range

R, RT, RM, RU Packages . . . . . . . . . . . . –65°C to +150°C

Operating Temperature Range

AD8591/AD8592/AD8594 . . . . . . . . . . . . –40°C to +85°C

Junction Temperature Range

R, RT, RM, RU Packages . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering, 60 sec) . . . . . . . +300°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational sections

of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2

For supplies less than ±5 V the differential input voltage is limited to the supplies.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD8591/AD8592/AD8594 features proprietary ESD protection circuitry, permanent damage

may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

1

Package Type

6-Lead SOT-23 (RT) 230 92 °C/W

S

10-Lead µSOIC (RM) 200 44 °C/W

16-Lead SOIC (R) 120 36 °C/W

16-Lead TSSOP (RU) 180 35 °C/W

NOTE

1

θJA is specified for worst case conditions, i.e., θ

for surface mount packages.

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

AD8591ART –40°C to +85°C 6-Lead SOT-23 RT-6

AD8592ARM –40°C to +85°C 10-Lead µSOIC RM-10

AD8594AR –40°C to +85°C 16-Lead SOIC R-16A

AD8594ARU –40°C to +85°C 16-Lead TSSOP RU-16

1

JA

JC

is specified for device in socket

JA

Units

Typical Performance Characteristics

1k

VS = +2.7V

= +258C

T

A

100

10

1

∆OUTPUT VOLTAGE – mV

0.1

SOURCE

0.1 1 10

LOAD CURRENT – mA

SINK

100

1k0.01

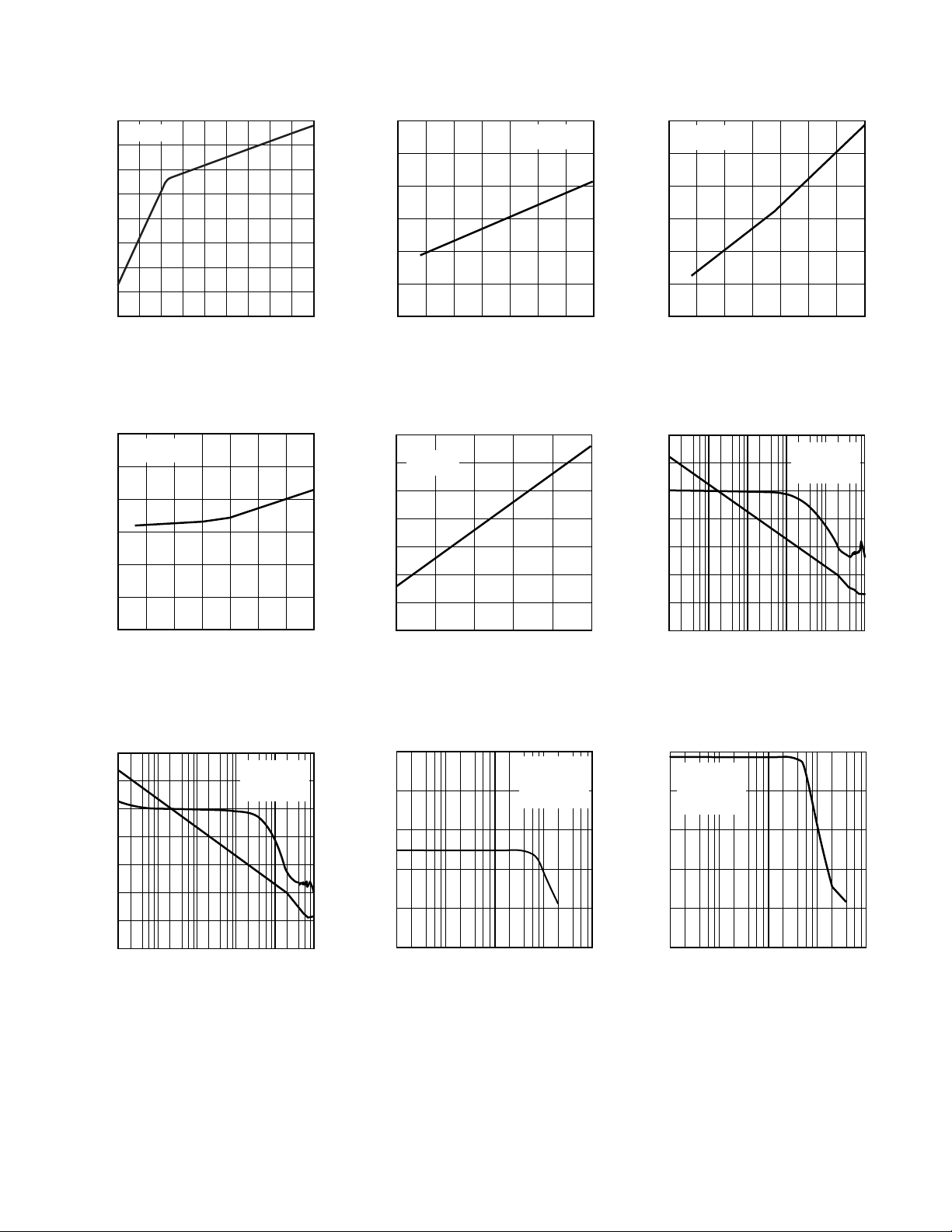

Figure 1. Output Voltage to Supply

Rail vs. Load Current

10k

VS = +5V

= +258C

T

A

1k

100

10

∆OUTPUT VOLTAGE – mV

1

0.1

Figure 2. Output Voltage to Supply

Rail vs. Load Current

SOURCE

0.1 1 10

LOAD CURRENT – mA

SINK

100

0.90

0.85

0.80

0.75

0.70

0.65

0.60

0.55

SUPPLY CURRENT/AMPLIFIER – mA

1k0.01

0.50

240 220

0 20406080

TEMPERATURE – 8C

VS = +5V

VS = +2.7V

100

Figure 3. Supply Current per

Amplifier vs. Temperature

–4–

REV. A

Page 5

AD8591/AD8592/AD8594

g

0.8

TA = +258C

0.7

0.6

0.5

0.4

0.3

0.2

0.1

SUPPLY CURRENT/AMPLIFIER – mA

0

0.75 1.25 3

1.75 2.25 2.75

SUPPLY VOLTAGE – 6Volts

Figure 4. Supply Current per

Amplifier vs. Supply Voltage

4

VS = +2.7V, +5V

V

= VS/2

CM

3

2

1

0

21

INPUT OFFSET CURRENT – pA

22

23

24

25

26

27

INPUT OFFSET VOLTAGE – mV

28

250 235

215

5254565

TEMPERATURE – 8C

VS = +5V

V

= +2.5V

CM

Figure 5. Input Offset Voltage vs.

Temperature

8

VS = +5V

7

T

= +258C

A

6

5

4

3

INPUT BIAS CURRENT – pA

2

8

VS = +2.7V, +5V

V

= VS/2

CM

7

6

5

4

INPUT BIAS CURRENT – pA

3

2

85

250 235

215

5254565

TEMPERATURE – 8C

85

Figure 6. Input Bias Current vs.

Temperature

80

60

40

20

0

GAIN – dB

VS = +2.7V

R

= NO LOAD

L

T

= +258C

A

45

90

135

180

PHASE SHIFT – Degrees

22

250 235

215

5254565

TEMPERATURE – 8C

85

Figure 7. Input Offset Current vs.

Temperature

80

60

40

20

0

GAIN – dB

1k 10k 100M

100k 1M 10M

FREQUENCY – Hz

VS = +5V

R

= NO LOAD

L

T

= +258C

A

Figure 10. Open-Loop Gain and

Phase vs. Frequency

45

90

rees

135

180

PHASE SHIFT – De

1

01 5

COMMON-MODE VOLTAGE – Volts

234

Figure 8. Input Bias Current vs.

Common-Mode Voltage

5

4

3

2

OUTPUT SWING – V p-p

1

0

1k 10k 10M

FREQUENCY – Hz

VS = +2.7V

R

= 2kV

L

T

= +258C

A

V

= 2.5V p-p

IN

100k 1M

Figure 11. Closed-Loop Output

Voltage Swing vs. Frequency

1k 10k 100M

100k 1M 10M

FREQUENCY – Hz

Figure 9. Open-Loop Gain and Phase

vs. Frequency

5

VS = +5V

R

= 2kV

L

4

T

= +258C

A

V

= 4.9V p-p

IN

3

2

OUTPUT SWING – V p-p

1

0

1k 10k 10M

100k 1M

FREQUENCY – Hz

Figure 12. Closed-Loop Output

Voltage Swing vs. Frequency

–5–REV. A

Page 6

AD8591/AD8592/AD8594

200

VS = +5V

180

T

= +258C

A

160

140

120

100

80

IMPEDANCE – V

60

40

20

0

1k 10k 100M

AV = 10

AV = 1

100k 1M 10M

FREQUENCY – Hz

Figure 13. Closed-Loop Output

Impedance vs. Frequency

140

120

100

80

60

40

20

PSRR – dB

0

220

240

260

100

+PSRR

1k 10k

2PSRR

FREQUENCY – Hz

VS = +5V

T

= +258C

A

100k 1M 10M

Figure 16. Power Supply Rejection

Ratio vs. Frequency

110

VS = +5V

T

= +258C

A

100

90

80

CMRR – dB

70

60

50

1k 10k 10M

100k 1M

FREQUENCY – Hz

Figure 14. Common-Mode Rejection

Ratio vs. Frequency

60

VS = +2.5V

R

= 2kV

L

50

T

= +258C

A

40

30

20

10

SMALL SIGNAL OVERSHOOT – %

0

10 100 10k1k

CAPACITANCE – pF

+OS

2OS

Figure 17. Small Signal Overshoot

vs. Load Capacitance

140

120

100

80

60

40

20

PSRR – dB

0

220

240

260

100

+PSRR

2PSRR

1k 10k

FREQUENCY – Hz

VS = +2.5V

T

= +258C

A

100k 1M 10M

Figure 15. Power Supply Rejection

Ratio vs. Frequency

60

VS = +5V

R

= 2kV

L

50

T

= +258C

A

40

30

20

10

SMALL SIGNAL OVERSHOOT – %

0

10 100 10k

2OS

+OS

1k

CAPACITANCE – pF

Figure 18. Small Signal Overshoot

vs. Load Capacitance

0V

20mV/DIV

VS = 61.35V

V

= 650mV

IN

A

= 1

V

R

= 2kV

L

C

= 300pF

L

T

= +258C

A

500 ns/DIV

Figure 19. Small Signal Transient

Response

0V

20mV/DIV

VS = 62.5V

V

= 650mV

IN

= 1

A

V

RL = 2kV

= 300pF

C

L

= +258C

T

A

500 ns/DIV

Figure 20. Small Signal Transient

Response

–6–

VS = 61.35V

= 1

A

100

90

10

0%

500mV

R

T

V

L

A

500ns

= 2kV

= +258C

Figure 21. Large Signal Transient

Response

REV. A

Page 7

AD8591/AD8592/AD8594

VS = 62.5V

A

= 1

100

90

10

0%

500mV

V

R

L

T

A

500ns

= 2kV

= +258C

Figure 22. Large Signal Transient

Response

100

90

100mV/DIV

10

0%

VS = +5V

A

= 1000

V

T

= +258C

A

FREQUENCY = 1kHz

1V

100

90

10

0%

1V

VS = 62.5V

= 1

A

V

T

= +258C

A

10ms

Figure 23. No Phase Reversal

VS = +5V

100

AV = 1000

90

TA = +258 C

FREQUENCY = 10kHz

V/DIV

m

200

10

0%

1

0.1

CURRENT NOISE DENSITY – pA/ Hz

0.01

10 100 100k

FREQUENCY – Hz

VS = +5V

= +258C

T

A

1k

10k

Figure 24. Current Noise Density vs.

Frequency

VS = +2.7V

= +1.35V

V

500

400

300

200

QUANTITY – Amplifiers

100

CM

T

A

= +258C

MARKER 41mV/ Hz

Figure 25. Voltage Noise Density vs.

Frequency

MARKER 25.9 mV/ Hz

Figure 26. Voltage Noise Density vs.

Frequency

VS = +5V

V

= +2.5V

500

400

300

200

QUANTITY – Amplifiers

100

–12

–10 –8 –6 –4 –2 0 2 4

INPUT OFFSET VOLTAGE – mV

CM

T

A

= +258C

Figure 28. Input Offset Voltage

Distribution

–12

–10 –8 –6 –4 –2 0 2 4

INPUT OFFSET VOLTAGE – mV

Figure 27. Input Offset Voltage

Distribution

–7–REV. A

Page 8

AD8591/AD8592/AD8594

AD8591/AD8592/AD8594 APPLICATION SECTION

Theory of Operation

The AD859x family of amplifiers are all CMOS, high output drive,

rail-to-rail input and output single supply amplifiers designed for

low cost and high output current drive. The parts include a power

saving shutdown function making the AD8591/AD8592/AD8594

op amps ideal for portable multimedia and telecom applications.

Figure 29 shows the simplified schematic for an AD8591/AD8592/

AD8594 amplifier. Two input differential pairs, consisting of an

n-channel pair (M1-M2) and a p-channel pair (M3-M4), provide

a rail-to-rail input common-mode range. The outputs of the input

differential pairs are combined in a compound folded-cascode

stage, which drives the input to a second differential pair gain

stage. The outputs of the second gain stage provide the gate voltage drive to the rail-to-rail output stage.

The rail-to-rail output stage consists of M15 and M16, which are

configured in a complementary common-source configuration.

As with any rail-to-rail output amplifier, the gain of the output

stage, and thus the open-loop gain of the amplifier, is dependent

on the load resistance. Also, the maximum output voltage swing

is directly proportional to the load current. The difference between the maximum output voltage to the supply rails, known as

the dropout voltage, is determined by the AD8591/AD8592/

AD8594 output transistors’ on-channel resistance. The output

dropout voltage is given in Figure 1 and Figure 2.

V+

*

100mA

M5

M8

M6

M7 M10

M9

V–

*NOTE: ALL CURRENT SOURCES GO

TO 0 mA IN SHUTDOWN MODE

M12

20mA

M11

M13

*

20mA

M30

M15

OUT

M16

M14

*

M31

SD

IN–

IN+

INV

M1

100mA

**

50mA

M337

V

M2

V

M340

B2

B3

M3

INV

M4

*

50mA

Figure 29. AD8591/AD8592/AD8594 Simplified Schematic

Input Voltage Protection

Although not shown on the simplified schematic, ESD protection diodes are connected from each input to each power supply

rail. These diodes are normally reverse biased, but will turn on

if either input voltage exceeds either supply rail by more than

+0.6 V. Should this condition occur, the input current should

be limited to less than ±5 mA. This can be done by placing a

resistor in series with the input(s). The minimum resistor value

should be:

Output Phase Reversal

The AD8591/AD8592/AD8594 are immune to output voltage

phase reversal with an input voltage within the supply voltages

of the device. However, if either of the device’s inputs exceeds

+0.6␣ V outside of the supply rails, the output could exhibit

phase reversal. This is due to the ESD protection diodes becoming forward biased, thus causing the polarity of the input

terminals of the device to switch.

The technique recommended in the Input Overvoltage Protection

section should be applied in applications where the possibility of

input voltages exceeding the supply voltages exists.

Output Short Circuit Protection

To achieve high output current drive and rail-to-rail performance,

the outputs of the AD859x family do not have internal short circuit protection circuitry. Although these amplifiers are designed to

sink or source as much as 250␣ mA of output current, shorting the

output directly to the positive supply could damage or destroy the

device. To protect the output stage, the maximum output current

should be limited to ±250␣ mA.

By placing a resistor in series with the output of the amplifier as

shown in Figure 30, the output current can be limited. The

minimum value for R

R

V

≥

X

250

For a +5 V single supply application, R

Because R

is inside the feedback loop, V

X

tradeoff in using R

under heavy output current loads. R

tive output impedance of the amplifier to R

can be found from Equation 2.

X

SY

mA

should be at least 20␣ Ω.

X

is not affected. The

is a slight reduction in output voltage swing

X

OUT

will also increase the effec-

X

+ RX, where RO is

O

(2)

the output impedance of the device.

+5V

R

V

IN

AD8592

20V

X

V

OUT

Figure 30. Output Short Circuit Protection

Power Dissipation

Although the AD859x family of amplifiers are able to provide

load currents of up to 250␣ mA, proper attention should be

given to not exceeding the maximum junction temperature for

the device. The equation for finding the junction temperature is

given as:

TP T

=×+θ

DISS A AJJ

(3)

Where TJ = AD859x junction temperature

P

= AD859x power dissipation

DISS

θ

= AD859x junction-to-ambient thermal resistance

JA

of the package; and

= The ambient temperature of the circuit

T

A

V

IN MAX

R

IN

,

≥

5

mA

(1)

–8–

REV. A

Page 9

AD8591/AD8592/AD8594

U1-A

R2

2kV

4

C1

100mF

+5V

1

10

2

3

5

+5V

V

DD

V

DD

LEFT

OUT

AD1881

(AC97)

RIGHT

OUT

V

SS

R4

20V

+5V

R1

100kV

7

8

6

9

R5

20V

C2

100mF

NOTE: ADDITIONAL PINS

OMITTED FOR CLARITY

U1-B

U1 = AD8592

R3

2kV

NC

28

35

36

In any application, the absolute maximum junction temperature

must be limited to +150°C. If this junction temperature is ex-

ceeded, the device could suffer premature failure. If the output

voltage and output current are in phase, for example, with a

purely resistive load, the power dissipated by the AD859x can

be found as:

PI VV

ISS SY OUTD LOAD

Where I

=×

= AD859x output load current

LOAD

V

= AD859x supply voltage; and

SY

V

= The output voltage

OUT

–

()

(4)

By calculating the power dissipation of the device and using the

thermal resistance value for a given package type, the maximum

allowable ambient temperature for an application can be found

using Equation 3.

Capacitive Loading

The AD859x exhibits excellent capacitive load driving capabilities

and can drive up to 10 nF directly. Although the device is stable

with large capacitive loads, there is a decrease in amplifier bandwidth as the capacitive load increases. Figure 31 shows a graph of

the AD8592 unity gain bandwidth under various capacitive loads.

4

3.5

3

2.5

2

VS = 62.5V

= 1kV

R

L

T

= +258C

A

50mV

ONLY

100

90

10

0%

50mV

10ms

47nF LOAD

SNUBBER

IN CIRCUIT

Figure 33. Snubber Network Reduces Overshoot and

Ringing Caused from Driving Heavy Capacitive Loads

The optimum values for the snubber network should be determined

empirically based on the size of the capacitive load. Table I shows a

few sample snubber network values for a given load capacitance.

Table I. Snubber Networks for Large Capacitive Loads

Load Capacitance Snubber Network

(CL)(R

, CS)

S

0.47 nF 300 Ω, 0.1 µF

4.7 nF 30 Ω, 1 µF

47 nF 5 Ω, 1 µF

A PC-98 Compliant Headphone/Speaker Amplifier

Because of its high output current performance and shutdown

feature, the AD8592 makes an excellent amplifier for driving an

audio output jack in a computer application. Figure 34 shows

how the AD8592 can be interfaced with an AC97 codec to drive

headphones or speakers.

Figure 31. Unity Gain Bandwidth vs. Capacitive Load

When driving heavy capacitive loads directly from the AD859x

output, a snubber network can be used to improve transient

response. This network consists of a series R-C connected from

the amplifier’s output to ground, placing it in parallel with the

capacitive load. The configuration is shown in Figure 32. Although this network will not increase the bandwidth of the amplifier, it will significantly reduce the amount of overshoot, as

shown in Figure 33.

1.5

BANDWIDTH – MHz

1

0.5

0

0.01 1000.1

V

100mV p-p

IN

Figure 32. Configuration for Snubber Network to

Compensate for Capacitive Loads

CAPACITIVE LOAD – nF

AD8592

110

+5V

R

S

5V

C

S

1mF

C

L

47nF

V

OUT

Figure 34. A PC-98 Compliant Headphone/Line Out Amplifier

When headphones are plugged into the jack, the normalizing contacts disconnect from the audio contacts. This allows the voltage to

the AD8592 shutdown pins to be pulled up to +5 V, activating the

amplifiers. With no plug in the output jack, the shutdown voltage is

pulled to 100 mV through the R1 and R3␣ +␣ R5 voltage divider.

This powers the AD8592 down when it is not needed, saving

current from the power supply or battery.

–9–REV. A

Page 10

AD8591/AD8592/AD8594

(

)

If gain is required from the output amplifier, four additional

resistors should be added as shown in Figure 35. The gain of

the AD8592 can be set as:

R

A

LEFT

AD1881

(AC97)

RIGHT

NOTE: ADDITIONAL PINS

OMITTED FOR CLARITY

7

=

V

R

6

+5V

V

DD

38

V

DD

35

OUT

R6

10kV

27

V

REF

R6

10kV

36

OUT

V

SS

R7

20kV

+5V

10

2

U1-A

3

5

6

7

U1-B

8

1

4

100kV

9

R7

U1 = AD8592

20kV

R7

AV = = +6dB WITH VALUES SHOWN

R6

C1

100mF

2kV

+5V

R1

C2

100mF

2kV

R4

20V

NC

R2

R5

20V

R3

(5)

Figure 35. A PC-98 Compliant Headphone/Line Out

Amplifier With Gain

Input coupling capacitors are not required for either circuit as

the reference voltage is supplied from the AD1881.

R4 and R5 help protect the AD8592 output in case the output

jack or headphone wires accidentally get shorted to ground.

The output coupling capacitors C1 and C2 block dc current

from the headphones and create a high-pass filter with a corner

frequency of:

f

=

dBL–3

214

1

π

CR R

+

()

(6)

Where RL is the resistance of the headphones.

A Combined Microphone and Speaker Amplifier for

Cellphone and Portable Headsets

The dual amplifiers in the AD8592 make an efficient design for

interfacing with a headset containing a microphone and speaker.

Figure 36 demonstrates a simple method for constructing an

interface to a codec.

R3

100kV

+5V

10

2

U1-A

1

4

3

5

6

7

U1-B

9

8

R5

10kV

OPTIONAL

R4

10kV

R6

10kV

TO

CODEC

V

REF

FROM CODEC

FROM CODEC

MONO OUT

(OR LEFT OUT)

(RIGHT OUT)

MIC + SPEAKER

JACK

U1 = AD8592

1kV

2.2kV

R7

+5V

R1

NC

C1

0.1mF

100kV

R8

C2

10mF

R2

10kV

+5V

Figure 36. A Speaker/Mic Headset Amplifier Circuit

U1-A is used as a microphone preamplifier, where the gain of

the preamplifier is set as R3/R2. R1 is used to bias an electret

microphone and C1 blocks any dc voltages from the amplifier.

U1-B is the speaker amplifier, and its gain is set at R5/R4. To

sum a stereo output, R6 should be added, equal in value to R4.

Using the same principle as described in the previous section,

the normalizing contact on the microphone/speaker jack can be

used to put the AD8592 into shutdown when the headset is not

plugged in. The AD8592 shutdown inputs can also be controlled with TTL or CMOS compatible logic, allowing microphone or speaker muting if desired.

An Inexpensive Sample-and-Hold Circuit

The independent shutdown control of each amplifier in the

AD8592 allows a degree of flexibility in circuit design. One particular application for which this feature is useful is in designing a

sample-and-hold circuit for data acquisition. Figure 37 shows a

schematic of a simple, yet extremely effective sample-and-hold

circuit using a single AD8592 and one capacitor.

C1

1nF

8

U1-B

6

7

U1 = AD8592

+5V

9

SAMPLE

AND HOLD

OUTPUT

+5V

2

10

U1-A

V

IN

3

SAMPLE

5

CLOCK

1

4

Figure 37. An Efficient Sample-and-Hold Circuit

–10–

REV. A

Page 11

AD8591/AD8592/AD8594

The U1-A amplifier is configured as a unity gain buffer driving a

1 nF capacitor. The input signal is connected to the noninverting

input, while the sample clock controls the shutdown for that

amplifier. When the sample clock is high, the U1-A amplifier is

active and the output follows V

. Once the sample clock goes

IN

low, U1-A shuts down with the output of the amplifier going to

a high impedance state, holding the voltage on the C1 capacitor.

The U1-B amplifier is used as a unity gain buffer to prevent loading on C1. Because of the low input bias current of the U1-B

CMOS input stage and the high impedance state of the U1-A

output in shutdown, there is very little voltage droop from C1

during the Hold period. This circuit can be used with sample

frequencies as high as 500␣ kHz and as low as below 1␣ Hz. Even

lower voltage droop can be achieved for very low sample rates

by increasing the value of C1.

Direct Access Arrangement for PCMCIA Modems

(Telephone Line Interface)

Figure 38 illustrates a +5␣ V transmit/receive telephone line

interface for 600␣ Ω systems. It allows full duplex transmission of

signals on a transformer-coupled 600␣ Ω line in a differential

manner. Amplifier A1 provides gain that can be adjusted to

meet the modem output drive requirements. Both A1 and A2

are configured to apply the largest possible signal on a single

supply to the transformer. Because of the AD8594’s high output

current drive and low dropout voltages, the largest signal available on a single +5␣ V supply is approximately 4.5␣ V␣ p-p into a

600␣ Ω transmission system. Amplifier A3 is configured as a

difference amplifier for two reasons: (1)␣ It prevents the transmit

signal from interfering with the receive signal and (2)␣ it extracts

the receive signal from the transmission line for amplification by

A4. Amplifier A4’s gain can be adjusted in the same manner as

A1’s to meet the modem’s input signal requirements. Standard

resistor values permit the use of SIP (Single In-line Package)

format resistor arrays. Couple this with the AD8594 16-lead

TSSOP or SOIC footprint, and this circuit offers a compact,

cost effective solution.

Single Supply Differential Line Driver

Figure 39 shows a single supply differential line driver circuit that

can drive a 600␣ Ω load with less than 0.7% distortion from 20 Hz

to 15 kHz with an input signal of 4 V p-p and a single +5 V supply.

The design uses an AD8594 to mimic the performance of a fully

balanced transformer based solution. However, this design occupies much less board space while maintaining low distortion and

can operate down to dc. Like the transformer based design, either

output can be shorted to ground for unbalanced line driver applications without changing the circuit gain of 1.

R3

2

C1

22mF

V

IN

A1, A2 = 1/2 AD8592

GAIN =

SET: R7, R10, R11 = R2

SET: R6, R12, R13 = R3

3

R3

R2

+5V

A1

10

4

10kV

1

R1

10kV

R10

10kV

10kV

R6

10kV

8

7

100kV

R9

+5V

R14

50V

R5

50V

R8

100kV

1mF

C2

2

1

A2

3

R2

R7

10kV

+5V

10

7

A1

9

4

R11

R12

10kV

10kV

8

9

A2

7

R13

10kV

C3

47mF

600V

C4

47mF

V

O1

R

L

V

O2

Figure 39. A Low Noise, Single Supply Differential

Line Driver

R8 and R9 set up the common-mode output voltage equal to

half of the supply voltage. C1 is used to couple the input signal

and can be omitted if the input’s dc voltage is equal to half of

the supply voltage.

The circuit can also be configured to provide additional gain if

desired. The gain of the circuit is:

P1

Tx GAIN

TO TELEPHONE

LINE

1:1

Z

O

600V

T1

MIDCOM

671-8005

A1, A2 = 1/2 AD8592

A3, A4 = 1/2 AD8592

6.2V

6.2V

R11

10kV

R3

360V

R9

10kV

R12

10kV

2

3

ADJUST

R5

10kV

R6

10kV

R10

10kV

5

A3

2kV

1

9

1

5

9.09kV

A1

6

A2

R13

10kV

R2

2

3

8

7

R14

14.3kV

8

7

R1

10kV

6

A4

C1

0.1mF

10mF

P2

Rx GAIN

ADJUST

2kV

9

TRANSMIT

SHUTDOWN

+5V

RECEIVE

C2

0.1mF

TxA

R7

10kV

R8

10kV

RxA

Figure 38. A Single Supply Direct Access Arrangement for

PCMCIA Modems

Where: V

–11–REV. A

V

OUT

A

==

V

V

IN

OUT

R2 = R7 = R10 = R11 and,

R3 = R6 = R12 = R13

R

3

R

2

= VO1␣–␣VO2,

(7)

Page 12

AD8591/AD8592/AD8594

SPICE Model for the AD8591/AD8592/AD8594 Amplifier

The SPICE model for the AD8591/AD8592/AD8594 amplifier is

one of the more realistic computer simulation macro-models

available, providing a high degree of realism with respect to characteristics of the actual amplifier. This model, shown in Listing 1,

is based on typical values for the device and can be downloaded

from Analog Devices’ Internet site at www.analog.com.

The model uses a common source output stage to provide railto-rail performance. This allows realistic simulation of openloop gain dependency on load resistance as well as maximum

output voltage versus output current. Two differential pairs are

used in the input stage of the model, simulating the rail-to-rail

input stage of the AD8591/AD8592/AD8594 amplifier.

The EOS voltage source establishes the input offset voltage and

is also used to simulate the common-mode rejection power

supply rejection, and input voltage noise characteristics for the

model. In addition, G2, R2 and CF are used to help set the

open-loop gain and gain-bandwidth product of the model.

A number of secondary characteristics are also accurately portrayed in the SPICE model. Flicker noise is accurately modeled

with the 1/f corner frequency set through the KF and AF terms

in the input stage transistors. C1 and C2 are used in the input

section to create secondary poles to achieve an accurate phase

margin characteristic for the model.

The AD8591/AD8592/AD8594 shutdown circuitry is included

in the model. Switches S1 through S7 deactivate the op amp

circuitry in shutdown mode. The logic threshold for the shutdown circuitry is accurately modeled through the VSWITCH

model parameters near the end of the listing. The active supply

current versus supply voltage is also modeled through the voltage-controlled current source GSY.

Characteristics of this model are based on typical values for the

AD8591/AD8592/AD8594 amplifier at +27°C. The model’s

characteristics are optimized specifically at +27°C, and may lose

accuracy at different simulation temperatures.

–12–

REV. A

Page 13

Listing 1: AD859x SPICE Macro-Model

* AD8592 SPICE Macro-Model Typical Values

* 9/98, Ver. 1

* TAM / ADSC

*

* Copyright 1998 by Analog Devices

*

* Refer to “README.DOC” file for License

* Statement. Use of this

* model indicates your acceptance of the

* terms and provisions in

* the License Statement.

*

* Node Assignments

* noninverting input

* | inverting input

* | | positive supply

* | | | negative supply

* | | | | output

* | | | | | shutdown

* | | | || |

.SUBCKT AD8592 1 2 99 50 45 80

*

* INPUT STAGE

*

M1 4 1 3 3 PIX L=0.8E-6 W=125E-6

M2 6 7 3 3 PIX L=0.8E-6 W=125E-6

RC1 4 50 4E3

RC2 6 50 4E3

C1 4 6 2E-12

I1 99 8 100E-6

AD8591/AD8592/AD8594

M3 10 1 12 12 NIX L=0.8E-6 W=125E-6

M4 11 7 12 12 NIX L=0.8E-6 W=125E-6

RC3 10 99 4E3

RC4 11 99 4E3

C2 10 11 2E-12

I2 13 50 100E-6

EOS 7 2 POLY(3) (21,98) (73,98) (61,0)

+1E-3 1 1 1

IOS 1 2 2.5E-12

V1 99 9 0.9

D1 3 9 DX

V2 14 50 0.9

D2 14 12 DX

S1 3 8 (82,98) SOPEN

S2 99 8 (98,82) SCLOSE

S3 12 13 (82,98) SOPEN

S4 13 50 (98,82) SCLOSE

*

* CMRR=64dB, ZERO AT 20kHz

*

ECM1 20 98 POLY(2) (1,98) (2,98) 0 .5 .5

RCM1 20 21 79.6E3

CCM1 20 21 100E-12

RCM2 21 98 50

*

* PSRR=80dB, ZERO AT 200Hz

*

RPS1 70 0 1E6

RPS2 71 0 1E6

CPS1 99 70 1E-5

–13–REV. A

Page 14

AD8591/AD8592/AD8594

CPS2 50 71 1E-5

EPSY 98 72 POLY(2) (70,0) (0,71) 0 1 1

RPS3 72 73 1.59E6

CPS3 72 73 500E-12

RPS4 73 98 80

*

* INTERNAL VOLTAGE REFERENCE

*

EREF 98 0 POLY(2) (99,0) (50,0) 0 .5 .5

GSY 99 50 POLY(1) (99,50) 20E-6 10E-7

*

* SHUTDOWN SECTION

*

E1 81 98 (80,50) 1

R1 81 82 1E3

C3 82 98 1E-9

*

* VOLTAGE NOISE REFERENCE OF 30nV/rt(Hz)

*

VN1 60 0 0

RN1 60 0 16.45E-3

HN 61 0 VN1 30

RN2 61 0 1

*

* GAIN STAGE

*

G2 98 30 POLY(2) (4,6) (10,11) 0 2.19E-5 +2.19E-5

R2 30 98 13E6

CF 45 30 5E-12

S5 30 98 (98,82) SCLOSE

D3 30 31 DX

D4 32 30 DX

V3 99 31 0.6

V4 32 50 0.6

*

* OUTPUT STAGE

*

M5 45 46 99 99 POX L=0.8E-6 W=16E-3

M6 45 47 50 50 NOX L=0.8E-6 W=16E-3

EG1 99 48 POLY(1) (98,30) 1.06 1

EG2 49 50 POLY(1) (30,98) 1.05 1

RG1 48 46 10E3

RG2 49 47 10E3

S6 46 99 (98,82) SCLOSE

S7 47 50 (98,82) SCLOSE

*

* MODELS

*

.MODEL PIX PMOS (LEVEL=2,KP=20E-6,VTO=-0.7, LAMBDA=0.01,AF=1,KF=1E-31)

.MODEL NIX NMOS (LEVEL=2,KP=20E-6,VTO=0.7, LAMBDA=0.01,AF=1,KF=1E-31)

.MODEL POX PMOS (LEVEL=2,KP=8E-6,VTO=-1, LAMBDA=0.067)

.MODEL NOX NMOS (LEVEL=2,KP=13.4E-6,VTO=1, LAMBDA=0.067)

.MODEL SOPEN VSWITCH(VON=2.4,VOFF=0.8, RON=10,ROFF=1E9)

.MODEL SCLOSE VSWITCH(VON=-0.8,VOFF=-2.4, RON=10,ROFF=1E9)

.MODEL DX D(IS=1E-14)

.ENDS AD8592

–14–

REV. A

Page 15

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

AD8591/AD8592/AD8594

0.071 (1.80)

0.059 (1.50)

0.051 (1.30)

0.035 (0.90)

6-Lead SOT

(RT-6)

0.122 (3.10)

0.106 (2.70)

4 5 6

0.118 (3.00)

0.098 (2.50)

3

0.037 (0.95) BSC

0.057 (1.45)

0.035 (0.90)

SEATING

PLANE

0.009 (0.23)

0.003 (0.08)

PIN 1

0.059 (0.15)

0.000 (0.00)

1

0.075 (1.90)

2

BSC

0.020 (0.50)

0.010 (0.25)

16-Lead Thin Shrink Small Outline

(RU-16)

0.201 (5.10)

0.193 (4.90)

16 9

108

08

0.022 (0.55)

0.014 (0.35)

0.124 (3.15)

0.112 (2.84)

0.038 (0.97)

0.030 (0.76)

0.1574 (4.00)

0.1497 (3.80)

0.124 (3.15)

0.112 (2.84)

10 6

1

PIN 1

0.0197 (0.50) BSC

0.122 (3.10)

0.110 (2.79)

0.006 (0.15)

0.002 (0.05)

16 9

10-Lead SOIC

(RM-10)

0.199 (5.05)

0.187 (4.75)

5

0.120 (3.05)

0.112 (2.84)

68

08

0.016 (0.41)

0.006 (0.15)

0.043 (1.09)

0.037 (0.94)

SEATING

PLANE

0.011 (0.28)

0.003 (0.08)

16-Lead Narrow Body SO

(R-16A)

0.3937 (10.00)

0.3859 (9.80)

0.2440 (6.20)

81

0.2284 (5.80)

C3456a–0–2/99

0.022 (0.56)

0.021 (0.53)

0.177 (4.50)

0.006 (0.15)

0.002 (0.05)

SEATING

PLANE

0.169 (4.30)

1

PIN 1

0.0256

(0.65)

BSC

0.0118 (0.30)

0.0075 (0.19)

8

0.256 (6.50)

0.246 (6.25)

0.0433

(1.10)

MAX

0.0079 (0.20)

0.0035 (0.090)

88

08

0.028 (0.70)

0.020 (0.50)

0.0098 (0.25)

0.0040 (0.10)

SEATING

PLANE

PIN 1

0.0500

(1.27)

BSC

0.0688 (1.75)

0.0532 (1.35)

0.0192 (0.49)

0.0138 (0.35)

0.0099 (0.25)

0.0075 (0.19)

0.0196 (0.50)

0.0099 (0.25)

8°

0°

0.0500 (1.27)

0.0160 (0.41)

x 45°

PRINTED IN U.S.A.

–15–REV. A

–15–

Loading...

Loading...