Page 1

Precision, Selectable Gain,

FEATURES

Precision attenuation: G = 0.4, G = 0.8

Fully differential or single-ended input/output

Differential output designed to drive precision ADCs

Drives switched capacitor and Σ-Δ ADCs

Rail-to-rail output

VOCM pin adjusts output common mode

Robust overvoltage protection up to ±15 V (V

Single supply: 3 V to 10 V

Dual supplies: ±1.5 V to ±5 V

High performance

Suited for driving 18-bit converter up to 4 MSPS

10 nV/√Hz output noise

3 ppm/°C gain drift

500 μV maximum output offset

50 V/μs slew rate

Low power: 3.2 mA supply current

APPLICATIONS

ADC drivers

Differential instrumentation amplifier building blocks

Single-ended-to-differential converters

GENERAL DESCRIPTION

The AD8475 is a fully differential, attenuating amplifier with

integrated precision gain resistors. It provides precision attenuation

(by 0.4 or 0.8), common-mode level shifting, and single-ended-todifferential conversion along with input overvoltage protection.

Power dissipation on a single 5 V supply is only 16 mW.

The AD8475 is a simple to use, fully integrated precision gain

block, designed to process signal levels of up to ±10 V on a single

supply. It provides a complete interface to make industrial level

signals directly compatible with the differential input ranges of low

voltage high performance 16-bit or 18-bit single-supply successive

approximation (SAR) analog-to-digital converters (ADCs).

The AD8475 comes with two standard pin-selectable gain

options: 0.4 and 0.8. The gain of the part is set by driving the

input pin corresponding to the appropriate gain.

The AD8475 also provides overvoltage protection from large

industrial input voltages up to ±15 V while operating on a single

5 V supply. The VOCM pin adjusts the output voltage common

mode for precision level shifting, to match the ADC’s input range

and maximize dynamic range.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

= +5 V)

S

Fully Differential Funnel Amplifier

AD8475

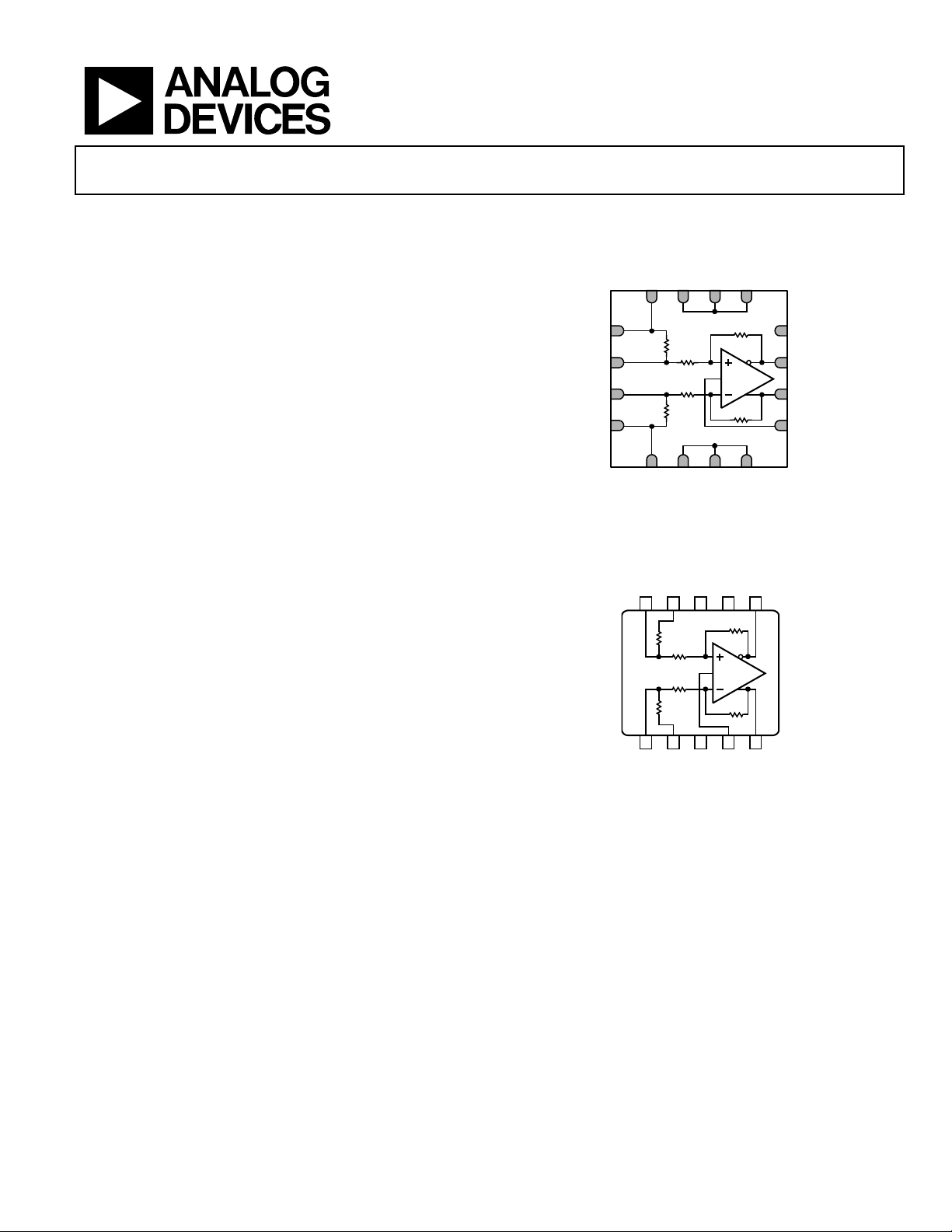

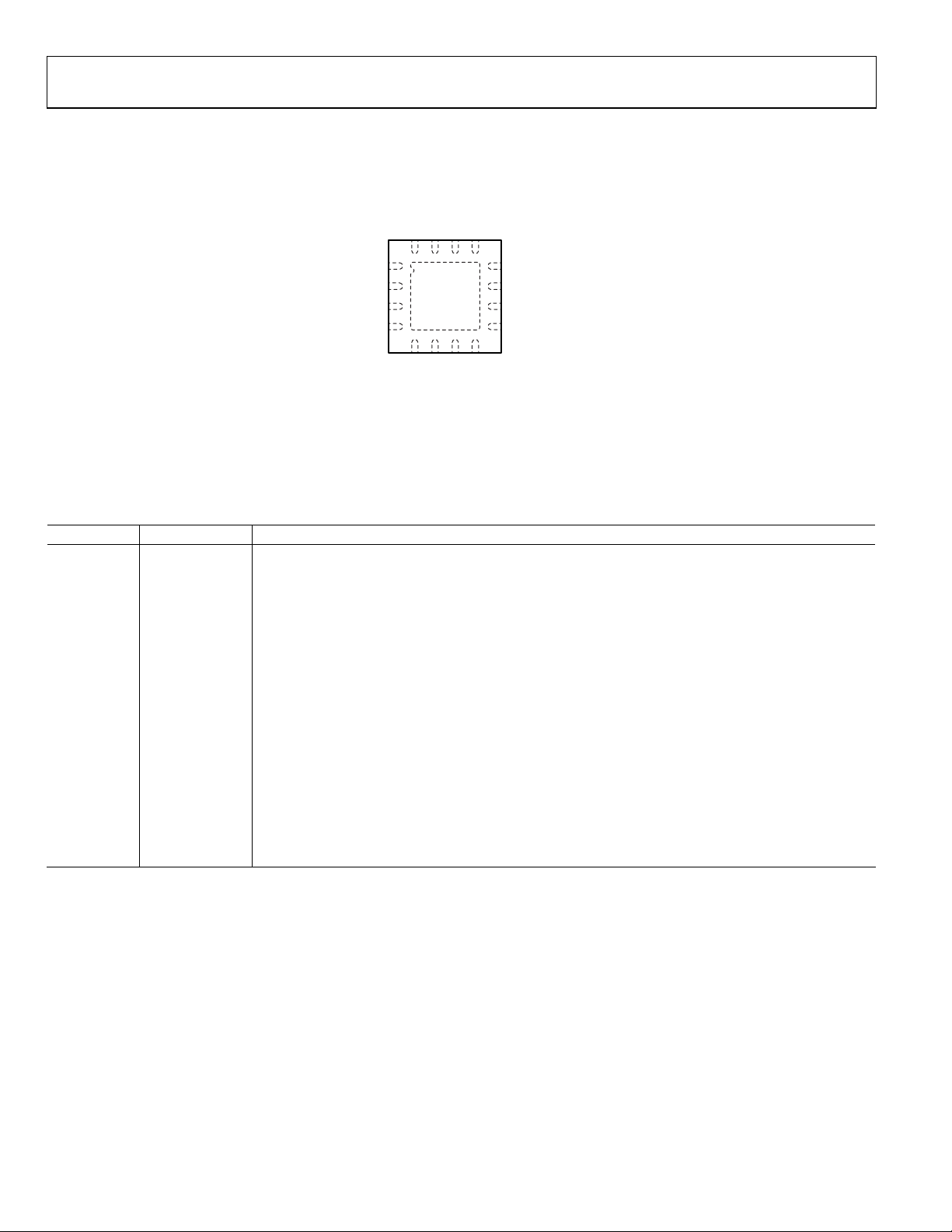

FUNCTIONAL BLOCK DIAGRAMS

S

S

S

–V

–V

–V

+IN 0.4x

16

+IN 0.4x

1

1.25kΩ

+IN 0.8x

2

–IN 0.8x

3

–IN 0.4x

NC = NO CONNECT

1.25kΩ

4

5

N 0.4x

–I

Figure 1. 16-Lead LFCSP

+IN 0.8x10+IN 0.4x9–V

1.25kΩ

1.25kΩ

1.25kΩ

1.25kΩ

–IN 0.8x1–IN 0.4x

NC = NO CONNECT

Figure 2. 10-Lead MSOP

The AD8475 works extremely well with SAR, Σ-, and pipeline

converters. The high current output stage of the part allows it to

drive the switched capacitor front-end circuits of many ADCs with

minimal error.

Unlike many differential drivers in the market, the AD8475 is a

high precision amplifier. With 500 µV maximum output offset,

10 nV/√Hz output noise, and −112 dB THD + N, the AD8475

pairs well with high accuracy converters. Considering its low power

consumption and high precision, the slew-enhanced AD8475 has

excellent speed, settling to 18-bit precision for 4 MSPS acquisition.

The AD8475 is available in a space-saving 16-lead 3 mm × 3 mm

LFCSP package and a 10-lead MSOP package. It is fully specified

over the −40°C to +85°C temperature range.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010–2011 Analog Devices, Inc. All rights reserved.

15

1.25kΩ

1.25kΩ

6

S

+V

2

14

7

+V

S

8

AD8475

3

S

+V

1kΩ

AD8475

1kΩ

S

NC7–OUT

1kΩ

1kΩ

4

VOCM

13

12

NC

11

–OUT

10

+OUT

9

VOCM

8

S

+V

09432-001

6

5

+OUT

09432-002

Page 2

AD8475

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description........................................................................... 1

Functional Block Diagrams............................................................. 1

Revision History ...............................................................................2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 5

Thermal Resistance...................................................................... 5

ESD Caution.................................................................................. 5

Pin Configurations and Function Descriptions........................... 6

Typical Performance Characteristics............................................. 8

Terminology.................................................................................... 16

Theory of Operation ......................................................................17

Overview...................................................................................... 17

Circuit Information.................................................................... 17

DC Precision............................................................................... 17

Input Voltage Range................................................................... 18

Driving the AD8475................................................................... 18

Power Supplies............................................................................ 18

Applications Information.............................................................. 19

Typical Configuration................................................................ 19

Single-Ended to Differential Conversion................................ 19

Setting the Output Common-Mode Voltage ..........................19

High Performance ADC Driving............................................. 20

AD8475 Evaluation Board ............................................................ 22

Outline Dimensions....................................................................... 23

Ordering Guide .......................................................................... 24

REVISION HISTORY

4/11—Rev. A to Rev. B

Added B Grade Columns to Specifications Section..................... 3

Changes to Figure 16........................................................................ 9

Changes to Figure 43...................................................................... 14

Changes to Ordering Guide.......................................................... 24

1/11—Rev. 0 to Rev. A

Added 16-Lead LFCSP.................................................. Throughout

Changes to Table 1 and Note 3........................................................ 3

Change to Table 2............................................................................. 5

Added Figure 3 and Table 4; Renumbered Sequentially ............. 6

Changes to Typical Performance Characteristics Format........... 8

Added AD8475 Evaluation Board Section and Figure 56......... 22

10/10—Revision 0: Initial Version

Rev. B | Page 2 of 24

Page 3

AD8475

SPECIFICATIONS

VS = 5 V, G = 0.4, VOCM connected to 2.5 V, RL = 1 kΩ differentially, TA = 25°C, referred to output (RTO), unless otherwise noted.

Table 1.

B Grade A Grade

Parameter Test Conditions/Comments Min Typ Max Min Typ Max Unit

DYNAMIC PERFORMANCE

−3 dB Small Signal

Bandwidth

−3 dB Large Signal

Bandwidth

Slew Rate 2 V step 50 50 V/μs

Settling Time to 0.01% 2 V step on output 45 45 ns

Settling Time to 0.001% 2 V step on output 50 50 ns

NOISE/DISTORTION1

THD + N

HD2 f = 1 MHz, V

HD3 f = 1 MHz, V

IMD3

IMD3

Output Voltage Noise f = 0.1 Hz to 10 Hz 2.5 2.5 μV p-p

Spectral Noise Density f = 1 kHz 10 10 nV/√Hz

GAIN 0.4 0.4 V/V

Gain Error RL = ∞ 0.02 0.05 %

Gain Drift −40°C ≤ TA ≤ +85°C 1 3 1 3 ppm/°C

Gain Nonlinearity V

OFFSET AND CMRR

Offset2 RTO 50 200 50 500 μV

vs. Temperature −40°C ≤ TA ≤ +85°C 2.5 2.5 μV/°C

vs. Power Supply VS = ±2.5 V to ±5 V 90 90 dB

Common-Mode Rejection

Ratio

INPUT CHARACTERISTICS

Input Voltage Range3 Differential input −6.25 +6.25 −6.25 +6.25 V

Single-ended input −12.5 +12.5 −12.5 +12.5 V

Impedance4 V

Single-Ended Input 2.92 2.92 kΩ

Differential Input 5 5 kΩ

Common Mode Input 1.75 1.75 kΩ

OUTPUT CHARACTERISTICS

Output Swing

Output Balance Error ∆V

Output Impedance 0.1 0.1 Ω

Capacitive Load Per output 30 30 pF

Short-Circuit Current Limit 110 110 mA

VOCM CHARACTERISTICS

VOCM Input Voltage Range −VS + 1 +VS −VS + 1 +VS V

VOCM Input Impedance 100 100 kΩ

VOCM Gain Error 0.02 0.02 %

150 150 MHz

15 15 MHz

f = 100 kHz, V

= 4 V p-p,

OUT

−112 −112 dB

22 kHz band-pass filter

= 2 V p-p −110 −110 dB

OUT

= 2 V p-p −96 −96 dB

OUT

= 0.95 MHz, f2 = 1.05 MHz,

f

1

= 2 V p-p

V

OUT

= 95 kHz, f2 = 105 kHz,

f

1

V

= 2 V p-p

OUT

= 4 V p-p 2.5 2.5 ppm

OUT

V

= ±5 V 86 76 dB

INcm

= VS/2

INcm

OUT,cm

/∆V

90 −80 dB

OUT,dm

−90 −90 dBc

−84 −84 dBc

−V

0.05

+

S

+V

0.05

−

S

−VS +

0.05

+V

S

−

0.05

Rev. B | Page 3 of 24

Page 4

AD8475

B Grade A Grade

Parameter Test Conditions/Comments Min Typ Max Min Typ Max Unit

POWER SUPPLY

Specified Voltage 5 5 V

Operating Voltage Range 3 10 3 10 V

Supply Current 3 3.2 3 3.2 mA

Over Temperature −40°C ≤ TA ≤ +85°C 4 4 mA

TEMPERATURE RANGE

Specified Performance Range −40 +85 −40 +85 °C

Operating Range −40 +125 −40 +125 °C

1

Includes amplifier voltage and current noise, as well as noise of internal resistors.

2

Includes input bias and offset current errors.

3

The input voltage range is a function of the voltage supplies and ESD diodes.

4

Internal resistors are trimmed to be ratio matched but have ±20% absolute accuracy.

Rev. B | Page 4 of 24

Page 5

AD8475

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage 11 V

Maximum Voltage at Any Input Pin +VS + 10.5 V

Minimum Voltage at Any Input Pin −VS − 16 V

Storage Temperature Range −65°C to +150°C

Specified Temperature Range −40°C to +85°C

Operating Temperature Range −40°C to +125°C

Junction Temperature 150°C

ESD (FICDM) 1500 V

ESD (HBM) 2000 V

Stresses above those listed under Absolute Maximum

Ratings may cause permanent damage to the device. This is

a stress rating only; functional operation of the device at

these or any other conditions above those indicated in the

operational section of this specification is not implied.

Exposure to absolute maximum rating conditions for

extended periods may affect device reliability.

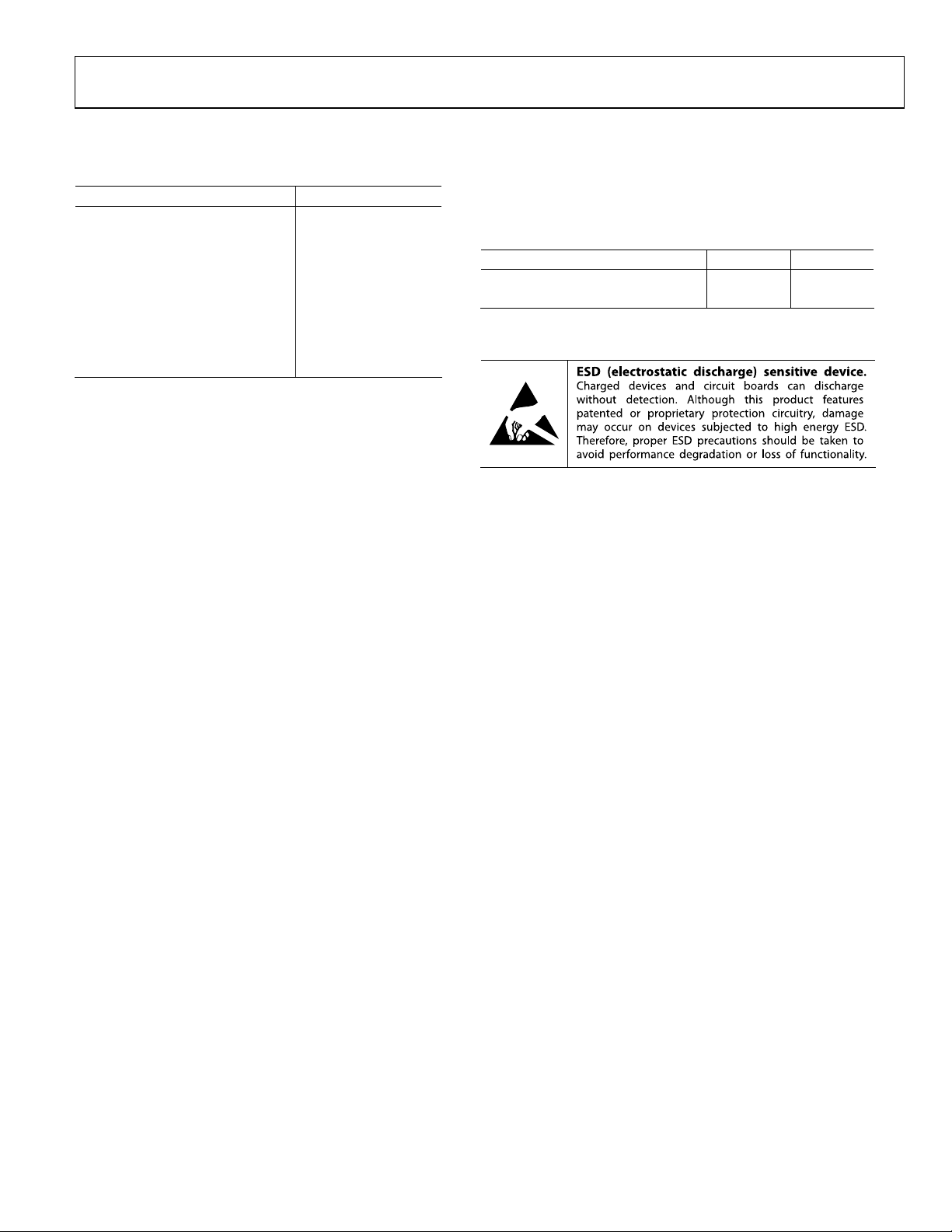

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 3. Thermal Resistance

Package Type θJA Unit

16-Lead LFCSP (Exposed Pad) 84.90 °C/W

10-Lead MSOP 214.0 °C/W

ESD CAUTION

Rev. B | Page 5 of 24

Page 6

AD8475

x

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

S

S

S

–V

–V

–V

+IN 0.4

16

15

14

13

+IN 0.4x

1

2

3

4

AD8475

TOP VIEW

(Not to Scale

6

5

7

S

S

+V

+V

–IN 0.4x

+IN 0.8x

–IN 0.8x

–IN 0.4x

NOTES

1. NC = NO CONNECT.

2. SOLDER THE EXPOSED PADDLE ON T HE BACK

OF THE PACKAG E TO A GRO UND PLANE.

Figure 3. 16-Lead LFCSP Pin Configuration

Table 4. 16-Lead LFCSP Pin Function Descriptions

Pin No. Mnemonic Description

1 +IN 0.4x Positive Input for 0.4 Attenuation.

2 +IN 0.8x Positive Input for 0.8 Attenuation

3 −IN 0.8x Negative Input for 0.8 Attenuation.

4 −IN 0.4x Negative Input for 0.4 Attenuation.

5 −IN 0.4x Negative Input for 0.4 Attenuation.

6 +VS Positive Supply.

7 +VS Positive Supply.

8 +VS Positive Supply.

9 VOCM Output Common-Mode Adjust.

10 +OUT Positive Output.

11 −OUT Negative Output.

12 NC No Connect.

13 −VS Negative Supply.

14 −VS Negative Supply.

15 −VS Negative Supply.

16 +IN 0.4x Positive Input for 0.4 Attenuation.

EPAD Solder the exposed paddle on the back of the package to a ground plane.

NC

12

–OUT

11

10

+OUT

9

VOCM

8

S

+V

09432-003

Rev. B | Page 6 of 24

Page 7

AD8475

–IN 0.8x

–IN 0.4x

+V

VOCM

S

1

2

3

4

AD8475

TOP VIEW

(Not to Scale

10

9

8

7

+IN 0.8x

+IN 0.4x

–V

S

NC

5

+OUT

NC = NO CONNECT

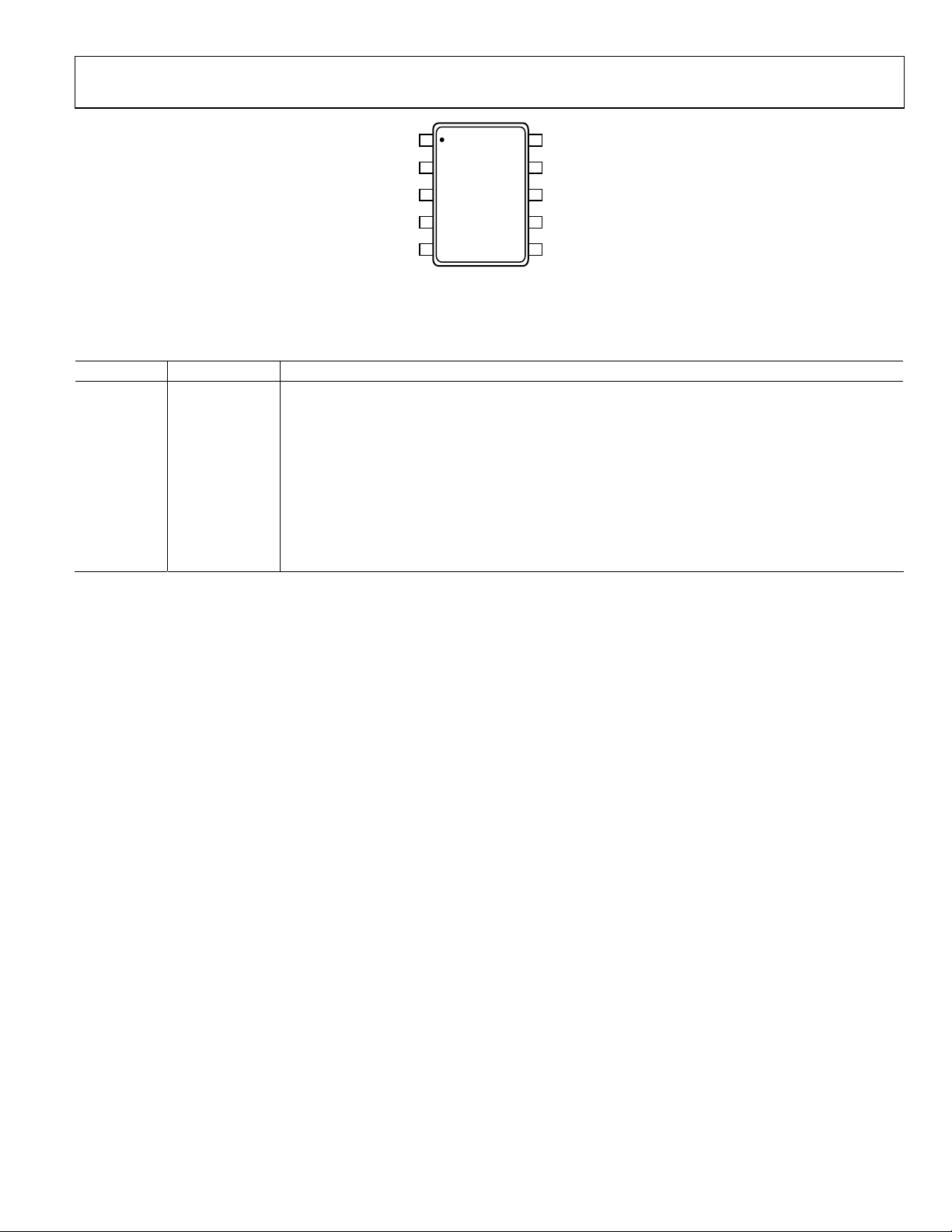

Figure 4. 10-Lead MSOP Pin Configuration

Table 5. 10-Lead MSOP Pin Function Descriptions

Pin No. Mnemonic Description

1 −IN 0.8x Negative Input for 0.8 Attenuation

2 −IN 0.4x Negative Input for 0.4 Attenuation

3 +VS Positive Supply

4 VOCM Output Common-Mode Adjust

5 +OUT Noninverting Output

6 −OUT Inverting Output

7 NC No Connect

8 −VS Negative Supply

9 +IN 0.4x Positive Input for 0.4 Attenuation

10 +IN 0.8x Positive Input for 0.8 Attenuation

6

–OUT

09432-004

Rev. B | Page 7 of 24

Page 8

AD8475

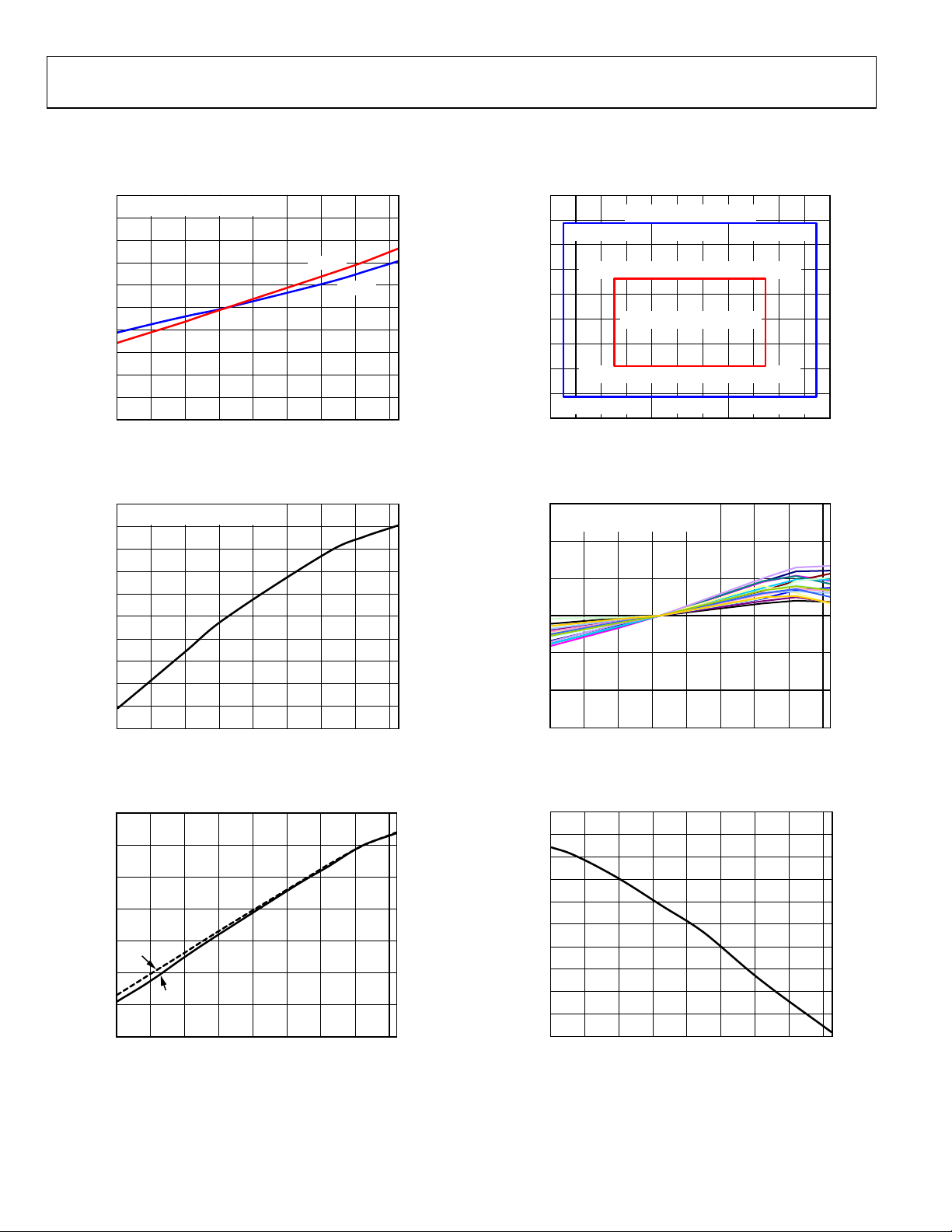

TYPICAL PERFORMANCE CHARACTERISTICS

TA = 25°C, VS = 5 V, gain = 0.4, R

1000

REPRESENTATIVE SAMPLES

800

600

400

200

(µV)

0

OSO

V

–200

–400

–600

–800

–1000

–40 120100806040200–20

Figure 5. System Offset vs. Temperature

5

REPRESENTATIVE SAMPLES

4

3

2

1

0

–1

CMRR (µV/V)

–2

–3

–4

–5

–40 120100806040200–20

Figure 6. CMRR vs. Temperature (G = 0.8)

65

60

55

50

45

FALL

SLEW RATE (V/µs)

40

35

30

–40 120

RISE

Figure 7. Slew Rate vs. Temperature

TEMPERATURE (°C)

TEMPERATURE (°C)

TEMPERAT URE (°C)

= 1 kΩ, RTO, unless otherwise specified.

LOAD

G = 0.8

G = 0.4

09432-006

09432-005

100806040200–20

09432-015

10

8

6

4

2

0

–2

–4

COMMON-MODE VOLTAGE (V)

–6

–4.97V, –6. 25V

–8

–5.5 –4.5 –3.5 –2.5 –1.5 –0.5 0. 5 1.5 2. 5 3.5 4.5 5.5

VS = +5V, VOCM = +2.5V

VS = +3V, VOCM = +1.5V

–2.97V, –3.75V

OUTPUT VO LTAGE (V)

0V, +7.75V–4.97V, +7. 75V +4.95V, + 7.75V

0V, +3.25V–2.97V, +3 .25V

0V, –3.75V +2.95V, –3. 75V

0V, –6.25V

+2.95V, + 3.25V

+4.95V, –6. 25V

Figure 8. Input Common-Mode Voltage vs. Output Voltage,

= +5 V and +3 V

V

S

150

VIN = ±5V

REPRESENTATIVE SAMPLES

100

50

0

–50

GAIN ERRO R (µV/V)

–100

–150

–40 120100806040200–20

Figure 9. Gain Error vs. Temperature, V

TEMPERAT URE (°C)

= ±5 V

S

130

125

120

115

110

105

100

95

90

SHORT-CIRCUIT CURRENT (mA)

85

80

–40 120100806040200–20

TEMPERATURE (°C)

Figure 10. Short-Circuit Current vs. Temperature

09432-008

09432-100

09432-016

Rev. B | Page 8 of 24

Page 9

AD8475

V

–

+V

S

0.2

0.4

0.6

0.8

1.0

+V

S

0.2

0.4

0.6

0.8

1.0

–40°C

+25°C

+85°C

+105°C

+125°C

1.0

OUTPUT VOLTAGE SWING (V)

0.8

REFERRED TO SUPPLY VOLTAGES

0.6

0.4

0.2

–V

S

100 1k 10k 100k 1M

Figure 11. Output Voltage Swing vs. R

2V/DI

R

LOAD

V

= ±5 V and +5 V

S

100µs/DIV

(Ω)

LOAD

0.8 × V

vs. Temperature,

IN

V

OUT

Figure 12. Overdrive Recovery

20

–30

–40°C

+25°C

+85°C

+105°C

+125°C

1.0

OUTPUT VOLTAGE SWING (V)

0.8

REFERRED TO SUPPLY VOLTAGES

0.6

0.4

0.2

–V

S

10µA 100µA 1mA 10mA 100mA

09432-013

OUTPUT CURRENT (A)

09432-014

Figure 14. Output Voltage Swing vs. Output Current vs. Temperature,

= ±5 V and +5 V

V

S

10

9

8

7

6

5

4

3

2

MAXIMUM OUTPUT VOLTAGE ( V p-p)

1

09432-051

0

100 10M1M100k10k1k

FREQUENCY (Hz)

09432-012

Figure 15. Maximum Output Voltage vs. Frequency

100

90

G = 0.8

–40

–50

–60

PSRR (dB)

–70

–80

–90

–100

100k 1M 10M

FREQUENCY (Hz)

Figure 13. Power Supply Rejection Ratio (PSRR) vs. Frequency

09432-011

80

70

60

CMRR (dB)

50

40

30

20

G = 0.4

FREQUENCY (Hz)

10M 100M1M100k10k1k

09432-216

Figure 16. CMRR vs. Frequency

Rev. B | Page 9 of 24

Page 10

AD8475

0

–1.94

–7.96

–10

G = 0.8

G = 0.4

–1.94

0

G = 0.8

–20

GAIN (dB)

–30

–40

–50

1k 1G100M10M1M100k10k

FREQUENCY (Hz)

Figure 17. Small Signal Frequency Response for All Gains V

0

–7.96

–10

–20

GAIN (dB)

–30

= ±5 V

S

VS = ±5V

VS = +3V

VS = +5V

–7.96

–10

GAIN (dB)

–20

–30

1k 100M10M1M100k10k

09432-017

Figure 20. Large Signal Frequency Response for All Gains, V

G = 0.4

FREQUENCY (Hz)

= ±5 V

S

09432-019

0

–7.96

–10

GAIN (dB)

–20

VS = ±5V

VS = +3V

VS = +5V

–40

1k 100M10M1M100k10k

FREQUENCY (Hz )

Figure 18. Small Signal Frequency Response for Various Supplies

0

–10

–20

GAIN (dB)

–30

–40

RL = 200Ω

RL = 1kΩ

RL = 10kΩ

–50

100k 100M10M1M

FREQUENCY (Hz )

Figure 19. Small Signal Frequency Response for Various Loads

–30

1k 100M10M1M100k10k

09432-018

FREQUENCY (Hz)

09432-020

Figure 21. Large Signal Frequency Response for Various Supplies

0

–10

–20

GAIN (dB)

–30

–40

RL = 200Ω

RL = 1kΩ

RL = 10kΩ

–50

100k 100M10M1M

09432-022

FREQUENCY (Hz)

09432-024

Figure 22. Large Signal Frequency Response for Various Loads

Rev. B | Page 10 of 24

Page 11

AD8475

–7.96

GAIN (dB)

–10

–20

–30

0

CL = 0pF

CL = 5pF

CL = 10pF

–7.96

GAIN (dB)

–10

–20

0

CL = 0pF

CL = 5pF

CL = 10pF

–40

1k 100M10M1M100k10k

FREQUENCY (Hz)

09432-025

Figure 23. Small Signal Frequency Response for Various Capacitive Loads

0

VOCM = 1V

VOCM = 2.5V

VOCM = 4V

–10

–20

GAIN (dB)

–30

–40

10k 100M10M1M100k

FREQUENCY (Hz)

09432-026

Figure 24. Small Signal Frequency Response for Various VOCM Levels

5

V

= 100mV p-p

OUT

VOCM = 2.5V

0

–30

1k 100M10M1M100k10k

FREQUENCY (Hz)

Figure 26. Large Signal Frequency Response for Various Capacitive Loads

0

VOCM = 1. 5V

VOCM = 2. 5V

VOCM = 3. 5V

–10

GAIN (dB)

–20

–30

1k 100M10M1M100k10k

FREQUENCY (Hz)

Figure 27. Large Signal Frequency Response for Various VOCM Levels

10

V

= 2V p-p

OUT

VOCM = 2.5V

0

09432-027

09432-028

–5

–10

VOCM GAIN (dB)

–15

–2

1k 10M1M100k10k

FREQUENCY (Hz)

Figure 25. VOCM Small Signal Frequency Response

09432-056

Rev. B | Page 11 of 24

–10

–20

VOCM GAIN (dB)

–30

–40

1k 10M1M100k10k

FREQUENCY (Hz)

Figure 28. VOCM Large Signal Frequency Response

09432-055

Page 12

AD8475

V

V

V

V

V

V

= 100mV p-p

OUT

OUT

= 2V p-p

20mV/DI

10ns/DIV

Figure 29. Small Signal Pulse Response, V

= ±2.5 V

S

09432-029

CL = 0pF

CL = 5pF

CL = 10pF

20mV/DI

10ns/DIV

09432-031

Figure 30. Small Signal Step Response for Various Capacitive Loads,

= ±2.5 V

V

S

500mV/DI

Figure 32. Large Signal Pulse Response, V

20ns/DIV

= ±2.5 V

S

09432-033

CL = 0pF

CL = 5pF

CL = 10pF

500mV/DI

20ns/DIV

09432-035

Figure 33. Large Signal Step Response for Various Capacitive Loads

RL = 200Ω

RL = 1kΩ

RL = 10kΩ

20mV/DIV

10ns/DIV

Figure 31. Small Signal Step Response for Various Resistive Loads

RL = 200Ω

RL = 1kΩ

RL = 10kΩ

500mV/DIV

09432-030

20ns/DIV

09432-034

Figure 34. Large Signal Step Response for Various Resistive Loads

Rev. B | Page 12 of 24

Page 13

AD8475

V

–

–

V

–

–

20mV/DI

50ns/DIV

Figure 35. VOCM Small Signal Step Response, V

= ±2.5 V

S

20

HD2, G = 0.4

HD3, G = 0.4

–40

–60

–80

–100

HARMONIC DI STORT ION (d Bc)

–120

–140

HD2, G = 0.8

HD3, G = 0.8

0.1 1 10

FREQUENCY (MHz)

Figure 36. Harmonic Distortion vs. Frequency at Various Gains

20

= 2V p-p

V

OUT

HD2, RL = 1kΩ

–40

–60

HD3, RL = 1kΩ

HD2, RL = 200Ω

HD3, RL = 200Ω

500mV/DI

09432-032

500ns/DIV

09432-036

Figure 38. VOCM Large Signal Step Response

20

= 2V p-p

V

OUT

HD2, VS = +5V

–40

–60

–80

–100

HARMONIC DI STORT ION (d Bc)

–120

–140

09432-043

HD3, VS = +5V

HD2, VS = ±5V

HD3, VS = ±5V

0.1 1 10

FREQUENCY (MHz)

09432-042

Figure 39. Harmonic Distortion vs. Frequency at Various Supplies

20

HD2, V

= 2V p-p

OUT

HD3, V

= 2V p-p

OUT

HD2, V

= 4V p-p

–40

–60

HD3, V

OUT

OUT

= 4V p-p

–80

–100

HARMONIC DI STORT ION (d Bc)

–120

–140

0.1 1 10

FREQUENCY (MHz)

Figure 37. Harmonic Distortion vs. Frequency at Various Loads

09432-040

–80

–100

HARMONIC DI STORT ION (d Bc)

–120

–140

0.1 1 10

FREQUENCY (MHz)

Figure 40. Harmonic Distortion vs. Frequency at Various V

OUT,dm

09432-046

Rev. B | Page 13 of 24

Page 14

AD8475

–

–

V

20

–40

–60

f = 100kHz

HD2, +5V SUPPLY

HD3, +5V SUPPLY

HD2, ±5V SUPPLY

HD3, ±5V SUPPLY

–40

–60

20

= 2V p-p

V

OUT

RL = 1kΩ

RL = 200Ω

–80

–100

HARMONIC DIST ORTIO N (dBc)

–120

–140

0987654321

Figure 41. Harmonic Distortion vs. V

V

(V p-p)

OUT

at Various Supplies

OUT

10

0

–10

–20

–30

–40

–50

–60

–70

–80

NORMALIZED SPECTRUM (dBc)

–90

–100

–110

75 80 85 90 95 100 105 110 115 120 125

FREQUENCY (kHz)

Figure 42. 100 kHz Intermodulation Distortion

100

90

80

70

60

50

40

30

VOLTAGE NOISE (nV/ Hz)

20

10

0

FREQUENCY (Hz)

10k 100k1k100101

Figure 43. Voltage Noise Density vs. Frequency

–80

–100

–120

SPURIOUS-FREE D YANMIC RANG E (dBc)

–140

0.1 1 10

09432-047

FREQUENCY (MHz)

09432-049

Figure 44. Spurious-Free Dynamic Range vs. Frequency at Various Loads

100

10

1

OUTPUT IMPEDANCE (Ω)

0.1

0.01

10k 100k 1M 10M 100M

09432-054

FREQUENCY (Hz)

09432-052

Figure 45. Output Impedance vs. Frequency

500nV/DI

1s/DIV

09432-243

09432-039

Figure 46. 0.1 Hz to 10 Hz Voltage Noise

Rev. B | Page 14 of 24

Page 15

AD8475

–

30

–40

–50

–60

–70

–80

OUTPUT BALANCE ERRO R (dB)

–90

–100

1M 10M 100M

FREQUENCY (Hz)

09432-050

Figure 47. Output Balance Error vs. Frequency

Rev. B | Page 15 of 24

Page 16

AD8475

V

TERMINOLOGY

1kΩ

+IN

OCM

–IN

1.25kΩ

AD8475

1.25kΩ

Figure 48. Signal and Circuit Definitions

1kΩ

–OUT

+OUT

R

L, dm

V

OUT, dm

09432-162

Differential Voltage

Differential voltage refers to the difference between two

node voltages. For example, the output differential voltage (or

equivalently, output differential mode voltage) is defined as

V

where V

OUT, dm

+OUT

= (V

and V

+OUT

−OUT

− V

)

−OUT

refer to the voltages at the +OUT and

−OUT terminals with respect to a common ground reference.

Similarly, the differential input voltage is defined as

= (V

− (V

V

IN, dm

+IN

−IN

))

Common-Mode Voltage

Common-mode voltage refers to the average of two node voltages

with respect to the local ground reference. The output commonmode voltage is defined as

V

OUT, cm

= (V

+OUT

+ V

−OUT

)/2

Balance

Output balance is a measure of how close the output differential

signals are to being equal in amplitude and opposite in phase.

Output balance is most easily determined by placing a wellmatched resistor divider between the differential voltage nodes

and comparing the magnitude of the signal at the divider midpoint

with the magnitude of the differential signal. By this definition,

output balance is the magnitude of the output common-mode

voltage divided by the magnitude of the output differential

mode voltage.

V

Δ

cmOUT

,

ErrorBalanceOutput

=

V

Δ

dmOUT

,

Rev. B | Page 16 of 24

Page 17

AD8475

–

–V

T

P

N

−

=

(

V

THEORY OF OPERATION

OVERVIEW

The AD8475 is a fully differential amplifier, with integrated lasertrimmed resistors, that provides precision attenuating gains of

0.4 and 0.8. The internal differential amplifier of the AD8475

differs from conventional operational amplifiers in that it has

two outputs whose voltages are equal in magnitude, but move in

opposite directions (180° out of phase). An additional input,

VOCM, sets the output common-mode voltage. Like an operational amplifier, it relies on high open-loop gain and negative

feedback to force the output nodes to the desired voltages. The

AD8475 is designed to greatly simplify single-ended-to-differential

conversion, common-mode level shifting and precision attenuation of large signals so that they are compatible with low voltage,

differential input ADCs.

+IN 0.8x + IN 0.4x

1.25kΩ

1.25kΩ

IN 0.8x –IN 0.4x +VSVOCM +O UT

1.25kΩ

1.25kΩ

Figure 49. Block Diagram

S

NC–OU

1kΩ

AD8475

1kΩ

9432-062

CIRCUIT INFORMATION

The AD8475 amplifier uses a voltage feedback topology;

therefore, the amplifier exhibits a nominally constant gain

bandwidth product. Like a voltage feedback operational

amplifier, the AD8475 also has high input impedance at its

internal input terminals (the summing nodes of the internal

amplifier) and low output impedance.

The AD8475 employs two feedback loops, one each to control

the differential and common-mode output voltages. The differential feedback loop, which is fixed with precision laser trimmed

on-chip resistors, controls the differential output voltage.

Output Common-Mode Voltage (VOCM)

The internal common-mode feedback controls the commonmode output voltage. This architecture makes it easy to set the

output common-mode level to any arbitrary value independent

of the input voltage. The output common-mode voltage is

forced by the internal common-mode feedback loop to be equal

to the voltage applied to the VOCM input. The VOCM pin can

be left unconnected, and the output common-mode voltage

self-biases to midsupply by the internal feedback control.

Due to the internal common-mode feedback loop and the fully

differential topology of the amplifier, the AD8475 outputs are

precisely balanced over a wide frequency range. This means that

the amplifier’s differential outputs are very close to the ideal of

being identical in amplitude and exactly 180° out of phase.

DC PRECISION

The dc precision of the AD8475 is highly dependent on the

accuracy of its internal resistors. Using superposition to analyze

the circuit shown in Figure 50, the following equation shows the

relationship between the input and output voltages of the

amplifier:

NP

=

++

RFN

RG

)(

RR

NP

RR

RGP

RGN

1

2

,

dmIN

2

1

()

2

,

dmOUT

2

RRRRVRRV

+++−

NPNP

RRVRRV

+++−=

NP

RRRR

++

NPNP

RR

++

NP

)

NP

RFP

V

ON

V

OP

RFN

09432-163

() ()

,

NPcmIN

()

,

cmOUT

where,

RFP

=

R

P

, NPcmIN

,

R

RG

dmIN

,

N

VVV

NP

1

VVV +=

2

The differential closed loop gain of the amplifier is

V

V

2

dmOUT

,

=

dmIN

,

2

and the common rejection of the amplifier is

V

dmOUT

,

V

cmIN

,

Figure 50. Functional Circuit Diagram of the AD8475 at a Given Gain

−

2

=

2

V

P

VOCM

N

The preceding equations show that the gain accuracy and the

common-mode rejection (CMRR) of the AD8475 are determined primarily by the matching of the feedback networks

(resistor ratios). If the two networks are perfectly matched, that

and RN equal RF/RG, then the resistor network does not

is, if R

P

generate any CMRR errors and the differential closed loop gain

of the amplifier reduces to

v

v

RF

dmOUT

,

dmIN

,

=

RG

The AD8475’s integrated resistors are precision wafer-lasertrimmed to guarantee a minimum CMRR of 86dB (50V/V),

and gain error of less that 0.05%. To achieve equivalent precision

and performance using a discrete solution, resistors must be

matched to 0.01% or better.

Rev. B | Page 17 of 24

Page 18

AD8475

INPUT VOLTAGE RANGE

The AD8475 can measure input voltages that are larger than the

supply rails. The internal gain and feedback resistors form a

divider, which reduces the input voltage seen by the internal

input nodes of the amplifier. The largest voltage that can be

measured is constrained by the capability of the amplifier’s

internal summing nodes. This voltage is defined by the input

voltage and the ratio between the feedback and the gain resistors.

Figure 51 shows the voltage at the internal summing nodes of

the amplifier, defined by the input voltage and internal resistor

network. If V

reduces to

The internal amplifier of the AD8475 has rail-to-rail inputs. To

obtain accurate measurements with minimal distortion, the

voltage at the internal inputs of the amplifier must stay below

− 1 V and above −VS.

+V

S

For example, with V

AD8475 can measure an input as high as ±12.5 V and maintain

its excellent distortion performance.

The AD8475 provides overvoltage protection for excessive input

voltages beyond the supply rails. Integrated ESD protection diodes

at the inputs prevent damage to the AD8475 up to +V

and −V

is grounded, the expression shown in the figure

N

RF

1

+

RG

2

− 16 V.

S

RG

==

VV

MINUSPLUS

= 5 V in a G = 0.4 configuration, the

S

⎛

VOCM

⎜

+

RGRF

⎝

V

P

⎞

⎟

⎠

+ 10.5 V

S

DRIVING THE AD8475

Care should be taken to drive the AD8475 with a low

impedance source: for example, another amplifier. Source

resistance can unbalance the resistor ratios and, therefore,

significantly degrade the gain accuracy and common-mode

rejection of the AD8475. For the best performance, source

impedance to the AD8475 input terminals should be kept

below 0.1 . Refer to the DC Precision section for details on

the critical role of resistor ratios in the precision of the AD8475.

POWER SUPPLIES

The AD8475 operates over a wide range of supply voltages. It

can be powered on a single supply as low as 3 V and as high as

10 V. The AD8475 can also operate on dual supplies from

±1.5 V up to ±5 V

A stable dc voltage should be used to power the AD8475. Note

that noise on the supply pins can adversely affect performance.

For more information, see the PSRR performance curve in

Figure 13.

Place a bypass capacitor of 0.1 F between each supply pin and

ground, as close as possible to each supply pin. Use a tantalum

capacitor of 10 F between each supply and ground. It can be

farther away from the supply pins and, typically, it can be

shared by other precision integrated circuits.

RF

V

ON

V

OP

RF

09432-164

RG

RF + RG

RG

V

P

1

RF

RG

− V

V

P

+

VOCM

2

Figure 51. Voltages at the Internal Op Amp Inputs of the AD8475

RF

+

N

RF + RG

V

VOCM

N

V

N

RG

Rev. B | Page 18 of 24

Page 19

AD8475

–V

APPLICATIONS INFORMATION

TYPICAL CONFIGURATION

The AD8475 is designed to facilitate single-ended-to-differential

conversion, common-mode level shifting, and precision attenuation

of large signals so that they are compatible with low voltage ADCs.

Figure 53 shows a typical connection diagram of the AD8475

in a gain of 0.4. To use the AD8475 in a gain of 0.8, drive the

±IN 0.8x inputs with a low impedance source.

SINGLE-ENDED TO DIFFERENTIAL CONVERSION

Many industrial systems use single-ended; however, the signals

are frequently processed by high performance differential input

ADCs for higher precision. The AD8475 performs the critical

function of precisely converting single-ended signals to the

differential inputs of precision ADCs, and it does so with no

need for external components.

To convert a single-ended signal to a differential signal, connect

one input to the signal source and the other input to ground (see

Figure 55). Note that either input can be driven by the source

with the only effect being that the outputs have reversed polarity.

The AD8475 also accepts truly differential input signals in

precision systems with differential signal paths.

SETTING THE OUTPUT COMMON-MODE VOLTAGE

The VOCM pin of the AD8475 is internally biased with a

precision voltage divider comprising two 200 kΩ resistors between

the supplies. This divider level shifts the output to midsupply.

Relying on the internal bias results in an output common-mode

voltage that is within 0.01% of the expected value.

In cases where control of the output common-mode level is

desired, an external source or resistor divider with source

resistance less than 100 Ω can be used to drive the VOCM pin.

If an external voltage divider consisting of equal resistor values

is used to set VOCM to midsupply, higher values can be used

because the external resistors are placed in parallel with the

internal resistors. The output common-mode offset listed in the

Specifications section assumes that the VOCM input is driven by a

low impedance voltage source.

Because of the internal divider, the VOCM pin sources and sinks

current, depending on the externally applied voltage and its

associated source resistance.

It is also possible to connect the VOCM input to the commonmode level output of an ADC; however, care must be taken to

ensure that the output has sufficient drive capability. The input

impedance of the VOCM pin is 100 kΩ. If multiple AD8475

devices share one ADC reference output, a buffer may be necessary to drive the parallel inputs.

S

LOW

IMPEDANCE

INPUT SO URCE

0.1µF 10µF

+IN 0.8x +IN 0.4x –V

1.25kΩ

1.25kΩ

–IN 0.8x –IN 0.4x +VSVOCM +OUT

Figure 52. Typical Configuration—10-Lead MSOP

S

1.25kΩ

1.25kΩ

+

0.1µF10µF

+V

S

+

NC –OUT

1kΩ

AD8475

1kΩ

0.1µF

REF

V

= (V

– V

OUT

+OUT

–OUT

)

09432-200

Rev. B | Page 19 of 24

Page 20

AD8475

–V

x

+IN 0.4

16

LOW

V

IMPEDANCE

INPUT SO URCE

IN

+IN 0.4x

+IN 0.8x

–IN 0.8x

–IN 0.4x

1

2

3

4

10µF

1.25kΩ

1.25kΩ

+

5

–IN 0.4x

0.1µF

Figure 53. Typical Configuration—16-Lead LFCSP

HIGH PERFORMANCE ADC DRIVING

The AD8475 is ideally suited for broadband dc-coupled and

industrial applications. The circuit in Figure 55 shows an

industrial front-end connection for an AD8475 driving an

AD7982, a 18-bit, 1 MSPS ADC, with dc coupling on the

AD8475 input and output. (The AD7982 achieves its optimum

performance when driven differentially.) The AD8475 performs

the attenuation of a 20 V p-p input signal, level shifts it, and

converts it to a differential signal without the need for any

external components. The AD8475 eliminates the need for dual

supplies at the front end to accept large bipolar signals. It also

eliminates the need for a precision resistor network for attenuation, and a transformer to drive the ADC and perform the singleended-to-differential conversion.

S

0.1µF 10µF

S

–V

15

1.25kΩ

AD8475

1.25kΩ

6

S

+V

+V

S

+

S

S

–V

–V

14

13

12

1kΩ

1kΩ

7

8

S

+V

+V

NC

11

–OUT

= (V

– V

REF

–OUT

)

09432-165

V

OUT

10

+OUT

9

VOCM

0.1µF

S

+OUT

The ac and dc performance of the AD8475 are compatible with

the 18-bit, 1 MSPS AD7982 PulSAR® ADC and other 16-bit and

18-bit members of the family, which have sampling rates up to

4 MSPS. Some suitable high performance differential ADCs are

listed in Table 6 .

Table 6. High Performance SAR ADCs

Sample

Part Resolution

AD7984 18 Bits 1.33 MSPS

Rate

Description

True differential input,

14 mW, 2.5 V ADC

AD7982 18 Bits 1 MSPS

True differential Input,

7.0 mW, 2.5 V ADC

AD7690 18 Bits 400 kSPS

True differential input,

4.5 mW, 5 V ADC

AD7641 18 Bits 2 MSPS

True differential input,

75 mW, 2.5 V ADC

In this example, the AD8475 is powered with a single 5 V

supply and used in a gain of 0.4, with a single-ended input

converted to a differential output. The input is a 20 V p-p

symmetric, ground-referenced bipolar signal. With an output

common-mode voltage of 2.5 V, each AD8475 output swings

between 0.5 V and 4.5 V, opposite in phase, providing an 8 V p-p

differential signal to the ADC input.

Rev. B | Page 20 of 24

Page 21

AD8475

V

The differential RC network between the AD8475 output and the

ADC provides a single-pole filter that reduces undesirable

aliasing effects and high frequency noise. The common-mode

bandwidth of the filter is 29.5 MHz (20 , 270 pF), and the

differential bandwidth is 3.1 MHz (40 , 1.3 nF).

The VOCM input is bypassed for noise reduction, and set

externally with 1% resistors to maximize output dynamic

range on a single 5 V supply.

09432-168

+10V

0V

20V

–10V

+7V TO +18V

NC

NC

+5V

+V

S

+IN 0.4x

+IN 0.8x

–IN 0.8x

–IN 0.4x

–V

S

AD8475

VOCM

–OUT

+OUT

20Ω

20Ω

270pF

270pF

Figure 54. FFT Results of the AD8475 Driving the AD7982

+4.5

4V

+2.5V

+0.5V

1.3nF

+4.5V

+2.5V +1.8V TO +5V

VDD

IN–

AD7982

IN+

GNDREF

+5V

VIO

SDI

SCK

SDO

CNV

2.5V

+0.5V

0.1µF

10kΩ

10kΩ

09432-167

ADR435

+5V

4V

Figure 55. Attenuation and Level Shifting of Industrial Voltages to Drive Single-Supply Precision ADC

Rev. B | Page 21 of 24

Page 22

AD8475

V

AD8475 EVALUATION BOARD

An evaluation board for the AD8475 is available to facilitate

standalone testing of the AD8475 performance and functionality

for customer evaluation and system design. The board provides

the user flexibility to configure the AD8475 in the desired gain

(0.4 or 0.8) and to install the suitable input and load impedances.

+

S

(GRN)

C4

10µF

C2

0.1µF

S

+IN 0.4x

–V

16

15

R2

IN+

IN–

0Ω

R1

0Ω

R5

J1

J2

R3

0Ω

R4

0Ω

R6

+IN 0.4x

+IN 0.8x

–IN 0.8x

–IN 0.4x

1

1.25kΩ

1.25kΩ

5

–IN 0.4x

1.25kΩ

1.25kΩ

6

S

+V

C1

0.1µF

2

3

4

+

S

–V

14

1kΩ

AD8475

1kΩ

7

S

+V

The AD8475-EVALZ board is designed so that a user can easily

evaluate system performance when the AD8475 is mated with

any Analog Devices, Inc., SAR ADC. The board can be installed

with SMB connectors that mate directly to the Pulsar® Analog-

to-Digital Converter Evaluation Kit.

See the AD8475 product page for more information on the

AD8475-EVALZ.

S

–V

13

12

NC

–OUT

+OUT

VOCM

0.1µF

R7

R9

R8

C5

R12

R10

R11

JP1

VOCM

11

10

9

8

S

+V

OUT–

OUT+

J4

J5

VOCM

J3

+

C3

10µF

+V

(RED)

S

09432-065

Figure 56. AD8475-EVALZ Schematic

Rev. B | Page 22 of 24

Page 23

AD8475

OUTLINE DIMENSIONS

PIN 1

INDICATOR

0.80

0.75

0.70

SEATING

PLANE

3.10

3.00 SQ

2.90

0.50

BSC

0.50

0.40

0.30

0.05 MAX

0.02 NOM

0.20 REF

0.30

0.25

0.20

13

12

9

8

BOTTOM VIEWTOP VIEW

COPLANARITY

0.08

N

1

P

I

C

I

N

I

16

EXPOSED

PAD

5

FOR PROPER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CONFIGURATION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

D

1

1.65

1.50 SQ

1.45

4

0.20 MIN

R

O

A

T

COMPLIANTTOJEDEC STANDARDS MO-229.

091609-A

Figure 57. 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ]

3 mm × 3 mm Body, Very Very Thin Quad

(CP-16-27)

Dimensions shown in millimeters

3.10

3.00

2.90

10

6

3.10

3.00

2.90

PIN 1

IDENTIFIER

0.95

0.85

0.75

0.15

0.05

COPLANARITY

0.10

1

0.50 BSC

COMPLIANT TO JEDEC STANDARDS MO-187-BA

5.15

4.90

4.65

5

15° MAX

6°

0°

0.23

0.13

0.70

0.55

0.40

091709-A

0.30

0.15

1.10 MAX

Figure 58. 10-Lead Mini Small Outline Package [MSOP]

(RM-10)

Dimensions shown in millimeters

Rev. B | Page 23 of 24

Page 24

AD8475

ORDERING GUIDE

Model1 Temperature Range Package Description Package Option Branding

AD8475ACPZ-R7 −40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] CP-16-27 Y3H

AD8475ACPZ-RL −40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] CP-16-27 Y3H

AD8475ACPZ-WP −40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] CP-16-27 Y3H

AD8475BRMZ −40°C to +85°C 10-Lead Lead Frame Chip Scale Package [MSOP] RM-10 Y41

AD8475BRMZ-R7 −40°C to +85°C 10-Lead Lead Frame Chip Scale Package [MSOP] RM-10 Y41

AD8475BRMZ-RL −40°C to +85°C 10-Lead Lead Frame Chip Scale Package [MSOP] RM-10 Y41

AD8475ARMZ −40°C to +85°C 10-Lead Lead Frame Chip Scale Package [MSOP] RM-10 Y31

AD8475ARMZ-R7 −40°C to +85°C 10-Lead Lead Frame Chip Scale Package [MSOP] RM-10 Y31

AD8475ARMZ-RL −40°C to +85°C 10-Lead Lead Frame Chip Scale Package [MSOP] RM-10 Y31

AD8475-EVALZ Evaluation Board

1

Z = RoHS Compliant Part.

©2010–2011 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D09432-0-4/11(B)

Rev. B | Page 24 of 24

Loading...

Loading...