Page 1

16 V Rail-to-Rail, Zero-Drift,

FEATURES

Resistor programmable gain range: 101 to 1000

Supply voltage range: ±4 V to ±8 V, +8 V to +16 V

Rail-to-rail input and output

Maintains performance over −40°C to +125°C

EXCELLENT AC AND DC PERFORMANCE

110 dB minimum CMR @ 60 Hz, G = 10 to 1000

10 µV max offset voltage (RTI, ±5 V)

50 nV/°C max offset drift

20 ppm max gain nonlinearity

APPLICATIONS

Pressure measurements

Temperature measurements

Strain measurements

Automotive diagnostics

GENERAL DESCRIPTION

The AD8230 is a low drift, differential sampling, precision

instrumentation amplifier. Auto-zeroing reduces offset voltage

drift to less than 50 nV/°C. The AD8230 is well-suited for

thermocouple and bridge transducer applications. The

AD8230’s high CMR of 110 dB (min) rejects line noise in

measurements where the sensor is far from the instrumentation.

The 16 V rail-to-rail, common-mode input range is useful for

noisy environments where ground potentials vary by several

volts. Low frequency noise is kept to a minimal 3 µV p-p

making the AD8230 perfect for applications requiring the

utmost dc precision. Moreover, the AD8230 maintains its high

performance over the extended industrial temperature range of

−40°C to +125°C.

Two external resistors are used to program the gain. By using

matched external resistors, the gain stability of the AD8230 is

much higher than instrumentation amplifiers that use a single

resistor to set the gain. In addition to allowing users to program

the gain between 10

offset voltage.

1

and 1000, users may adjust the output

Precision Instrumentation Amplifier

AD8230

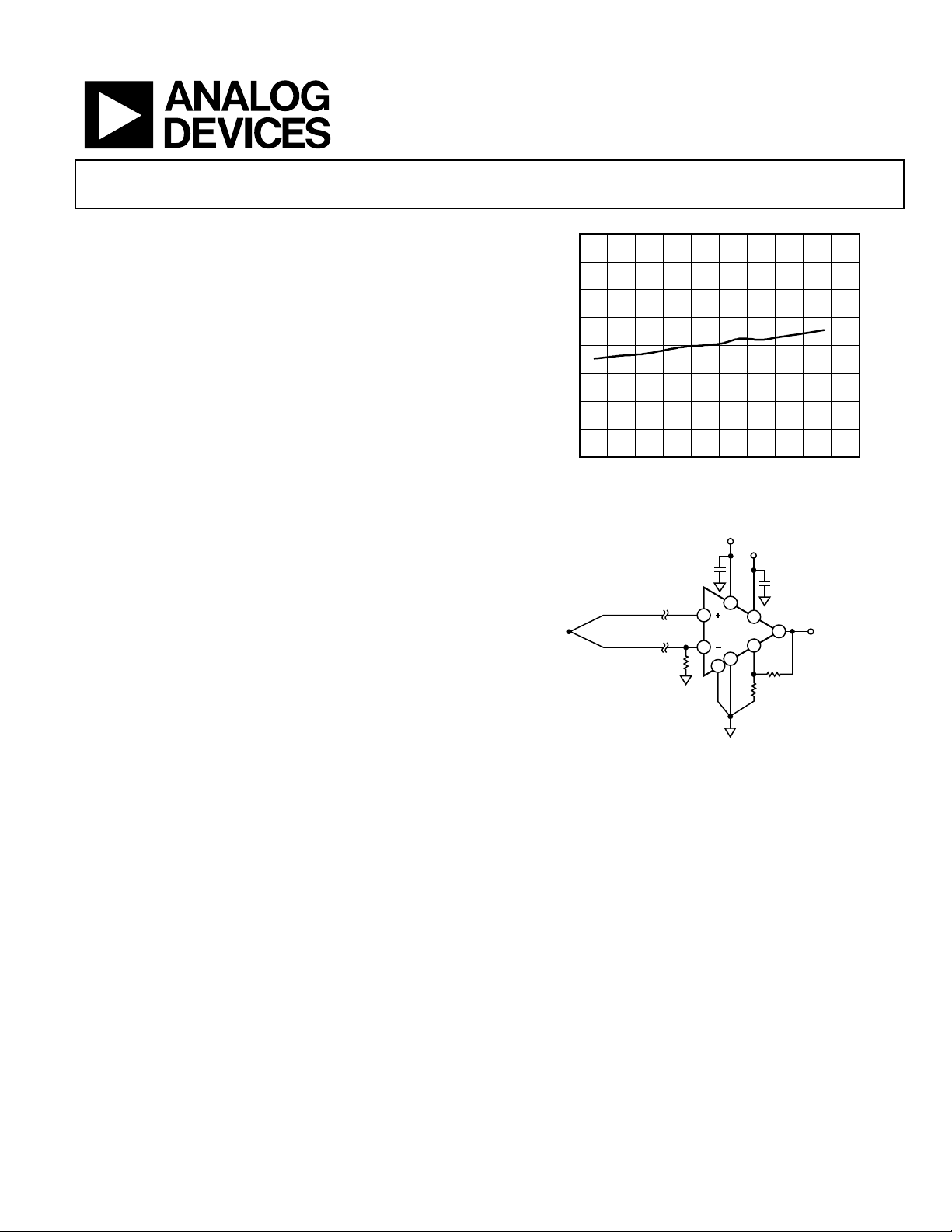

2.0

1.5

1.0

0.5

0

–0.5

–1.0

OFFSET VOLTAGE (µV RTI)

–1.5

–2.0

TEMPERATURE (°C)

Figure 1. Relative Offset Voltage vs. Temperature

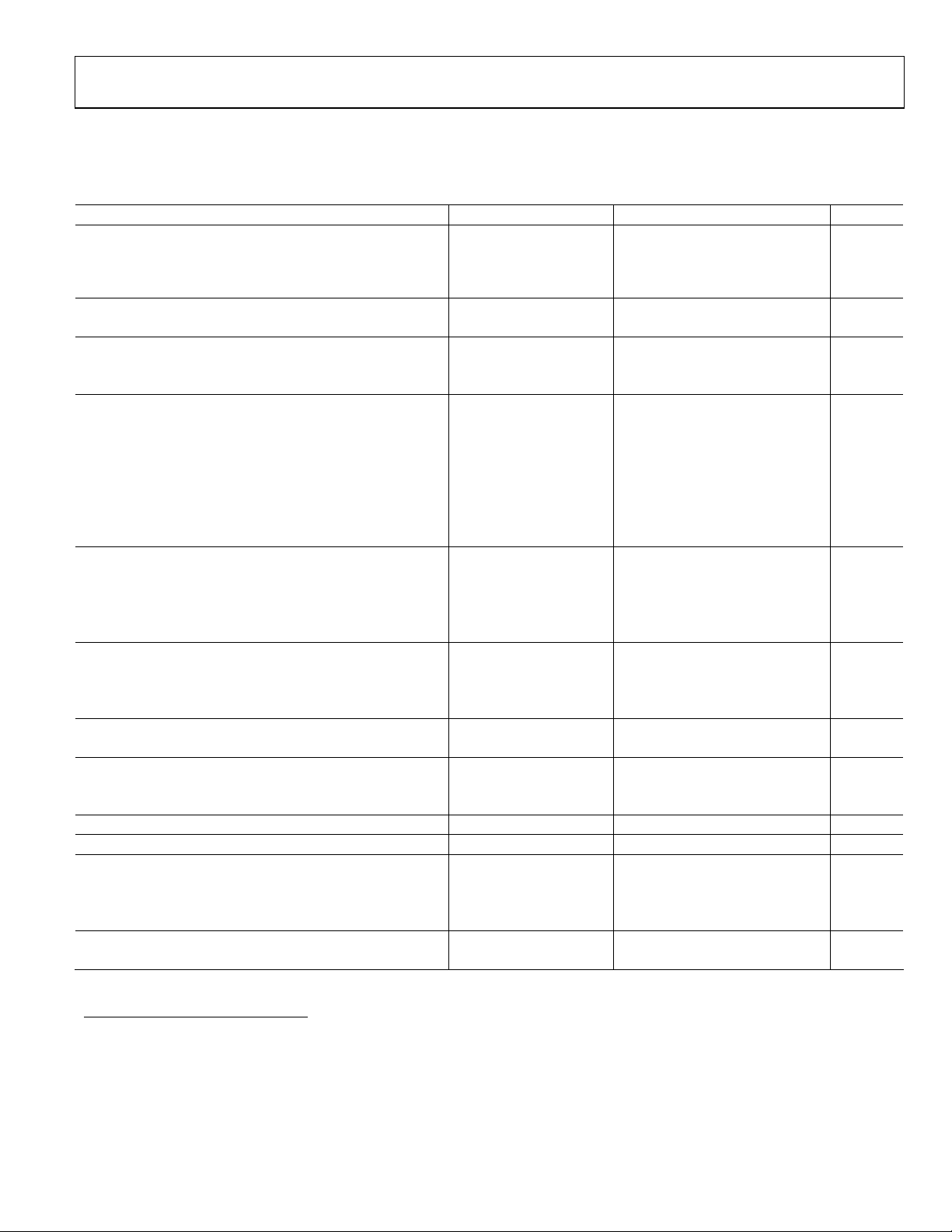

+5V

–5V

0.1µF

4

TYPE K THERMOCOUPLE

Figure 2. Thermocouple Measurement

AD8230

5

3

0.1µF

2

1

7

6

34.8kΩ

284Ω

V

8

OUT

The AD8230 is versatile yet simple to use. Its auto-zeroing

topology significantly minimizes the input and output

transients typical of commutating or chopper instrumentation

amplifiers. The AD8230 operates on ±4 V to ±8 V (+8 V to +16 V)

supplies and is available in an 8-lead SOIC.

1

The AD8230 can be programmed for a gain as low as 2, but the maximum

input voltage is limited to approximately 750 mV.

150–50 –30 –10 10 30 50 70 90 110 130

05063-002

05063-107

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

Page 2

AD8230

TABLE OF CONTENTS

Specifications..................................................................................... 3

Input Voltage Range ................................................................... 11

Absolute Maximum Ratings............................................................ 5

ESD Caution.................................................................................. 5

Typical Performance Characteristics............................................. 6

Theory of Operation ...................................................................... 10

Setting the Gain.......................................................................... 10

Level-Shifting the Output.......................................................... 11

Source Impedance and Input Settling Time ........................... 11

REVISION HISTORY

10/04—Revision 0: Initial Version

Input Protection ......................................................................... 11

Power Supply Bypassing ............................................................ 11

Power Supply Bypassing for Multiple Channel Systems ....... 11

Layout .......................................................................................... 12

Applications ................................................................................ 12

Outline Dimensions....................................................................... 13

Ordering Guide .......................................................................... 13

Rev. 0 | Page 2 of 16

Page 3

AD8230

SPECIFICATIONS

VS = ±5 V, V

Table 1.

Parameter Conditions Min Typ Max Unit

VOLTAGE OFFSET

RTI Offset, V

Offset Drift

COMMON-MODE REJECTION (CMR)

CMR to 60 Hz with 1 kΩ Source Imbalance VCM = −5 V to +5 V 110 120 dB

VOLTAGE OFFSET RTI vs. SUPPLY (PSR)

G = 2 120 120 dB

G = 202 120 140 dB

GAIN G = 2(1 + RF/RG)

Gain Range 10

Gain Error

G = 2 0.01 %

G = 10 0.01 %

G = 100 0.01 %

G = 1000 0.02 %

Gain Nonlinearity 20 ppm

INPUT

Input Common-Mode Operating Voltage Range −V

Over Temperature T = −40°C to +125°C −V

Input Differential Operating Voltage Range 750 mV

Average Input Offset Current

OUTPUT

Output Swing −VS + 0.1 +VS − 0.2 V

Over Temperature T = −40°C to +125°C −VS + 0.1 +VS − 0.2 V

Short-Circuit Current 15 mA

REFERENCE INPUT

Voltage Range −1 +1 V

NOISE

Voltage Noise Density, 1 kHz, RTI V

Voltage Noise f = 0.1 Hz to 10 Hz 3 µV p-p

SLEW RATE VIN = 500 mV, G = 10 2 V/µs

INTERNAL SAMPLE RATE 6 kHz

POWER SUPPLY

Operating Range (Dual Supplies) ±4 ±8 V

Operating Range (Single Supply) +8 +16 V

Quiescent Current T = −40°C to +125°C 2.7 3.5 mA

TEMPERATURE RANGE

Specified Performance −40 +125 °C

= 0 V, RF = 100 kΩ, RG = 1 kΩ (@ TA = 25°C, G = 202, RL = 10 kΩ, unless otherwise noted).

REF

V

OSI

2

= V

+IN

V

+IN

T

A

= 0 V 10 µV

−IN

= V

= 0 V,

−IN

50 nV/°C

= −40°C to +125°C

1

S

S

VCM = 0V 33 pA

, V

, V

IN+

= 0 240 nV/√Hz

IN−

REF

1000 V/V

+V

+V

S

S

V

V

1

The AD8230 can operate as low as G = 2. However, since the differential input range is limited to approximately 750 mV, the AD8230 configured at G < 10 does not

make use of the full output voltage range.

2

Differential source resistance less than 10 kΩ does not result in voltage offset due to input bias current or mismatched series resistors.

Rev. 0 | Page 3 of 16

Page 4

AD8230

VS = ±8 V, V

Table 2.

Parameter Conditions Min Typ Max Unit

VOLTAGE OFFSET

RTI Offset, V

Offset Drift

COMMON-MODE REJECTION (CMR)

CMR to 60 Hz with 1 kΩ Source Imbalance VCM = −8 V to +8 V 110 120 dB

VOLTAGE OFFSET RTI vs. SUPPLY (PSR)

G = 2 120 120 dB

G = 202 120 140 dB

GAIN G = 2(1 + RF/RG)

Gain Range 10

Gain Error

G = 2 0.01 %

G = 10 0.01 %

G = 100 0.01 %

G = 1000 0.02 %

Gain Nonlinearity 20 ppm

INPUT

Input Common-Mode Operating Voltage Range −V

Over Temperature T = −40°C to +125°C −V

Input Differential Operating Voltage Range 750 mV

Average Input Offset Current

OUTPUT

Output Swing −VS + 0.1 +VS − 0.2 V

Over Temperature T = −40°C to +125°C −VS + 0.1 +VS − 0.4 V

Short-Circuit Current 15 mA

REFERENCE INPUT

Voltage Range −1 +1 V

NOISE

Voltage Noise Density, 1 kHz, RTI V

Voltage Noise f = 0.1 Hz to 10 Hz 3 µV p-p

SLEW RATE VIN = 500 mV, G = 10 2 V/µs

INTERNAL SAMPLE RATE 6 kHz

POWER SUPPLY

Operating Range (Dual Supplies) ±4 ±8 V

Operating Range (Single Supply) +8 +16 V

Quiescent Current T = −40°C to +125°C 3.2 4 mA

TEMPERATURE RANGE

Specified Performance −40 +125 °C

1

The AD8230 can operate as low as G = 2. However, since the differential input range is limited to approximately 750 mV, the AD8230 configured at G < 10 does not

make use of the full output voltage range.

2

Differential source resistance less than 10 kΩ does not result in voltage offset due to input bias current or mismatched series resistors.

= 0 V, RF = 100 kΩ, RG = 1 kΩ (@ TA = 25°C, G = 202, RL = 10 kΩ, unless otherwise noted).

REF

V

OSI

= V

+IN

V

+IN

= 0 V 20 µV

−IN

= V

= 0 V,

−IN

50 nV/°C

T = −40°C to +125°C

1

S

S

2

VCM = 0V 33 pA

, V

, V

IN+

= 0 240 nV/√Hz

IN−

REF

1000 V/V

+V

+V

S

S

V

V

Rev. 0 | Page 4 of 16

Page 5

AD8230

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage ±8 V, +16 V

Internal Power Dissipation 304 mW

Output Short-Circuit Current 20 mA

Input Voltage (Common-Mode) ±V

Differential Input Voltage ±V

S

S

Storage Temperature −65°C to +150°C

Operational Temperature Range −40°C to +125°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions may affect device reliability.

CONNECTION DIAGRAM

1

–V

S

2

+V

S

3

V

1

REF

4

+IN

AD8230

TOP VIEW

(Not to Scale)

Figure 3.

8

V

OUT

7

R

G

6

V

2

REF

5

–IN

05063-001

Specification is for device in free air: SOIC: θ

(4-layer JEDEC

JA

board) = 121°C/W.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

this product features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

Rev. 0 | Page 5 of 16

Page 6

AD8230

TYPICAL PERFORMANCE CHARACTERISTICS

TOTAL NUMBER OF

500

SAMPLES = 2839 FROM 3 LOTS

20

NORMALIZED FOR VCM = 0V

15

400

300

SAMPLES

200

100

0

OFFSET VOLTAGE (µV RTI)

Figure 4. Offset Voltage (RTI) Distribution at ±5 V, CM = 0 V, T

SAMPLES

40

35

30

25

20

15

10

5

0

TOTAL NUMBER OF SAMPLES = 300 FROM 3 LOTS

OFFSET VOLTAGE DRIFT (nV/°C)

Figure 5. Offset Voltage (RTI) Drift Distribution

9–9 –3–6 036

= +25°C

A

50–50 –30 –10 10 30

05063-100

05063-108

10

5

0

–5

–10

OFFSET VOLTAGE (µV RTI)

–15

–20

–2 0–6 –4 2 4 6

COMMON-MODE VOLTAGE (V)

Figure 7. Offset Voltage (RTI) vs. Common-Mode Voltage, V

20

NORMALIZED FOR VCM = 0V

15

10

5

0

–5

–10

OFFSET VOLTAGE (µV RTI)

–15

–20

–10–8–6–4–20246810

COMMON-MODE VOLTAGE (V)

Figure 8. Offset Voltage (RTI) vs. Common-Mode Voltage, V

= ±5 V

S

= ±8 V

S

05063-007

05063-008

0

–2

–4

–6

–8

–10

–12

–14

OFFSET VOLTAGE (µV RTI)

–16

–18

–20

TEMPERATURE (°C)

VS = ±5V

V

= ±8V

S

05063-005

150–50 –30 –10 10 7030 50 110 13090

Figure 6. Offset Voltage (RTI) vs. Temperature

0

–1

–2

–3

–4

–5

OFFSET VOLTAGE (µV)

–6

–7

–8

±5V SUPPLY

±8V SUPPLY

2301 456

SOURCE IMPEDANCE (kΩ)

05063-009

Figure 9. Offset Voltage (RTI) vs. Source Impedance, 1 µF Across Input Pins

Rev. 0 | Page 6 of 16

Page 7

AD8230

40

30

20

10

0

–10

–20

OFFSET VOLTAGE (µV RTI)

–30

–40

NORMALIZED FOR V

= 0V

REF

–0.5 0–1.5 –1.0 0.5 1.0 1.5

V

(V)

REF

Figure 10. Offset Voltage (RTI) vs. Reference Voltage

05063-010

6.8k

6.6k

6.4k

±8V

6.2k

6.0k

5.8k

CLOCK FREQUENCY (Hz)

5.6k

5.4k

–50 –30 –10 10 30 50 70 90 110 130

TEMPERATURE (°C)

±5V

Figure 13. Clock Frequency vs. Temperature

05063-013

130

120

110

100

90

80

CMR (dB)

70

60

50

40

10 100 1k 10k

CMR WITH NO SOURCE IMBALANCE

CMR WITH 1k SOURCE IMBALANCE

FREQUENCY (Hz)

Figure 11. Commo n-Mode Re jection vs. Frequen cy

130

128

126

124

122

120

CMR (dB)

118

116

114

112

110

±5V SUPPLY

±8V SUPPLY

4602 81012

SOURCE IMPEDANCE (kΩ)

Figure 12. Common-Mode Rejection vs.

Source Impedance, 1.1 µF Across Input Pins

05063-011

05063-012

1.0

0.8

0.6

0.4

0.2

0

–0.2

–0.4

0°C

–0.6

AVERAGE INPUT BIAS CURRENT (µA)

–0.8

–1.0

+25°C

–2 0–6–4 246

COMMON-MODE VOLTAGE (V)

+85°C

+125°C

–40°C

Figure 14. Average Input Bias Current vs. Common-Mode Voltage

−40°C, +25°C, +85°C, +125°C

3.5

3.4

3.3

3.2

3.1

3.0

2.9

2.8

2.7

POSITIVE SUPPLY CURRENT (mA)

2.6

2.5

0–50 50 100 150

TEMPERATURE (°C)

±8V

±5V

Figure 15. Supply Current vs. Temperature

05063-020

05063-018

Rev. 0 | Page 7 of 16

Page 8

AD8230

90

80

70

60

50

40

GAIN (dB)

30

20

10

0

–10

10010 1k 10k 100k

FREQUENCY (Hz)

Figure 16. Gain vs. Frequency, G = 2

05063-014

90

80

70

60

50

40

GAIN (dB)

30

20

10

0

–10

10010 1k 10k 100k

FREQUENCY (Hz)

05063-016

Figure 19. Gain vs. Frequency, G = 100

90

80

70

60

50

40

GAIN (dB)

30

20

10

0

–10

10010 1k 10k 100k

FREQUENCY (Hz)

Figure 17. Gain vs. Frequency, G = 10

40

G = +20

30

20

10

0

–10

NONLINEARITY (ppm)

–20

–30

–40

–5 –4 –3 –2 –1 0 1 2 3 4 5

V

(V)

OUT

Figure 18. Gain Nonlinearity, G = 20

05063-015

05063-019

90

80

70

60

50

40

GAIN (dB)

30

20

10

0

–10

10010 1k 10k 100k

FREQUENCY (Hz)

Figure 20. Gain vs. Frequency, G = 1000

0.010

0.008

0.006

0.004

0.002

0

–0.002

GAIN ERROR (%)

–0.004

–0.006

–0.008

–0.010

50101520

SOURCE IMPEDANCE (kΩ)

Figure 21. Gain Error vs. Differential Source Impedance

05063-017

05063-036

Rev. 0 | Page 8 of 16

Page 9

AD8230

0.35

140

0.30

0.25

0.20

V/ Hz

0.15

µ

0.10

0.05

0

FREQUENCY (Hz)

Figure 22. Voltage Noise Spectral Density

3.90

3.70

3.50

3.30

3.10

2.90

POSITIVE SUPPLY CURRENT (mA)

2.70

2.50

2µV/DIV 1s/DIV

–50 –30 –10 10 30 50 70 90 110 130

TEMPERATURE (°C)

Figure 23. 0.1 Hz to 10 Hz RTI Voltage Noise (G = 100)

120

100

80

60

PSR (dB)

40

20

05063-024

100k1 10 100 1k 10k

0

0.1 1 10

G = +100

G = +1000

G = +2

FREQUENCY (kHz)

G = +10

05063-035

Figure 25. Negat ive PSR vs. Frequenc y, RTI

05063-102

10

–2

–4

–6

OUTPUT VOLTAGE SWING (V)

–8

–10

8

6

4

2

0

V

= ±8V

S

VS = ±5V

= ±5V

V

S

V

= ±8V

S

–40°C

+125°C

+125°C

–40°C

OUTPUT CURRENT (mA)

–40°C

+125°C

+125°C

–40°C

+25°C

+25°C

+25°C

+25°C

120246810

05063-109

Figure 26. Output Voltage Swing vs. Output Current,

−40°C, +25°C, +85°C, +125°C

160

140

G = +100

G = +2

G = +1000

G = +10

120

100

80

PSR (dB)

60

40

20

0

0.1 1 10

FREQUENCY (kHz)

Figure 24. Posit ive PSR vs. Frequ ency, RTI

05063-034

Rev. 0 | Page 9 of 16

Page 10

AD8230

V

+V

V

+V

THEORY OF OPERATION

Auto-zeroing is a dynamic offset and drift cancellation technique that reduces input referred voltage offset to the µV level

and voltage offset drift to the nV/°C level. A further advantage

of dynamic offset cancellation is the reduction of low frequency

noise, in particular the 1/f component.

The AD8230 is an instrumentation amplifier that uses an

auto-zeroing topology and combines it with high commonmode signal rejection. The internal signal path consists of an

active differential sample-and-hold stage (preamp) followed by

a differential amplifier (gain amp). Both amplifiers implement

auto-zeroing to minimize offset and drift. A fully differential

topology increases the immunity of the signals to parasitic noise

and temperature effects. Amplifier gain is set by two external

resistors for convenient TC matching.

The signal sampling rate is controlled by an on-chip, 6 kHz

oscillator and logic to derive the required nonoverlapping

clock phases. For simplification of the functional description,

two sequential clock phases, A and B, are used to distinguish

the order of internal operation, as depicted in Figure 27 and

Figure 28, respectively.

PREAMP

V

DIFF

+IN

C

CM

V

–IN

SAMPLE

–

+

–

+

V

REF

Figure 27. Phase A of the Sampling Phase

During Phase A, the sampling capacitors are connected to the

inputs. The input signal’s difference voltage, V

across the sampling capacitors, C

SAMPLE

capacitors only retain the difference voltage, the common-mode

voltage is rejected. During this period, the gain amplifier is not

connected to the preamplifier so its output remains at the level

set by the previously sampled input signal held on C

shown in Figure 27.

PREAMP

V

+IN

DIFF

CM

V

C

SAMPLE

–IN

Figure 28. Phase B of the Sampling Phase

–

+

–

+

V

REF

GAIN AMP

–V

S

C

HOLD

C

HOLD

–V

S

R

G

R

, is stored

DIFF

V

OUT

F

. Since the sampling

HOLD

GAIN AMP

–V

S

C

HOLD

C

HOLD

–V

S

R

G

V

OUT

R

F

05063-103

, as

05063-104

In Phase B, the differential signal is transferred to the hold

capacitors refreshing the value stored on C

. The output of

HOLD

the preamplifier is held at a common-mode voltage determined

by the reference potential, V

. In this manner, the AD8230 is

REF

able to condition the difference signal and set the output voltage

level. The gain amplifier conditions the updated signal stored on

the hold capacitors, C

HOLD

.

SETTING THE GAIN

Two external resistors set the gain of the AD8230. The gain is

expressed in the following function:

R

10µF

F

F

)2(1

R

G

+V

0.1µF

4

AD8230

V

REF2

5

V

REF1

3

Figure 29. Gain Setting

S

–V

S

0.1µF

2

1

R

G

7

6

R

F

R

G

R

G

10µF

V

8

OUT

05063-030

Actual Gain

, small. This is due

F

pin, Pin 7. The effect

G

Gain +=

Table 4. Gains Using Standard 1% Resistors

Gain R

2 0 Ω (short) None 2

10 8.06 kΩ 2 kΩ 10

50 12.1 kΩ 499 Ω 50.5

100 9.76 kΩ 200 Ω 99.6

200 10 kΩ 100 Ω 202

500 49.9 kΩ 200 Ω 501

1000 100 kΩ 200 Ω 1002

Figure 29 and Table 4 provide an example of some gain settings.

As Table 4 shows, the AD8230 accepts a wide range of resistor

values. Since the instrumentation amplifier has finite driving

capability, make sure that the output load in parallel with the

sum of the gain setting resistors is greater than 2 kΩ.

||(RF + RG) > 2 kΩ

R

L

Offset voltage drift at high temperature can be minimized by

keeping the value of the feedback resistor, R

to the junction leakage current on the R

of the gain setting resistor on offset voltage drift is shown in

Figure 30. In addition, experience has shown that wire-wound

resistors in the gain feedback loop may degrade the offset

voltage performance.

Rev. 0 | Page 10 of 16

Page 11

AD8230

0

–1

–2

–3

OFFSET VOLTAGE (µV RTI)

–4

–5

RF = 100kΩ, RG = 1kΩ

R

F

TEMPERATURE (°C)

= 10kΩ, RG = 100Ω

150–50 0 50 100

Figure 30. Effect of Feedback Resistor on Offset Voltage Drift

LEVEL-SHIFTING THE OUTPUT

A reference voltage, as shown in Figure 31, can be used to levelshift the output 1 V from midsupply. Otherwise, it is nominally

tied to midsupply. The voltage source used to level-shift the

output should have a low output impedance to avoid contributing to gain error. In addition, it should be able to source and

sink current. To minimize offset voltage, the V

pins should be

REF

connected either to the local ground or to a reference voltage

source that is connected to the local ground.

+V

S

–V

S

0.1µF

0.1µF

2

4

5

AD8230

6

3

1

7

R

R

G

V

8

F

LEVEL-SHIFT

V

OUT

+–VS)

(+V

S

=

2

Figure 31. Level-Shifting the Output

± 1V

05063-031

SOURCE IMPEDANCE AND INPUT SETTLING TIME

The input stage of the AD8230 consists of two actively driven,

differential switched capacitors, as described in Figure 27 and

Figure 28. Differential input signals are sampled on C

that the associated parasitic capacitances, 70 pF, are balanced

between the inputs to achieve high common-mode rejection.

On each sample period (approximately 85 µs), these parasitic

capacitances must be recharged to the common-mode voltage

by the signal source impedance (10 kΩ max).

SAMPLE

such

05063-110

INPUT VOLTAGE RANGE

The input common-mode range of the AD8230 is rail to rail.

However, the differential input voltage range is limited to,

approximately, 750 mV. The AD8230 does not phase invert

when its inputs are overdriven.

INPUT PROTECTION

The input voltage is limited to within one diode drop beyond

the supply rails by the internal ESD protection diodes. Resistors

and low leakage diodes may be used to limit excessive, external

voltage and current from damaging the inputs, as shown in

Figure 32. Figure 34 shows an overvoltage protection circuit

between the thermocouple and the AD8230.

+V

S

–V

BAV199

0.1µF

+V

–V

S

S

2.49kΩ

2.49kΩ

+V

BAV199

4

AD8230

5

–V

S

S

Figure 32. Overvoltage Input Protection

S

0.1µF

2

1

7

6

19.1kΩ

3

200Ω

V

8

OUT

05063-037

POWER SUPPLY BYPASSING

A regulated dc voltage should be used to power the instrumentation amplifier. Noise on the supply pins may adversely affect

performance. Bypass capacitors should be used to decouple

the amplifier.

The AD8230 has internal clocked circuitry that requires

adequate supply bypassing. A 0.1 µF capacitor should be placed

as close to each supply pin as possible. As shown in Figure 29,

a 10 µF tantalum capacitor may be used further away from

the part.

POWER SUPPLY BYPASSING FOR MULTIPLE CHANNEL SYSTEMS

The best way to prevent clock interference in multichannel

systems is to lay out the PCB with a star node for the positive

supply and a star node for the negative supply. Each AD8230

has a pair of traces leading to the star nodes. Using such a technique, crosstalk between clocks is minimized. If laying out star

nodes is unfeasible, then use thick traces to minimize parasitic

inductance and decouple frequently along the power supply

traces. Examples are shown in Figure 33. Care and forethought

go a long way in maximizing performance.

Rev. 0 | Page 11 of 16

Page 12

AD8230

–V

S

+V

10µF

10µF

0.1µF

S

0.1µF

–V

S

1

+V

S

2

3

0.1µF

4

AD8230

0.1µF

–V

S

1

+V

2

3

4

S

AD8230

8

7

6

5

0.1µF

Figure 33. Use Star Nodes for +V

8

7

6

5

0.1µF

1µF 1µF 1µF

0.1µF

–V

S

1

+V

S

2

3

0.1µF

4

AD8230

STAR –V

STAR +V

–V

S

1

+V

2

3

4

S

AD8230

8

7

6

5

and −VS or Use Thick Traces and Decouple Frequently Along the Supply Lines

S

LAYOUT

The AD8230 has two reference pins: V

draws current to set the internal voltage references. In

contrast, V

2 does not draw current. It sets the common

REF

mode of the output signal. As such, V

be star-connected to ground (or to a reference voltage). In

addition, to maximize CMR, the trace between V

gain resistor, R

, should be kept short.

G

REF

1 and V

REF

1 and V

2. V

REF

2 should

REF

2 and the

REF

REF

1

APPLICATIONS

+V

–V

0.1µF

S

S+VS

4

AD8230

5

3

S

–V

S

0.1µF

2

1

7

6

19.1kΩ

200Ω

V

8

OUT

BAV199

+V

S

+V

S

THERMOCOUPLE

TYPE J

100MΩ

100MΩ

4.99kΩ

4.99kΩ

–V

S

1nF

1nF

1µF

–V

BAV199

Figure 34. Type J Thermocouple with Overvoltage Protection and RFI Filter

The AD8230 may be used in thermocouple applications, as

shown in Figure 2 and Figure 34. Figure 34 is an example of

such a circuit for use in an industrial environment. It has

voltage overload protection (see the Input Protection section

for more information) and an RFI filter in front. The matched

100 MΩ resistors serve to provide input bias current to the

input transistors and also serve as an indicator as to when the

8

7

6

5

S

10µF

S

05063-032

0.1µF

1µF

8

7

6

5

–V

1

+V

2

3

4

0.1µF

0.1µF

S

S

AD8230

–V

1

+V

2

3

4

S

S

AD8230

8

7

6

5

0.1µF

10µF

–V

1

+V

2

3

4

S

S

AD8230

0.1µF

8

7

6

5

0.1µF

1

2

3

4

0.1µF

–V

+V

0.1µF

1

2

3

4

S

S

AD8230

–V

S

+V

S

AD8230

8

7

6

5

0.1µF

0.1µF

thermocouple connection is broken. Well-matched 1% 4.99 kΩ

resistors are used in the RFI filter. It is good practice to match

the source impedances to ensure high CMR. The circuit is

configured for a gain of 193, which provides an overall

temperature sensitivity of 10 mV/°C.

+V

S

–V

S

0.1µF

1

7

102kΩ

1kΩ

0.1µF

8

4kΩ

+V

S

350Ω

350Ω 350Ω

350Ω

–V

S

2

4

AD8230

5

6

3

Figure 35. Bridge Measurement with Filtered Output

Measuring load cells in industrial environments can be a

challenge. Often, the load cell is located some distance away

from the instrumentation amplifier. The common-mode

potential can be several volts, exceeding the common-mode

input range of many 5 V auto-zero instrumentation amplifiers.

Fortunately, the AD8230’s wide common-mode input voltage

range spans 16 V, relieving designers of having to worry about

the common-mode range.

1µF

8

7

6

5

05063-106

V

OUT

05063-033

Rev. 0 | Page 12 of 16

Page 13

AD8230

OUTLINE DIMENSIONS

5.00 (0.1968)

4.80 (0.1890)

4.00 (0.1574)

3.80 (0.1497)

85

6.20 (0.2440)

5.80 (0.2284)

41

1.27 (0.0500)

BSC

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

0.10

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MS-012AA

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

0.25 (0.0098)

0.17 (0.0067)

0.50 (0.0196)

0.25 (0.0099)

8°

1.27 (0.0500)

0°

0.40 (0.0157)

× 45°

Figure 36. 8-Lead Standard Small Outline Package [SOIC]

Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD8230YRZ

AD8230YRZ-REEL1 −40°C to +125°C 8-Lead SOIC, 13" Tape and Reel R-8

AD8230YRZ-REEL71 −40°C to +125°C 8-Lead SOIC, 7" Tape and Reel R-8

AD8230-EVAL Evaluation Board

1

Z = Pb-free part.

1

−40°C to +125°C 8-Lead SOIC R-8

Rev. 0 | Page 13 of 16

Page 14

AD8230

NOTES

Rev. 0 | Page 14 of 16

Page 15

AD8230

NOTES

Rev. 0 | Page 15 of 16

Page 16

AD8230

NOTES

© 2004 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D05063–0–10/04(0)

Rev. 0 | Page 16 of 16

Loading...

Loading...