Page 1

Low Voltage, Low Power,

a

Factory-Calibrated 16-/24-Bit Dual - ADC

FEATURES

HIGH RESOLUTION - ADCs

Two Independent ADCs (16- and 24-Bit Resolution)

Factory-Calibrated (Field Calibration Not Required)

Output Settles in One Conversion Cycle (Single

Conversion Mode)

Programmable Gain Front End

Simultaneous Sampling and Conversion of Two

Signal Sources

Separate Reference Inputs for Each Channel

Simultaneous 50 Hz and 60 Hz Rejection at 20 Hz

Update Rate

ISOURCE Select

TM

24-Bit No Missing Codes—Main ADC

13-Bit p-p Resolution @ 20 Hz, 20 mV Range

18-Bit p-p Resolution @ 20 Hz, 2.56 V Range

INTERFACE

3-Wire Serial

TM

, QSPITM, MICROWIRETM and DSP-Compatible

SPI

Schmitt Trigger on SCLK

POWER

Specified for Single 3 V and 5 V Operation

Normal: 1.5 mA Typ @ 3 V

Power-Down: 10 A (32 kHz Crystal Running)

ON-CHIP FUNCTIONS

Rail-Rail Input Buffer and PGA

4-Bit Digital I/O Port

On-Chip Temperature Sensor

Dual Switchable Excitation Current Sources

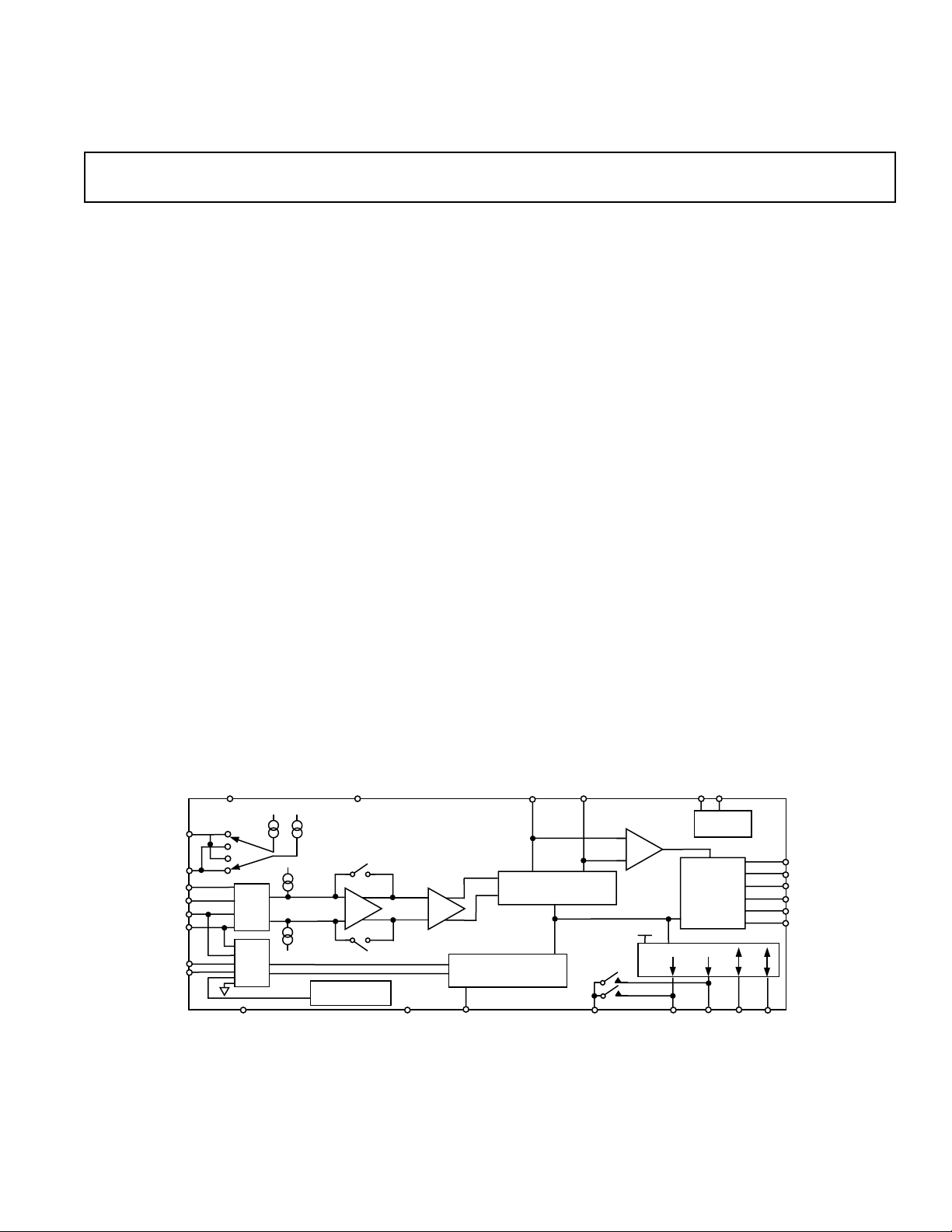

FUNCTIONAL BLOCK DIAGRAM

IOUT1

DV

DD

IEXC1

200A

AV

DD

IEXC2

200A

DGND

AD7719

AD7719

Low-Side Power Switches

Reference Detect Circuit

APPLICATIONS

Sensor Measurement

Temperature Measurement

Pressure Measurements

Weigh Scales

Portable Instrumentation

4–20 mA Transmitters

GENERAL DESCRIPTION

The AD7719 is a complete analog front end for low frequency

measurement applications. It contains two high resolution sigmadelta ADCs, switchable matched excitation current sources,

low-side power switches, digital I/O port, and temperature

sensor. The 24-bit main channel with PGA accepts fully differential, unipolar, and bipolar input signal ranges from 1.024 ×

REFIN1/128 to 1.024 × REFIN1. Signals can be converted

directly from a transducer without the need for signal conditioning. The 16-bit auxiliary channel has an input signal range

of REFIN2 or REFIN2/2.

The device operates from a 32 kHz crystal with an on-chip

PLL generating the required internal operating frequency. The

output data rate from the part is software programmable. The

peak-to-peak resolution from the part varies with the programmed

gain and output data rate.

The part operates from a single 3 V or 5 V supply. When operating from 3 V supplies, the power dissipation for the part is

4.5 mW with both ADCs enabled and 2.85 mW with only the

main ADC enabled in unbuffered mode. The AD7719 is housed

in 28-lead SOIC and TSSOP packages.

XTAL1 XTAL2REFIN1(+) REFIN1(–)

REFERENCE

DETECT

OSC. AND

PLL

IOUT2

AIN1

AIN2

AIN3

AIN4

AIN5

AIN6

ISOURCE Select is a trademark of Analog Devices.

SPI and QSPI are trademarks of Motorola Inc.

MICROWIRE is a trademark of National Semiconductor Corporation.

MUX1

MUX2

AV

MUX

DD

AV

DD

AGND

BUF

TEMP

SENSOR

PGA

AUXILIARY CHANNEL

AGND REFIN2 PWRGND P1/SW1 P2/SW2 P3 P4

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

MAIN CHANNEL

24-BIT - ADC

AV

DD

I/O PORT

16-BIT - ADC

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

SERIAL

INTERFACE

AND

CONTROL

LOGIC

DOUT

DIN

SCLK

CS

RDY

RESET

Page 2

AD7719

TABLE OF CONTENTS

FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . 1

SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . 6

ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . 7

DIGITAL INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

PIN CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

PIN FUNCTION DESCRIPTIONS . . . . . . . . . . . . . . . . . . 9

TYPICAL PERFORMANCE CHARACTERISTICS . . . . 11

DUAL-CHANNEL ADC CIRCUIT INFORMATION . . . 12

Main Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Auxiliary Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Both Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

MAIN AND AUXILIARY ADC NOISE

PERFORMANCE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

ON-CHIP REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Communications Register

(A3, A2, A1, A0 = 0, 0, 0, 0) . . . . . . . . . . . . . . . . . . . . 19

Status Register (A3, A2, A1, A0 = 0, 0, 0, 0;

Power–On Reset = 00 Hex) . . . . . . . . . . . . . . . . . . . . . 20

Mode Register (A3, A2, A1, A0 = 0, 0, 0, 1;

Power-On-Reset = 00 Hex) . . . . . . . . . . . . . . . . . . . . . 21

Operating Characteristics when Addressing the Mode

and Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Main ADC Control Register (AD0CON):

(A3, A2, A1, A0 = 0, 0, 1, 0;

Power-On Reset = 07 Hex) . . . . . . . . . . . . . . . . . . . . . 22

Aux ADC Control Registers (AD1CON):

(A3, A2, A1, A0 = 0, 0, 1, 1;

Power-On Reset = 01 Hex) . . . . . . . . . . . . . . . . . . . . . 23

Filter Register (A3, A2, A1, A0 = 0, 1, 0, 0;

Power-On Reset = 45 Hex) . . . . . . . . . . . . . . . . . . . . . 24

I/O and Current Source Control Register (IOCON):

(A3, A2, A1, A0 = 0, 1, 1, 1;

Power-On Reset = 0000 Hex) . . . . . . . . . . . . . . . . . . . 24

Main ADC Data Result Registers (DATA0):

(A3, A2, A1, A0 = 0, 1, 0, 1;

Power-On Reset = 000000 Hex) . . . . . . . . . . . . . . . . . 26

Aux ADC Data Result Registers (DATA1):

(A3, A2, A1, A0 = 0, 1, 1, 0;

Power-On Reset = 0000 Hex) . . . . . . . . . . . . . . . . . . . 26

Main ADC Offset Calibration Coefficient Registers (OF0):

(A3, A2, A1, A0 = 1, 0, 0, 0;

Power-On Reset = 800000 Hex) . . . . . . . . . . . . . . . . . 26

Aux ADC Offset Calibration Coefficient Registers (OF1):

(A3, A2, A1, A0 = 1, 0, 0, 1;

Power-On Reset = 8000 Hex) . . . . . . . . . . . . . . . . . . . 26

Main ADC Gain Calibration Coefficient Registers (GNO):

(A3, A2, A1, A0 = 1, 0, 1, 0;

Power-On Reset = 5XXXX5 Hex) . . . . . . . . . . . . . . . . 25

Aux ADC Gain Calibration Coefficient Registers (GN1):

(A3, A2, A1, A0 = 1, 0, 1, 1;

Power-On Reset = 59XX Hex) . . . . . . . . . . . . . . . . . . . 26

ID Register (ID): (A3, A2, A1, A0 = 1, 1, 1, 1;

Power-On Reset = 0X Hex) . . . . . . . . . . . . . . . . . . . . . 26

User Nonprogrammable Test Registers . . . . . . . . . . . . . . 26

CONFIGURING THE AD7719 . . . . . . . . . . . . . . . . . . . . . 27

MICROCOMPUTER/MICROPROCESSOR

INTERFACING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

AD7719-to-68HC11 Interface . . . . . . . . . . . . . . . . . . . . . 28

AD7719-to-8051 Interface . . . . . . . . . . . . . . . . . . . . . . . . 28

AD7719-to-ADSP-2103/ADSP-2105 Interface . . . . . . . . 30

CIRCUIT DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . 30

Analog Input Channels . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Programmable Gain Amplifier . . . . . . . . . . . . . . . . . . . . . 32

Bipolar/Unipolar Configuration . . . . . . . . . . . . . . . . . . . . 33

Data Output Coding . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Burnout Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Excitation Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Reference Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Reference Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Reset Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Power-Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Idle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

ADC Disable Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Grounding and Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

APPLICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Pressure Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Temperature Measurement . . . . . . . . . . . . . . . . . . . . . . . 37

3-Wire RTD Configurations . . . . . . . . . . . . . . . . . . . . . . 38

Smart Transmitters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . 40

–2–

REV. 0

Page 3

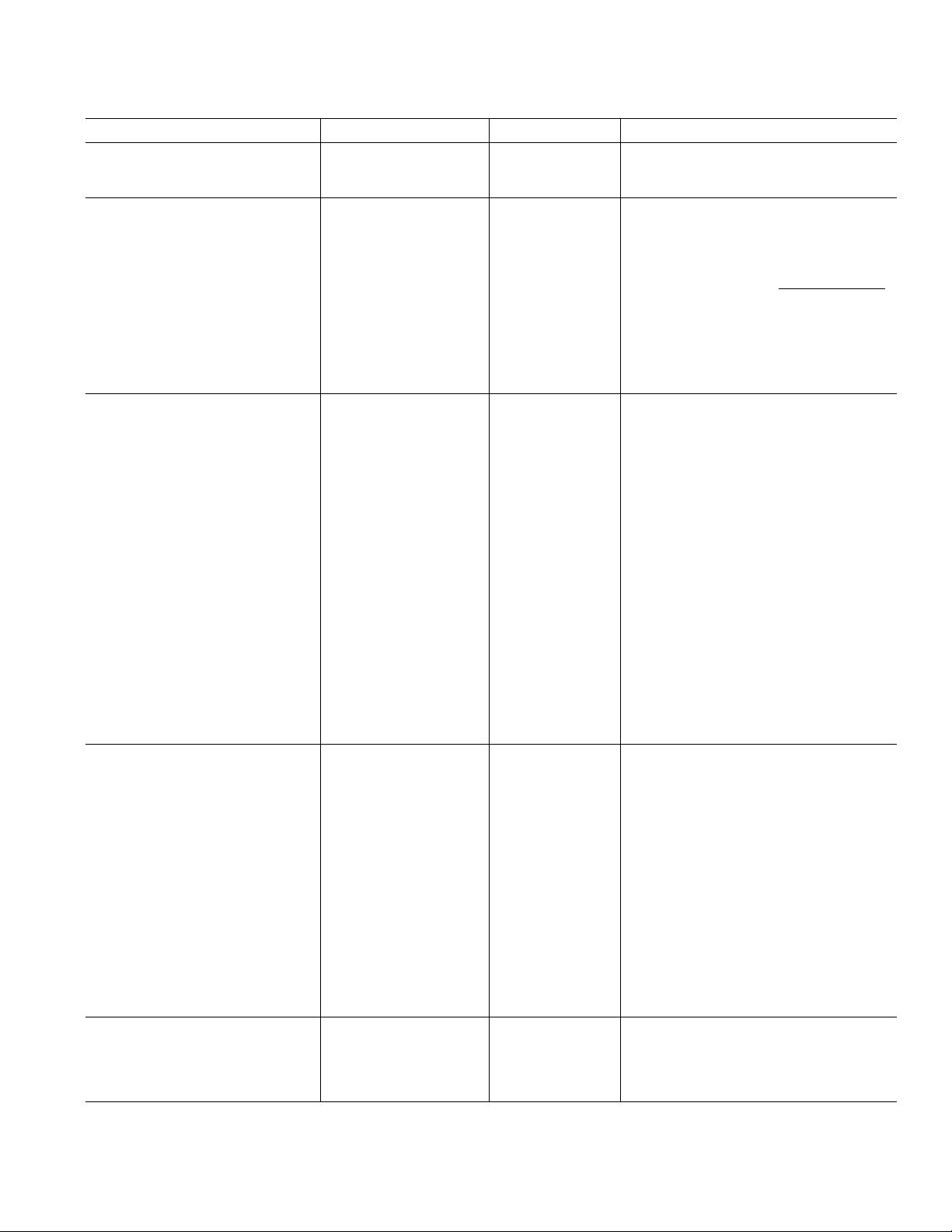

AD7719–SPECIFICATIONS

REFIN(+) = 2.5 V; REFIN(–) = AGND; AGND = DGND = 0 V; XTAL1/XTAL2 = 32.768 kHz Crystal; all specifications T

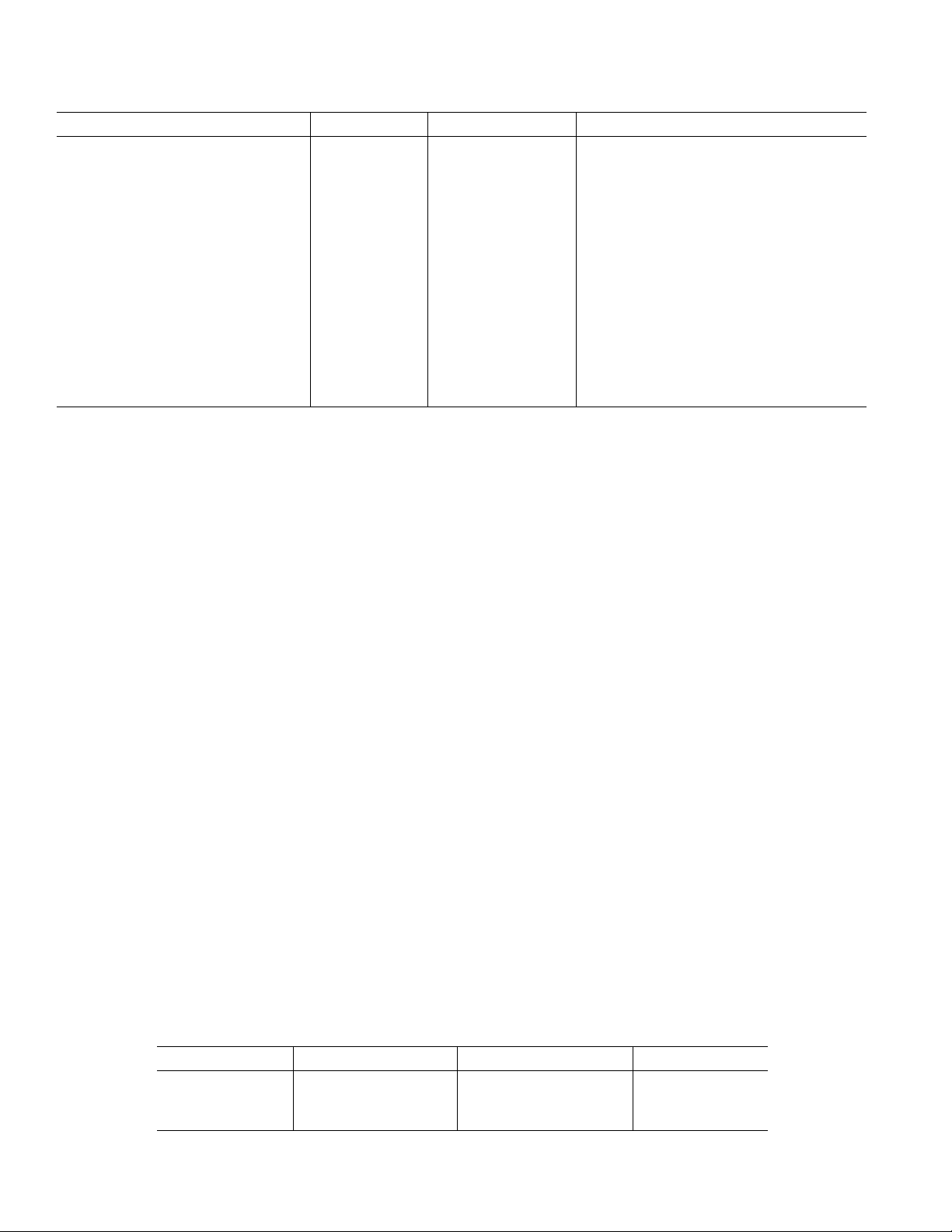

Parameter AD7719B Unit Test Conditions

ADC CHANNEL SPECIFICATION

Output Update Rate 5.4 Hz min Both Channels Synchronized

MAIN CHANNEL

No Missing Codes

2

Resolution 13 Bits p-p ±20 mV Range, 20 Hz Update Rate

Output Noise and Update Rates See Tables II to V

Integral Nonlinearity ±10 ppm of FSR max Typically 2 ppm.

Offset Error

Offset Error Drift vs. Temperature

Full-Scale Error

Gain Drift vs. Temperature

3

5, 8, 9

4

Power Supply Rejection (PSR) 80 dB min Input Range = ± 2.56 V, 100 dB typ.

ANALOG INPUTS

Differential Input Voltage Ranges ±1.024 × REFIN1/GAIN V nom REFIN1 = REFIN1(+) – REFIN1(–)

ADC Range Matching ±2 µV typ Input Voltage = 19 mV on All Ranges

Absolute AIN Voltage Limits AGND + 100 mV V min BUF = 0; Buffered Mode of Operation

Analog Input Current

2

DC Input Current ± 1 nA max

DC Input Current Drift ± 5 pA /°C typ

Absolute AIN Voltage Limits AGND – 30 mV V min BUF = 1; Unbuffered mode of operation.

Analog Input Current BUF = 1. Unbuffered Mode of Operation.

DC Input Current ± 125 nA/V typ Input Current Varies with Input Voltage

DC Input Current Drift ± 2 pA/V/°C typ

Normal-Mode Rejection

2, 6

@ 50 Hz 100 dB min

@ 60 Hz 100 dB min 60 Hz ± 1 Hz, 20 Hz Update Rate, SF = 68

Common-Mode Rejection

@ DC 90 dB min Input Range = ± 2.56 V, AIN = 1 V.

@ 50 Hz

@ 60 Hz

2

2

REFERENCE INPUT (REFIN1)

REFIN1 Voltage 2.5 V nom REFIN1 = REFIN1(+) – REFIN1(–)

REFIN1 Voltage Range

2

REFIN1 Common-Mode Range AGND – 30 mV V min

Reference DC Input Current 0.5 µA/V typ

Reference DC Input Current Drift ±0.01 nA/V/°C typ

Normal-Mode Rejection

2, 6

@ 50 Hz 100 dB min 50 Hz ± 1 Hz, SF = 82

@ 60 Hz 100 dB min 60 Hz ± 1 Hz, SF = 68

Common-Mode Rejection

@ DC 110 dB typ Input Range = ± 2.56 V, AIN = 1 V

@ 50 Hz 110 dB typ 50 Hz ± 1 Hz, Range = 2.56 V, AIN = 1 V

@ 60 Hz 110 dB typ 60 Hz ± 1 Hz, Range = 2.56 V, AIN = 1 V

Reference Detect Levels 0.3 V min NOXREF Bit Active if VREF < 0.3 V

AUXILIARY CHANNEL

No Missing Codes

2

Resolution 16 Bits p-p ±2.5 V Range, 20 Hz Update Rate

Output Noise and Update Rates See Tables VI and VIII

Integral Nonlinearity ±15 ppm of FSR max

105 Hz max 0.732 ms Increments

24 Bits min 20 Hz Update Rate

18 Bits p-p ±2.56 V Range, 20 Hz Update Rate

±3 µV typ

4

±10 nV/°C typ

±10 µV typ At the Calibrated Conditions

±0.5 ppm/°C typ

AV

DD

AV

DD

100 dB min 50 Hz ± 1 Hz, Range = ± 2.56 V, AIN = 1 V

100 dB min 60 Hz ± 1 Hz, Range = ± 2.56 V, AIN = 1 V

1 V min

AV

DD

AV

DD

0.65 V max NOXREF Bit Inactive if VREF > 0.65 V

16 Bits min

(AVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V, DVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V,

to T

MIN

110 dB typ on ±20 mV Range

GAIN = 1 to 128.

– 100 mV V max

BUF = 0

+ 30 mV V max

50 Hz ± 1 Hz, 16.65 Hz Update Rate, SF = 82

100 dB typ. 110 dB typ on ± 20 mV Range

V max

+ 30 mV V max

unless otherwise noted.)

MAX

FSR

=

×2 1 024 1.

REFIN

Gain

1

REV. 0

–3–

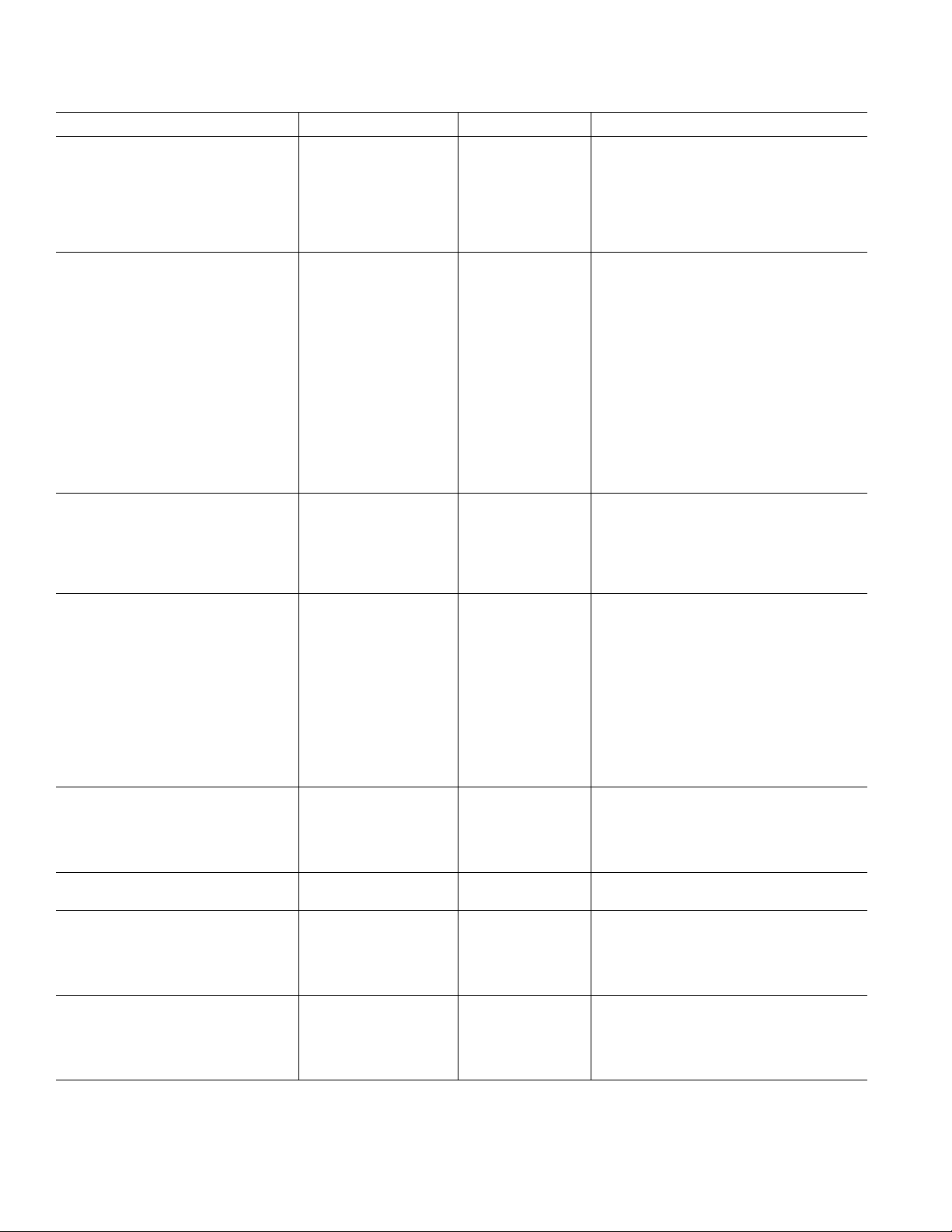

Page 4

AD7719

Parameter AD7719B Unit Test Conditions

AUXILIARY CHANNEL (continued)

Offset Error

Offset Error Drift vs. Temperature

Full-Scale Error

Gain Drift vs. Temperature

Negative Full-Scale Error ±1 LSB typ

Power Supply Rejection (PSR) 70 dB min AIN = 1 V Input Range = ±2.5 V, Typically 80 dB

ANALOG INPUTS

Differential Input Voltage Ranges ±REFIN2 V nom ARN = 1

Absolute AIN Voltage Limits AGND – 30 mV V min Unbuffered Input

Analog Input Current

DC Input Current ± 125 nA/V typ Input Current Varies with Input Voltage

DC Input Current Drift ± 2 pA/V/°C typ

Normal-Mode Rejection

@ 50 Hz 100 dB min 50 Hz ± 1 Hz, SF = 82

@ 60 Hz 100 dB min 60 Hz ± 1 Hz, SF = 68

Common-Mode Rejection

@ DC 85 dB min Input Range = ± 2.5 V, AIN = 1 V

@ 50 Hz

@ 60 Hz

REFERENCE INPUT (REFIN2) With Respect to AGND

REFIN2 Voltage 2.5 V nom

REFIN2 Range

Reference DC Input Current

Reference DC Input Current Drift 0.003 nA/V/°C typ

EXCITATION CURRENT SOURCES

(IEXC1 and IEXC2)

Output Current 200 µA nom

Initial Tolerance at 25°C ± 10 % typ

Drift 20 ppm/°C typ

Initial Current Matching at 25°C ±1 % typ Matching between IEXC1 and IEXC2

Drift Matching 1 ppm/°C typ

Line Regulation (AV

Load Regulation 300 nA/V typ

Output Compliance AVDD – 0.6 V max

LOW-SIDE POWER SWITCHES

(SW1 AND SW2)

R

Allowable Current

TEMPERATURE SENSOR

Accuracy See TPC 5 °C typ

TRANSDUCER BURNOUT

AIN(+) Current –100 nA typ

AIN(–) Current +100 nA typ

Initial Tolerance @ 25°C ±15 % typ

Drift 0.03 %/°C typ

SYSTEM CALIBRATION

Full-Scale Calibration Limit 1.05 × FS

Zero-Scale Calibration Limit –1.05 × FS V min

Input Span 0.8 × FS V min

ON

3

8, 9

4

±3 µV typ Selected Channel = AIN5/AIN6

4

±10 nV/°C typ

±0.75 LSB typ

0.5 ppm/°C typ

±REFIN2/2 V nom ARN = 0

+ 30 mV V max

AV

DD

2, 6

2

2

2

2

90 dB min 50 Hz ± 1 Hz, Range = 2.5 V, AIN = 1 V

90 dB min 60 Hz ± 1 Hz, Range = 2.5 V, AIN = 1 V

1 V min

AV

DD

V max

0.2 µA/V typ

No Load

) 2.1 µA/V max AVDD = 5 V ± 5%. Typically 1.25 µA/V

DD

AGND –30 mV V min

5 Ω max AVDD = 5 V. Typically 3 Ω

2

10, 2

7 Ω max AV

20 mA max Continuous Current per Switch

11

V max

= 3 V. Typically 4.5 Ω

DD

2.1 × FS V max

–4–

REV. 0

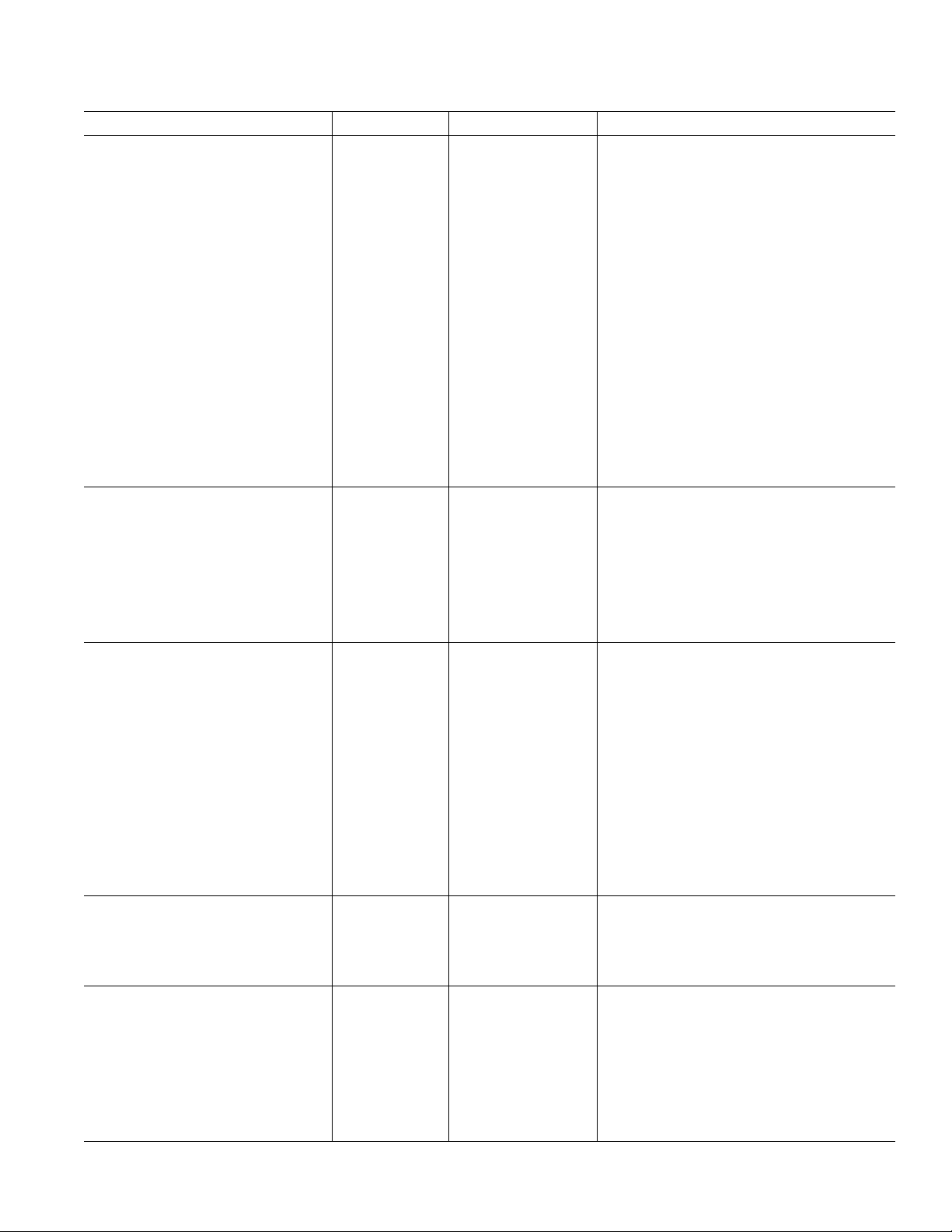

Page 5

AD7719–SPECIFICATIONS

1

Parameter AD7719B Unit Test Conditions

LOGIC INPUTS

All Inputs Except SCLK and XTAL1

V

, Input Low Voltage 0.8 V max DVDD = 5 V

INL

V

, Input High Voltage 2.0 V min DVDD = 3 V or 5 V

INH

SCLK Only (Schmitt-Triggered Input)

V

T(+)

V

T(–)

V

– V

T(+)

V

V

V

XTAL1 Only

V

V

V

V

T(–)

T(+)

T(–)

– V

T(+)

T(–)

2

, Input Low Voltage 0.8 V max DVDD = 5 V

INL

, Input High Voltage 3.5 V min DVDD = 5 V

INH

, Input Low Voltage 0.4 V max DVDD = 3 V

INL

, Input High Voltage 2.5 V min DVDD = 3 V

INH

Input Currents ±10 µA max VIN = DV

Input Capacitance

LOGIC OUTPUTS (Excluding XTAL2)

V

, Output High Voltage

OH

VOL, Output Low Voltage

V

, Output High Voltage

OH

VOL, Output Low Voltage

2

2

2

2

2

Floating-State Leakage Current ±10 µA max

Floating-State Output Capacitance ±10 pF typ

Data Output Coding Binary Unipolar Mode

I/O PORT

V

V

7

, Input Low Voltage

INL

, Input High Voltage

INH

2

2

Input Currents ±10 µA max V

Input Capacitance 10 pF typ All Digital Inputs

V

, Output High Voltage

OH

VOL, Output Low Voltage

V

, Output High Voltage

OH

VOL, Output Low Voltage

2

2

2

2

Floating-State Output Leakage Current ±10 µA max

Floating-State Output Capacitance ±10 pF typ

START-UP TIME

From Power-On 300 ms typ

From Idle Mode 1 ms typ

From Power-Down Mode 1 ms typ Osc. Active in Power-Down

POWER REQUIREMENTS

Power Supply Voltages

AV

– AGND 2.7/3.6 V min/max AVDD = 3 V nom

DD

DVDD – DGND 2.7/3.6 V min/max DVDD = 3 V nom

Power Supply Currents

DI

Current (Normal Mode)

DD

2

0.4 V max DVDD = 3 V

2

1.4/2 V min/V max DVDD = 5 V

0.8/1.4 V min/V max DVDD = 5 V

0.3/0.85 V min/V max DVDD = 5 V

0.95/2 V min/V max DVDD = 3 V

0.4/1.1 V min/V max DVDD = 3 V

0.3/0.85 V min/V max DVDD = 3 V

–70 µA max VIN = DGND, Typically –40 µA at 5 V

DD

and –20 µA at 3 V

10 pF typ All Digital Inputs

DVDD – 0.6 V min DVDD = 3 V, I

0.4 V max DVDD = 3 V, I

4 V min DVDD = 5 V, I

0.4 V max DVDD = 5 V, I

SOURCE

= 100 µA

SINK

SOURCE

= 1.6 mA

SINK

= 100 µA

= 200 µA

Offset Binary Bipolar Mode

I/O Port Voltages Are with Respect to

AV

and AGND

DD

0.8 V max AVDD = 5 V

0.4 V max AV

DD

= 3 V

2.0 V min AVDD = 3 V or 5 V

= AV

IN

DD

–70 µA max VIN = AGND, Typically –40 µA at AVDD = 5 V

and –20 µA at AV

AVDD – 0.6 V min AVDD = 3 V, I

0.4 V max AVDD = 3 V, I

4 V min AVDD = 5 V, I

0.4 V max AVDD = 5 V, I

DD

SOURCE

= 100 µA

SINK

SOURCE

= 1.6 mA

SINK

= 3 V

= 100 µA

= 200 µA

300 ms typ Osc. Powered Down

4.75/5.25 V min/max AV

4.75/5.25 V min DV

12

0.6 mA max DVDD = 3 V, 0.5 mA typ

= 5 V nom

DD

= 5 V nom

DD

0.75 mA max DVDD = 5 V, 0.6 mA typ

REV. 0

–5–

Page 6

AD7719

Parameter AD7719B Unit Test Conditions

Power Supply Currents (Continued)

AI

Current (Main ADC) 1.1 mA max AVDD = 3 V or 5 V, Buffered Mode,

DD

0.55 mA max AV

AI

Current (Aux ADC) 0.3 mA max AVDD = 3 V or 5 V, 0.25 mA typ

DD

AI

Current (Main and Aux ADC) 1.25 mA max AVDD = 3 V or 5 V, Main ADC Buffered,

DD

DI

(ADC Disable Mode)

DD

13

0.35 mA max DVDD = 3 V, 0.25 mA typ

0.4 mA max DV

AI

(ADC Disable Mode) 0.15 mA max AVDD = 3 V or 5 V

DD

DI

(Power-Down Mode) 10 µA max DVDD = 3 V, 32.768 kHz Osc. Running

DD

2 µA max DV

30 µA max DV

8 µA max DV

AIDD (Power-Down Mode) 1 µA max AVDD = 3 V or 5 V

NOTES

1

Temperature Range –40°C to +85°C.

2

Guaranteed by design and/or characterization data on production release.

3

System zero calibration will remove this error.

4

A calibration at any temperature will remove this drift error.

5

The Main ADC is factory-calibrated with AVDD = DVDD = 4 V, TA = 25°C, REFIN1(+) – REFIN1(–) = 2.5 V. If the user power supplies or temperature conditions

are significantly different from these, internal full-scale calibration will restore this error to the published specification. System calibration can be used to reduce this

error to the order of the noise. Full scale error applies to both positive and negative full scale.

6

Simultaneous 50 Hz and 60 Hz rejection is achieved using 19.8 Hz (SF = 69) update rate. Normal mode rejection in this case is 60 dB min.

7

Input and Output levels on the I/O Port are with respect to AVDD and AGND.

8

A system full-scale calibration will remove this error.

9

A typical gain error of ± 10µV results following a user self calibration.

10

After a calibration if the analog input exceeds positive full scale, the converter will output all 1s. If the analog input is less than negative full scale then the device will

output all 0s.

11

FS = Full-Scale Input. FS = 1.024 × REFIN1/Gain on the Main ADC, where REFIN1 = REFIN1(+) – REFIN1(–). FS = REFIN2 on the aux ADC when ARN = 1

in the aux ADC control register (AD1CON) and REFIN2/2 on the aux ADC when ARN = 0.

12

Normal Mode refers to the case where both main and aux ADCs are running.

13

ADC disable is entered by setting both the AD0EN and AD1EN bits in the Main and Aux ADC control registers to a 0 and setting the mode bits (MD2, MD1,

MD0) in the Mode register to non-0.

Specifications subject to change without notice.

0.85 mA typ

= 3 V or 5 V, Unbuffered Mode,

DD

0.45 mA typ

1 mA typ

= 5 V, 0.3 mA typ

DD

= 3 V, Oscillator Powered Down

DD

= 5 V, 32.768 kHz Osc. Running

DD

= 5 V, Oscillator Powered Down

DD

ABSOLUTE MAXIMUM RATINGS

(TA = 25°C unless otherwise noted)

1

AVDD to AGND . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

AV

to DGND . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

DD

DV

to AGND . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

DD

to DGND . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

DV

DD

AGND to DGND

2

. . . . . . . . . . . . . . . . . . . –20 mV to +20 mV

PWRGND to AGND . . . . . . . . . . . . . . . . –20 mV to +20 mV

to DVDD . . . . . . . . . . . . . . . . . . . . . . . . . . –5 V to +5 V

AV

DD

Analog Input Voltage to AGND . . . . –0.3 V to AV

Reference Input Voltage to AGND . . –0.3 V to AV

+0.3 V

DD

+0.3 V

DD

Total AIN/REFIN Current (Indefinite) . . . . . . . . . . . . 30 mA

Digital Input Voltage to DGND . . . . –0.3 V to DV

Digital Output Voltage to DGND . . . –0.3 V to DV

+0.3 V

DD

+0.3 V

DD

Operating Temperature Range . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD7719BR –40°C to +85°C SOIC R-28

AD7719BRU –40°C to +85°C TSSOP RU-28

EVAL-AD7719EB Evaluation Board

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . 150°C

SOIC Package

Thermal Impedance . . . . . . . . . . . . . . . . . . . . 71.4°C/W

θ

JA

θ

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . 23°C/W

JC

TSSOP Package

Thermal Impedance . . . . . . . . . . . . . . . . . . . . 97.9°C/W

θ

JA

θ

Thermal Impedance . . . . . . . . . . . . . . . . . . . . . . 14°C/W

JC

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . . 215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

AGND and DGND and connected internally within the AD7719.

–6–

REV. 0

Page 7

TIMING CHARACTERISTICS

WARNING!

ESD SENSITIVE DEVICE

5.25 V; AGND = DGND = 0 V; X

= 32.768 kHz; Input Logic 0 = 0 V, Logic 1 = DVDD unless otherwise noted.)

TAL

1, 2

(AVDD = 2.7 V to 3.6 V or AVDD = 4.75 V to 5.25 V; DVDD = 2.7 V to 3.6 V or DVDD = 4.75 V to

AD7719

Limit at T

MIN

, T

MAX

Parameter (B Version) Unit Conditions/Comments

t

1

t

2

32.768 kHz typ Crystal Oscillator Frequency.

50 ns min RESET Pulsewidth

Read Operation

t

3

t

4

4

t

5

0 ns min RDY to CS Setup Time

0 ns min CS Falling Edge to SCLK Active Edge Setup Time

0 ns min SCLK Active Edge to Data Valid Delay

3

3

60 ns max DVDD = 4.75 V to 5.25 V

4, 5

t

5A

80 ns max DV

0 ns min CS Falling Edge to Data Valid Delay

= 2.7 V to 3.6 V

DD

3

60 ns max DVDD = 4.75 V to 5.25 V

80 ns max DV

t

6

t

7

t

8

6

t

9

100 ns min SCLK High Pulsewidth

100 ns min SCLK Low Pulsewidth

0 ns min CS Rising Edge to SCLK Inactive Edge Hold Time

10 ns min Bus Relinquish Time after SCLK Inactive Edge

80 ns max

t

10

100 ns max SCLK Active Edge to RDY High

Write Operation

t

11

t

12

t

13

t

14

t

15

t

16

NOTES

1

Sample tested during initial release to ensure compliance. All input signals are specified with tR = tF = 5 ns (10% to 90% of DVDD) and timed from a voltage level of 1.6 V.

2

See Figures 2 and 3.

3

SCLK active edge is falling edge of SCLK.

4

These numbers are measured with the load circuit of Figure 1 and defined as the time required for the output to cross the V

5

This specification only comes into play if CS goes low while SCLK is low. It is required primarily for interfacing to DSP machines.

6

These numbers are derived from the measured time taken by the data output to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the

part and as such are independent of external bus loading capacitances.

7

RDY returns high after a read of both ADCs. The same data can be read again, if required, while RDY is high, although care should be taken that subsequent reads do not occur

close to the next output update.

0 ns min CS Falling Edge to SCLK Active Edge Setup Time

30 ns min Data Valid to SCLK Edge Setup Time

25 ns min Data Valid to SCLK Edge Hold Time

100 ns min SCLK High Pulsewidth

100 ns min SCLK Low Pulsewidth

0 ns min CS Rising Edge to SCLK Edge Hold Time

= 2.7 V to 3.6 V

DD

or VOH limits.

OL

3

3

3, 7

3

I

(1.6mA WITH DVDD = 5V

TO OUTPUT

PIN

50pF

SINK

100A WITH DV

I

(200A WITH DVDD = 5V

SOURCE

100A WITH DV

1.6V

DD

= 3V)

DD

= 3V)

Figure 1. Load Circuit for Timing Characterization

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD7719 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

REV. 0

–7–

Page 8

AD7719

DIGITAL INTERFACE

As previously outlined, the AD7719’s programmable functions

are controlled using a set of on-chip registers. Data is written to

these registers via the part’s serial interface and read access to

the on-chip registers is also provided by this interface. All communications to the part must start with a write operation to the

Communications Register. After power-on or

RESET

, the device

expects a write to its Communications Register. The data written to this register determines whether the next operation to the

part is a read or a write operation and also determines to which

register this read or write operation occurs. Therefore, write

access to any of the other registers on the part starts with a write

operation to the Communications Register followed by a write

to the selected register. A read operation from any other register

on the part (including the output data register) starts with a

write operation to the Communications Register followed by a

read operation from the selected register.

The AD7719’s serial interface consists of five signals, CS, SCLK,

DIN, DOUT, and RDY. The DIN line is used for transferring

data into the on-chip registers while the DOUT line is used for

accessing data from the on-chip registers. SCLK is the serial

clock input for the device and all data transfers (either on DIN

or DOUT) take place with respect to this SCLK signal. The

RDY line is used as a status signal to indicate when data is ready

to be read from the AD7719’s data register. RDY goes low when a

new data word is available in the output register of either the

main or Aux ADCs. It is reset high when a read operation from

the data register is complete. It also goes high prior to the updating

of the output register to indicate when not to read from the device

to ensure that a data read is not attempted while the register is

being updated. CS is used to select the device. It can be used to

decode the AD7719 in systems where a number of parts are

connected to the serial bus.

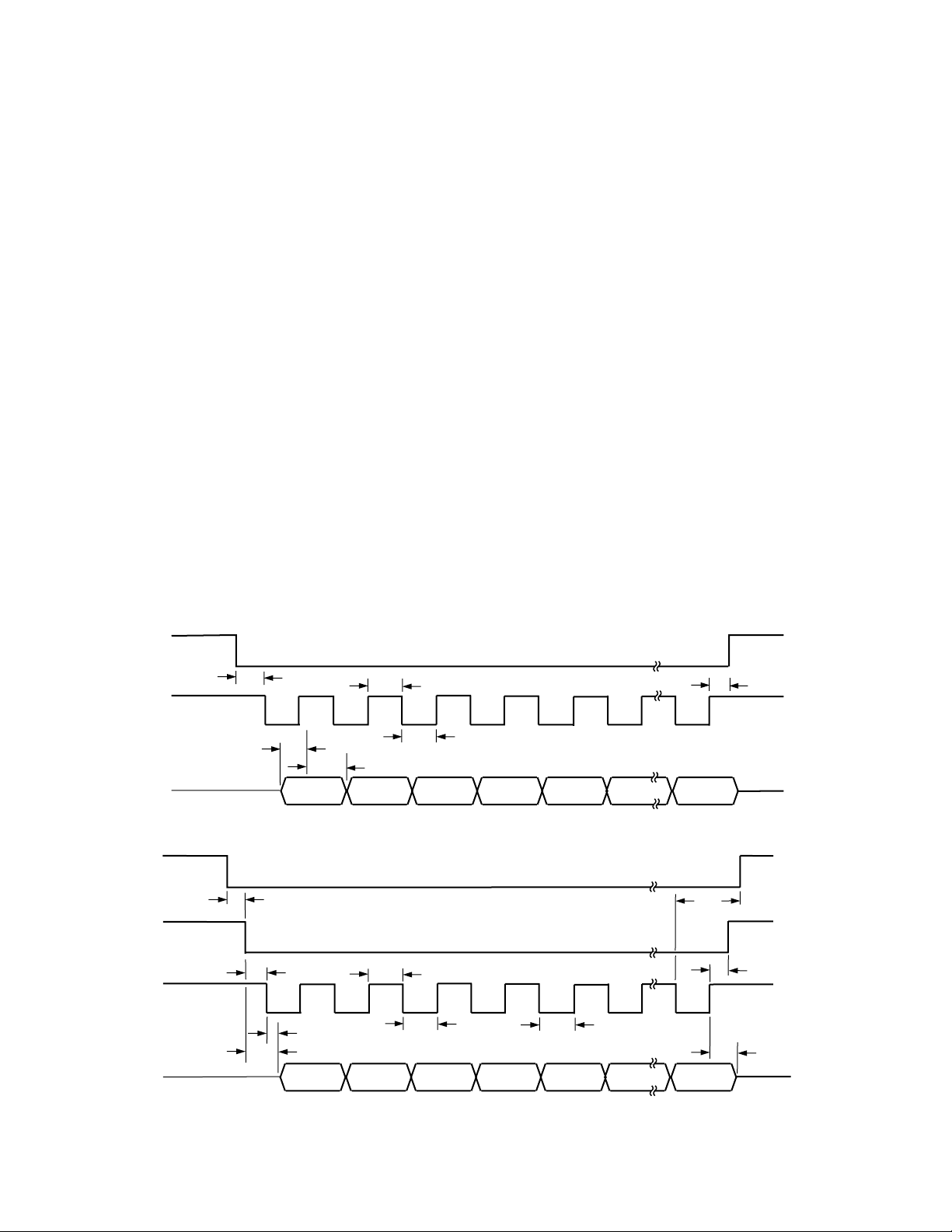

Figures 2 and 3 show timing diagrams for interfacing to the

AD7719 with CS used to decode the part. Figure 3 is for a read

operation from the AD7719’s output shift register while Figure 2

shows a write operation to the input shift register. It is possible

to read the same data twice from the output register even though

the RDY line returns high after the first read operation. Care must

be taken, however, to ensure that the read operations have been

completed before the next output update is about to take place.

The AD7719 serial interface can operate in 3-wire mode by

tying the CS input low. In this case, the SCLK, DIN, and

DOUT lines are used to communicate with the AD7719 and

the status of RDY bits (RDY0 and RDY1) can be obtained by

interrogating the STATUS Register. This scheme is suitable

for interfacing to microcontrollers. If CS is required as a decoding signal, it can be generated from a port bit. For microcontroller

interfaces, it is recommended that the SCLK idles high between

data transfers.

The AD7719 can also be operated with CS used as a frame

synchronization signal. This scheme is suitable for DSP interfaces. In this case, the first bit (MSB) is effectively clocked out

by CS since CS would normally occur after the falling edge of

SCLK in DSPs. The SCLK can continue to run between data

transfers provided the timing numbers are obeyed.

SCLK

RDY

SCLK

DOUT

CS

CS

DIN

t

11

t

12

t

13

MSB

t

14

t

15

LSB

t

16

Figure 2. Write Cycle Timing Diagram

t

3

t

4

t

5

t

5A

MSB

t

6

t

7

t

6

t

LSB

10

t

8

t

9

Figure 3. Read Cycle Timing Diagram

–8–

REV. 0

Page 9

AD7719

The serial interface can be reset by exercising the RESET input

on the part. It can also be reset by writing a series of 1s on the

DIN input. If a Logic 1 is written to the AD7719 DIN line for

at least 32 serial clock cycles the serial interface is reset. This

ensures that in 3-wire systems, if the interface gets lost either via

a software error or by some glitch in the system, it can be reset

back to a known state. This state returns the interface to where

the AD7719 is expecting a write operation to its Communications Register. This operation resets the contents of all registers to

their power-on reset values.

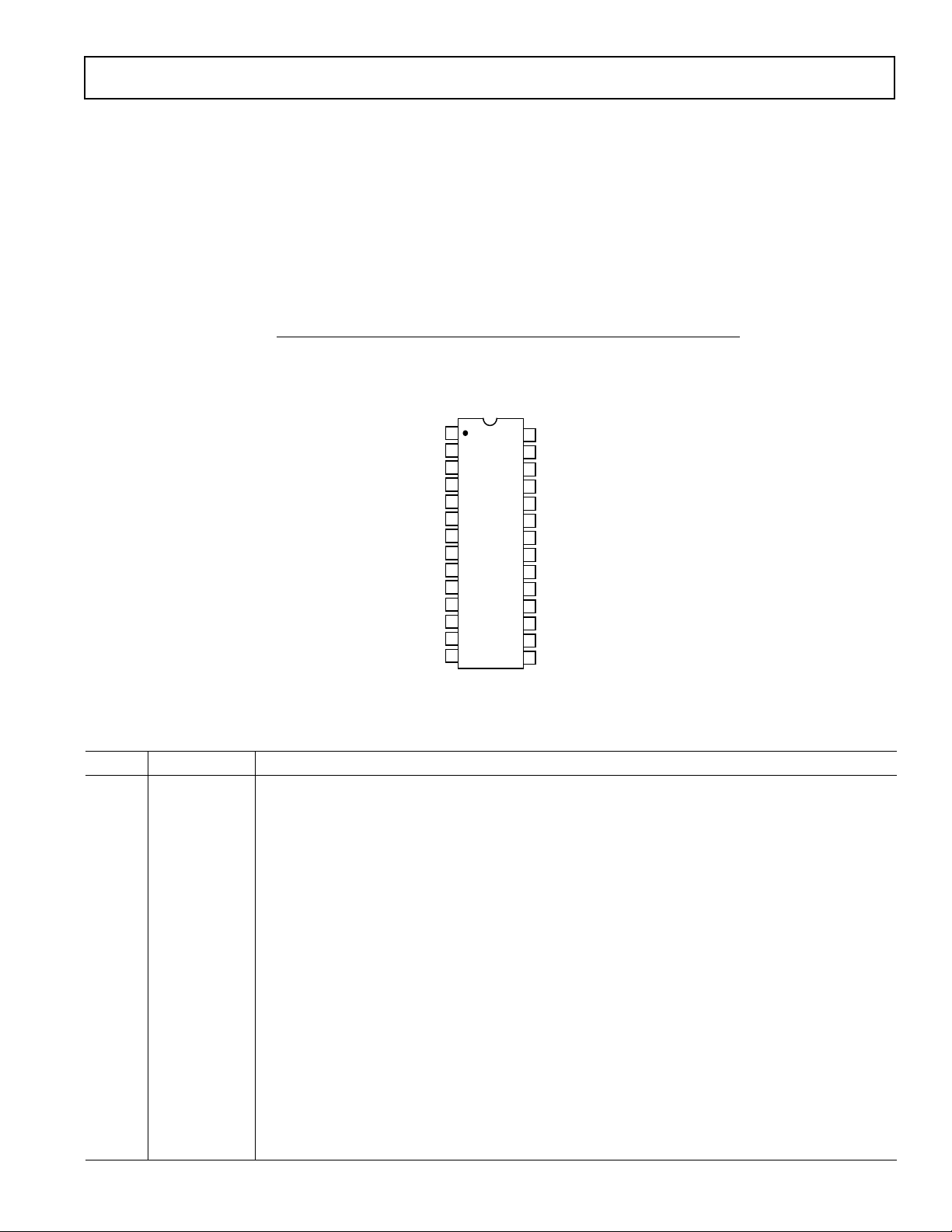

PIN CONFIGURATION

1

IOUT1

2

IOUT2

3

AV

DD

4

AGND

AIN1

AIN2

AIN3

AIN4

AIN5

AIN6

REFIN2

10

12

13

14

P4

5

AD7719

6

TOP VIEW

(Not to Scale)

7

8

9

11

REFIN1(–)

REFIN1(+)

Some microprocessor or microcontroller serial interfaces have a

single serial data line. In this case, it is possible to connect the

AD7719’s DATA OUT and DATA IN lines together and connect

them to the single data line of the processor. A 10 kΩ pull-up

resistor should be used on this single data line. In this case, if

the interface gets lost, because the read and write operations

share the same line the procedure to reset it back to a known

state is somewhat different than previously described. It requires

a read operation of 24 serial clocks followed by a write operation

where a Logic 1 is written for at least 32 serial clock cycles to

ensure that the serial interface is back into a known state.

XTAL1

28

XTAL2

27

DV

26

DD

DGND

25

DIN

24

DOUT

23

22

RDY

21

CS

SCLK

20

19

RESET

P1/SW1

18

PWRGND

17

16

P2/SW2

P3

15

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Function

1 IOUT1 Output for Internal 200 µA Excitation Current Source. Either current source IEXC1 or IEXC2 or

both can be switched to this output.

2 IOUT2 Output for Internal 200 µA Excitation Current Source. Either IEXC1 or IEXC2 current source or

both can be switched to this output.

3AV

DD

Analog Supply Voltage.

4 AGND Analog Ground.

5 REFIN1(–) Negative Reference Input for Main ADC Channel. This reference input can lie anywhere between

AGND and AV

6 REFIN1(+) Positive Reference Input for Main ADC Channel. REFIN1(+) can lie anywhere between AV

DD

– 1 V.

DD

and

AGND + 1 V. The nominal reference voltage (REFIN1(+) – REFIN1(–)) is 2.5 V, but the part is

functional with a reference range from 1 V to AV

DD

.

7 AIN1 Analog Input. AIN1 is dedicated to the main channel.

8 AIN2 Analog Input. AIN2 is dedicated to the main channel.

9 AIN3 Analog Input. AIN3 can be multiplexed to either the main or auxiliary channel

10 AIN4 Analog Input. AIN4 can be multiplexed to either the main or auxiliary channel.

11 AIN5 Analog Input. AIN5 is dedicated to the auxiliary channel and is referenced to AIN6 or AGND

12 AIN6 Analog Input. AIN6 is dedicated to the auxiliary channel. It forms a differential input pair with AIN5

in fully differential input mode or is referenced to AGND in pseudo-differential mode.

13 REFIN2 Single-Ended Reference Input for Auxiliary Channel. The nominal input reference is 2.5 V. The

auxiliary channel will function with an input reference range from 1 V to AV

14 P4 General-Purpose I/O Bit. The input and output voltage levels are referenced to AV

DD

.

DD

and AGND.

15 P3 General-Purpose I/O Bit. The input and output voltage levels are referenced to AVDD and AGND.

REV. 0

–9–

Page 10

AD7719

PIN FUNCTION DESCRIPTIONS (continued)

Pin No. Mnemonic Function

16 P2/SW2 Dual-Purpose Pin. It can act as a general purpose output (P2) bit referenced between AV

AGND or as a low-side power switch (SW2) to PWRGND.

17 PWRGND Ground Point for the Low-Side Power Switches SW2 and SW1. PWRGND must be tied to AGND.

18 P1/SW1 Dual-Purpose Pin. It can act as a general-purpose output (P1) bit referenced between AV

AGND or as a low-side power switch (SW1) to PWRGND.

19 RESET Digital Input Used to Reset the ADC to Its Power-On-Reset Status. This pin has a weak pull-up

internally to DV

DD

.

20 SCLK Serial Clock Input for Data Transfers to and from the ADC. The SCLK has a Schmitt triggered

input making the interface suitable for opto-isolated applications. The serial clock can be continuous

with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous

clock with the information being transmitted to or from the AD7719 in smaller batches of data. A

weak pull-up to DV

is provided on the SCLK input.

DD

21 CS Chip Select Input. This is an active low logic input used to select the AD7719. CS can be used to

select the AD7719 in systems with more than one device on the serial bus or as a frame synchroniza-

tion signal in communicating with the device. CS can be hardwired low allowing the AD7719 to be

operated in 3-wire mode with SCLK, DIN and DOUT used to interface with the device. A weak

pull-up to DV

is provided on the CS input.

DD

22 RDY RDY is a Logic Low Status Output from the AD7719. RDY is low if either the Main ADC or auxil-

iary ADC channel has valid data in their data register. This output returns high on completion of a

read operation from the data register. If data is not read, RDY will return high prior to the next up-

date indicating to the user that a read operation should not be initiated. The RDY pin also returns

low following the completion of a calibration cycle. The RDY pin is effectively the digital NOR func-

tion of the RDY0 and RDY1 bits in the Status register. If one of the ADCs is disabled the RDY pin

reflects the active ADC. RDY does not return high after a calibration until the mode bits are written

to enabling a new conversion or calibration. Since the RDY pin provides information on both the

main and aux ADCs, therefore, when either the main or aux ADC is disabled it is recommended to

immediately read its data register to ensure that its RDY bit goes inactive and releases the RDY pin

to indicate output data updates on the remaining active ADC.

23 DOUT Serial Data Output Accessing the Output Shift Register of the AD7719. The output shift register can

contain data from any of the on-chip data, calibration or control registers.

24 DIN Serial Data Input Accessing the Input Shift Register on the AD7719. Data in this shift register is

transferred to the calibration or control registers within the ADC depending on the selection bits of

the Communications register. A weak pull-up to DV

is provided on the DIN input.

DD

25 DGND Ground Reference Point for the Digital Circuitry.

26 DV

DD

Digital Supply Voltage, 3 V or 5 V Nominal.

27 XTAL2 Output from the 32 kHz Crystal Oscillator Inverter.

28 XTAL1 Input to the 32 kHz Crystal Oscillator Inverter.

DD

DD

and

and

–10–

REV. 0

Page 11

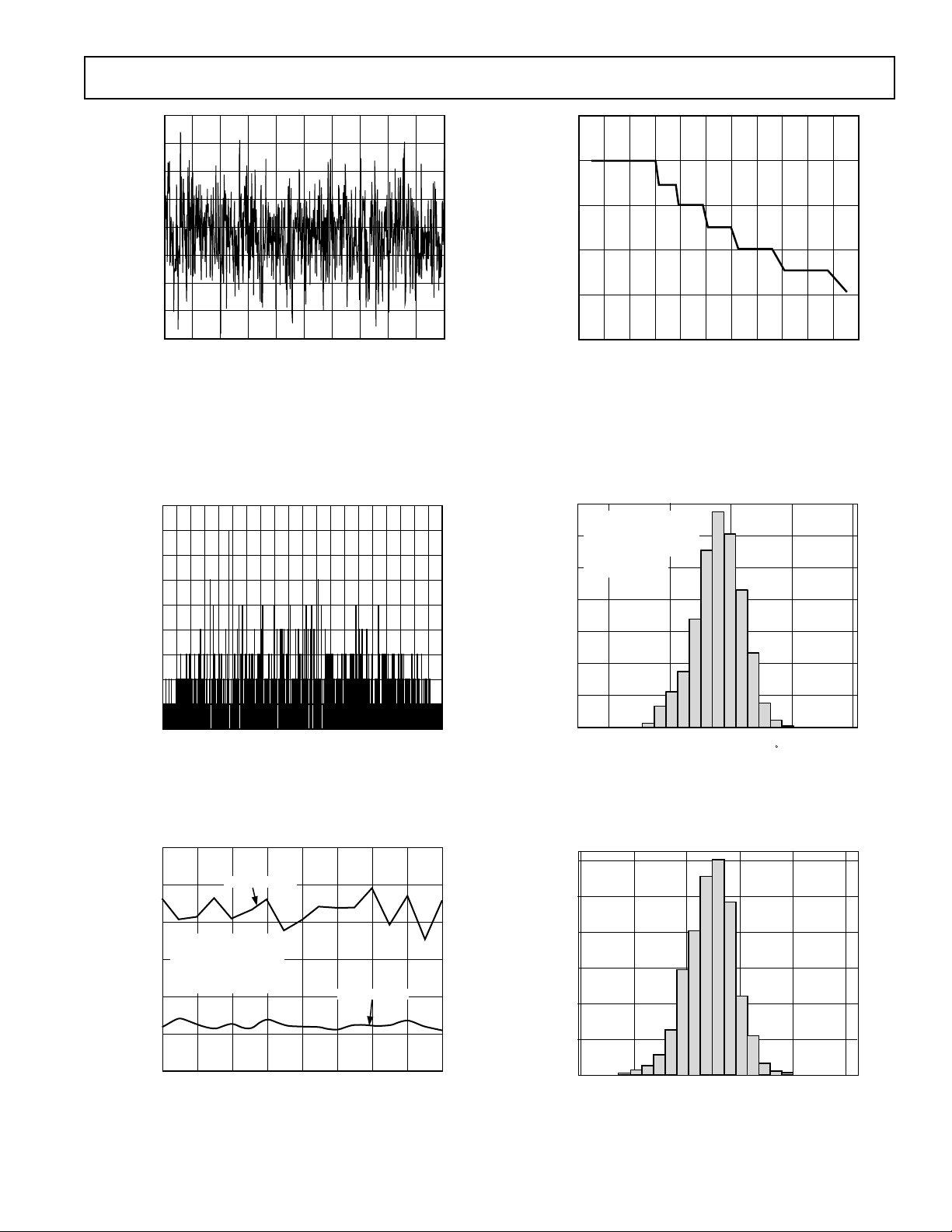

Typical Performance Characteristics–

AD7719

8389600

8389400

8389200

8389000

8388800

8388600

CODE READ

8388400

8388200

8388000

0 1000100

200 300

= DVDD = 5V

AV

DD

INPUT RANGE = 20mV

REFIN1(+)–REFIN1(–)=2.5V

UPDATE RATE=19.79Hz

400 500 600 700 800 900

READING NO.

MAIN ADC IN BUFFERED MODE

RMS NOISE = 0.58Vrms

= 25C

T

A

V

= 2.5V

REF

TPC 1. Typical Noise Plot on ±20 mV Input Range with

19.79 Hz Update Rate

9

8

7

6

5

4

3

2

1

0

8388841

8388382

8388039

8388499

8388449

8388579

8388547

8388615

8388657

8388687

8388721

8388754

8388805

8388779

8388906

8388874

8388985

8388941

8389033

8389110

26

24

22

20

NO MISSING CODES – Min

18

16

040302010 50 10090807060

UPDATE RATE – Hz

TPC 4. No-Missing-Codes Performance

1400

THE AMBIENT

TEMPERATURE VARIES

1200

FROM 25C TO 30C

WHILE RECORDING

THE DATA FROM

1000

THE DEVICES.

800

HITS

600

400

200

0

TEMPERATURE SENSOR – C

110

503010 20 40

REV. 0

TPC 2. Noise Distribution Histogram

3.0

= 2.5V

= 25C

2.56V RANGE

V

REF

20mV RANGE

– Volts

2.5

2.0

AVDD = DVDD = 5V

V

REF

1.5

INPUT RANGE = 2.56V

UPDATE RATE = 19.79Hz

T

A

RMS NOISE –V

1.0

0.5

0

1.0 3.02.52.01.5 3.5 5.04.54.0

TPC 3. RMS Noise vs. Reference Input

–11–

TPC 5. Temperature Sensor Accuracy

1200

1000

800

600

HITS

400

200

0

–30

MAIN CAL ACC. @ 4V – V

TPC 6. Full-Scale Error Distribution

200–20 –10 10

Page 12

AD7719

AVDD = DVDD = 5V

= 25C

T

A

V

DD

OSCILLATOR

TIME BASE = 100ms/DIV

TRACE 1 = TRACE 2 = 2V/DIV

TPC 7. Typical Oscillator Power-Up

DUAL-CHANNEL ADC CIRCUIT INFORMATION

Overview

The AD7719 incorporates two independent Σ-∆ ADC channels

(main and auxiliary) with on-chip digital filtering intended for

the measurement of wide dynamic range, low frequency signals

such as those in weigh-scale, strain-gauge, pressure transducer,

or temperature measurement applications.

Main Channel

This channel is intended to convert the primary sensor input.

This channel can be operated in buffered or unbuffered mode

and can be programmed to have one of eight input voltage ranges

from ±20 mV to ± 2.56 V. This channel can be configured as

either two fully differential inputs (AIN1/AIN2 and AIN3/AIN4)

or three pseudo-differential input channels (AIN1/AIN4, AIN2/

AIN4, and AIN3/AIN4). Buffering the input channel means that

the part can accommodate significant source impedances on the

analog input and that R, C filtering (for noise rejection or RFI

reduction) can be placed on the analog inputs if required. Operating in unbuffered mode leads to lower power consumption in

low power applications, but care must be exercised in unbuffered

mode as source impedances can introduce gain errors. The main

ADC also features sensor burnout currents that can be switched

on and off. These currents can be used to check that a transducer

is still operational before attempting to take measurements.

The ADC employs a sigma-delta conversion technique to realize

up to 24 bits of no-missing-codes performance. The sigma-delta

modulator converts the sampled input signal into a digital pulse

train whose duty cycle contains the digital information. A Sinc

3

programmable low-pass filter is then employed to decimate the

modulator output data stream to give a valid data conversion

result at programmable output rates from 5.35 Hz (186.77 ms)

to 105.0 3 Hz (9.52 ms). A chopping scheme is also employed

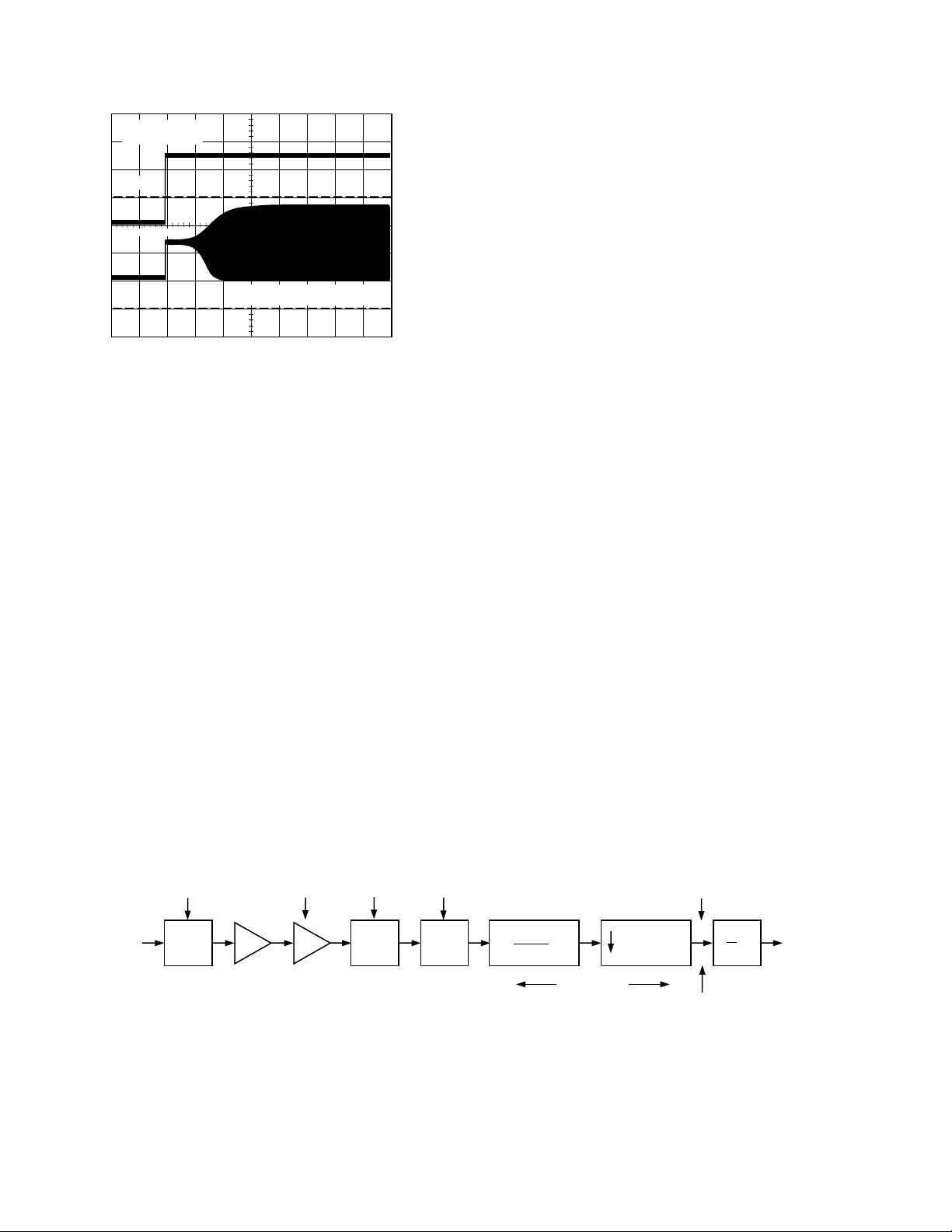

to minimize ADC channel offset errors. A block diagram of the

Main ADC input channel is shown in Figure 4. The sampling

frequency of the modulator loop is many times higher than the

bandwidth of the input signal. The integrator in the modulator

shapes the quantization noise (which results from the analog-todigital conversion) so that the noise is pushed toward one-half of

the modulator frequency. The output of the sigma-delta modulator feeds directly into the digital filter. The digital filter then

band-limits the response to a frequency significantly lower than

one-half of the modulator frequency. In this manner, the 1-bit

output of the comparator is translated into a bandlimited, low

noise output from the AD7719 ADC. The AD7719 filter is a

low-pass, Sinc

3

or (SIN(x)/x)3 filter whose primary function is to

remove the quantization noise introduced at the modulator. The

cutoff frequency and decimated output data rate of the filter are

programmable via the SF word loaded to the filter register.

A chopping scheme is employed where the complete signal chain is

chopped, resulting in excellent dc offset and offset drift specifications, and is extremely beneficial in applications where drift, noise

rejection, and optimum EMI rejection are important factors.

With chopping the ADC repeatedly reverses its inputs. The

decimated digital output words from the Sinc

3

filters therefore

have a positive offset and negative offset term included. As a result,

a final summing stage is included so that each output word from

the filter is summed and averaged with the previous filter output

to produce a new valid output result to be written to the ADC

data register.

Auxiliary Channel

The Auxiliary (Aux) channel is intended to convert supplementary inputs such as from a cold junction diode or thermistor.

This channel is unbuffered and has an input range of ±REFIN2

or ±REFIN2/2 determined by the ARN bit in the auxiliary ADC

control register (AD1CON). AIN3 and AIN4 can be multiplexed

into the auxiliary channel as single ended inputs with respect to

AGND while AIN5 and AIN6 can operate as a differential input

pair or with AIN6 tied to AGND, AIN5 can be operated as an

additional single-ended input. A block diagram of the Auxiliary

ADC channel is shown in Figure 5.

ANALOG

INPUT

f

CHOP

MUX

BUF

f

IN

PGA

f

MOD

S-D

MOD0

f

CHOP

XOR

(

8 SF

1

3

)

SINC3 FILTER

Figure 4. Main ADC Channel Block Diagram

–12–

3

(8 SF )

f

ADC

AIN + V

A

– V

IN

1

2

OS

OS

DIGITAL

OUTPUT

REV. 0

Page 13

AD7719

ANALOG

INPUT

f

CHOP

MUX

f

MOD

S-D

MOD1

f

CHOP

XOR

Figure 5. Auxiliary ADC Channel Block Diagram

Both Channels

The operation of the AUX channel is identical to the Main

channel with the exception that there is no PGA on the AUX

channel. The input chopping is incorporated into the input

multiplexer while the output chopping is accomplished by an

XOR gate at the output of the modulator. The chopped modulator bit stream is applied to a Sinc

the Sinc

3

decimation factor is restricted to an 8-bit register SF,

the actual decimation factor is the register value times 8. The

decimated output rate from the Sinc

3

filter. The programming of

3

filter (and the ADC con-

version rate) will therefore be:

f

1

=×

ADC MOD

318

×

f

SF

×

where

is the ADC update rate.

f

ADC

SF is the decimal equivalent of the word loaded to the

filter register.

f

is the modulator sampling rate of 32.768 kHz.

MOD

Programming the filter register determines the update rate for

both the main and aux ADC. Both ADCs operate with the same

update rate.

The chop rate of the channel is half the output data rate.

The frequency response of the filter H (f) is as follows:

3

SF

sin ( / )

1

×

8

×

81

SF f f

×××

sin ( / )

π

×

π

ff

MOD

MOD

××

sin ( / )

π

××

2

sin ( / )

π

2

×

ff

ff

OUT

OUT

where

f

= 32,768 Hz

MOD

SF = value programmed into SF SFR.

f

= f

OUT

/(SF × 8 × 3)

MOD

The following shows plots of the filter frequency response for

the SF words shown in Table I. The overall frequency response

is the product of a Sinc

notches at integer multiples of 3 × f

3

and a sinc response. There are Sinc

and there are sinc notches

ADC

3

f

ADC

(

8 SF

1

)

SINC3 FILTER

3

3

at odd integer multiples of f

(8 SF )

AIN + V

A

/2. The 3 dB frequency for all

ADC

1

2

OS

– V

OS

IN

DIGITAL

OUTPUT

values of SF obeys the following equation:

f (3 dB) = 0.24 × f

ADC

The signal chain is chopped as shown in Figures 4 and 5. The

chop frequency is:

f

CHOP

=

f

ADC

2

As shown in the block diagram, the Sinc3 filter outputs alternately

contain +V

and –VOS, where VOS is the respective channel

OS

offset. This offset is removed by performing a running average

of 2. This average by 2 means that the settling time to any change

in programming of the ADC will be twice the normal conversion

time, while an asynchronous step change on the analog input will

not be fully reflected until the third subsequent output.

t

SETTLE

2

=

f

ADC

=×

t

2

ADC

The allowable range for SF is 13 to 255, with a default of 69

(45H). The corresponding conversion rates, conversion times

and settling times are tabulated in Table I. Note that the conversion time increases by 0.732 ms for each increment in SF.

Table I. ADC Conversion and Settling Times for Various

SF Words

SF Data Update Rate Settling Time

Word f

(Hz) t

ADC

SETTLE

(ms)

13 105.3 19.04

69 (Default) 19.79 101.07

255 5.35 373.54

Normal-mode rejection is the major function of the digital filter

on the AD7719. The normal mode 50 ± 1 Hz rejection with an SF

word of 82 is typically –100 dB. The 60 ± 1 Hz rejection with

SF = 68 is typically –100 dB. Simultaneous 50 Hz and 60 Hz

rejection of better than 60 dB is achieved with an SF of 69.

Choosing an SF word of 69 places notches at both 50 Hz and

60 Hz. Figures 6 to 9 show the filter rejection for a selection

of SF words.

REV. 0

–13–

Page 14

AD7719

0

–20

–40

–60

–80

–100

–120

–140

ATTENUATION – dB

–160

–180

–200

100

50

0

SF = 13

OUTPUT DATA RATE = 105Hz

INPUT BANDWIDTH = 25.2Hz

FIRST NOTCH = 52.5Hz

50Hz REJECTION = –23.6dB, 50Hz1Hz REJECTION = –20.5dB

60Hz REJECTION = –14.6dB, 60Hz1Hz REJECTION = –13.6dB

150 200 250 300 350 400

FREQUENCY – Hz

450 500 550 600

Figure 6. Filter Profile with SF = 13

650

700

Figure 8. Filter Profile with Default SF = 69 Giving Filter

0

–20

–40

–60

–80

–100

ATTENUATION – dB

–120

–140

–160

10

0 100

SF = 69

OUTPUT DATA RATE = 19.8Hz

INPUT BANDWIDTH = 4.74Hz

FIRST NOTCH = 9.9Hz

50Hz REJECTION = –66dB, 50Hz1Hz REJECTION = –60dB

60Hz REJECTION = –117dB, 60Hz1Hz REJECTION = –94dB

20 30 40 50 60 70 80 90

FREQUENCY – Hz

Notches at Both 50 Hz and 60 Hz

0

–20

–40

0

–20

–40

–60

–80

–100

ATTENUATION – dB

–120

–140

–160

0 10010

SF = 82

OUTPUT DATA RATE = 16.65Hz

INPUT BANDWIDTH = 4Hz

50Hz REJECTION = –171dB, 50Hz1Hz REJECTION = –100dB

60Hz REJECTION = –58dB, 60Hz1Hz REJECTION = –53dB

20 30 40 50 60 70 80 90

FREQUENCY – Hz

Figure 7. Filter Profile with SF = 82

MAIN AND AUXILIARY ADC NOISE PERFORMANCE

Tables II to VII show the output rms noise and output peak-topeak resolution in bits (rounded to the nearest 0.5 LSB) for a

selection of output update rates on both the main and auxiliary

ADCs. The numbers are typical and generated at a differential

input voltage of 0 V. The output update rate is selected via the

SF7-SF0 bits in the Filter Register. It is important to note that

the peak-to-peak resolution figures represent the resolution for

which there will be no code flicker within a six-sigma limit. The

output noise comes from two sources. The first is the electrical

–60

–80

–100

ATTENUATION – dB

–120

–140

–160

0 10010

SF = 255

OUTPUT DATA RATE = 5.35Hz

INPUT BANDWIDTH = 1.28Hz

50Hz REJECTION = –93dB, 50Hz1Hz REJECTION = –93dB

60Hz REJECTION = –74dB, 60Hz1Hz REJECTION = –68dB

20 30 40 50 60 70 80 90

FREQUENCY – Hz

Figure 9. Filter Profile with SF = 255

noise in the semiconductor devices (device noise) used in the

implementation of the modulator. Secondly, when the analog

input is converted into the digital domain, quantization noise is

added. The device noise is at a low level and is independent of

frequency. The quantization noise starts at an even lower level

but rises rapidly with increasing frequency to become the dominant noise source. The numbers in the tables are given for the

bipolar input ranges. For the unipolar ranges the rms noise

numbers will be the same as the bipolar range, but the peak-topeak resolution is now based on half the signal range, which

effectively means losing 1 bit of resolution.

–14–

REV. 0

Page 15

AD7719

Table II. Typical Output RMS Noise vs. Input Range and Update Rate for Main ADC (Buffered Mode) Output RMS

Noise in V

SF Data Update

Word Rate (Hz) 20 mV 40 mV 80 mV 160 mV 320 mV 640 mV 1.28 V 2.56 V

13 105.3 1.50 1.50 1.60 1.75 3.50 4.50 6.70 11.75

69 19.79 0.60 0.65 0.65 0.65 0.65 0.95 1.40 2.30

255 5.35 0.35 0.35 0.37 0.37 0.37 0.51 0.82 1.25

Table III. Peak-to-Peak Resolution vs. Input Range and Update Rate for Main ADC (Buffered Mode) Peak-to-Peak

Resolution in Bits

Input Range

SF Data Update

Word Rate (Hz) 20 mV 40 mV 80 mV 160 mV 320 mV 640 mV 1.28 V 2.56 V

13 105.3 12 13 14 15 15 15.5 16 16

69 19.79 13 14 15 16 17 17.5 18 18.5

255 5.35 14 15 16 17 18 18.5 18.8 19.2

Table IV. Typical Output RMS Noise vs. Input Range and Update Rate for Main ADC (Unbuffered Mode) Output

RMS Noise in V

SF Data Update

Word Rate (Hz) 20 mV 40 mV 80 mV 160 mV 320 mV 640 mV 1.28 V 2.56 V

13 105.3 1.27 1.27 1.35 1.48 2.95 3.82 5.69 10.2

69 19.79 0.52 0.56 0.56 0.56 0.56 0.82 1.21 2.00

255 5.35 0.30 0.30 0.32 0.32 0.32 0.44 0.71 1.10

Table V. Peak-to-Peak Resolution vs. Input Range and Update Rate for Main ADC (Unbuffered Mode) Peak-to-Peak

Resolution in Bits

SF Data Update

Word Rate (Hz) 20 mV 40 mV 80 mV 160 mV 320 mV 640 mV 1.28 V 2.56 V

13 105.3 12 13 14 15 15 15.5 16 16

69 19.79 13 14 15 16 17 17.5 18 18.5

255 5.35 14 15 16 17 18 18.5 19 19.5

Input Range

Input Range

Input Range

Table VI. Typical Output RMS Noise vs.

Update Rate for Auxiliary ADC Unbuffered)

SF Data Update Input Range

Word Rate (Hz) 2.5 V

13 105.3 10.75 µV

69 19.79 2.00 µV

255 5.35 1.15 µV

REV. 0

Table VII. Peak-to-Peak Resolution vs. Update

Rate for Auxiliary ADC (Unbuffered Mode)

SF Data Update Input Range

Word Rate (Hz) 2.5 V

13 105.3 16 Bits

69 19.79 16 Bits

255 5.35 16 Bits

–15–

Page 16

AD7719

ON-CHIP REGISTERS

Both the main and auxiliary ADC channels are controlled and

configured via a number of on-chip registers as shown in Figure

10 and described in more detail in the following pages. In the following descriptions, SET implies a Logic 1 state and CLEARED

implies a Logic 0 state, unless otherwise stated.

DIN

DOUT

DOUT

DOUT

DOUT

DOUT

DOUT

DOUT

DOUT

DOUT

COMMUNICATIONS REGISTER

WEN R/W 00 A1A2A3 A0

ADC STATUS REGISTER

DIN

MODE REGISTER

DIN

MAIN ADC CONTROL REGISTER

DIN

AUX ADC CONTROL REGISTER

DIN

I/O CONTROL REGISTER

DIN

FILTER REGISTER

MAIN ADC DATA REGISTER

AUX ADC DATA REGISTER

REGISTER

SELECT

DECODER

DOUT

DOUT

DOUT

DOUT

DOUT

DOUT

DIN

MAIN ADC OFFSET REGISTER

DIN

AUX ADC OFFSET REGISTER

DIN

MAIN ADC GAIN REGISTER

DIN

AUX ADC GAIN REGISTER

ID REGISTER

DIN

TEST REGISTER

Figure 10. On-Chip Registers

–16–

REV. 0

Page 17

AD7719

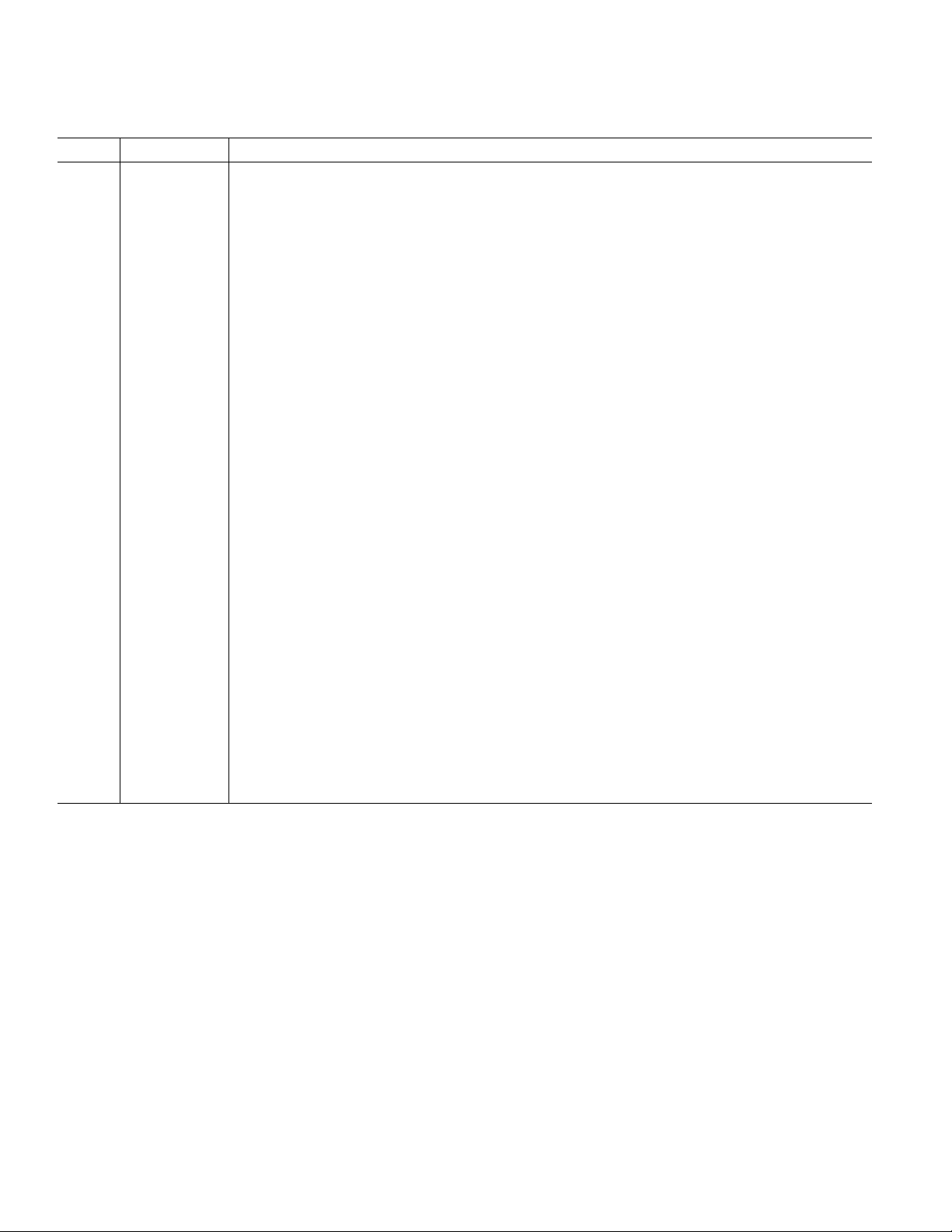

Table VIII. Registers—Quick Reference Guide

Power-On/Reset

Register Name Type Size Default Value Function

Communications Write Only 8 Bits Not Applicable All operations to other registers are initiated through

MSB LSB

WWWWEEEENNNNR/WW

WW

0 0 A3 A2 A1 A0

Status Register Read Only 8 Bits 00 Hex Provides status information on conversions, cali-

MSB LSB

RDY0 RDY1 CAL NOREF ERR0 ERR1 0 LOCK

Mode Register Read/Write 8 Bits 00 Hex Controls functions such as mode of operation, chan-

MSB LSB

0 BUF 0 CHCON OSCPD MD2 MD1 MD0

Main ADC (AD0CON)

Control Register Read/Write 8 Bits 07 Hex This register is used to enable the Main ADC and

MSB LSB

AD0EN WL CH1 CH0 U/B RN2 RN1 RN0

the Communications Register. This controls whether

subsequent operations are read or write operations

and also selects the register for that subsequent

operation.

brations, error conditions, and the validity of the

reference voltage.

nel configuration, oscillator operation in power-down.

configure the Main ADC for range, channel selection,

16-/24-bit operation, and unipolar or bipolar operation.

Aux ADC (AD1CON)

Control Register Read/Write 8 Bits 01 Hex This register is used to enable the aux ADC and

configure the Aux ADC for range, channel selection,

MSB LSB

AD1EN ACH2 ACH1 ACH0 U/B 0 0 ARN

unipolar or bipolar operation, and input range.

I/O (IOCON)

Control Register Read/Write 16 Bits 0000 Hex This register is used to control and configure the

various excitation and burnout current source options

MSB

PSW2 PSW1 0 BO I2PIN I1PIN I2EN I1EN

LSB

P4DIR P3DIR P2EN P1EN P4DAT P3DAT P2DAT P1DAT

available on-chip along with controlling the I/O port.

Filter Register Read/Write 8 Bits 45 Hex This register determines the amount of averaging

MSB LSB

SF7 SF6 SF5 SF4 SF3 SF2 SF1 SF0

performed by the sinc filter and consequently determines the data update rate of the AD7719. The filter

register determines the update rate for both the main

and aux ADCs.

REV. 0

–17–

Page 18

AD7719

Power-On/Reset

Register Name Type Size Default Value Function

Main ADC (DATA0)

Data Register Read Only 16 Bits or 24 Bits 000000 Hex Provides the most up-to-date conversion result from

the Main ADC. Main ADC data register length

can be programmed to be 16-bit or 24-bit.

Aux ADC (DATA1)

Data Register Read Only 16 Bits 0000 Hex Provides the most up-to-date conversion result from

the auxiliary ADC. Aux ADC data register length is

16 bits.

Main ADC

Offset Register Read/Write 24 Bits 800000 Hex Contains a 24-bit word that is the offset calibration

coefficient for the part. The contents of this register

are used to provide offset correction on the output

from the digital filter. There are three Offset Registers on the part and these are associated with input

channel pairs as outlined in the AD0CON register.

Main ADC

Gain Register Read/Write 24 Bits 5XXXX5 Hex Contains a 24-bit word that is the gain calibration

coefficient for the part. The contents of this register

are used to provide gain correction on the output

from the digital filter. There are three Gain Registers

on the part and these are associated with input channel pairs as outlined in the AD0CON register.

Aux ADC

Offset Register Read/Write 16 Bits 8000 Hex Contains a 16-bit word that is the offset calibration

coefficient for the part. The contents of this register

are used to provide offset correction on the output

from the digital filter.

Aux ADC

Gain Register Read/Write 24 Bits 59XX Hex Contains a 16-bit word that is the gain calibration

coefficient for the part. The contents of this register

are used to provide gain correction on the output

from the digital filter.

ID Register Read 8 Bits 0X Hex Contains an 8-bit byte that is the identifier for the

part.

Test Registers Read/Write 16 Bits 0000 Hex Controls the test modes of the part which are used

when testing the part. The user is advised not to

change the contents of these registers.

–18–

REV. 0

Page 19

AD7719

Communications Register (A3, A2, A1, A0 = 0, 0, 0, 0)

The Communications Register is an 8-bit write-only register. All communications to the part must start with a write operation to the

Communications Register. The data written to the Communications Register determines whether the next operation is a read

or write operation, and to which register this operation takes place. For read or write operations, once the subsequent read or write

operation to the selected register is complete, the interface returns to where it expects a write operation to the Communications

Register. This is the default state of the interface, and on power-up or after a RESET, the AD7719 is in this default state waiting for

a write operation to the Communications Register. In situations where the interface sequence is lost, a write operation of at least 32

serial clock cycles with DIN high, returns the AD7719 to this default state by resetting the part. Table IX outlines the bit designations for the Communications Register. CR0 through CR7 indicate the bit location, CR denoting the bits are in the Communications

Register. CR7 denotes the first bit of the data stream.

CR7 CR6 CR5 CR4 CR3 CR2 CR1 CR0

WEN

(0) R/W (0) 0 (0) 0 (0) A3 (0) A2 (0) A1 (0) A0 (0)

Table IX. Communications Register Bit Designations

Bit Bit

Location Name Description

CR7 WEN Write Enable Bit. A 0 must be written to this bit so the write operation to the Communications Register

actually takes place. If a 1 is written to this bit, the part will not clock on to subsequent bits in the register. It will stay at this bit location until a 0 is written to this bit. Once a 0 is written to the WEN bit, the

next seven bits will be loaded to the Communications Register.

CR6 R/W A zero in this bit location indicates that the next operation will be a write to a specified register. A one in

this position indicates that the next operation will be a read from the designated register.

CR5 Zero A zero must be written to this bit position to ensure correct operation of the AD7719.

CR4 Zero A zero must be written to this bit position to ensure correct operation of the AD7719.

CR3–CR0 A3–A0 Register Address Bits. These address bits are used to select which of the AD7719’s registers are being

accessed during this serial interface communication. A3 is the MSB of the three selection bits.

Table X. Register Selection Table

A3 A2 A1 A0 Register

0000Communications Register during a Write Operation

0000Status Register during a Read Operation

0001Mode Register

0010Main ADC Control Register (AD0CON)

0011Aux ADC Control Register (AD1CON)

0100Filter Register

0101Main ADC Data Register

0110Aux ADC Data Register

0111I/O Control Register

1000Main ADC Offset Calibration Register

1001Aux ADC Offset Calibration Register

1010Main ADC Gain Calibration Register

1011Aux ADC Gain Calibration Register

1100Test 1 Register

1101Test 2 Register

1110Undefined

1111ID Register

REV. 0

–19–

Page 20

AD7719

Status Register (A3, A2, A1, A0 = 0, 0, 0, 0; Power-On Reset = 00 Hex)

The ADC Status Register is an 8-bit read-only register. To access the ADC Status Register, the user must write to the Communications Register selecting the next operation to be a read and load bits A3–A0 with 0, 0, 0, 0. Table XI outlines the bit designations for

the Status Register. SR0 through SR7 indicate the bit location, SR denoting the bits are in the Status Register. SR7 denotes the first

bit of the data stream. The number in brackets indicates the power-on/reset default status of that bit.

7RS6RS5RS4RS3RS2RS1RS0RS

)0(0YDR)0(1YDR)0(LAC)0(FERXON)0(0RRE)0(1RRE)0()0(KCOL

Table XI. Status Register Bit Designations

Bit Bit

Location Name Description

SR7 RDY0 Ready Bit for Main ADC.

Set when data is written to Main ADC data registers or on completion of calibration cycle. The RDY0 bit

is cleared automatically after the Main ADC data register has been read or a period of time before the data

register is updated with a new conversion result. This bit is also cleared by a write to the mode bits to

indicate a conversion or calibration.

SR6 RDY1 Ready Bit for Aux ADC.

Set when data is written to Aux ADC data registers or on completion of calibration cycle. The RDY1 bit

is cleared automatically after the Aux ADC data register has been read or a period of time before the data

register is updated with a new conversion result. This bit is also cleared by a write to the mode bits to

indicate a conversion or calibration.

SR5 CAL Calibration Status Bit.

Set to indicate completion of calibration. It is set at the same time that the RDY0 and/or RDY1 bits

are set high.

Cleared by a write to the mode bits to start another ADC conversion or calibration.

SR4 NOXREF No External Reference Bit. (Only active if Main ADC is active and applies to REFIN1 only.)

Set to indicate that one or both of the REFIN1 pins is floating or the applied voltage is below a specified

threshold. When Set, conversion results are clamped to all ones.

Cleared to indicate valid Reference applied between REFIN1(+) and REFIN1(–).

SR3 ERR0 Main ADC Error Bit.

Set to indicate that the result written to the Main ADC data registers has been clamped to all zeros or all

ones. After a calibration this bit also flags error conditions that caused the calibration registers not to be

written. Error sources include Overrange, Underrange and NOXREF.

Cleared by a write to the mode bits to initiate a conversion or calibration.

SR2 ERR1 Aux ADC Error Bit.

Set to indicate that the result written to the Aux ADC data registers has been clamped to all zeros or all

ones. After a calibration this bit also flags error conditions that caused the calibration registers not to be

written. Error sources include Overrange, Underrange, and NOXREF.

Cleared by a write to the mode bits to initiate a conversion or calibration.

SR1 0 Reserved for Future Use.

SR0 LOCK PLL Lock Status Bit.

Set if the PLL has locked onto the 32 kHz crystal oscillator clock. If the user is worried about exact sampling

frequencies etc., the LOCK bit should be interrogated and the result discarded if the LOCK bit is zero.

–20–

REV. 0

Page 21

AD7719

Mode Register (A3, A2, A1, A0 = 0, 0, 0, 1; Power-On-Reset = 00 Hex)

The Mode Register is an 8-bit register from which data can be read or to which data can be written. This register configures the

operating modes of the AD7719. Table XII outlines the bit designations for the Mode Register. MR7 through MR0 indicate the bit

location, MR denoting the bits are in the Mode Register. MR7 denotes the first bit of the data stream. The number in brackets indicates the power-on/reset default status of that bit.

MR7 MR6 MR5 MR4 MR3 MR2 MR1 MR0

0 (0) BUF (0) 0 (0) CHCON (0) OSCPD (0) MD2 (0) MD1 (0) MD0 (0)

Table XII. MODE Register Bit Designations

Bit Bit

Location Name Description

MR7 0 Reserved for Future Use.

MR6 BUF Configures the Main ADC for buffered or unbuffered mode of operation. If set, the Main ADC

operates in unbuffered mode, lowering the power consumption of the AD7719. If cleared, the

Main ADC operates in buffered mode allowing the user to place source impedances on the front end

without contributing gain errors to the system.

MR5 0 Reserved for Future Use.

MR4 CHCON Channel Configure Bit. If this bit is set, the Main ADC operates with three pseudo-differential input

channels and the AUX ADC does not have AIN3/AIN4 as an input option. If cleared, the Main

ADC operates with two fully differential input channels and the aux channel operates as one fully

differential input and two single-ended inputs or three single-ended inputs.

MR3 OSCPD Oscillator Power-Down Bit.

If this bits is set, placing the AD7719 in standby mode will stop the crystal oscillator, reducing the

power drawn by the AD7719 to a minimum. The oscillator will require 300 ms to begin oscillating

when the ADC is taken out of standby mode. If this bit is cleared, the oscillator is not shut off when

the ADC is put into standby mode and will not require the 300 ms start-up time when the ADC is

taken out of standby.

MR2–MR0 MD2–MD0 Main and Aux ADC Mode Bits.

These bits select the operational mode of the enabled ADC as follows:

MD2 MD1 MD0

0 0 0 Power-Down Mode (Power-On Default).

The current sources, power switches, and PLL are shut off in power-down mode.

0 0 1 Idle Mode.

In Idle Mode the ADC filter and modulator are held in a reset state although the modulator clocks

are still provided.

0 1 0 Single Conversion Mode.

In Single Conversion Mode, a single conversion is performed on the enabled channels. On completion

of the conversion the ADC data registers are updated, the relevant flags in the STATUS register are

written and idle mode is entered with the MD2–MD0 being written accordingly to 001.

0 1 1 Continuous Conversion.

In continuous conversion mode the ADC data registers are regularly updated at the selected update

rate (see Filter register)

1 0 0 Internal Zero-Scale Calibration.

Internal short automatically connected to the enabled channel(s). Returns to Idle mode (001) when

complete.

1 0 1 Internal Full-Scale Calibration.

External V

when complete.

1 1 0 System Zero-Scale Calibration.

User should connect system zero-scale input to the channel input pins as selected by CH1/CH0 and

ACH1/ACH0 bits in the control registers.

1 1 1 System Full-Scale Calibration.

User should connect system full-scale input to the channel input pins as selected by CH1/CH0 and

ACH1/ACH0 bits in the control registers.

is connected automatically to the ADC input for this calibration. Returns to idle mode

REF

REV. 0

–21–

Page 22

AD7719

Operating Characteristics when Addressing the Mode and Control Registers

1. Any change to the MD bits will immediately reset both ADCs. A write to the MD2–0 bits with no change is also treated as a reset.

(See exception to this in Note 3.)

2. If AD0CON is written when AD0EN = 1, or if AD0EN is changed from 0 to 1, both ADCs are also immediately reset. In other

words, the Main ADC is given priority over the Aux ADC and any change requested on main is immediately responded to.

3. On the other hand, if AD1CON is written to only the Aux ADC is reset. For example, if the Main ADC is continuously converting when the Aux ADC change or enable occurs, the Main ADC continues undisturbed. Rather than allow the Aux ADC

to operate with a phase difference from the Main ADC, the Aux ADC will fall into step with the outputs of the Main ADC.

The result is that the first conversion time for the Aux channel will be delayed up to three outputs while the Aux ADC update rate

is synchronized to the Main ADC.

4. Once the MODE has been written with a calibration mode, the RDY0/1 bits (STATUS) are immediately reset and the calibration

commences. On completion the appropriate calibration registers are written, the relevant bits in STATUS are written, and

the MD2–0 bits are reset to 001 to indicate the ADC is back in Idle Mode.

5. Any calibration request of the Aux ADC while the temperature sensor is selected will fail to complete.

6. Calibrations are performed with the maximum allowable SF value. SF register is reset to user configuration after calibration.

Main ADC Control Register (AD0CON): (A3, A2, A1, A0 = 0, 0, 1, 0; Power-On Reset = 07 Hex)

The Main ADC control Register is an 8-bit register from which data can be read or to which data can be written. This register is used

to configure the Main ADC for range, channel selection, 16-/24-bit operation and unipolar or bipolar coding. Table XIII outlines the bit

designations for the Main ADC control register. AD0CON7 through AD0CON0 indicate the bit location, AD0CON denoting the

bits are in the Main ADC Control Register. AD0CON7 denotes the first bit of the data stream. The number in brackets indicates the

power-on/reset default status of that bit.

AD0CON7 AD0CON6 AD0CON5 AD0CON4 AD0CON3 AD0CON2 AD0CON1 AD0CON0

AD0EN (0) WL (0) CH1 (0) CH0 (0) U/B (0) RN2 (1) RN1 (1) RN0 (1)

Table XIII. Main ADC Control Register (AD0CON) Bit Designations

Bit Bit

Location Name Description

AD0CON7 AD0EN Main ADC Enable Bit.

Set by user to enable the Main ADC. When set the Main ADC operates according to the MD

bits in the mode register.

Cleared by the user to power down the Main ADC.

AD0CON6 WL 16-/24-Bit Operating Mode.

Set by user to enable 16-bit mode. The conversion results from the Main ADC will be rounded

to 16 bits and the Main ADC data register will be 16 bits wide.

Cleared by user to enable 24-bit mode. The conversion results from the Main ADC will be

rounded to 24 bits and the Main ADC data register will be 24 bits wide.

AD0CON5 CH1 Main ADC Channel Selection Bits.

AD0CON4 CH0 Written by the user to select the differential input pairs used by the Main ADC as follows:

Note: The CHCON bit resides in the MODE register.

CHCON CH1 CH0 Positive Input Negative Input Calibration Register Pair

0 0 0 AIN1 AIN2 0

0 0 1 AIN3 AIN4 1

0 1 0 AIN2 AIN2 0

0 1 1 AIN3 AIN2 1

1 0 0 AIN1 AIN4 0

1 0 1 AIN3 AIN4 1

1 1 0 AIN4 AIN4 0

1 1 1 AIN2 AIN4 2

–22–

REV. 0

Page 23

AD7719

Table XIII (continued)

AD0CON3 U/B Main ADC Unipolar/Bipolar Bit.

Set by user to enable unipolar coding i.e., Zero differential input will result in 000000 Hex output

and a full-scale differential input will result in FFFFFF Hex output when operated in 24-bit mode.

Cleared by user to enable bipolar coding, Negative full-scale differential input will result in an

output code of 000000 Hex, Zero differential input will result in an output code of 800000 Hex

and a Positive full-scale differential input will result in an output code of FFFFFF Hex.

AD0CON2 RN2 Main ADC Range Bits.

AD0CON1 RN1 Written by the user to select the Main ADC input range as follows.