Page 1

16-Bit, 30 MSPS

a

FEATURES

30 MSPS Update Rate

16-Bit Resolution

Linearity: 1/2 LSB DNL @ 14 Bits

1 LSB INL @ 14 Bits

Fast Settling: 25 ns Full-Scale Settling to 0.025%

SFDR @ 1 MHz Output: 86 dBc

THD @ 1 MHz Output: 71 dBc

Low Glitch Impulse: 35 pV-s

Power Dissipation: 465 mW

On-Chip 2.5 V Reference

Edge-Triggered Latches

Multiplying Reference Capability

APPLICATIONS

Arbitrary Waveform Generation

Communications Waveform Reconstruction

Vector Stroke Display

PRODUCT DESCRIPTION

The AD768 is a 16-bit, high speed digital-to-analog converter

(DAC) that offers exceptional ac and dc performance. The

AD768 is manufactured on ADI’s Advanced Bipolar CMOS

(ABCMOS) process, combining the speed of bipolar transistors,

the accuracy of laser-trimmable thin film resistors, and the efficiency of CMOS logic. A segmented current source architecture

is combined with a proprietary switching technique to reduce

glitch energy and maximize dynamic accuracy. Edge triggered

input latches and a temperature compensated bandgap reference

have been integrated to provide a complete monolithic DAC

solution.

The AD768 is a current-output DAC with a nominal full-scale

output current of 20 mA and a 1 kΩ output impedance. Differential current outputs are provided to support single-ended

or differential applications. The current outputs may be tied

directly to an output resistor to provide a voltage output, or fed

to the summing junction of a high speed amplifier to provide a

buffered voltage output. Also, the differential outputs may be

interfaced to a transformer or differential amplifier.

The on-chip reference and control amplifier are configured for

maximum accuracy and flexibility. The AD768 can be driven by

the on-chip reference or by a variety of external reference voltages based on the selection of an external resistor. An external

capacitor allows the user to optimally trade off reference bandwidth and noise performance.

The AD768 operates on ± 5 V supplies, typically consuming

465 mW of power. The AD768 is available in a 28-pin SOIC

package and is specified for operation over the industrial temperature range.

D/A Converter

AD768

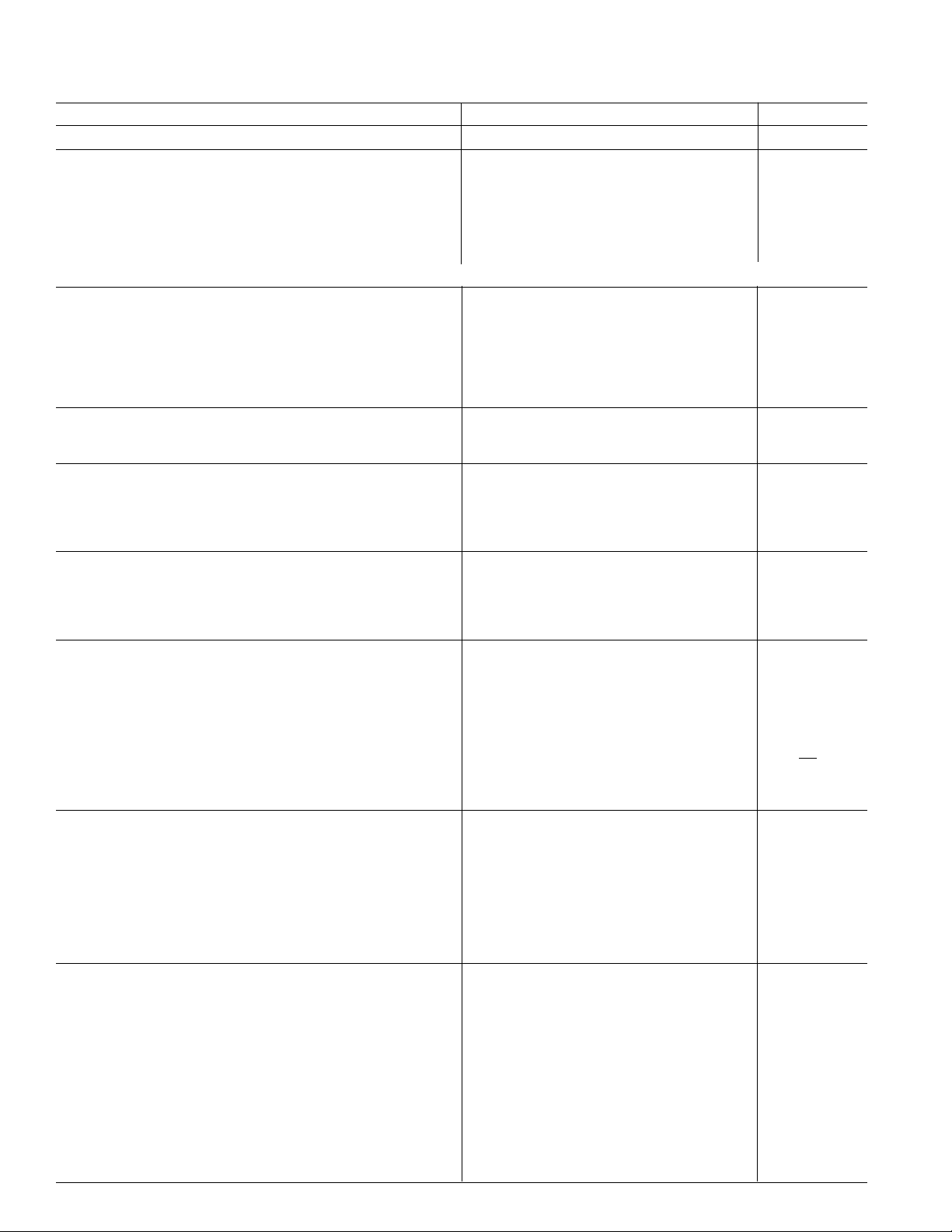

FUNCTIONAL BLOCK DIAGRAM

V

DCOM

(MSB)

DB15

MSBs: SEGMENTED

CURRENT SOURCES

AND SWITCHES

MSB

DB0

(LSB)

DECODER

AND

EDGE-

TRIGGERED

BIT

LATCHES

CLOCK

LSBs:

CURRENT SOURCES,

SWITCHES, AND

1kΩ R-2R

LADDERS

NC REFCOM REFOUT

PRODUCT HIGHLIGHTS

1. The low glitch and fast settling time provide outstanding

dynamic performance for waveform reconstruction or digital

synthesis requirements, including communications.

2. The excellent dc accuracy of the AD768 makes it suitable for

high speed A/D conversion applications.

3. On-chip, edge-triggered input CMOS latches interface

readily to CMOS logic families. The AD768 can support update rates up to 40 MSPS.

4. A temperature compensated, 2.5 V bandgap reference is

included on-chip allowing for generation of the reference

input current with the use of a single external resistor. An external reference may also be used.

5. The current output(s) of the AD768 may be used singly or

differentially, either into a load resistor, external op amp

summing junction or transformer.

6. Proper selection of an external resistor and compensation

capacitor allow the performance-conscious user to optimize

the AD768 reference level and bandwidth for the target

application.

DD

2.5V

BANDGAP

REFERENCE

AD768

1k

CONTROL

IREFIN

AMP

IOUTA

NR

IOUTB

LADCOM

V

EE

1k

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

© Analog Devices, Inc., 1996

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

Page 2

(T

to T

, VDD = +5.0 V, VEE = –5.0 V, LADCOM, REFCOM, DCOM = 0 V, IREFIN = 5 mA,

MAX

AD768–SPECIFICA TIONS

MIN

CLOCK = 10 MHz, unless otherwise noted)

Parameter Min Typ Max Units

RESOLUTION 16 Bits

DC ACCURACY

1

Linearity Error

= +25°C–8±4 +8 LSB

T

A

to T

T

MIN

MAX

–8 +8 LSB

Differential Nonlinearity

= +25°C–6±2 +6 LSB

T

A

to T

T

MIN

MAX

–8 +8 LSB

Monotonicity (13-Bit) GUARANTEED OVER RATED SPECIFICATION TEMPERATURE RANGE

ANALOG OUTPUT

Offset Error –0.2 +0.2 % of FSR

Gain Error –1.0 +1.0 % of FSR

Full-Scale Output Current

2

20 mA

Output Compliance Range –1.2 +5.0 V

Output Resistance 0.8 1.0 1.2 kΩ

Output Capacitance 3 pF

REFERENCE OUTPUT

Reference Voltage 2.475 2.5 2.525 V

Reference Output Current

3

+5.0 +15 mA

REFERENCE INPUT

Reference Input Current 1 5 7 mA

Reference Bandwidth

4

Small Signal, IREF = 5 mA ± 0.1 mA 28 MHz

Large Signal, IREF = 4 mA ± 2 mA 9 MHz

TEMPERATURE COEFFICIENTS

Unipolar Offset Drift –5 +5 ppm of FSR/

Gain Drift

Gain Drift

5

6

–20 +20 ppm of FSR/oC

–40 +40 ppm of FSR/oC

Reference Voltage Drift –30 +30 ppm/oC

DYNAMIC PERFORMANCE

7

Maximum Output Update Rate 30 40 MSPS

Output Settling Time (t

Output Propagation Delay (t

) (to 0.025%) 25 35 ns

ST

)10ns

PD

Glitch Impulse 35 pV-s

Output Rise Time (10% to 90%) 5 ns

Output Fall Time (10% to 90%) 5 ns

Output Noise (DB0–DB15 High, into 50 Ω) 3 nV/√

Hz

Differential Gain Error 0.01 %

Differential Phase Error 0.01 Degree

DIGITAL INPUTS

Logic “1” Voltage 3.5 V

Logic “0” Voltage 1.5 V

Logic “1” Current –10 +10 µA

Logic “0” Current –10 +10 µA

Input Capacitance 10 pF

Input Setup Time (t

Input Hold Time (t

Latch Pulse Width (t

AC LINEARITY

)10ns

S

)5ns

H

)10 ns

LPW

7

Spurious-Free Dynamic Range (SFDR Within a Window)

= 1.002 MHz; CLOCK = 10 MHz; 2 MHz Span 86 79 dB

F

OUT

= 1.002 MHz; CLOCK = 20 MHz; 2 MHz Span 85 dB

F

OUT

= 5.002 MHz; CLOCK = 30 MHz; 10MHz Span 78 dB

F

OUT

Spurious-Free Dynamic Range (SFDR to Nyquist)

= 1.002 MHz; CLOCK = 10 MHz 74 70 dB

F

OUT

= 1.002 MHz; CLOCK = 20 MHz 73 dB

F

OUT

= 5.002 MHz; CLOCK = 30 MHz 67 dB

F

OUT

Total Harmonic Distortion (THD)

= 1.002 MHz; CLOCK = 10 MHz –71 –68 dB

F

OUT

= 1.002 MHz; CLOCK = 20 MHz –66 dB

F

OUT

F

= 5.002 MHz; CLOCK = 30 MHz –61 dB

OUT

o

C

–2–

REV. B

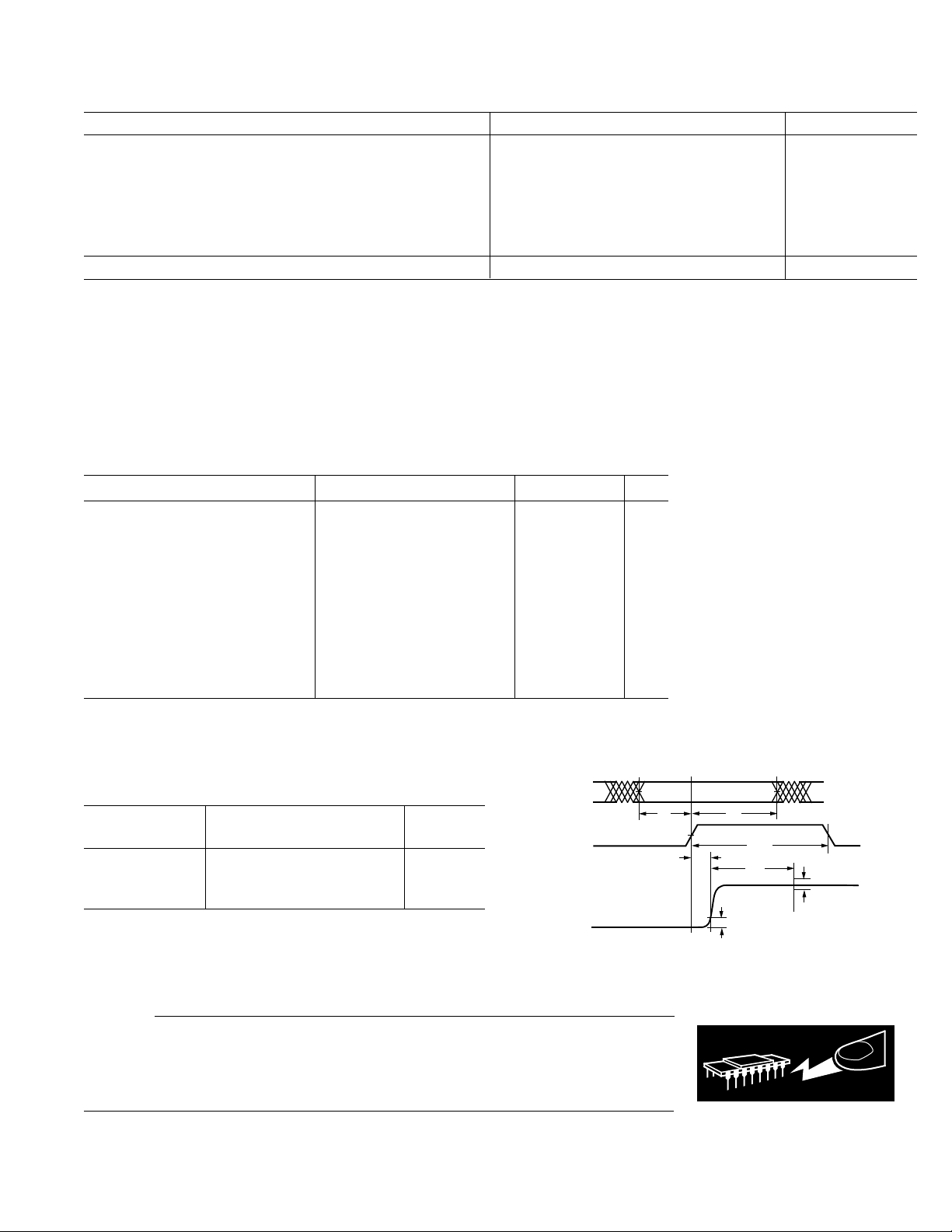

Page 3

Parameter Min Typ Max Units

t

H

t

S

t

LPW

t

PD

t

ST

0.025%

0.025%

DB0–DB15

CLOCK

IOUTA

OR

IOUTB

WARNING!

ESD SENSITIVE DEVICE

POWER SUPPLY

Positive Voltage Range 4.75 5 5.25 V

Negative Voltage Range –5.25 –5 –4.75 V

Positive Supply Current 30 40 mA

Negative Supply Current 63 73 mA

Nominal Power Dissipation 465 600 mW

Power Supply Rejection Ratio (PSRR) –0.2 +0.2 % of FSR/V

OPERATING RANGE –40 +85 °C

NOTES

1

Measured at IOUTA, driving a virtual ground.

2

Nominal FS output current is 4× the current at IREFIN. Therefore, nominal FS current is 20 mA when IREFIN = 5 mA.

3

Output current is defined as total current available for IREFIN and any external load.

4

Reference bandwidth is a function of external cap at NR pin. Refer to compensation section of data sheet for details.

5

Excludes internal reference drift.

6

Includes internal reference drift.

7

Measured as unbuffered voltage output (1 V range) with FS current into 50 Ω load at IOUTB.

Specifications subject to change without notice.

AD768

ABSOLUTE MAXIMUM RATINGS

*

Parameter with Respect to Min Max Units

Positive Supply Voltage (V

Negative Supply Voltage (V

) DCOM, REFCOM, LADCOM –0.5 +6.0 V

DD

) DCOM, REFCOM, LADCOM –6.0 +0.5 V

EE

Analog-to-Other Grounds (REFCOM) DCOM, LADCOM –0.5 +0.5 V

Digital-to-Other Grounds (DCOM) LADCOM, REFCOM –0.5 +0.5 V

Reference Output (REFOUT) REFCOM V

+ 0.5 V

DD

Reference Input Current (IREFIN) +7.5 mA

Digital Inputs (DB0–DB15, CLOCK) DCOM –0.5 V

+ 0.5 V

DD

Analog Outputs (IOUTA, IOUTB) LADCOM –2.0 +5.0 V

Maximum Junction Temperature +150 °C

Storage Temperature –65 +150 °C

Lead Temperature +300 °C

*Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating for extended periods may affect device

reliability.

ORDERING GUIDE

Package

Model Package Description Option

AD768AR 28-Pin 300 mil SOIC R-28

AD768ACHIPS Die

AD768-EB AD768 Evaluation Board

Timing Diagram

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD768 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. B

–3–

Page 4

AD768

1

WAFER TEST LIMITS

(TA = +258C, VDD = +5.0 V, VEE = –5.0 V, I

Parameter AD768ACHIPS Limit Units

Integral Nonlinearity

Differential Nonlinearity

2

2

±8 LSB max

± 6 LSB max

Offset Error ± 0.2 % FSR max

Gain Error ±1.0 % FSR max

Reference Voltage ±1.0 % of nom. 2.5 V max

Positive Supply Current 40 mA max

Negative Supply Current 73 mA max

Power Dissipation 600 mW max

NOTES

1

Electrical test are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal

yield loss, yield after packaging is not guaranteed for standard product dice.

2

Limits extrapolated from testing of individual bit errors.

3

Die offers latch control pad. Edge triggered latches become level triggered when latch control and clock pads are high.

4

Die substrate is connected to V

EE.

PIN DESCRIPTIONS

Pin No. Symbol Type Name and Function

1 IOUTA AO DAC Current Output. Full-scale current when all data bits are 1s.

2 NR AI Noise Reduction Node. Add capacitor for noise reduction.

3 REFOUT AO Reference Output Voltage. Nominal value is 2.5 V.

4 NC NC No Connect. Reserved for internal use.

5 REFCOM P Reference Ground.

6 IREFIN AI Reference Input Current. Nominal is 5 mA. DAC full-scale is 4× this current.

7 DB0 DI Data Bit 0 (LSB).

8–14 DB1–DB7 DI Data Bits 1–7.

15 DCOM P Digital Ground.

16 CLOCK DI Clock Input. Data latched on positive edge of clock.

17–23 DB8–DB14 DI Data Bits 8–14.

24 DB15 DI Data Bit 15 (MSB).

25 V

26 V

DD

EE

P Positive Supply Voltage. Nominal is +5V.

P Negative Supply Voltage. Nominal is –5V.

27 IOUTB AO Complementary DAC Current Output. Full-scale current when all data bits are 0s.

28 LADCOM P DAC Ladder Common.

Type: AI = Analog Input; DI = Digital Input; AO = Analog Output; P = Power.

= 5 mA, unless otherwise noted)

REFIN

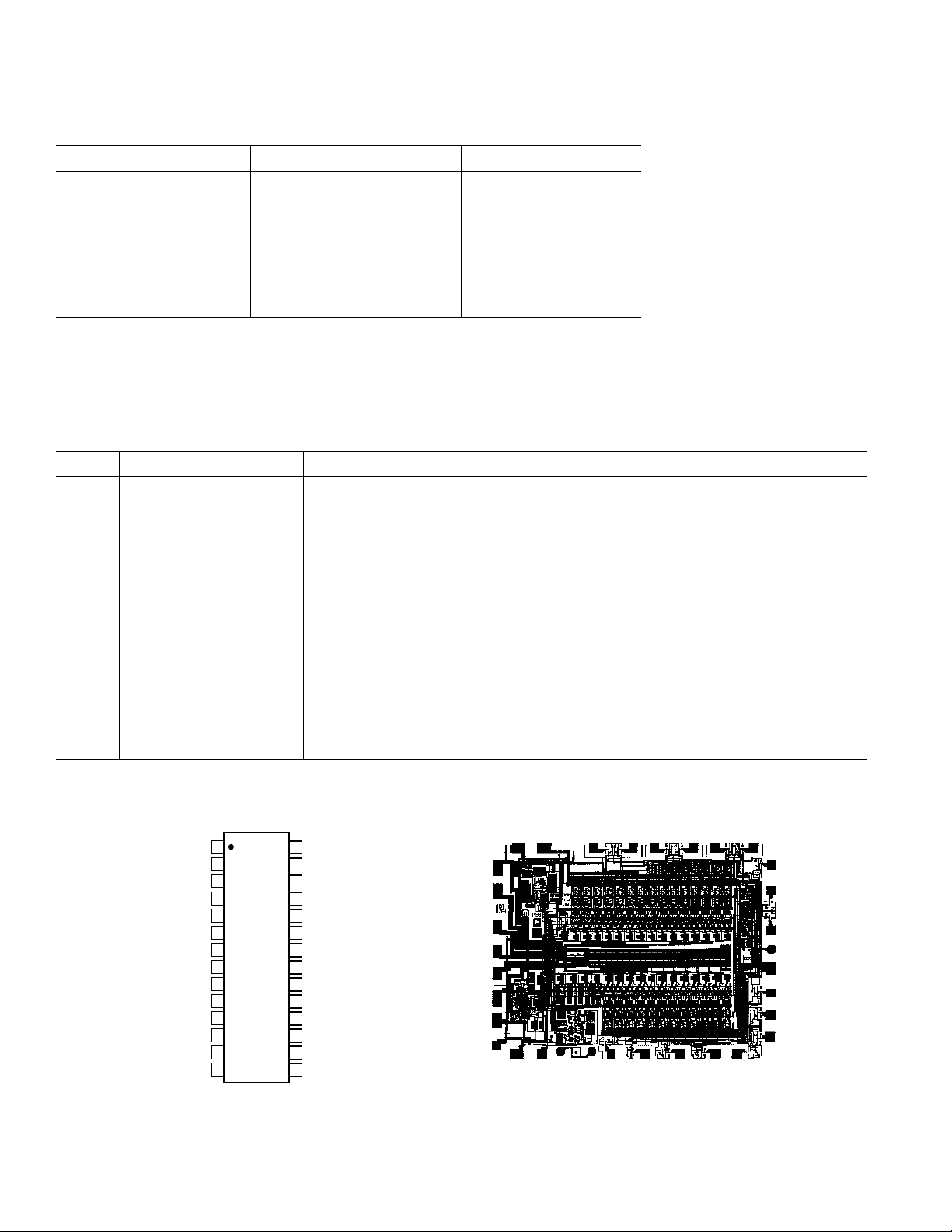

PIN CONFIGURATION

1

IOUTA

NR

REFOUT

NC

REFCOM

IREFIN

(LSB) DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

2

3

4

5

6

AD768

TOP VIEW

7

(Not to Scale)

8

9

10

11

12

13

14

NC = NO CONNECT

28

27

26

25

24

23

22

21

20

19

18

17

16

15

LADCOM

IOUTB

(–5V)

V

EE

VDD (+5V)

DB15 (MSB)

DB14

DB13

DB12

DB11

DB10

DB9

DB8

CLOCK

DCOM

DICE CHARACTERISTICS

VDDV

V

EE

V

EE

IOUTB

LADCOM

IOUTA

NR

REFOUT

NC

REFCOM IREFIN DB0 DB1 DB2 DB3 DB4

DB15 DB14 DB13 DB12 DB11 DB10

DD

Die Size:

×

0.1106

(2.81

0.1417 inch, 15,672 sq. mils

×

3.60 mm, 10.116 sq. mm)

–4–

3, 4

DB9

DB8

CLOCK

LATCH CONTROL

DCOM

DB7

DB6

DB5

REV. B

Page 5

AD768

DEFINITIONS OF SPECIFICATIONS

Linearity Error (Also Called Integral Nonlinearity or INL)

Linearity error is defined as the maximum deviation of the actual analog output from the ideal output, determined by a

straight line drawn from zero to full scale.

Differential Nonlinearity (or DNL)

DNL is the measure of the variation in analog value, normalized

to full scale, associated with a1LSBchangein digital input code.

Monotonicity

A D/A converter is monotonic if the output either increases or

remains constant as the digital input increases.

Offset Error

The deviation of the output current from the ideal of zero is

called offset error. For IOUTA, 0 mA output is expected when

the inputs are all 0s. For IOUTB, 0 mA output is expected

when all inputs are set to 1s.

Gain Error

The difference between the actual and ideal output span. The

actual span is determined by the output when all inputs are set

to 1s minus the output when all inputs are set to 0s. The ideal

output current span is 4× the current applied to the IREFIN pin.

Output Compliance Range

The range of allowable voltage at the output of a current-output

DAC. Operation beyond the maximum compliance limits may

cause either output stage saturation or breakdown, resulting in

nonlinear performance.

C

REFCOMP

R

20

6

DB11

REF

500Ω

REFINREFOUT

19

DB10

+5V

–5V

CLOCK

1µF

1µF

1µF

C

1µF

DB14

AD768

21222324

DB13

DB12

34

NC

V

DD

REFCOM

NR

V

EE

DCOM

CLOCK

+2.5V REF

MSB DECODE

& LATCHES

DB15

25

5

2

NR

26

15

16

Temperature Drift

Temperature drift is specified as the maximum change from the

ambient (+25°C) value to the value at either T

MIN

or T

MAX

. For

offset and gain drift, the drift is reported in ppm of full-scale

range (FSR) per degree C. For reference drift, the drift is reported in ppm per degree C.

Power Supply Rejection

The maximum change in the full-scale output as the supplies

are varied from nominal to minimum and maximum specified

voltages.

Settling Time

The time required for the output to reach and remain within a

specified error band about its final value, measured from the

start of the output transition.

Spurious-Free Dynamic Range

The difference, in dB, between the rms amplitude of the

input signal and the peak spurious signal over the specified

bandwidth.

Total Harmonic Distortion

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal. It is expressed as a percentage or in decibels (dB).

Glitch Impulse

Asymmetrical switching times in a DAC give rise to undesired

output transients which are quantified by a glitch impulse. It is

specified as the net area of the glitch in pV-sec.

IOUTA

5mA

SEGMENTED

CURRENT

SOURCES

LATCHES – LOWER 12 BITS

DB7

DB9

DB8

13141718

DB5

DB6

CURRENT SOURCES

AND R-2R LADDER

DB4

R

1kΩ

LAD

DB3

R

1kΩ

LADCOM

89101112

DB2

LAD

DB1

IOUTB

7

DB0

1

27

50Ω

28

R

50Ω

IOUTA

IOUTB

LOAD

Figure 1. Functional Block Diagram and Basic Hookup

FUNCTIONAL DESCRIPTION

The AD768 is a current-output DAC with a nominal full-scale

current of 20 mA and a 1 kΩ output impedance. Differential

outputs are provided to support single-ended or differential

applications. The DAC architecture combines segmented current sources for the top four bits (MSBs) and a 1kΩ R-2R ladder for the lower 12 bits (LSBs). The DAC current sources are

implemented with laser-trimmable thin film resistors for excellent dc linearity. A proprietary switching technique is utilized to

reduce glitch energy and maximize dynamic accuracy.

REV. B

–5–

The digital interface offers CMOS compatible edge-triggered

input latches that interface readily to CMOS logic and supports

clock rates up to 40 MSPS. A temperature compensated 2.5V

bandgap reference is integrated on-chip to drive the AD768 reference input current with the use of a single external resistor.

The functional block diagram in Figure 1 is a simple representation of the internal circuitry to aid the understanding of the

AD768’s operation. The DAC transfer function is described,

and followed by a detailed description of each key portion of the

circuit. Typical circuit configurations are shown in the section

APPLYING THE AD768.

Page 6

AD768

I

REFIN

– mA

POWER – mW

550

500

300

1.0 7.02.0 3.0 4.0 5.0 6.0

450

400

350

DAC TRANSFER FUNCTION

The AD768 may be used in either current-output mode with the

output connected to a virtual ground, or voltage-output mode

with the output connected to a resistive load.

In current output mode,

I

= (DAC CODE/65536) × (I

OUT

In voltage output mode,

= I

V

OUT

OUT

× R

LOADiRLAD

where:

DAC CODE is the decimal representation of the DAC inputs;

an integer between 0 and 65535.

I

is the current applied at the IREFIN pin, determined by

REFIN

V

REF/RREF

Substituting for I

V

OUT

= –V

.

and I

OUT

× (DAC CODE/65536) × 4 × [(R

REF

REFIN

,

These equations clarify an important aspect of the AD768

transfer function; the full-scale current output of the DAC is

proportional to a current input. The voltage output is then a

function of the ratio of (R

LOADiRLAD

)/R

REF

lation of resistor drift by selection of resistors with matched

characteristics.

REFERENCE INPUT

The IREFIN pin is a current input node with low impedance to

REFCOM. This input current sets the magnitude of the DAC

current sources such that the full-scale output current is exactly

four times the current applied at IREFIN. For the nominal input current of 5 mA, the nominal full-scale output current is

20 mA.

The 5 mA reference input current can be generated from the

on-chip 2.5 V reference with an external resistor of 500 Ω from

REFOUT to IREFIN. If desired, a variety of external reference

voltages may be used based on the selection of an appropriate

resistor. However, to maintain stability of the reference amplifier, the external impedance at IREFIN must be kept below

1kΩ.

IREFIN

5

6

V

EE

REFCOM

× 4)

REFIN

LOADiRLAD

)/R

REF

, allowing for cancel-

IFB

5mA

V

EE

]

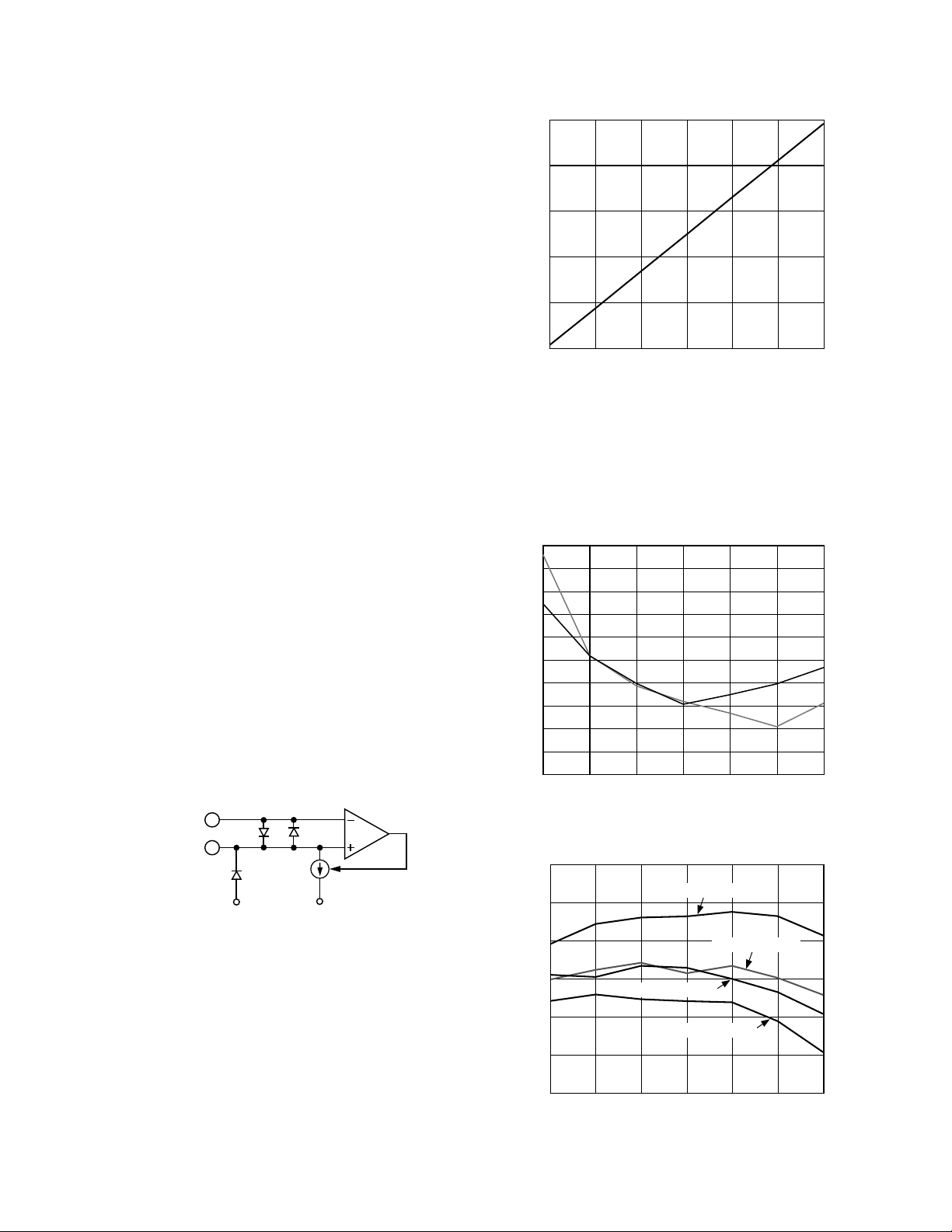

Figure 3. Power Dissipation vs. I

REFIN

Current

Note the AD768 is optimized for operation at an input current

of 5 mA. Both linearity and dynamic performance at other input

currents may be somewhat degraded. Figure 4 shows typical dc

linearity over a range of input currents. Figure 5 shows typical

SFDR (to Nyquist) performance over a range of input currents

and CLOCK input rates for a 1 MHz output frequency.

10

9

8

7

6

5

4

ERROR – LSB

3

2

1

0

1.0 7.02.0 3.0 4.0 5.0 6.0

I

REFIN

– mA

Figure 4. INL/DNL vs. I

–85

–80

CLOCK = 10 MSPS

REFIN

INL

DNL

Current

The I

current can be varied from 1 mA to 7 mA which

REFIN

subsequently will result in a proportional change in the DAC

Figure 2. Equivalent Reference Input Circuit

full-scale. Since the operating currents within the DAC vary

with I

, so does the power dissipation. Figure 3 illustrates

REFIN

that relationship.

–6–

–75

–70

SFDR – dB

–65

–60

–55

1.0 7.02.0 3.0 4.0 5.0 6.0

CLOCK = 30 MSPS

CLOCK = 40 MSPS

I

– mA

REFIN

Figure 5. SFDR (to Nyquist) vs. I

CLOCK = 20 MSPS

@ F

REFIN

OUT

= 1 MHz

REV. B

Page 7

REFERENCE OUTPUT

NOISE REDUCTION CAPACITOR – F

BANDWIDTH – Hz

100M

1k

10p 1µ100p 1n 10n 100n

10M

1M

100k

10k

DIGITAL INPUT CODE – k

8

–8

06510 20 30 40

4

–2

–4

–6

6

0

2

INL ERROR – LSB

50 6051525354555

The internal 2.5 V bandgap reference is provided for generation

of the I

current, and must be compensated externally with

REFIN

a capacitor of 0.1 µF or greater from REFOUT to REFCOM. If

an external reference is used, REFOUT should be tied directly

to the positive supply voltage, V

. This effectively turns off the

DD

internal reference, eliminating the need for the external capacitor at REFOUT. The reference is specified to drive a nominal

load of 5 mA with a maximum of 15 mA. Operation with a

heavier load will result in degradation of supply rejection and

reference voltage accuracy. Therefore, the reference output

should be buffered with an amplifier when additional load current is required. A properly sized pull-up resistor can also be

used to source additional current to the load. The resistors value

should be selected such that REFOUT will always source a

minimum of 5 mA to IREFIN and the additional load.

AD768

6

3

5

AD768

IREFIN

REFOUT

REFCOM

C

REFCOMP

500Ω

1µF

Figure 6. Typical Reference Hookup

TEMPERATURE CONSIDERATIONS

Note that the reference plays a key role in the overall temperature performance of the AD768. Any drift of I

directly in I

of I

REFIN

When the output is taken as a current, the drift

OUT.

(which depends on both V

REF

and R

shows up

REFIN

) must be mini-

REF

mized. This can be done by using the internal temperature compensated reference for V

resistor for R

If the output is taken as a voltage, it is a func-

REF.

tion of a resistor ratio, not an absolute resistor value.

ing resistors with matched temperature coefficients for R

and R

the drift in the resistor values will cancel, providing

LOAD,

and a low temperature coefficient

REF

By select-

REF

optimal drift performance.

REFERENCE NOISE REDUCTION AND MULTIPLYING

BANDWIDTH

For application flexibility and multiplying capabilities, the reference amplifier is designed to offer adjustable bandwidth that can

be reduced by connecting an external capacitor from the NR

node to the negative supply pin, V

. This capacitor limits the

EE

bandwidth and acts as a filter to reduce the noise contribution

from the reference amplifier.

The noise reduction capacitor, C

, is not required for stability

NR

and does not affect the settling time of the DAC output. Without this capacitor, the I

bandwidth is 15 MHz allowing

REFIN

high frequency modulation of the DAC full-scale range through

the reference input node. Figure 7 shows the relationship between the external noise reduction capacitor and the –3 dB

bandwidth of the reference amplifier.

Figure 7. External Noise Reduction Capacitor vs. –3 dB

Bandwidth

The sensitivity of the NR node requires that care be taken in

capacitor placement. The capacitor should be located as physically close to the package pins as possible and lead lengths

should be minimized. For this purpose, the use of a chip

capacitor is recommended. For applications that do not require

high frequency modulation at IREFIN, it is recommended that

a capacitor on the order of 1 µF be connected from NR to V

EE

.

If the reference input is purely dc, noise may be minimized with

multiple capacitors, such as 1 µF and 0.1 µF, to more effectively

filter both high and low frequency disturbances.

ANALOG OUTPUTS

The AD768 offers two analog outputs; IOUTA is trimmed for

optimal INL and DNL performance and has a full-scale output

when all bits are high. For applications that require the specified

dc accuracy, IOUTA should be used. IOUTB is the complementary output with full-scale output when all bits are low.

Both IOUTA and IOUTB provide similar dynamic performance. Refer to Figures 8 and 9 for typical INL and DNL performance curves. The outputs can also be used differentially.

Refer to the section “Applying the AD768” for examples of various output configurations.

Figure 8. Typical INL Performance

REV. B

–7–

Page 8

AD768

1

26

27

28

1kΩ 1kΩ

3pF 3pF

I

OUT

I

OUT

IREFIN

x2.75

V

EE

LADCOM IOUTB

IOUTA

8

6

4

2

0

–2

DNL ERROR – LSB

–4

–6

–8

06510 20 30 40

DIGITAL INPUT CODE – k

50 6051525354555

Figure 9. Typical DNL Performance

The outputs have a compliance range of –1.2 V to +5.0V with

respect to LADCOM. The current steering output stages will

remain functional over this range. Operation beyond the maximum compliance limits may cause either output stage saturation

or breakdown, resulting in nonlinear performance. The rated dc

and ac performance specifications are for an output voltage of

0 V to –1 V.

The current in LADCOM is proportional to I

and has been

REFIN

carefully configured to be independent of digital code when the

output is connected to a virtual ground. This minimizes any detrimental effects of ladder ground resistance on linearity. For

optimal dc linearity, IOUTA should be connected directly to a

virtual ground, and IOUTB should be grounded. An example of

this configuration is provided in the section “Buffered Voltage

Output.” If IOUTA is driving a resistive load directly, then

IOUTB should be terminated with an equal impedance. This

will ensure the current in LADCOM remains constant with digital code, and is recommended for improved dc linearity in the

unbuffered voltage output configuration.

As shown in Figure 10, there is an equivalent output impedance

of 1 kΩ in parallel with 3 pF at each output terminal. If the output voltage deviates from the ladder common voltage, an error

current flows through this 1 kΩ impedance. This is a linear effect

which does not change with input code, so it appears as a gain

error. With 50 Ω output termination, the resulting gain error is

approximately –5%. An example of this configuration is provided in the section Unbuffered Voltage Output.

Figure 10. Equivalent Analog Output Circuit

DIGITAL INPUTS

The AD768 digital inputs consist of 16 data input pins and a

clock pin. The 16-bit parallel data inputs follow standard positive binary coding, where DB15 is the most significant bit

(MSB) and DB0 is the least significant bit (LSB). IOUTA produces full-scale output current when all data bits are at logic 1.

IOUTB is the complementary output, with full-scale when all

data bits are at logic 0. The full-scale current is split between

the two outputs as a function of the input code.

The digital interface is implemented using an edge-triggered

master slave latch. The DAC output is updated following the

rising edge of the clock, and is designed to support a clock rate

as high as 40 MSPS. The clock can be operated at any duty

cycle that meets the specified minimum latch pulse width. The

setup and hold times can also be varied within the clock cycle as

long as the specified minimums are met, although the location

of these transition edges may affect digital feedthrough. The

digital inputs are CMOS compatible with logic thresholds set to

approximately half the positive supply voltage. The small input

current requirements allow for easy interfacing to unbuffered

CMOS logic. Figure 11 shows the equivalent digital input

circuit.

V

DIGITAL

INPUT

CC

V

EE

V

CC

DCOM

Figure 11. Equivalent Digital Input Circuit

Digital input signals to the DAC should be isolated from the

analog output as much as possible. Interconnect distances to the

DAC inputs should be kept as short as possible. Termination

resistors may improve performance if the digital lines become

too long. To minimize digital feedthrough, the inputs should be

free from glitches and ringing, and may be further improved

with a reduction of edge speed.

–8–

REV. B

Page 9

Typical Performance Curves––AD768

0.2

0.0

–0.2

–0.4

–0.6

–0.8

–1.0

VOLTS

TIME – 5ns/Div

RL = 50Ω

V

OUT

= 0 TO –1V

10k 2.0M1.0M

OUTPUT – dB

FREQUENCY – Hz

CLOCK = 10MHz

F

OUT

= 1.002MHz

AMPLITUDE = 0dBm

0

–20

–40

–60

–80

–100

AD768

–0.9405

–0.9415

–0.9424

–0.9433

–0.9443

–0.9453

–0.9462

OUTPUT – dB

–0.9472

–0.9481

–0.9498

–0.9500

12 24 3614 16 18 20 22 3426 28 30 32

TIME – ns

Figure 12. Settling Time

–80

–75

–70

–65

THD – dB

–60

–55

RL = 50Ω

V

= 0 TO –1V

OUT

RL = 50Ω

V

OUT

= 0 TO –1V

1.00

0.90

0.80

0.70

0.60

0.50

0.40

ERROR BAND – %

0.30

0.20

0.10

0.05

0.025

–0.470

RL = 50Ω

–0.472

–0.474

–0.476

OUTPUT – V

–0.478

–0.480

–0.482

TIME – 2ns/Div

V

OUT

= 0 TO –1V

Figure 13. Glitch Impulse at Major

Carry

0

CLOCK = 10MHz

F

= 1.002MHz

–20

–40

–60

OUTPUT – dB

–80

OUT

AMPLITUDE = 0dBm

OUTPUT IOUTB

R

= 50Ω

L

Figure 14. Rise and Fall

Characteristics

Figure 15. THD vs. Clock Frequency

at F

REV. B

–50

5678910 30

42040

= 1 MHz

OUT

–86

–82

–78

–74

–70

SFDR

–66

–62

–58

–54

–50

FREQUENCY – MHz

CLOCK = 10MHz

1

FREQUENCY – MHz

CLOCK = 30MHz

CLOCK = 20MHz

10

Figure 18. SFDR (Within a Window)

vs. F

OUT

–100

FREQUENCY – MHz

Figure 16. Typical Spectral

Performance

–80

–75

–70

–65

THD – dB

–60

–55

–50

0.01 0.1 10

CLOCK = 1MHz

CLOCK = 10MHz

CLOCK = 20MHz

CLOCK = 30MHz

CLOCK = 40MHz

FREQUENCY – MHz

1

Figure 19. THD vs. F

OUT

–9–

50.1 3241

Figure 17. Typical SFDR

(With a Window)

0

–20

–40

–60

OUTPUT – dB

–80

–100

150 350

190 230 270 310

FREQUENCY – Hz

CLOCK = 10 MHz

= 240 kHz

F

OUT1

= 260 kHz

F

OUT2

AMPLITUDE = –6.0 dB FS

PER TONE

OUTPUT IOUTB

= 50Ω

R

L

Figure 20. Intermodulation

Distortion

Page 10

AD768

1

27

28

AD768

R

FB

100Ω

IOUTA

LADCOM

IOUTB

A1

APPLYING THE AD768

OUTPUT CONFIGURATIONS

The following sections illustrate some typical output configurations for the AD768. While most figures take the output at

IOUTA, IOUTB can be interchanged in all cases. Unless otherwise noted, it is assumed that I

set to nominal values.

For application that require the specified dc accuracies, proper

resistor selection is required. In addition to absolute resistor tolerances, resistor self-heating can result in unexpected errors. For

optimal INL, the buffered voltage output is recommended as

shown in Figure 23. In this configuration, self-heating of R

may cause a change in gain, producing a bow in the INL curve.

This effect can be minimized by selection of a low temperature

coefficient resistor.

UNBUFFERED VOLTAGE OUTPUT CONFIGURATIONS

Figure 21 shows the AD768 configured to provide a unipolar

output range of approximately 0 V to –1V. The nominal fullscale current of 20 mA flows through the parallel combination

of the 50 Ω R

resistor and the 1 kΩ DAC output resistance

L

(from the R-2R ladder), for a combined 47.6 Ω. This produces

an ideal full-scale voltage of –0.952 V with respect to LADCOM.

In addition, the 1 kΩ DAC output resistance has a tolerance of

±20% which may vary the full-scale gain by ± 1%. This linear

variation results in a gain error which can be easily compensated

for by adjusting I

REFIN

AD768

LADCOM

.

IOUTA

IOUTB

1

28

27

Figure 21. 0 V to –1 V Unbuffered Voltage Output

In this configuration, it is important to note the restrictions from

the output compliance limits. The maximum negative voltage

compliance is –1.2 V, prohibiting use of a 100Ω load to produce

a 0 V to –2 V output swing. One additional consideration for

operation in this mode is integral nonlinearity. As the voltage at

the output node changes, the finite output impedance of the

DAC current steering switches gives rise to small changes in the

output current that vary with output voltage, producing a bow

(up to 8 LSBs) in the INL. For optimal INL performance, the

buffered voltage output mode is recommended.

The INL is also slightly dependent on the termination of the

unused output (IOUTB) as described in the ANALOG OUTPUT section. To eliminate this effect, IOUTB should be terminated with the same impedance as IOUTA, so both outputs see

the same resistive divider to ground. This will keep the current

in LADCOM constant, minimizing any code-dependent IR

drops within the DAC ladder that may give rise to additional

nonlinearities.

AC-Coupled Output

Configuring the output as shown in Figure 22 provides a bipolar

output signal from the AD768 without requiring the use of a

summing amplifier. The ac load impedance presented to the

and full-scale currents are

REFIN

R

L

49.9Ω

R

49.9Ω

VA

L

VB

FB

DAC output is the parallel combination of the AD768’s output

impedance, R

with the values given in Figure 22 is ± 0.5 V assuming R

, and bias resistor RB. The nominal output swing

L

>> RL.

B

The gain of the circuit will be a function of the tolerances of the

impedances R

Choosing the value of R

, RB, and RL.

LAD

and C will depend primarily on the

B

desired –3 dB high pass cutoff frequency and the bias current,

I

, of the subsequent stage connected to RB. The –3 dB fre-

B

quency can be approximated by the equation,

f

= 1/[2 × π × (RB + RLiR

–3 dB

LAD

) × C].

The dc offset of the output is a function of the bias current of

the subsequent stage and the value of R

C = 390 pF, R

= 20 kΩ, and IB = 1.0 µA, the –3 dB frequency

B

. For example, if

B

is approximately 20.4 kHz and the dc offset would be 20mV.

AD768

IOUTA

IOUTB

LADCOM

1

R

27

R

49.9Ω

28

L

49.9Ω

L

I

B

C

R

B

Figure 22. 0.5 V to –0.5 V Unbuffered AC-Coupled Output

BUFFERED VOLTAGE OUTPUT CONFIGURATIONS

Unipolar Configuration

For positive output voltages, or voltage ranges greater than

allowed by output compliance limits, some type of external

buffer is needed. A wide variety of amplifiers may be selected

based on considerations such as speed, accuracy and cost. The

AD9631 is an excellent choice when dynamic performance is

important, offering low distortion up to 10MHz. Figure 23

shows the implementation of 0 V to +2V full-scale unipolar

buffered voltage output. The amplifier establishes a summing

node at ground for the DAC output. The buffered output voltage results from the DAC output current flowing through the

amplifier’s feedback resistor, R

scale current across R

(100 Ω) produces an output voltage

FB

. In this case, the 20 mA full-

FB

range of 0 V through +2 V. The same configuration using a precision amplifier such as the AD845 is recommended for optimal

dc linearity.

Figure 23. Unipolar 0 V to +2 V Buffered Voltage Output

Buffered Output Using a Current Divider

The configuration shown in Figure 23 may not be possible in

cases where the amplifier cannot supply the requisite 20mA

feedback current. As an alternative, Figure 24 shows amplifier

A1 in conjunction with a resistive current divider. The values of

R

and RL are chosen to limit the current, I3, which must be

FF

supplied by A1. Current, I

tor, R

. The parallel combination of RFF and RL should not ex-

L

, is shunted to ground through resis-

2

ceed 60 Ω to avoid exceeding the specified compliance voltage.

–10–

REV. B

Page 11

AD768

1

27

28

AD768

R*

IOUTA

LADCOM

IOUTB

R

REF

*

I

REF

A1

R*

6

3

REFOUT

REFIN

V

OUT

V

OUT

= ±4 I

REF

R

WHERE I

REF

=

2.5V

R

REF

V

OUT

± 2V

R = 200Ω

R

REF

= 5 x 200Ω

*OHMTEK TDP-1403

For the values given in Figure 24, I3 equals 4 mA, which results

in a nominal unipolar output swing of 0 V to 2 V. Note, since

A1 has an inverting gain of approximately –4 and a noise gain of

+5, A1’s distortion and noise performance should be considered.

R

FB

500Ω

FF

A1

AD768

IOUTA

IOUTB

LADCOM

R

I

1

1

27

R

20Ω

28

I

3

100Ω

I

2

R

L

24.9Ω

P

Figure 24. 0 V to 2 V Buffered Unipolar Output Using a

Current Divider

Bipolar Configuration

Bipolar mode is accomplished by providing an offset current,

I

ting I

through R

, to the I/V amplifier’s (A1) summing junction. By set-

BIPOLAR

to exactly half the full-scale current flowing

BIPOLAR

, the resulting output voltage will be symmetrical

FB

about the summing junction voltage, typically ground. Figure 25

shows the implementation for a bipolar ± 2.5 V buffered voltage

output. The resistor divider sets the full-scale current for I

5 mA. The internal 2.5 V reference generates a 2.5mA I

current across R

. An output voltage of 0 V is produced when

BIP

to

DAC

BIPOLAR

the DAC is set to half scale (100. . .0) such that the 2.5mA current, I

, is exactly offset by I

DAC

. As the DAC is varied

BIPOLAR

from zero to full-scale, the output voltage swings from –2.5V to

+2.5 V. Note, in configurations that require more than 15mA

of total current from REFOUT, an external buffer is required.

Op amps such as the AD811, AD8001, and AD9631 are good

selections for superior dynamic performance. In dc applications,

op amps such as the AD845 or AD797 may be more appropriate.

R

AD768

REFOUT

IOUTA

IOUTB

LADCOM

3

1

27

28

R

20Ω

BIP

1kΩ

C

P

75Ω

24.9Ω

I

BIPOLAR

I

DAC

A1

R

1kΩ

FB

primary side is multiplied by a factor of 4 (i.e., in this case

200 Ω). To avoid dc current from flowing into the R-2R ladder

of the DAC, the center tap of the transformer should be connected to LADCOM.

In order to comply with the minimum voltage compliance of

–1.2 V, the maximum differential resistance seen between

IOUTA and IOUTB should not exceed 240 Ω. Note that the

differential resistance consists of the load R

, referred to the

L

primary side of the transformer in parallel with any added differential resistance, R

, across the two outputs. R

DIFF

is typically

DIFF

added to the primary side of the transformer to match the effective primary source impedance to the load (i.e., in this case

200 Ω).

AD768

IOUTA

1

R

IOUTB

LADCOM

DIFF

200Ω

27

28

4:1 IMPEDANCE

RATIO

T1

T1 = MINI-CIRCUITS T4-6T

R

50Ω

L

Figure 26. Differential Output Using a Transformer

DC COUPLING VIA AN AMPLIFIER

A dc differential to single-ended conversion can be easily accomplished using the circuit shown in Figure 27. This circuit

will attenuate both ac and dc common-mode error sources due

to the differential nature of the circuit. Thus, common-mode

noise (i.e., clock feedthrough) as well as dc unipolar offset errors

will be significantly reduced. Also, excellent temperature stability can be obtained by using temperature tracking, thin film

resistors for R and R

. The design equations for the circuit are

REF

provided such that the voltage output swing and IREF can be

optimized for a given application.

Figure 25. Bipolar ±2.5 V Buffered Voltage Output

DIFFERENTIAL OUTPUT CONFIGURATIONS

AC Coupling via a Transformer

Applications that do not require baseband operation typically

use transformer coupling. Transformer coupling the complementary outputs of the AD768 to a load has the inherent benefit

of providing electrical isolation while consuming no additional

power. Also, a properly applied transformer should not degrade

the AD768’s output signal with respect to noise and distortion,

since the transformer is a passive device. Figure 26 shows a

center-tapped output transformer that provides the necessary dc

load conditions at the outputs IOUTA and IOUTB to drive a

±0.5 V signal into a 50 Ω load. In this particular circuit, the cen-

ter-tapped transformer has an impedance ratio of 4 that corresponds to a turns ratio of 2. Hence, any load, R

REV. B

, referred to the

L

Figure 27. DC Differential to Single-Ended Conversion

POWER AND GROUNDING CONSIDERATIONS

In systems seeking to simultaneously achieve high speed and

high accuracy, the implementation and construction of the

printed circuit board design is often as important as the circuit

design. Proper RF techniques must be used in device selection,

placement and routing, and supply bypassing and grounding.

Maintaining low noise on power supplies and ground is critical

to obtaining optimum results from the AD768. Figure 28 provides an illustration of the recommended printed circuit board

ground plane layout which is implemented on the AD768 evaluation board.

–11–

Page 12

AD768

Figure 28. Printed Circuit Board Ground Plane Layout

Figure 29. Printed Circuit Board Power Plane Layout

–12–

REV. B

Page 13

AD768

6

3

AD768

R

REF

625Ω

IREFIN

REFOUT

1µF

R

REFMOD

VMOD

VMOD

R

REFMOD

≤ ±3.0mA

FREQUENCY – kHz

THD – dB

–75

–40

250 2500500 750 1000 1250 1500 1750 2000 2250

–70

–60

–55

–50

–45

–65

I

REF

= 4.0+/–3 mA

I

REF

= 4.0+/–2 mA

I

REF

= 5.0+/–1 mA

If properly implemented, ground planes can perform a host of

functions on high speed circuit boards: bypassing, shielding,

current transport, etc. In mixed signal design, the analog and

digital portions of the board should be distinct from each other,

with the analog ground plane confined to the areas covering

analog signal traces and the digital ground plane confined to

areas covering the digital interconnects.

All analog ground pins of the DAC, reference, and other analog

output components, should be tied directly to the analog ground

plane. The two ground planes should be connected by a path

1/4 to 1/2 inch wide underneath or within 1/2 inch of the DAC

as shown in Figure 28. Care should be taken to ensure that the

ground plane is uninterrupted over crucial signal paths. On the

digital side, this includes the digital input lines running to the

DAC as well as any clock signals. On the analog side, this includes the DAC output signal, reference signal, and the supply

feeders.

The use of wide runs or planes in the routing of power lines is

also recommended. This serves the dual role of providing a low

series impedance power supply to the part, as well as, providing

some “free” capacitive decoupling to the appropriate ground

plane. Figure 29 illustrates the power plane layout used in the

AD768 evaluation board. The AD768 evaluation board uses a

four layer P.C. board which illustrates good layout practices as

discussed above.

It is essential that care be taken in the layout of signal and

power ground interconnects to avoid inducing extraneous voltage drops in the signal ground paths. It is recommended that all

connections be short, direct and as physically close to the package as possible, in order to minimize the sharing of conduction

paths between different currents. When runs exceed an inch in

length, some type of termination resistor should be considered.

The necessity and value of this resistor will be dependent upon

the logic family used.

For maximum ac performance, the DAC should be mounted

directly to the circuit board; sockets should be avoided since

they introduce unwanted capacitive coupling between adjacent

pins of the device.

A clean digital supply may be generated using the circuit shown

in Figure 30. The circuit consists of a differential LC filter with

separate power supply and return lines. Lower noise can be attained using low ESR (Equivalent Series Resistance) type electrolytic and tantalum capacitors.

TTL/CMOS

LOGIC

CIRCUITS

+5V DGND

+5V

POWER SUPPLY

FERRITE

BEADS

100µF

ELECT.

10–20µF

TANT.

0.1µF

CER.

V

DD

DCOM

Figure 30. Differential LC Filter for Single +5 V

Applications

APPLICATIONS

USING THE AD768 AS A MULTIPLYING DAC

The AD768 can be easily configured as a multiplying DAC

since I

can be modulated from 1 mA to 7 mA. The refer-

REFIN

ence amplifier sets the maximum multiplying bandwidth to 15

MHz, while any external capacitor to the NR node serves to

limit the bandwidth according to Figure 7. I

can be easily

REFIN

modulated by properly scaling and summing into the IREFIN

node the modulating signal. Figure 31 demonstrates how the

modulating signal VMOD can be properly scaled and converted

to a current via R

such that its peak current does not ex-

REFMOD

ceed 3.0 mA. Figure 32 shows the AD768’s typical distortion

versus the reference channel frequency.

POWER SUPPLY AND DECOUPLING

One of the most important external components associated with

high speed designs are the capacitors used to bypass the power

supplies. Both selection and placement of these capacitors can

be critical and, to a large extent, dependent upon the specifics of

the system configuration. The dominant consideration in the

selection of bypass capacitors for the AD768 is the minimization

of the series resistance and inductance. Many capacitors will

begin to look inductive at 20 MHz and above. Ceramic and film

type capacitors generally feature lower series inductance than

tantalum or electrolytic types.

It is recommended that each power supply to the AD768 be decoupled by a 0.1 µF capacitor located as close to the device pins

as possible. Surface-mount chip capacitors, by virtue of their

low parasitic inductance, are preferable to through-hole types.

Some series inductance between the DAC supply pins and the

power supply plane may help to provide additional filtering of

high frequency power supply noise. This inductance can be generated by using small ferrite beads.

REV. B

Figure 31. Typical Multiplying DAC Application

Figure 32. Reference Channel Distortion vs. Frequency

–13–

Page 14

AD768

AD768 IN MULTITONE TRANSMITTERS (FOR ADSL)

Communications applications frequently require aspects of

component performance that differ significantly from the

simple, single tone signals used in typical SNR and THD tests.

This is particularly true for spread-spectrum and frequency division multiplexed (FDM) type signals, where information content is held in a number of small signal components spread

across the frequency band. In these applications, a combination

of wide dynamic range, good fine-scale linearity, and low intermodulation distortion is required. Unfortunately, a part’s full

scale SNR and THD performance may not be a reliable indicator of how it will perform in these multitone applications.

One example of an FDM communications system is the DMT

(discrete multitone) ADSL (Asymmetrical Digital Subscriber

Line) standard currently being considered by ANSI. Figure 33

shows a block diagram of a transmitter function.

The digital bits are used to QAM modulate each of approximately 200 discrete tones. An inverse FFT turns this modulated frequency domain information into 512 time points at a

2.2 MSPS sample rate. These time points are then put through

an FIR interpolation filter to upsample (in this case to 4.4 MSPS).

The bit stream is run through the AD768, which is followed by

a 4th order analog smoothing filter, then run to the line-driving

circuitry

BIT

STREAM

QAM

ENCODER

AD768

+BUFFER

256

MODULATED

FREQUENCY

BINS

INVERSE

FFT

4TH ORDER

SMOOTHING

FILTER

512 TIME

POINTS

@ 2.2MSPS

2X

INTERPOLATOR

FIR

TO

TRANSMITTER

1024 TIME

POINTS

@ 4.4MSPS

Figure 33. Typical DMT ADSL Transmit Chain

Figure 34a shows a frequency domain representation of a test

vector run through this system, while 34b shows the time domain representation. (Clearly the frequency domain picture is

more informative.) We wish to optimize the SINAD of each

4 kHz frequency band: this is a function of both noise

(wideband and quantization) and distortion (simple harmonic

and intermod).

0

1.5

1.0

0.5

0

OUTPUT – Volts

–0.5

–1.0

–1.5

TIME – 25µs/DIV

Figure 34b. Time Domain Output Signal of ADSL Test

Vector

Table I and II show the available SNR and THD at the output

of the filter vs. frequency bin for the ADSL application. The

AD768’s combination of 16-bit dynamic range and 14-bit linearity provides excellent performance for the DMT signal. Its

fast input rate would support even faster rates of oversampling,

if one were interested in trading off digital filter complexity in

the interpolator for a simplified analog filter.

Table I. SNR vs. Frequency

Frequency SNR

151 kHz 70.1 dB

349 kHz 69.7 dB

500 kHz 69.4 dB

1 MHz 69.8 dB

Table II. THD vs. Frequency

Frequency THD

160 kHz –68.9 dBc

418 kHz –64.0 dBc

640 kHz –64.3 dBc

893 kHz –63.8 dBc

–20

–40

–60

OUTPUT – dB

–80

0

FREQUENCY – Hz

1.1M

Figure 34a. Output Spectrum of ADSL Test Vector

–14–

REV. B

Page 15

AD768

AD768 EVALUATION BOARD

GENERAL DESCRIPTION

The AD768-EB is an evaluation board for the AD768 16-bit

30 Msps D/A converter. Careful attention to layout and circuit

design combined with analog and digital prototyping areas allows the user to easily and effectively evaluate the AD768 in any

application where high resolution, high speed conversion is

required.

The digital inputs to the AD768-EB may be driven directly using the standard 40-pin IDC connector. An external clock is

also required. These signals may be applied from a user’s

bench, or they can be generated from a circuit built on the

prototyping area. The analog outputs from the AD768-EB are

available on BNC connectors. These outputs may be configured

to use either resistors, op amps, or a transformer.

OPERATING PROCEDURE AND FUNCTIONAL

DESCRIPTION

Power

Power may be supplied to the AD768-EB by applying either

wires or banana plugs to the metal binding posts included on the

printed circuit board.

DGND. Digital Ground. The digital ground and the analog

ground are connected together underneath the AD768. Optimal

performance can be obtained with separate analog and digital

supplies. For evaluation purposes, a single-supply which makes

a second analog and digital ground connection at the supply is

acceptable.

+5D. The +5 V (±5%) digital supply should be capable of sup-

plying 50 mA.

–5A. The –5 V (±5%) analog supply should be capable of sup-

plying –75 mA.

AGND. Analog ground. The analog ground and the digital

ground are connected together underneath the AD768. Optimal

performance can be obtained with separate analog and digital

supplies. For evaluation purposes, a single-supply which makes

a second analog and digital ground connection at the supply is

acceptable.

–V

. Negative analog supply; typically –5 V to –15 V. This

EE

supply is used as the negative supply rail for the external op

amps. For the AD811 supplied with the AD768-EB, a supply

capable of supplying –20 mA (excluding external load requirements) is required.

+V

. Positive analog supply; typically +5 V to +15V. This

CC

supply is used as the positive supply rail for the external op

amps. For the AD811 supplied with the AD768-EB, a supply

capable of supplying +20 mA (excluding external load requirements) is required.

Analog Outputs

The analog output(s) from the AD768-EB are available on BNC

jacks “A” and “B.” The complementary current outputs from

the AD768 can be configured using either resistors, op amps, or

a transformer. Only the “A” portion of the AD768-EB is populated and shipped from the factory. The “B” side, or complementary output, may be populated by the user if so desired.

JP1. Buffered op amp output “A”. Jumper JP1 should be

installed if the buffered op amp output is desired. When JP1

is installed, JP2 and JP3 must be removed for proper

operation. The output, available on the “A” connector, has a

nominal voltage swing of 0 V to 2 V and is in-phase with the

digital input. This is the factory default setting.

JP2. Bipolar 50 Ω transformer output. If jumper JP2 is in-

stalled, a transformer coupled output is available on the “A”

connector. When JP2 is installed, JP1 and JP3 must be re-

moved for proper operation. The transformer acts both as a

differential-to-single-ended converter and as an impedance

transformer. For proper operation, the transformer must be

terminated with a 50 Ω resistor. R2 must be replaced with

the 100 Ω resistor, R7. An additional 100 Ω resistor and the

transformer are included with the AD768-EB. The additional

100 Ω resistor must be soldered into the appropriate position labeled “R3” and the transformer must be inserted into the

socket labeled “T1.” The nominal output voltage into a 50Ω

load is 1 V

p-p centered on a common-mode voltage of 0V.

JP3. Resistor output “A.” JP3 is used to connect the resistor

R2 to the “A” output. U2 should be removed from its socket.

Using a 24.9 Ω resistor for R2, the output is an unbuffered 0V

to –0.5 V output that is out of phase with the digital input. Resistor R2 may be replaced with other values, but careful attention to the recommended output compliance range should be

observed. When JP3 is installed, JP1 and JP2 must be re-

moved for proper operation.

JP4. Resistor output “B.” JP4 is used to connect the resistor

R3 to the “A” output. U3 should be removed from its socket.

The AD768-EB is shipped from the factory with resistor R3

shorted to ground. A different value selected by the user can be

installed for R3 to generate an unbuffered output that is inphase with the digital input. Careful attention to the recommended output compliance range should be observed when

selecting the value of R3. When JP4 is installed, JP5 must

be removed for proper operation.

JP5. Buffered op amp output “B.” Jumper JP5 should be in-

stalled if the buffered op amp output is desired. When JP5 is

installed, JP4 must be removed for proper operation.

The output is available on the “B” connector and has a nominal

voltage swing determined by the combination of resistors R3,

R9, and R10. This op amp is not provided with the AD768-EB.

Reference

Either the internal reference of the AD768 or an external reference may be selected on the AD768-EB. R12 is used to adjust

the full-scale output current of the AD768.

SW2. Internal/External reference select switch. When SW2 is

in position 1, the internal reference of the AD768 is selected.

When SW2 is in position 2, an external reference must be provided by the user.

Level-Shifting the Analog Output

Resistor sockets R8 and R6 can be populated with an appropriately valued resistor to add dc offset current to an output which

uses the op amp configuration. As an example, to generate a

bipolar output signal, a 1.25 kΩ resistor installed into the “R8”

socket level-shifts the normally unipolar output by –1V. The

factory defaults for R8 and R6 are open circuits.

REV. B

–15–

Page 16

AD768

Clock Input

An external sample clock must be provided to either the BNC

connector labeled “CLOCK” or on Pin 33 of the IDC connector. This clock must comply with the logic levels outlined in the

AD768 data sheet. The “CLOCK” input is terminated with a

removable 51 Ω resistor. The IDC connector clock connection

is unterminated.

SW1. Clock source select switch. When SW1 is in position 1, Pin

33 of the IDC connected is applied to the CLOCK input of the

AD768. When SW2 is in position 2, the “CLOCK” BNC connector is applied to the CLOCK input of the AD768.

Digital Inputs

The digital inputs of the AD768, DB0–DB15, are available via

J1, a 40-pin IDC connector. These inputs should comply with

the specifications given in the AD768 data sheet.

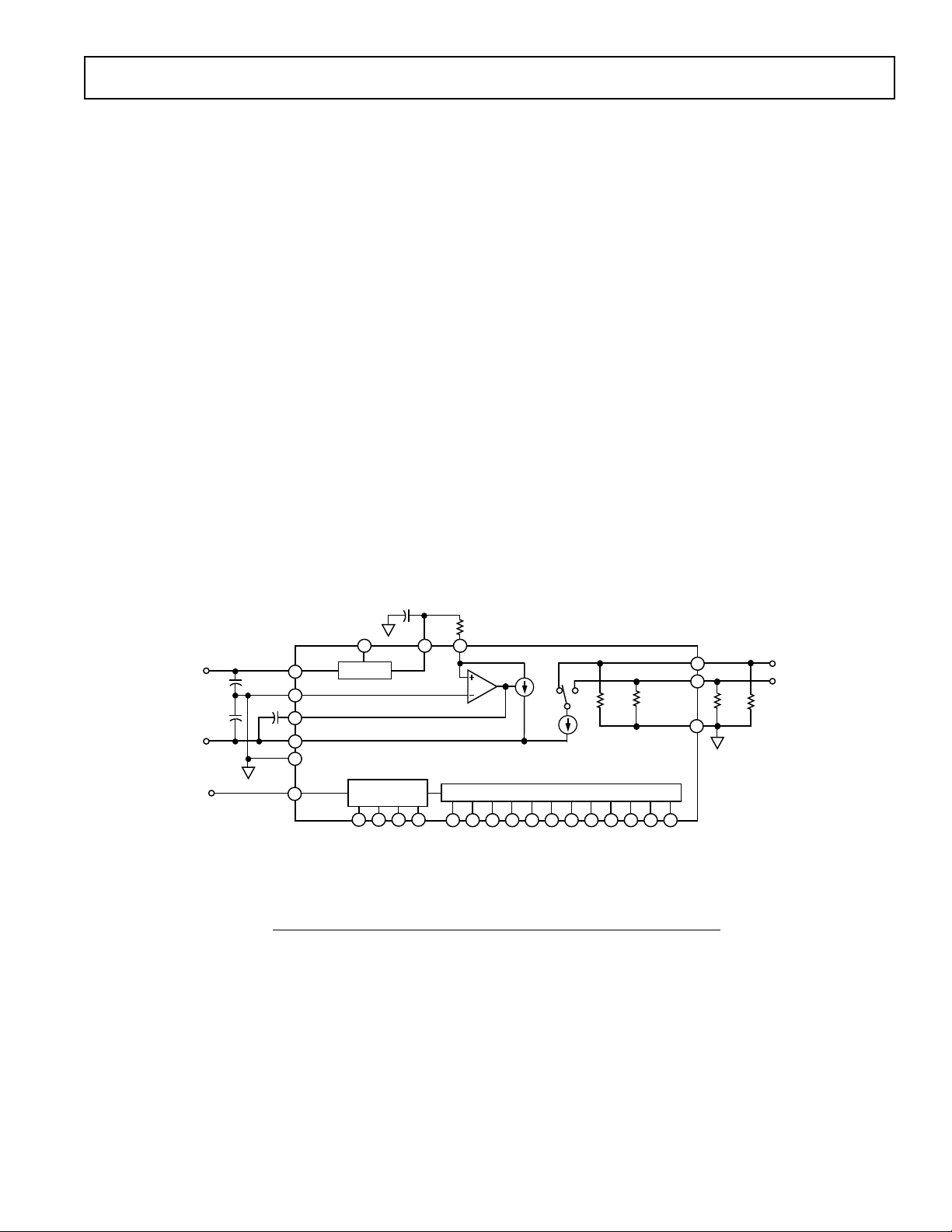

Layout Considerations

Figures 28 and 29 show the AD768-EB ground and power

plane layouts. Figures 35–38 show the schematic diagram, trace

routing, silk screening, and component layout for the AD768 4

layer evaluation board.

Separate ground and power planes have several advantages for

high speed layouts. (For further information outlining these

advantages, see the application note “Design and Layout of a

Video Graphics System for Reduced EMI” [E1309] available

from Analog Devices [(617) 461-3392].) A solid ground plane

can be used if the digital return current can be routed such that

it does not modulate the analog ground plane. If this is not possible, it may be necessary to split the ground plane in order to

force currents to flow in a controlled direction. This type of

grounding scheme is shown in the Figure 28. The ground plane

is separated into analog and digital planes that are joined

together under the AD768. In any case, the AD768 should be

treated as an analog component and a common ground connection should be made underneath the AD768 despite some pins

being labeled “digital” ground and some as “analog” ground.

A complete parts list for the AD768 evaluation board is given in

Table IV.

Table III. Summary of Jumper Functionality

Installed Jumper Function

Jumper

JP1 Buffered Output A

JP2 50 Ω Transformer Output

JP3 (STBY) Unbuffered Output A

JP4 Unbuffered Output B

JP5 Buffered Output B

Table IV. AD768-EB Parts List

Reference Value / Part Type Package Qty/Bd

U1 AD768 28-Pin SOIC 1

U2 AD811 8-Pin DIP 1

T1 Mini-Circuits Not Installed 1

T4–6T

A, B, CLOCK BNC JACKs, Small, Vertical 3

Small

JP1–5 Header 2-Pin 5

SW1, 2 SPDT, Secme 0.1" × 0.3" 2

J1 40-Pin IDC R.A., Male, 1

Connector w/ Latches

R1 500 Ω 1/4 W, 0.01%, 1

Vishay

R2 25 Ω 1/4 W, 0.01%, 1

Vishay

R3, R13–21, &

R23–29 Wire Jumpers 17

R5 500 Ω 1/4 W, 0.01%, 1

Vishay

R7 100 Ω 1/4 W, 0.01%, 1

Vishay

R11 51 Ω 1/8 W, 5%, Carbon 1

R12 10 kΩ Pot. 3266 W 1

C1–4 1µF Ceram. Cap. Leaded 4

C5–8, C10, 12, 0.1 µF Chip Cap,

14, & C16–19 1206 11

C9, 11, 13, 15 22 µF Tant. Cap., Teardrop, 4

25 V 0.1" Spacing

–16–

REV. B

Page 17

AD768

TP1

R5

499

+V

CC

C5

0.1µF

U2

7

2

AD811

3

4

A

–V

EE

R7

100

R8

∞

R12

10k

SW2

J1

J1

J1

J1

J1

J1

J1

J1

R13

31

R14

29

R15

27

R16

25

R17

23

R18

21

R19

19

R20

17

A

R1

499

C1

1µF

1

2

0

0

0

0

0

0

0

0

1µF

A

C2

A

6

C6

0.1µF

A A

C18

0.1µF

1

IOUTA

2

NR

3

REFOUT

4

NC

5

REFCOM

6

IREFIN

7

DB0 (LSB)

8

DB1

9

DB2

10

DB3

11

DB4

12

DB5

13

DB6

14

DB7

50

T1

3

1

4:1

45 6

R2

24.9

R3

24.9

A

U1

AD768

LADCOM

IOUTB

(–5V) V

(+5V) V

(MSB) DB15

CLOCK

DCOM

AB

22

JP1

JP2

JP3

JP4

28

27

26

EE

25

DD

24

23

DB14

22

DB13

21

DB12

20

DB11

19

DB10

18

DB9

17

DB8

16

15

11

R9

100

C3

1µF

A

C4

1µF

C17

0.1µF

C19

0.1µF

U3

AD811

R10

499

+V

–V

R21

R23

R24

R25

R26

R27

R28

R29

50

CC

C7

0.1µF

7

A

6

C8

4

0.1µF

EE

A

–V

C10

0.1µF

C12

A

0.1µF

C14

0.1µF

A

C16

0.1µF

0

0

0

0

0

0

0

0

EE

+V

CC

–5A

+5D

J1

1

J1

3

J1

5

J1

7

J1

9

J1

11

J1

13

J1

15

JP5

2

3

A

C9

47µF, 25V

R6

∞

C11

47µF, 25V

C13

47µF, 25V

C15

47µF, 25V

33

J1

CLOCK

1

2

R11

50

SW1

1

2

J1

2

J1

4

J1

6

J1

8

J1

10

J1

12

J1

14

16

J1

J1

18

J1

20

J1

22

J1

24

J1

26

J1

28

30

J1

J1

32

J1

34

J1

36

J1

38

J1

40

AGND CONNECTED TO DGND

ON GND PLANE UNDER U1

IN BETWEEN PINS 5 AND 25

A

DGND

AGND

Figure 35. AD768 Evaluation Board Schematic

REV. B

–17–

Page 18

AD768

Figure 36. Silkscreen Layer (Not to Scale)

–18–

REV. B

Page 19

AD768

Figure 37. Component Side PCB Layout (Not to Scale)

REV. B

Figure 38. Solder Side PCB Layout (Not to Scale)

–19–

Page 20

AD768

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

R-28

300 Mil 28-Pin SOIC

0.7125 (18.10)

0.6969 (17.70)

28 15

PIN 1

0.0500

0.0118 (0.30)

0.0040 (0.10)

(1.27)

BSC

0.0192 (0.49)

0.0138 (0.35)

141

0.1043 (2.65)

0.0926 (2.35)

SEATING

PLANE

0.2992 (7.60)

0.2914 (7.40)

0.4193 (10.65)

0.3937 (10.00)

0.0125 (0.32)

0.0091 (0.23)

0.0291 (0.74)

0.0098 (0.25)

0.0500 (1.27)

8°

0°

0.0157 (0.40)

C1941a–5–6/96

x 45°

–20–

PRINTED IN U.S.A.

REV. B

Loading...

Loading...