Page 1

16-Bit, 250 kSPS, Unipolar/Bipolar

P

VCCV

FEATURES

Multiple pins/software programmable input ranges:

5 V, 1 0 V, ± 5 V, ±1 0 V

Pins or serial SPI®-compatible input ranges/mode selection

Throughput: 250 kSPS

16-bit resolution with no missing codes

INL: ±0.75 LSB typ, ±1.5 LSB max (±23 ppm of FSR)

SNR: 94 dB @ 2 kHz

iCMOS® process technology

5 V internal reference: typical drift 3 ppm/°C;

On-chip temperature sensor

No pipeline delay (SAR architecture)

Parallel (16- or 8-bit bus) and serial 5 V/3.3 V interface

SPI-/QSPI™-/MICROWIRE™-/DSP-compatible

Power dissipation

90 mW @ 250 kSPS

10 mW @ 1 kSPS

48-lead LQFP and LFCSP (7 mm × 7 mm) packages

APPLICATIONS

Process control

Medical instruments

High speed data acquisition

Digital signal processing

Instrumentation

Spectrum analysis

AT E

Programmable Input PulSAR® ADC

AD7610

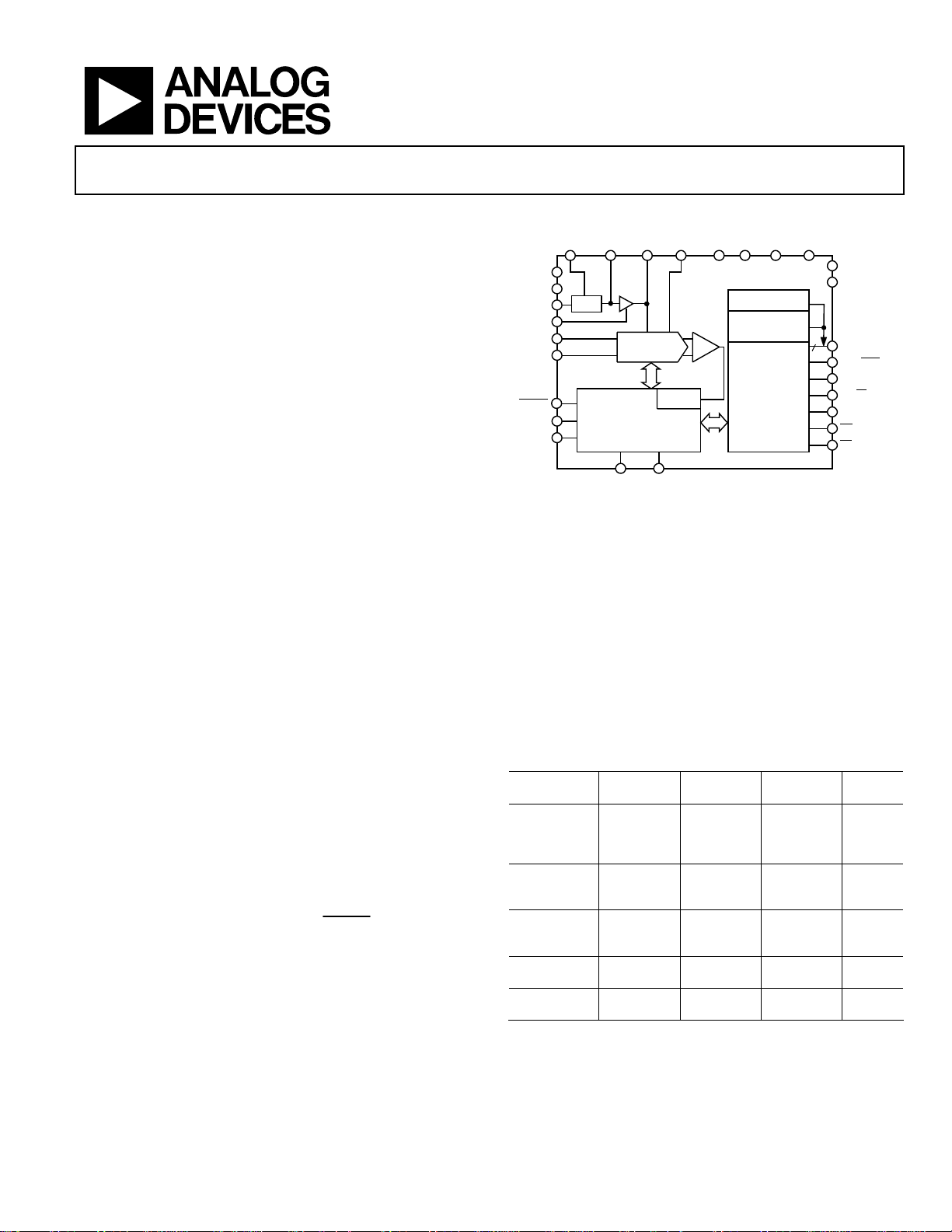

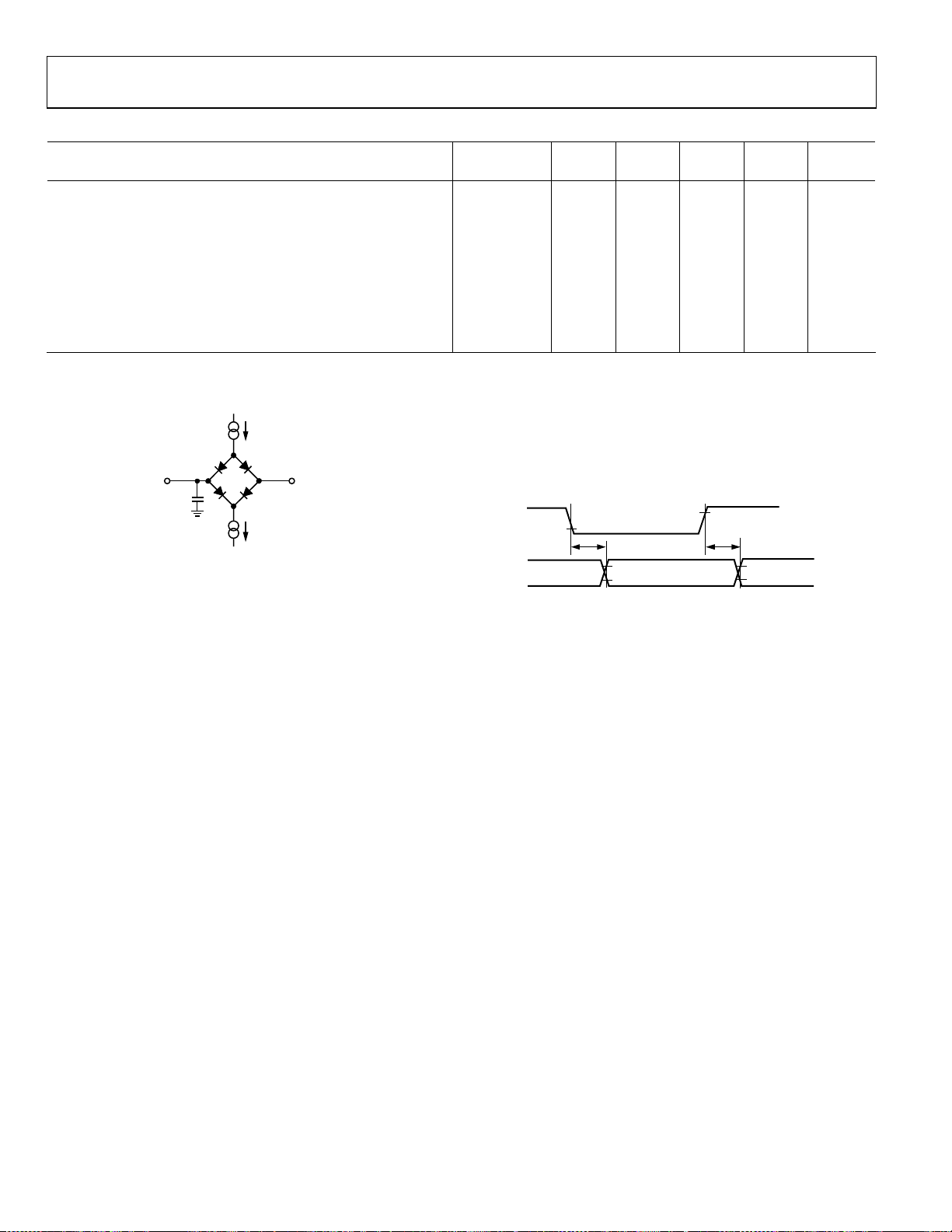

FUNCTIONAL BLOCK DIAGRAM

AGND

AVDD

PDREF

PDBUF

IN+

IN–

CNVST

PD

RESET

REFBUFI N

TEM

REF

AMP

REF

SWITCHED

CAP DAC

CONTROL LOG IC AND

CALIBRATION CIRCUIT RY

BIPOLAR TEN

REF REFGND

CLOCK

Figure 1.

EE

AD7610

DATAPORT

CONFIG URATIO N

PARALLEL

INTERF ACE

SERIAL

SERIAL

PORT

DGNDDVDD

OVDD

OGND

16

D[15:0]

SER/PAR

BYTESWAP

OB/2C

BUSY

RD

CS

06395-001

GENERAL DESCRIPTION

The AD7610 is a 16-bit charge redistribution successive approximation register (SAR), architecture analog-to-digital converter

(ADC) fabricated on Analog Devices, Inc.’s iCMOS high voltage

process. The device is configured through hardware or via a

dedicated write only serial configuration port for input range

and operating mode. The AD7610 contains a high speed 16-bit

sampling ADC, an internal conversion clock, an internal reference

(and buffer), error correction circuits, and both serial and parallel

system interface ports. A falling edge on

analog input on IN+ with respect to a ground sense, IN−. The

AD7610 features four different analog input ranges: 0 V to 5 V, 0 V

to 1 0 V, ±5 V, a nd ±1 0 V. Po we r co n su m pt i on i s s ca l e d l i ne a rl y

with throughput. The device is available in Pb-free 48-lead, lowprofile quad flat package (LQFP) and a lead frame chip-scale

(LFCSP_VQ) package. Operation is specified from −40°C to

+85°C.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

CNVST

samples the

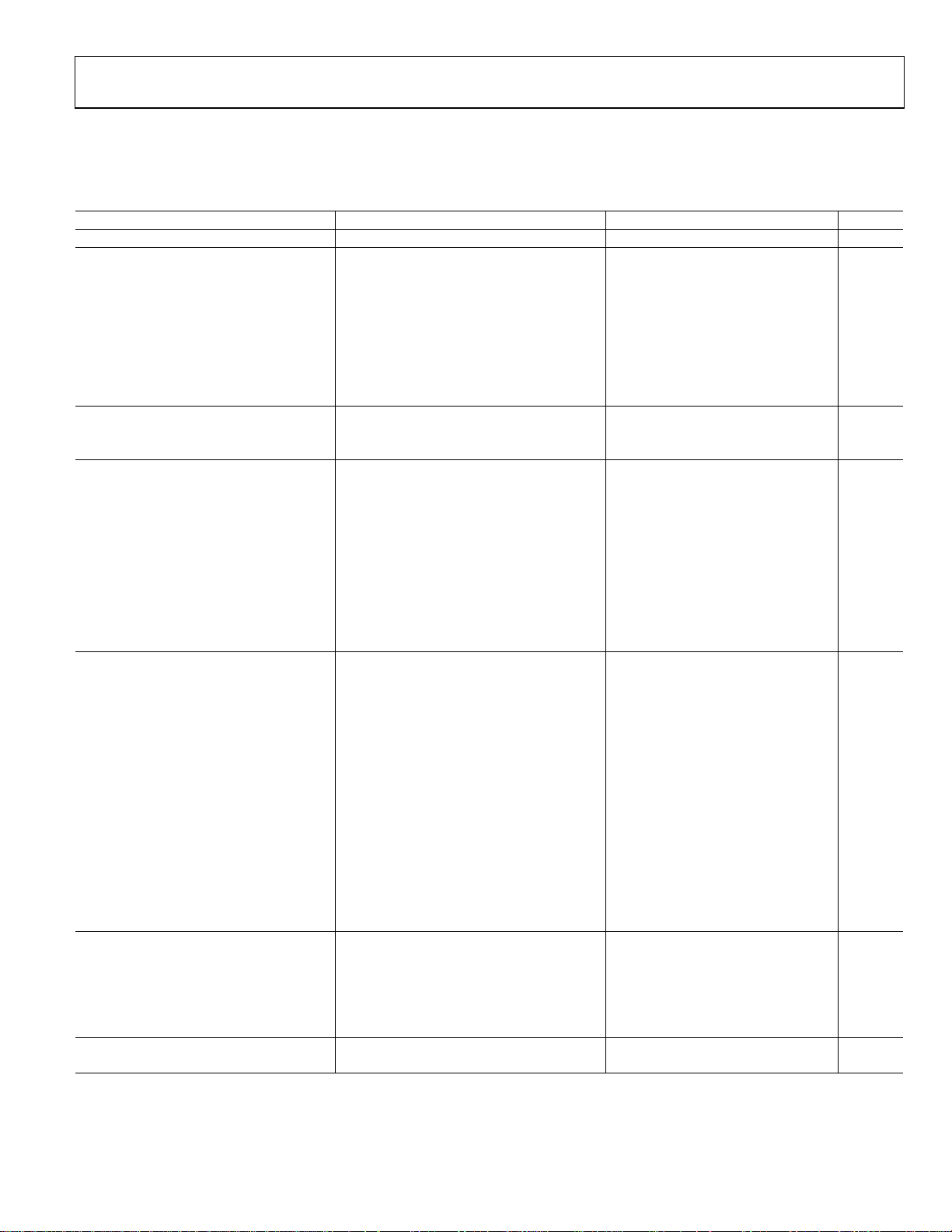

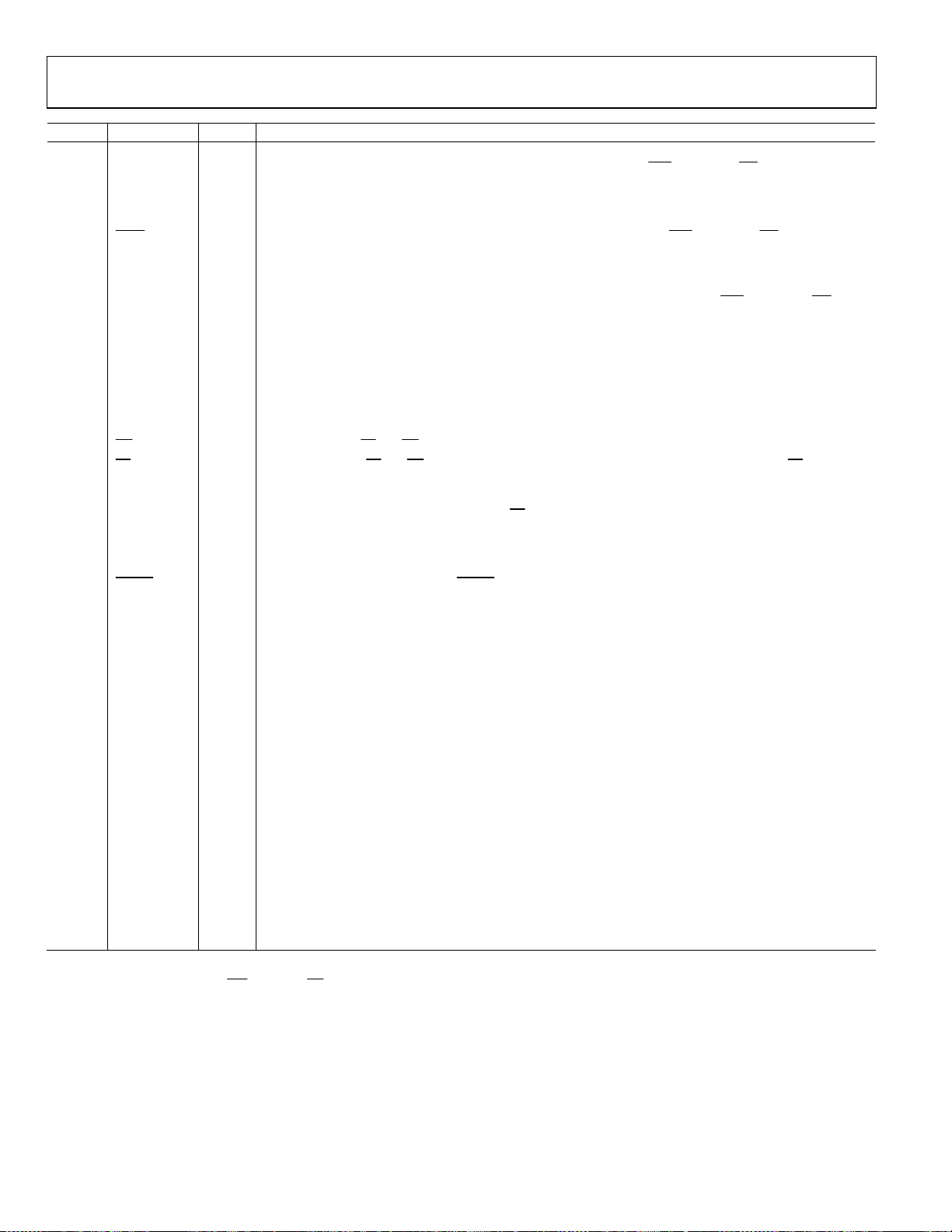

Table 1. 48-Lead 14-/16-/18-Bit PulSAR Selection

100 kSPS to

Type

Pseudo

Differential

True Bipolar AD7610

True

Differential

18-Bit, True

Differential

Multichannel/

Simultaneous

250 kSPS

AD7651

AD7660

AD7661

AD7663

AD7675 AD7676 AD7677 AD7621

AD7678 AD7679 AD7674 AD7641

AD7654

500 kSPS to

570 kSPS

AD7650

AD7652

AD7664

AD7666

AD7665 AD7612

AD7655

800 kSPS to

1000 kSPS

AD7653

AD7667

AD7671

AD7951

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

>1000

kSPS

AD7622

AD7623

AD7643

Page 2

AD7610

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram ..............................................................1

General Description......................................................................... 1

Revision History ...............................................................................2

Specifications..................................................................................... 3

Timing Specifications ..................................................................5

Absolute Maximum Ratings............................................................ 7

ESD Caution.................................................................................. 7

Pin Configuration and Function Descriptions............................. 8

Typical Performance Characteristics........................................... 11

Terminology.................................................................................... 15

Theory of Operation ......................................................................16

Overview...................................................................................... 16

Converter Operation.................................................................. 16

Transfer Functions......................................................................17

Typical Connection Diagram ...................................................18

Analog Inputs..............................................................................19

Driver Amplifier Choice ........................................................... 20

Voltage Reference Input/Output ..............................................20

Power Supplies............................................................................ 21

Conversion Control................................................................... 22

Interfaces.......................................................................................... 23

Digital Interface.......................................................................... 23

Parallel Interface......................................................................... 23

Serial Interface............................................................................ 24

Master Serial Interface............................................................... 24

Slave Serial Interface.................................................................. 26

Hardware Configuration........................................................... 28

Software Configuration............................................................. 28

Microprocessor Interfacing....................................................... 29

Application Information................................................................ 30

Layout Guidelines....................................................................... 30

Evaluating Performance ............................................................ 30

Outline Dimensions....................................................................... 31

Ordering Guide .......................................................................... 31

REVISION HISTORY

10/06—Revision 0: Initial Version

Rev. 0 | Page 2 of 32

Page 3

AD7610

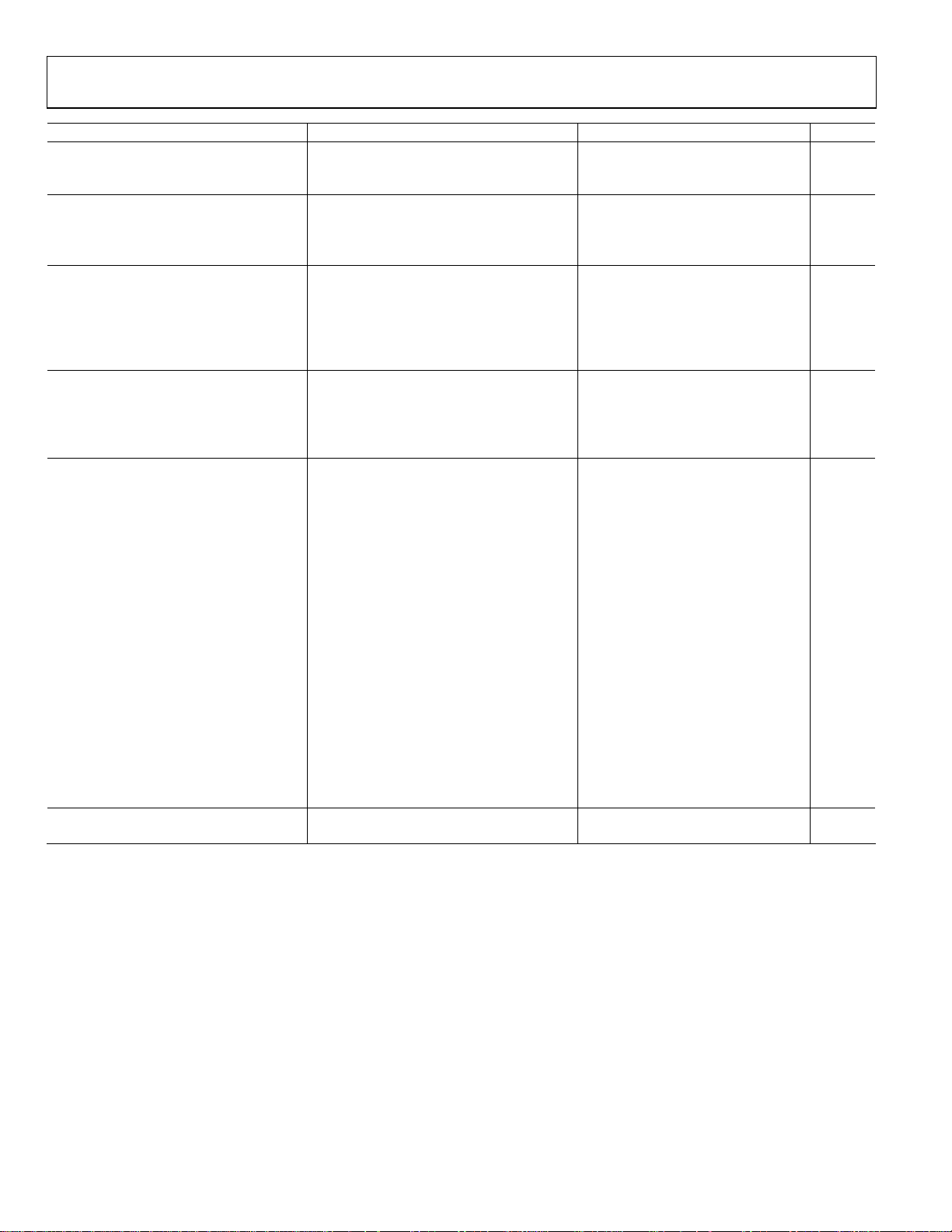

SPECIFICATIONS

AVDD = DVDD = 5 V; OVDD = 2.7 V to 5.5 V; VCC = 15 V; VEE = −15 V; V

Table 2.

Parameter Conditions/Comments Min Typ Max Unit

RESOLUTION 16 Bits

ANALOG INPUT

Voltage Range, VIN V

V

V

V

V

Analog Input CMRR fIN = 100 kHz 75 dB

Input Current V

Input Impedance

THROUGHPUT SPEED

Complete Cycle 4 s

Throughput Rate 250 kSPS

DC ACCURACY

Integral Linearity Error

No Missing Codes

Differential Linearity Error

2

2

2

Transition Noise 0.55 LSB

Zero Error (Unipolar or Bipolar) −35 +35 LSB

Zero Error Temperature Drift ±1 ppm/°C

Bipolar Full-Scale Error −50 +50 LSB

Unipolar Full-Scale Error −70 +70 LSB

Full-Scale Error Temperature Drift ±1 ppm/°C

Power Supply Sensitivity AVDD = 5 V ± 5% 3 LSB

AC ACCURACY

Dynamic Range VIN = 0 V to 5 V, fIN = 2 kHz, −60 dB 92.5 93.5 dB

V

V

Signal-to-Noise Ratio VIN = 0 V to 5 V, 0 V to 10 V, fIN = 2 kHz 92 93 dB

V

V

Signal-to-(Noise + Distortion) (SINAD) VIN = ±5 V, fIN = 2 kHz 92.5 dB

V

V

Total Harmonic Distortion fIN = 2 kHz −107 dB

Spurious-Free Dynamic Range fIN = 2 kHz 107 dB

–3 dB Input Bandwidth VIN = 0 V to 5 V 650 kHz

Aperture Delay 2 ns

Aperture Jitter 5 ps rms

Transient Response Full-scale step 500 ns

INTERNAL REFERENCE PDREF = PDBUF = low

Output Voltage REF @ 25°C 4.965 5.000 5.035 V

Temperature Drift –40°C to +85°C ±3 ppm/°C

Line Regulation AVDD = 5 V ± 5% ±15 ppm/V

Long-Term Drift 1000 hours 50 ppm

Turn-On Settling Time C

REFERENCE BUFFER PDREF = high

REFBUFIN Input Voltage Range 2.4 2.5 2.6 V

− V

= 0 V to 5 V −0.1 +5.1 V

IN+

IN−

− V

= 0 V to 10 V −0.1 +10.1 V

IN+

IN−

− V

= ±5 V −5.1 +5.1 V

IN+

IN−

− V

= ±10 V −10.1 +10.1 V

IN+

IN−

to AGND −0.1 +0.1 V

IN−

= ±5 V, ±10 V @ 250 kSPS 100

IN

Analog Inputs section

See

−1.5 ±0.75 +1.5 LSB

16 Bits

−1 +1.5 LSB

= 0 V to 10 V, ±5 V, fIN = 2 kHz, −60 dB 94 dB

IN

= ±10 V, fIN = 2 kHz, −60 dB 94.5 dB

IN

= ±5 V, ±10 V, fIN = 2 kHz 94 dB

IN

= 0 V to 5 V, fIN = 20 kHz 93.5 dB

IN

= 0 V to 10 V, ±5 V, fIN = 2 kHz 93 dB

IN

= ±10 V, fIN = 2 kHz 93.5 dB

IN

= 22 µF 10 ms

REF

= 5 V; all specifications T

REF

to T

MIN

, unless otherwise noted.

MAX

1

µA

3

4

Rev. 0 | Page 3 of 32

Page 4

AD7610

Parameter Conditions/Comments Min Typ Max Unit

EXTERNAL REFERENCE PDREF = PDBUF = high

Voltage Range REF 4.75 5 AVDD + 0.1 V

Current Drain 250 kSPS throughput 30 µA

TEMPERATURE PIN

Voltage Output @ 25°C 311 mV

Temperature Sensitivity 1 mV/°C

Output Resistance 4.33 kΩ

DIGITAL INPUTS

Logic Levels

VIL −0.3 +0.6 V

VIH 2.1 OVDD + 0.3 V

IIL −1 +1 µA

IIH −1 +1 µA

DIGITAL OUTPUTS

Data Format Parallel or serial 16-bit

Pipeline Delay

VOL I

VOH I

POWER SUPPLIES

Specified Performance

AVDD 4.75

DVDD 4.75 5 5.25 V

OVDD 2.7 5.25 V

VCC 7 15 15.75 V

VEE −15.75 −15 0 V

Operating Current

AVDD

With Internal Reference 8 mA

With Internal Reference Disabled 6.3 mA

DVDD 3.3 mA

OVDD 0.3 mA

VCC VCC = 15 V, with internal reference buffer 1.4 mA

VCC = 15 V 0.8 mA

VEE VEE = −15 V 0.7 mA

Power Dissipation @ 250 kSPS throughput

With Internal Reference PDREF = PDBUF = low 90 110 mW

With Internal Reference Disabled PDREF = PDBUF = high 70 90 mW

In Power-Down Mode9 PD = high 10 µW

TEMPERATURE RANGE

Specified Performance T

1

With VIN = 0 V to 5 V or 0 V to 10 V ranges, the input current is typically 40 A. In all input ranges, the input current scales with throughput. See the Ana log Inp uts section.

2

Linearity is tested using endpoints, not best fit. All linearity is tested with an external 5 V reference.

3

LSB means least significant bit. All specifications in LSB do not include the error contributed by the reference.

4

All specifications in dB are referred to a full-scale range input, FSR. Tested with an input signal at 0.5 dB below full-scale, unless otherwise specified.

5

Conversion results are available immediately after completed conversion.

6

4.75 V or V

7

Tested in parallel reading mode.

8

With internal reference, PDREF = PDBUF = low; with internal reference disabled, PDREF = PDBUF = high. With internal reference buffer, PDBUF = low.

9

With all digital inputs forced to OVDD.

10

Consult sales for extended temperature range.

5

7, 8

10

– 0.1 V, whichever is larger.

REF

= 500 µA 0.4 V

SINK

= –500 µA OVDD − 0.6 V

SOURCE

6

5 5.25 V

@ 250 kSPS throughput

to T

MIN

−40 +85 °C

MAX

Rev. 0 | Page 4 of 32

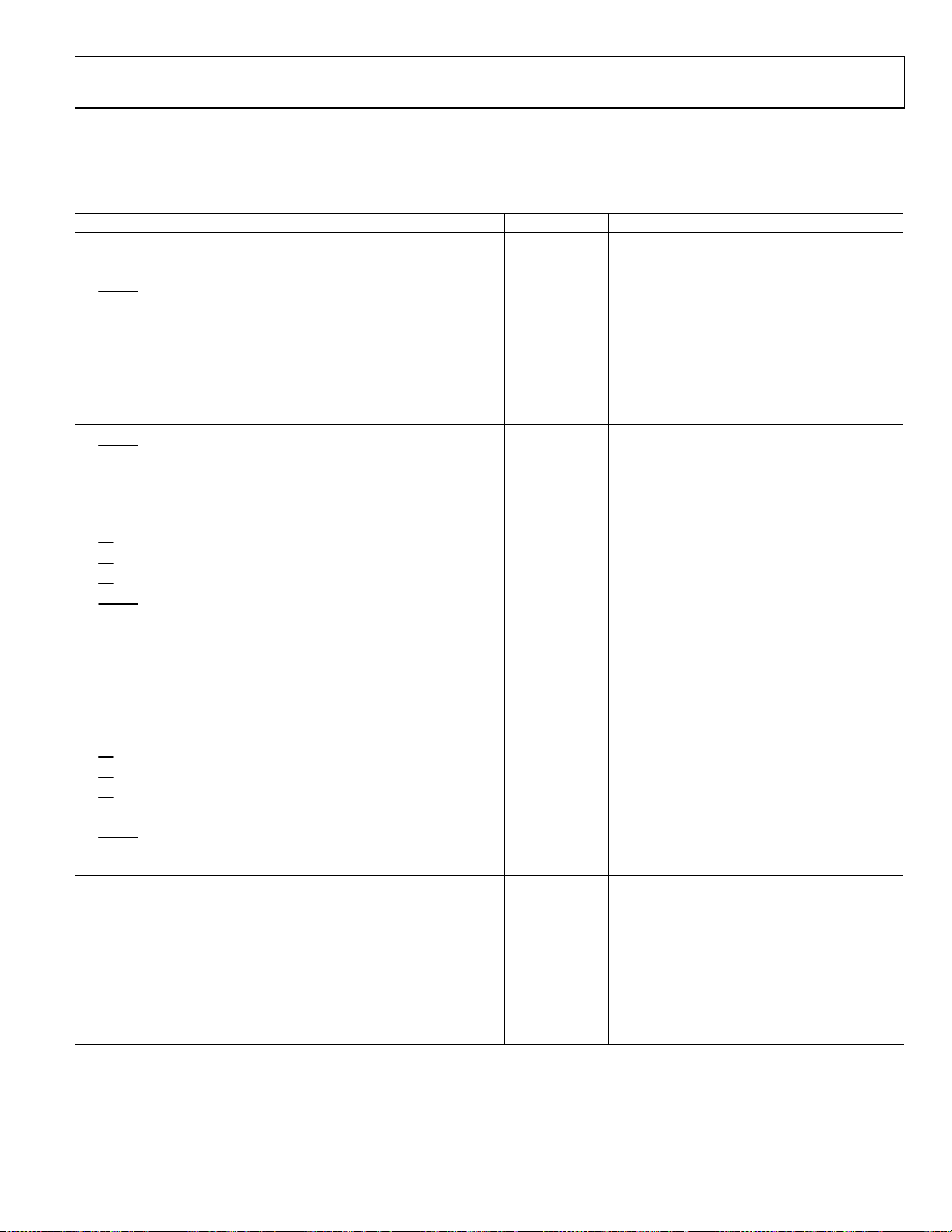

Page 5

AD7610

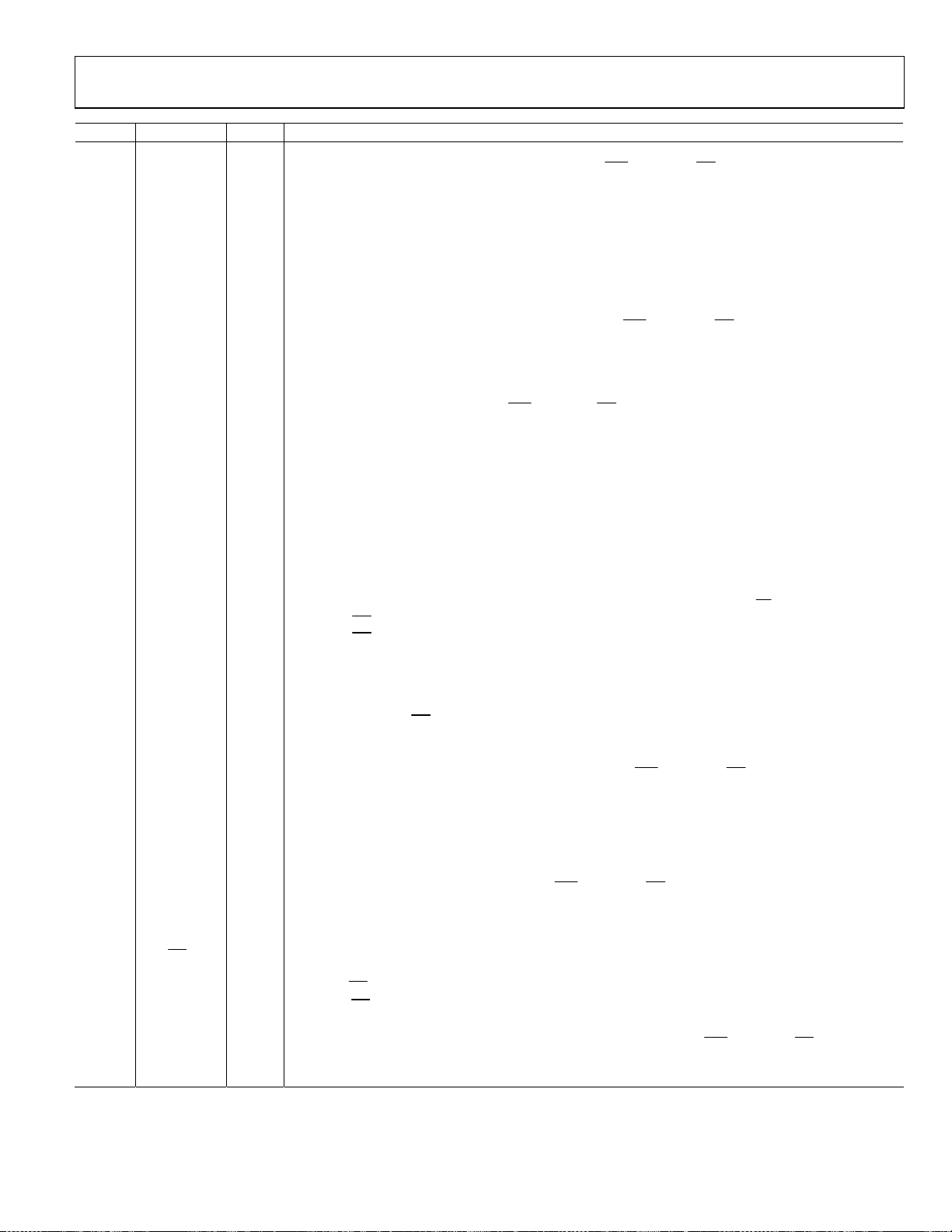

TIMING SPECIFICATIONS

AVDD = DVDD = 5 V; OVDD = 2.7 V to 5.5 V; VCC = 15 V; VEE = −15 V; V

Table 3.

Parameter Symbol Min Typ Max Unit

CONVERSION AND RESET (See Figure 33 and Figure 34)

Convert Pulse Width t1 10 ns

Time Between Conversions t2 4 μs

CNVST Low to BUSY High Delay

BUSY High (Except Master Serial Read After Convert) t4 1.45 μs

Aperture Delay t5 2 ns

End of Conversion to BUSY Low Delay t6 10 ns

Conversion Time t7 1.45 μs

Acquisition Time t8 380 ns

RESET Pulse Width t9 10 ns

PARALLEL INTERFACE MODES (See Figure 35 and Figure 37)

CNVST Low to DATA Valid Delay

DATA Valid to BUSY Low Delay t11 20 ns

Bus Access Request to DATA Valid t12 40 ns

Bus Relinquish Time t13 2 15 ns

MASTER SERIAL INTERFACE MODES1 (See Figure 39 and Figure 40)

CS Low to SYNC Valid Delay

CS Low to Internal SDCLK Valid Delay1

CS Low to SDOUT Delay

CNVST Low to SYNC Delay, Read During Convert

SYNC Asserted to SDCLK First Edge Delay t18 3 ns

Internal SDCLK Period2 t

Internal SDCLK High2 t

Internal SDCLK Low2 t

SDOUT Valid Setup Time2 t

SDOUT Valid Hold Time2 t

SDCLK Last Edge to SYNC Delay2 t

CS High to SYNC HI-Z

CS High to Internal SDCLK HI-Z

CS High to SDOUT HI-Z

BUSY High in Master Serial Read After Convert2 t

CNVST Low to SYNC Delay, Read After Convert

SYNC Deasserted to BUSY Low Delay t30 25 ns

SLAVE SERIAL/SERIAL CONFIGURATION INTERFACE MODES1 (See Figure 42,

Figure 43, and Figure 45)

External SDCLK, SCCLK Setup Time t31 5 ns

External SDCLK Active Edge to SDOUT Delay t32 2 18 ns

SDIN/SCIN Setup Time t33 5 ns

SDIN/SCIN Hold Time t34 5 ns

External SDCLK/SCCLK Period t35 25 ns

External SDCLK/SCCLK High t36 10 ns

External SDCLK/SCCLK Low t37 10 ns

1

In serial interface modes, the SDSYNC, SDSCLK, and SDOUT timings are defined with a maximum load CL of 10 pF; otherwise, the load is 60 pF maximum.

2

In serial master read during convert mode. See Table 4 for serial mode read after convert mode.

= 5 V; all specifications T

REF

t

35 ns

3

t

1.41 μs

10

t

10 ns

14

t

10 ns

15

t

10 ns

16

t

560 ns

17

30 45 ns

19

15 ns

20

10 ns

21

4 ns

22

5 ns

23

5 ns

24

t

10 ns

25

t

10 ns

26

t

10 ns

27

See Table 4

28

t

1.31 μs

29

MIN

to T

, unless otherwise noted.

MAX

Rev. 0 | Page 5 of 32

Page 6

AD7610

Table 4. Serial Clock Timings in Master Read After Convert Mode

DIVSCLK[1]

0 0 1 1

DIVSCLK[0] Symbol 0 1 0 1 Unit

SYNC to SDCLK First Edge Delay Minimum t18 3 20 20 20 ns

Internal SDCLK Period Minimum t19 30 60 120 240 ns

Internal SDCLK Period Maximum t19 45 90 180 360 ns

Internal SDCLK High Minimum t20 15 30 60 120 ns

Internal SDCLK Low Minimum t21 10 25 55 115 ns

SDOUT Valid Setup Time Minimum t22 4 20 20 20 ns

SDOUT Valid Hold Time Minimum t23 5 8 35 90 ns

SDCLK Last Edge to SYNC Delay Minimum t24 5 7 35 90 ns

BUSY High Width Maximum t28 2.25 3.00 4.40 7.30 µs

1.6mA I

TO OUTPUT

PIN

C

L

60pF

500µA I

NOTES

1. IN SERIAL INTERFACE MODES, THE SY NC, SCLK, AND

SDOUT ARE DEFI NED WITH A MAX IMUM LOAD

OF 10pF; OTHERWISE, THE LOAD IS 60pF MAXIMUM.

C

L

Figure 2. Load Circuit for Digital Interface Timing,

SDOUT, SYNC, and SCLK Outputs, C

OL

1.4V

2V

OH

6395-002

0.8V

t

DELAY

t

DELAY

2V

2V

0.8V0.8V

06395-003

Figure 3. Voltage Reference Levels for Timing

= 10 pF

L

Rev. 0 | Page 6 of 32

Page 7

AD7610

ABSOLUTE MAXIMUM RATINGS

Table 5.

Parameter Rating

Analog Inputs/Outputs

IN+, IN−1 to AGND VEE − 0.3 V to VCC + 0.3 V

REF, REFBUFIN, TEMP,

REFGND to AGND

AVDD + 0.3 V to

AGND − 0.3 V

Ground Voltage Differences

AGND, DGND, OGND ±0.3 V

Supply Voltages

AVDD, DVDD, OVDD −0.3 V to +7 V

AVDD to DVDD, AVDD to OVDD ±7 V

DVDD to OVDD ±7 V

VCC to AGND, DGND –0.3 V to +16.5 V

VEE to GND +0.3 V to −16.5 V

Digital Inputs −0.3 V to OVDD +0.3 V

PDREF, PDBUF

2

±20 mA

Internal Power Dissipation3 700 mW

Internal Power Dissipation4 2.5 W

Junction Temperature 125°C

Storage Temperature Range −65°C to +125°C

1

See the Analog Inputs section.

2

See the Voltage Reference Input section.

3

Specification is for the device in free air: 48-Lead LQFP; θJA = 91°C/W,

θJC = 30°C/W.

4

Specification is for the device in free air: 48-Lead LFCSP; θJA = 26°C/W.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 7 of 32

Page 8

AD7610

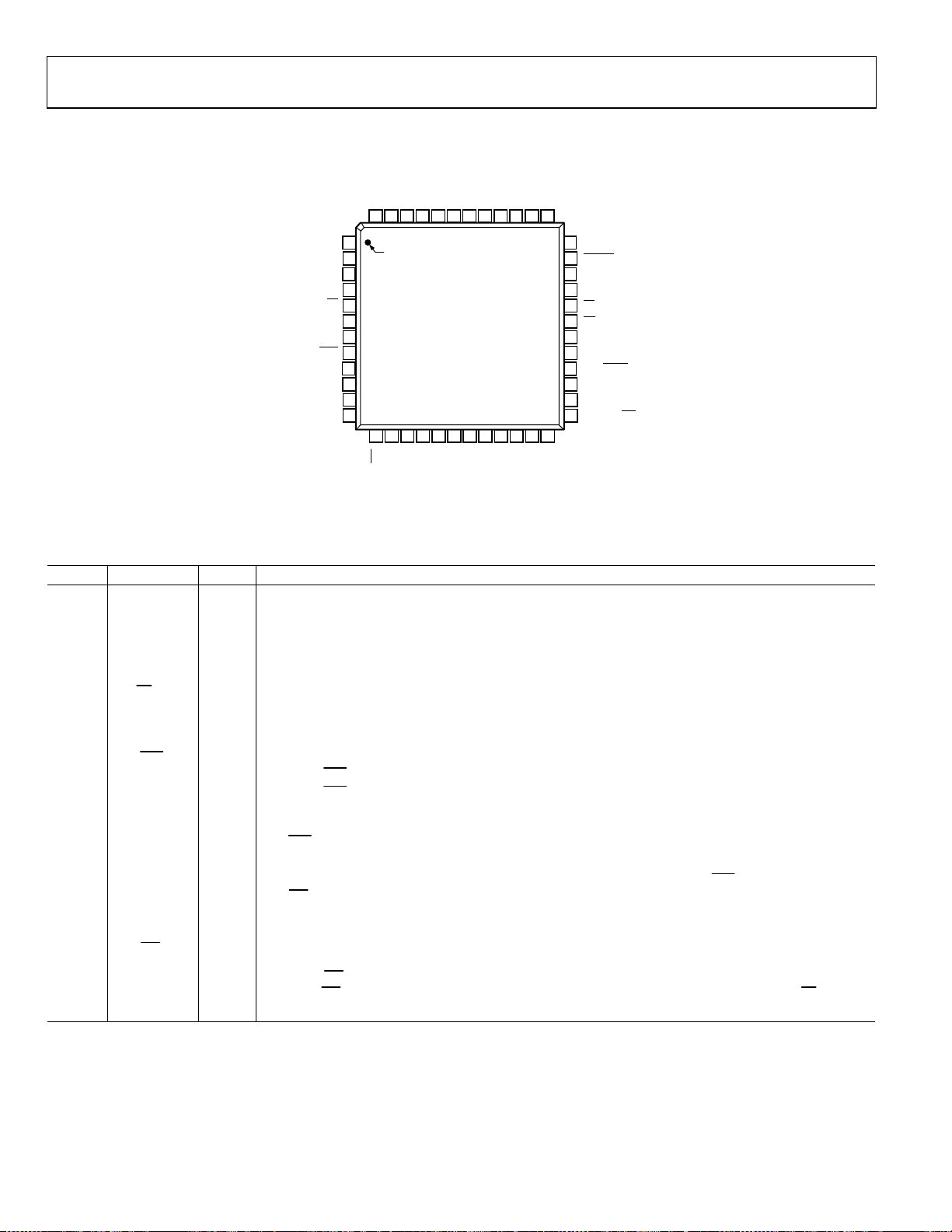

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

PDBUF

PDREF

REFBUFIN

TEMP

AVDD

IN+

AGND

VEE

VCC

IN–

REFGND

REF

36

BIPOL AR

35

CNVST

34

PD

33

RESET

32

CS

31

RD

30

TEN

29

BUSY

28

D15/SCCS

27

D14/SCCLK

26

D13/SCIN

25

D12/HW/ SW

D10/SYNC

D8/SDOUT

D9/SDCLK

D11/RDERROR

06395-004

AGND

AVDD

AGND

BYTESWAP

OB/2C

OGND

OGND

SER/PAR

D0

D1

D2/DIVSCLK[0]

D3/DIVSCLK[1]

48 47 46 45 44 43 42 41 40 39 38 37

1

PIN 1

2

3

4

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20 21 22 23 24

D4/EXT/INT

D5/INVSYNC

AD7610

TOP VIEW

(Not to Scale)

D6/INVSCLK

D7/RDC/SDIN

DVDD

OVDD

OGND

Figure 4. Pin Configuration

DGND

Table 6. Pin Function Descriptions

Pin No. Mnemonic Type1Description

1, 3, 42 AGND P Analog Power Ground Pins. Ground reference point for all analog I/O. All analog I/O should be referenced to

2, 44 AVDD P Analog Power Pins. Nominally 4.75 V to 5.25 V and decoupled with 10 F and 100 nF capacitors.

4 BYTESWAP DI Parallel Mode Selection (8-Bit/16-Bit). When high, the LSB is output on D[15:8] and the MSB is output on

5

OB/

2C

DI

6, 7, 17 OGND P Input/Output Interface Digital Power Ground. Ground reference point for digital outputs. Should be

8

SER/

PAR

DI Serial/Parallel Selection Input.

9, 10 D[0:1] DO Bit 0 and Bit 1 of the parallel port data output bus. These pins are always outputs regardless of the state of

11, 12 D[2:3] or DI/O In parallel mode, these outputs are used as Bit 2 and Bit 3 of the parallel port data output bus.

DIVSCLK[0:1]

13 D4 or DI/O In parallel mode, this output is used as Bit 4 of the parallel port data output bus.

EXT/

INT

AGND and should be connected to the analog ground plane of the system. In addition, the AGND, DGND, and

OGND voltages should be at the same potential.

D[7:0]; when low, the LSB is output on D[7:0] and the MSB is output on D[15:8].

2

Straight Binary/Binary Twos Complement Output. When high, the digital output is straight binary. When low,

the MSB is inverted resulting in a twos complement output from its internal shift register.

connected to the system digital ground ideally at the same potential as AGND and DGND.

When SER/

When SER/

PAR

= low, the parallel mode is selected.

PAR

= high, the serial modes are selected. Some bits of the data bus are used as a serial port and

the remaining data bits are high impedance outputs.

PAR

SER/

Serial Data Division Clock Selection. In serial master read after convert mode (SER/

EXT/

.

PAR

= high,

INT

= low, RDC/SDIN = low) these inputs can be used to slow down the internally generated serial data

clock that clocks the data output. In other serial modes, these pins are high impedance outputs.

Serial Data Clock Source Select. In serial mode, this input is used to select the internally generated (master) or

external (slave) serial data clock for the AD7610 output data.

When EXT/

When EXT/

INT

= low, master mode; the internal serial data clock is selected on SDCLK output.

INT

= high, slave mode; the output data is synchronized to an external clock signal (gated by CS)

connected to the SDCLK input.

Rev. 0 | Page 8 of 32

Page 9

AD7610

Pin No. Mnemonic Type1 Description

14 D5 or DI/O In parallel mode, this output is used as Bit 5 of the parallel port data output bus.

INVSYNC

15 D6 or DI/O In parallel mode, this output is used as Bit 6 of the parallel port data output bus.

INVSCLK In all serial modes, invert SDCLK/SCCLK select. This input is used to invert both SDCLK and SCCLK.

16 D7 or DI/O In parallel mode, this output is used as Bit 7 of the parallel port data output bus.

RDC or

SDIN

18 OVDD P Input/Output Interface Digital Power. Nominally at the same supply as the supply of the host interface 2.5 V, 3

19 DVDD P Digital Power. Nominally at 4.75 V to 5.25 V and decoupled with 10 μF and 100 nF capacitors. Can be supplied

20 DGND P Digital Power Ground. Ground reference point for digital outputs. Should be connected to system digital

21 D8 or DO In parallel mode, this output is used as Bit 8 of the parallel port data output bus.

SDOUT Serial Data output. In all serial modes this pin is used as the serial data output synchronized to SDCLK.

22 D9 or DI/O In parallel mode, this output is used as Bit 9 of the parallel port data output bus.

SDCLK Serial Data Clock. In all serial modes, this pin is used as the serial data clock input or output, dependent on the

23 D10 or DO In parallel mode, this output is used as Bit 10 of the parallel port data output bus.

SYNC

24 D11 or DO In parallel mode, this output is used as Bit 11 of the parallel port data output bus.

RDERROR

25 D12 or DI/O In parallel mode, this output is used as Bit 12 of the parallel port data output bus.

26 D13 or DI/O In parallel mode, this output is used as Bit 13 of the parallel port data output bus.

SCIN

HW/

SW

Serial Configuration Hardware/Software Select. In serial mode, this input is used to configure the AD7610 by

Serial Data Invert Sync Select. In serial master mode (SER/

select the active state of the SYNC signal.

When INVSYNC = low, SYNC is active high.

When INVSYNC = high, SYNC is active low.

When INVSCLK = low, the rising edge of SDCLK/SCCLK are used.

When INVSCLK = high, the falling edge of SDCLK/SCCLK are used.

Serial Data Read During Convert. In serial master mode (SER/

the read mode. See the

When RDC = low, the current result is read after conversion. Note the maximum throughput is not attainable

in this mode.

When RDC = high, the previous conversion result is read during the current conversion.

Serial Data In. In serial slave mode (SER/

chain the conversion results from two or more ADCs onto a single SDOUT line. The digital data level on SDIN is

output on SDOUT with a delay of 16 SDCLK periods after the initiation of the read sequence.

V, or 5 V and decoupled with 10 μF and 100 nF capacitors.

from AVDD.

ground ideally at the same potential as AGND and OGND.

Conversion results are stored in an on-chip register. The AD7610 provides the conversion result, MSB first,

from its internal shift register. The data format is determined by the logic level of OB/

When EXT/

When EXT/

When INVSCLK = low, SDOUT is updated on SDCLK rising edge.

When INVSCLK = high, SDOUT is updated on SDCLK falling edge.

logic state of the EXT/

the INVSCLK pin.

Serial Data Frame Synchronization. In serial master mode (SER/

as a digital output frame synchronization for use with the internal data clock.

When a read sequence is initiated and INVSYNC = low, SYNC is driven high and remains high while the SDOUT

output is valid.

When a read sequence is initiated and INVSYNC = high, SYNC is driven low and remains low while the SDOUT

output is valid.

Serial Data Read Error. In serial slave mode (SER/

incomplete data read error flag. If a data read is started and not completed when the current conversion is

complete, the current data is lost and RDERROR is pulsed high.

hardware or software. See the

When HW/

When HW/

Serial Configuration Data Input. In serial software configuration mode (SER/

input is used to serially write in, MSB first, the configuration data into the serial configuration register. The

data on this input is latched with SCCLK. See the

INT

= low, (master mode) SDOUT is valid on both edges of SDCLK.

INT

= high (slave mode).

SW

= low, the AD7610 is configured through software using the serial configuration register.

SW

= high, the AD7610 is configured through dedicated hardware input pins.

Master Serial Interface section.

PAR

= high EXT/

INT

pin. The active edge where the data SDOUT is updated depends on the logic state of

PAR

Hardware Configuration section and Software Configuration section.

Software Configuration section.

PAR

= high, EXT/

PAR

= high, EXT/

INT

= high) SDIN can be used as a data input to daisy-

PAR

= high, EXT/

INT

INT

= low). This input is used to

INT

= low) RDC is used to select

2C

.

= high, EXT/

= high), this output is used as an

INT

= low), this output is used

PAR

= high, HW/SW = low) this

Rev. 0 | Page 9 of 32

Page 10

AD7610

Pin No. Mnemonic Type1Description

27 D14 or DI/O In parallel mode, this output is used as Bit 14 of the parallel port data output bus.

SCCLK

Serial Configuration Clock. In serial software configuration mode (SER/

used to clock in the data on SCIN. The active edge where the data SCIN is updated depends on the logic state

of the INVSCLK pin. See the

Software Configuration section.

28 D15 or DI/O In parallel mode, this output is used as Bit 15 of the parallel port data output bus.

SCCS

Serial Configuration Chip Select. In serial software configuration mode (SER/

input enables the serial configuration port. See the

Software Configuration section.

29 BUSY DO Busy Output. Transitions high when a conversion is started, and remains high until the conversion

is complete and the data is latched into the on-chip shift register. The falling edge of BUSY can be

used as a data ready clock signal. Note that in master read after convert mode (SER/

Table 4.

30 TEN DI

RDC = low) the busy time changes according to

2

Input Range Select. Used in conjunction with BIPOLAR per the following:

Input Range BIPOLAR TEN

0 V to 5 V Low Low

0 V to 10 V Low High

±5 V High Low

±10 V High High

31

32

RD

CS

DI

DI

Read Data. When

Chip Select. When

CS

and RD are both low, the interface parallel or serial output bus is enabled.

CS

and RD are both low, the interface parallel or serial output bus is enabled. CS is also

used to gate the external clock in slave serial mode (not used for serial programmable port).

33 RESET DI Reset Input. When high, reset the AD7610. Current conversion, if any, is aborted. The falling edge of RESET

resets the data outputs to all zero’s (with OB/

2C

= high) and clears the configuration register. See the Digital

Interface section. If not used, this pin can be tied to OGND.

34 PD DI

2

Power-Down Input. When PD = high, power down the ADC. Power consumption is reduced and conversions

are inhibited after the current one is completed. The digital interface remains active during power down.

35

CNVST

DI

Conversion Start. A falling edge on

CNVST

puts the internal sample-and-hold into the hold state and initiates

a conversion.

36 BIPOLAR DI

2

Input Range Select. See description for Pin 30.

37 REF AI/O Reference Input/Output. When PDREF/PDBUF = low, the internal reference and buffer are enabled, producing 5 V

on this pin. When PDREF/PDBUF = high, the internal reference and buffer are disabled, allowing an externally

supplied voltage reference up to AVDD volts. Decoupling with at least a 22 F is required with or without the

internal reference and buffer. See the

Reference Decoupling section.

38 REFGND AI Reference Input Analog Ground. Connected to analog ground plane.

39 IN− AI Analog Input Ground Sense. Should be connected to the analog ground plane or to a remote sense ground.

40 VCC P High Voltage Positive Supply. Normally +7 V to +15 V.

41 VEE P High Voltage Negative Supply. Normally 0 V to −15 V (0 V in unipolar ranges).

43 IN+ AI Analog Input. Referenced to IN−.

45 TEMP AO Temperature Sensor Analog Output. Enabled when the internal reference is turned on (PDREF = PDBUF =

low). See the

Temperature Sensor section.

46 REFBUFIN AI Reference Buffer Input. When using an external reference with the internal reference buffer (PDBUF = low,

PDREF = high), applying 2.5 V on this pin produces 5 V on the REF pin. See the

47 PDREF DI Internal Reference Power-Down Input.

When low, the internal reference is enabled.

When high, the internal reference is powered down, and an external reference must be used.

48 PDBUF DI Internal Reference Buffer Power-Down Input.

When low, the buffer is enabled (must be low when using internal reference).

When high, the buffer is powered-down.

1

AI = analog input; AI/O = bidirectional analog; AO = analog output; DI = digital input; DI/O = bidirectional digital; DO = digital output; P = power.

2

In serial configuration mode (SER/

PAR

= high, HW/SW = low), this input is programmed with the serial configuration register and this pin is a don’t care. See the

Hardware Configuration section and Software Configuration section.

PAR

= high, HW/SW = low) this input is

PAR

= high, HW/SW = low) this

PAR

= high, EXT/

Voltage Reference Input section.

INT

= low,

Rev. 0 | Page 10 of 32

Page 11

AD7610

TYPICAL PERFORMANCE CHARACTERISTICS

AVDD = DVDD = 5 V; OVDD = 5 V; VCC = 15 V; VEE = −15 V; V

= 5 V; TA = 25°C.

REF

1.5

1.0

0.5

0

INL (LSB)

–0.5

–1.0

–1.5

0 65536

16384 32768 49152

CODE

Figure 5. Integral Nonlinearity vs. Code

250

200

150

100

NUMBER OF UNIT S

50

0

–1.0 1.0

–0.6 –0.4 –0.2 0 0.2 0.4 0.6 0.8–0.8

INL DISTRIBUTION (LSB)

NEGATIVE INL

POSITIVE INL

Figure 6. Integral Nonlinearity Distribution (296 Devices)

250000

211404

200000

150000

σ = 0.44

1.5

1.0

0.5

0

DNL (LSB)

–0.5

–1.0

–1.5

0 16384 32768 49152 65536

6395-005

CODE

06395-008

Figure 8. Differential Nonlinearity vs. Code

180

160

140

120

100

80

60

NUMBER OF UNITS

40

20

0

–1.0 1.0

06395-006

–0.6 –0.4 –0.2 0 0.2 0.4 0.6 0.8–0.8

NEGATIVE DNL

POSITIVE DNL

DNL DISTRIBUTION (LSB)

06395-009

Figure 9. Differential Nonlinearity Distribution (296 Devices)

140000

120000

100000

80000

127179

132700

σ = 0.51

COUNTS

100000

50000

00 4 00

0

7FFF 8006

8000 8001 8002 8003 8004 8005

27510

CODE IN HEX

22202

Figure 7. Histogram of 261,120 Conversions of a DC Input

at the Code Center

06395-007

Rev. 0 | Page 11 of 32

60000

COUNTS

40000

20000

00 00

0

1072

169

CODE IN HEX

Figure 10. Histogram of 261,120 Conversions of a DC Input

at the Code Transition

800780068000 8001 8002 8003 8004 8005

06395-010

Page 12

AD7610

–

95.0

94.5

±5V

±10V

SNR

SINAD

–20

–40

–60

0

f

= 250kSPS

S

f

= 19.95kHz

IN

SNR = 93.4dB

THD = –107dB

SFDR = 114dB

SINAD = 93dB

–80

–100

–120

AMPLITUDE (dB OF FULL SCALE)

–140

–160

0 125

FREQUENCY (kHz)

Figure 11. FFT 20 kHz

96

94

92

90

88

86

SNR, SINAD (dB)

84

82

80

1 10 100

SNR

SINAD

ENOB

FREQUENCY (kHz)

Figure 12. SNR, SINAD, and ENOB vs. Frequency

94.0

0V TO 5V

93.5

SNR, SINAD REFERRED TO FULL SCALE (dB)

93.0

10025 50 75

06395-011

–60 –50 –40 –30 –20 –10 0

0V TO 10V

INPUT LEVEL (dB)

06395-014

Figure 14. SNR and SINAD vs. Input Level (Referred to Full Scale)

16.0

15.8

15.6

15.4

15.2

15.0

14.8

14.6

14.4

70

–80

SFDR

–90

THD

–100

ENOB (Bits)

06395-012

THIRD

HARMONIC

–110

SECOND

THD, HARMONICS (dB)

HARMONIC

–120

–130

1 10 100

FREQUENCY (kHz)

120

110

100

90

80

70

60

SFDR (dB)

6395-015

Figure 15. THD, Harmonics, and SFDR vs. Frequency

96

95

94

93

SNR (dB)

92

91

90

–55 125

–35 –15 5 25 45 65 85 105

TEMPERATURE (° C)

VIN = 0V TO 5V

VIN = 0V TO 10V

VIN = ±5V

VIN = ±10V

Figure 13. SNR vs. Temperature

06395-013

Rev. 0 | Page 12 of 32

96

95

94

93

SINAD (dB)

92

91

90

–55 125

–35 –15 5 25 45 65 85 105

TEMPERATURE ( °C)

VIN = 0V TO 5V

VIN = 0V TO 10V

VIN = ±5V

VIN = ±10V

Figure 16. SINAD vs. Temperature

06395-016

Page 13

AD7610

–

96

–100

–104

–108

–112

THD (dB)

–116

–120

–124

–35 –15 5 25 45 65 85 105

–55 125

TEMPERATURE (° C)

VIN = 0V TO 5V

VIN = 0V TO 10V

VIN = ±5V

VIN = ±10V

Figure 17. THD vs. Temperature

06395-017

126

124

122

120

118

116

SFDR (dB)

114

112

110

108

–35 –15 5 25 45 65 85 105

–55 125

TEMPERATURE (° C)

VIN = 0V TO 5V

VIN = 0V TO 10V

VIN = ±5V

VIN = ±10V

Figure 20. SFDR vs. Temperature (Excludes Harmonics)

06395-020

5

4

3

2

1

0

–1

–2

–3

–4

ZERO ERROR, FULL SCALE ERROR (LSB)

–5

–55 –35 –15 5 25 45 65 85 105 125

TEMPERATURE ( °C)

ZERO ERROR

POSITIVE FS ERROR

NEGATIVE FS ERROR

06395-018

Figure 18. Zero Error, Positive and Negative Full Scale vs. Temperature

60

50

40

30

20

NUMBER OF UNITS

10

0

1234567

08

REFERENCE DRIFT (ppm/ °C)

06395-019

Figure 19. Reference Voltage Temperature Coefficient Distribution (247 Devices)

5.012

5.010

5.008

5.006

5.004

VREF (V)

5.002

5.000

4.998

4.996

–55 –35 –15 5 25 45 65 85 105 125

TEMPERATURE (°C)

Figure 21. Typical Reference Voltage Output vs. Temperature (3 Devices)

100000

10000

OPERATING CURRENTS (µA)

0.001

1000

100

0.1

0.01

DVDD

10

1

AVDD

VCC +15V

VEE –15V

ALL MODES

OVDD

PDREF = PDBUF = HIG H

10

100 1000 10000 100000

SAMPLING RAT E (SPS)

1000000

Figure 22. Operating Currents vs. Sample Rate

06395-021

06395-022

Rev. 0 | Page 13 of 32

Page 14

AD7610

700

PD = PDBUF = PDREF = HIGH

VEE = –15V

VCC = +15V

600

DVDD

OVDD

AVDD

500

400

300

200

100

POWER-DOW N OPERATING CURRENTS (nA)

0

–55 –35 –15 5 25 45 65 8 5 105

TEMPERATURE (°C)

Figure 23. Power-Down Operating Currents vs. Temperature

06395-023

50

45

40

35

30

25

DELAY (ns)

20

12

t

15

10

5

0

0 50 100 150 200

OVDD = 2.7V @ 25°C

OVDD = 5V @ 25°C

C

L

OVDD = 2.7V @ 85°C

OVDD = 5V @ 85°C

(pF)

Figure 24. Typical Delay vs. Load Capacitance C

06395-024

L

Rev. 0 | Page 14 of 32

Page 15

AD7610

TERMINOLOGY

Least Significant Bit (LSB)

The least significant bit, or LSB, is the smallest increment that

can be represented by a converter. For an analog-to-digital converter with N bits of resolution, the LSB expressed in volts is

maxV

LSB

INp-p

)V(

=

)(

N

2

Integral Nonlinearity Error (INL)

Linearity error refers to the deviation of each individual code

from a line drawn from negative full-scale through positive fullscale. The point used as negative full-scale occurs a ½ LSB before

the first code transition. Positive full-scale is defined as a level

1½ LSBs beyond the last code transition. The deviation is measured from the middle of each code to the true straight line.

Differential Nonlinearity Error (DNL)

In an ideal ADC, code transitions are 1 LSB apart. Differential

nonlinearity is the maximum deviation from this ideal value. It

is often specified in terms of resolution for which no missing

codes are guaranteed.

Bipolar Zero Error

The difference between the ideal midscale input voltage (0 V)

and the actual voltage producing the midscale output code.

Unipolar Offset Error

The first transition should occur at a level ½ LSB above analog

ground. The unipolar offset error is the deviation of the actual

transition from that point.

Full-Scale Error

The last transition (from 111…10 to 111…11) should occur for

an analog voltage 1½ LSB below the nominal full-scale. The fullscale error is the deviation in LSB (or % of full-scale range) of

the actual level of the last transition from the ideal level and

includes the effect of the offset error. Closely related is the gain

error (also in LSB or % of full-scale range), which does not

include the effects of the offset error.

Dynamic Range

Dynamic range is the ratio of the rms value of the full-scale to

the rms noise measured for an input typically at −60 dB. The

value for dynamic range is expressed in decibels.

Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the actual input signal to the

rms sum of all other spectral components below the Nyquist

frequency, excluding harmonics and dc. The value for SNR is

expressed in decibels.

Total Harmonic Distortion (THD)

THD is the ratio of the rms sum of the first five harmonic

components to the rms value of a full-scale input signal and

is expressed in decibels.

Signal-to-(Noise + Distortion) Ratio (SINAD)

SINAD is the ratio of the rms value of the actual input signal to

the rms sum of all other spectral components below the Nyquist

frequency, including harmonics but excluding dc. The value for

SINAD is expressed in decibels.

Spurious-Free Dynamic Range (SFDR)

The difference, in decibels (dB), between the rms amplitude of

the input signal and the peak spurious signal.

Effective Number of Bits (ENOB)

ENOB is a measurement of the resolution with a sine wave

input. It is related to SINAD and is expressed in bits by

ENOB = [(SINAD

− 1.76)/6.02]

dB

Aperture Delay

Aperture delay is a measure of the acquisition performance

measured from the falling edge of the

CNVST

input to when

the input signal is held for a conversion.

Transi ent Res p ons e

The time required for the AD7610 to achieve its rated accuracy

after a full-scale step function is applied to its input.

Reference Voltage Temperature Coefficient

Reference voltage temperature coefficient is derived from the

typical shift of output voltage at 25°C on a sample of parts at the

maximum and minimum reference output voltage (V

ured at T

, T(25°C), and T

MIN

REF

. It is expressed in ppm/°C as

MAX

((

Cppm/ ×

=°

)(TCV

REF

REFREF

C25

×°

MAX

MIN

) meas-

REF

)MinV–)MaxV

6

10

)T–T()(V

where:

V

(Max) = maximum V

REF

(Min) = minimum V

V

REF

V

(25°C) = V

REF

= +85°C.

T

MAX

T

= –40°C.

MIN

at 25°C.

REF

REF

REF

at T

at T

MIN

MIN

, T(25°C), or T

, T(25°C), or T

MAX

MAX

.

.

Rev. 0 | Page 15 of 32

Page 16

AD7610

THEORY OF OPERATION

IN+

REF

REFGND

MSB

32,768C

16,384C 4C 2C C C

IN–

Figure 25. ADC Simplified Schematic

OVERVIEW

The AD7610 is a very fast, low power, precise, 16-bit analog-todigital converter (ADC) using successive approximation capacitive

digital-to-analog converter (CDAC) architecture.

The AD7610 can be configured at any time for one of four input

ranges with inputs in parallel and serial hardware modes or by a

dedicated write only, SPI-compatible interface via a configuretion register in serial software mode. The AD7610 uses Analog

Device’s patented iCMOS high voltage process to accommodate

0 to 5 V, 0 to 10 V, ±5 V, and ±10 V input ranges without the use

of conventional thin films. Only one acquisition cycle, t

for the inputs to latch to the correct configuration. Resetting or

power cycling is not required for reconfiguring the ADC.

The AD7610 is capable of converting 250,000 samples per

second (250 kSPS) and power consumption scales linearly with

throughput making it useful for battery powered systems.

The AD7610 provides the user with an on-chip track-and-hold,

successive approximation ADC that does not exhibit any pipeline or latency, making it ideal for multiple multiplexed channel

applications.

For unipolar input ranges, the AD7610 typically requires three

supplies; VCC, AVDD (which can supply DVDD), and OVDD

which can be interfaced to either 5 V, 3.3 V, or 2.5 V digital logic.

For bipolar input ranges, the AD7610 requires the use of the

additional VEE supply.

The device is housed in Pb-free, 48-lead LQFP or tiny LFCSP

7 mm × 7 mm packages that combine space savings with flexibility. In addition, the AD7610 can be configured as either a

parallel or serial SPI-compatible interface.

, is required

8

65,536C

SWITCHES

LSB

SW

SW

A

COMP

B

CONTROL

CONTRO L

LOGIC

CNVST

BUSY

OUTPUT

CODE

6395-025

CONVERTER OPERATION

The AD7610 is a successive approximation ADC based on a

charge redistribution DAC.

schematic of the ADC. The CDAC consists of two identical

arrays of 16 binary weighted capacitors, which are connected

to the two comparator inputs.

During the acquisition phase, terminals of the array tied to the

comparator’s input are connected to AGND via SW+ and SW−.

All independent switches are connected to the analog inputs.

Thus, the capacitor arrays are used as sampling capacitors and

acquire the analog signal on IN+ and IN− inputs. A conversion

phase is initiated once the acquisition phase is complete and the

CNVST

input goes low. When the conversion phase begins, SW+

and SW− are opened first. The two capacitor arrays are then

disconnected from the inputs and connected to the REFGND

input. Therefore, the differential voltage between the inputs (IN+

and IN−) captured at the end of the acquisition phase is applied

to the comparator inputs, causing the comparator to become

unbalanced. By switching each element of the capacitor array

between REFGND and REF, the comparator input varies by

binary weighted voltage steps (V

The control logic toggles these switches, starting with the MSB

first, in order to bring the comparator back into a balanced

condition.

After the completion of this process, the control logic generates

the ADC output code and brings the BUSY output low.

Figure 25 shows the simplified

/2, V

REF

/4 through V

REF

/65536).

REF

Rev. 0 | Page 16 of 32

Page 17

AD7610

TRANSFER FUNCTIONS

Using the OB/2C digital input or via the configuration register,

the AD7610 offers two output codings: straight binary and twos

complement. See

Figure 26 and Tab le 7 for the ideal transfer characteristic and digital output codes for the different analog input

ranges, V

OB/

. Note that when using the configuration register, the

IN

2C

input is a don’t care and should be tied to either high or low.

Table 7. Output Codes and Ideal Input Voltages

V

= 5 V Digital Output Code

REF

Description VIN = 5 V VIN = 10 V VIN = ±5 V VIN = ±10 V Straight Binary Twos Complement

FSR −1 LSB 4.999924 V 9.999847 V +4.999847 V +9.999695 V 0xFFFF

FSR − 2 LSB 4.999847 V 9.999695 V +4.999695 V +9.999390 V 0xFFFE 0x7FFE

Midscale + 1 LSB 2.500076 V 5.000153 V +152.6 µV +305.2 µV 0x8001 0x0001

Midscale 2.5 V 5.000000 V 0 V 0 V 0x8000 0x0000

Midscale − 1 LSB 2.499924 V 4.999847 V −152.6 µV −305.2 µV 0x7FFF 0xFFFF

−FSR + 1 LSB 76.3 µV 152.6 µV −4.999847 V −9.999695 V 0x0001 0x8001

−FSR 0 V 0 V −5 V −10 V 0x0000

1

This is also the code for overrange analog input (V

2

This is also the code for overrange analog input (V

− V

above V

IN+

IN−

− V

below V

IN+

IN−

− V

− V

REFGND

REFGND

).

).

REF

REF

111...111

111...110

111...101

ADC CODE (Straigh t Binary)

000...010

000...001

000...000

–FSR

–FSR + 0.5 L SB

ANALOG INPUT

Figure 26. ADC Ideal Transfer Function

1

2

+FSR – 1 LSB–FSR + 1 LSB

+FSR – 1.5 L SB

1

0x7FFF

2

0x8000

06395-026

Rev. 0 | Page 17 of 32

Page 18

AD7610

TYPICAL CONNECTION DIAGRAM

Figure 27 shows a typical connection diagram for the AD7610 using the internal reference, serial data and serial configuration interfaces.

Different circuitry from that shown in

ANALOG

SUPPLY (+5V)

10µF

+7V TO +15.75V

SUPPLY

–7V TO –15. 75V

SUPPLY

NOTE 6

10µF

10µF

NOTE 4

C

REF

22µF

100nF

100nF

100nF

Figure 27 is optional and is discussed in the following sections.

DIGIT AL

SUPPLY (+5V)

100nF 100nF

AD7610

BUSY

SDCLK

SDOUT

SCCLK

SCIN

SCCS

CNVST

100nF

NOTE 5

10Ω

10µF

AVDD

AGND DGND DVDD O VDD OGND

VCC

VEE

NOTE 3

REF

REFBUFI N

REFGND

10µF

DIGIT AL

INTERFACE

SUPPLY

(+2.5V, +3.3V, OR +5V)

NOTE 7

50Ω

D

MICROCO NVERTER/

MICROPRO CESSOR/

DSP

SERIAL

PORT 1

SERIAL

PORT 2

RD CS

OB/2C

SER/PAR

HW/SW

BIPOLA R

TEN

RESETPD

NOTE 2

ANALOG

INPUT +

ANALOG

INPUT–

NOTES

1. SEE ANAL OG I NPUT SECT ION. ANA LOG I NPUT(–) I S REFER ENCED TO A GND ±0.1V.

2. THE AD8021 IS RECOMMENDED. SEE DRIVER AMPLIFIER CHOICE SECTION.

3. THE CO NFIGUR ATION S HOWN IS USING T HE INTE RNAL REFE RENCE. SE E VOLT AGE REF ERENCE INP UT SECTI ON.

4. A 22µF CE RAMIC CAPACI TOR (X 5R, 1206 SIZ E) IS RE COMMENDE D (FOR EXAMPLE, PANASONI C ECJ4YB1A226M).

SEE VOLTAGE REFERENCE INPUT SECTION.

5. OPTION, SEE P OWER SUPPLY SECTIO N.

6. THE VCC AND VEE SUPPLIES SHOULD BE VCC = [VIN(MAX) +2V] and VEE = [VI N(MIN) –2V] FOR BIPOLAR INPUT RANGES.

FOR UNIPOLAR INPUT RANGES, VE E CAN BE 0V. SEE POWER SUPPLY SECTI ON.

7. OPT IONAL L OW JI TTER CNVS T, SE E CONVERSION CONT ROL SE CTION.

U1

C

C

NOTE 1

15Ω

2.7nF

IN–

IN+

NOTE 3

PDREF

PDBUF

Figure 27. Typical Connection Diagram Shown with Serial Interface and Serial Programmable Port

OVDD

CLOCK

6395-027

Rev. 0 | Page 18 of 32

Page 19

AD7610

V

ANALOG INPUTS

Input Range Selection

In parallel mode and serial hardware mode, the input range is

selected by using the BIPOLAR (bipolar) and TEN (10 Volt range)

inputs. See

Configuration

programming the mode selection with either pins or configuration

register. Note that when using the configuration register, the

BIPOLAR and TEN inputs are don’t cares and should be tied to

either high or low.

Input Structure

Figure 28 shows an equivalent circuit for the input structure of

the AD7610.

The four diodes, D1 to D4, provide ESD protection for the analog

inputs, IN+ and IN−. Care must be taken to ensure that the analog

input signal never exceeds the supply rails by more than 0.3 V,

because this causes the diodes to become forward-biased and to

start conducting current. These diodes can handle a forwardbiased current of 120 mA maximum. For instance, these conditions

could eventually occur when the input buffer’s U1 supplies are

different from AVDD, VCC, and VEE. In such a case, an input

buffer with a short-circuit current limitation can be used to protect

the part although most op amps’ short circuit current is <100 mA.

Note that D3 and D4 are only used in the 0 V to 5 V range to

allow for additional protection in applications that are switching

from the higher voltage ranges.

This analog input structure allows the sampling of the differential

signal between IN+ and IN−. By using this differential input,

small signals common to both inputs are rejected as shown in

Figure 29, which represents the typical CMRR over frequency.

Table 6 for pin details and the Hardware

section and Software Configuration section for

VCC

IN+ OR IN–

VEE

C

PIN

Figure 28. AD7610 Simplified Analog Input

D1

D2

0 TO 5

RANGE ONLY

AVDD

D3

D4

R

IN

AGND

C

IN

6395-028

For instance, by using IN− to sense a remote signal ground,

ground potential differences between the sensor and the local

ADC ground are eliminated.

100

90

80

70

60

50

CMRR (dB)

40

30

20

10

0

1 10000

10 100 1000

FREQUENCY (kHz)

Figure 29. Analog Input CMRR vs. Frequency

06395-029

During the acquisition phase for ac signals, the impedance of

the analog inputs, IN+ and IN−, can be modeled as a parallel

combination of Capacitor C

the series connection of R

capacitance. R

is typically 5 kΩ and is a lumped component

IN

and the network formed by

PIN

and CIN. C

IN

is primarily the pin

PIN

comprised of serial resistors and the on resistance of the switches.

C

is primarily the ADC sampling capacitor and depending on

IN

the input range selected is typically 48 pF in the 0 V to 5 V range,

typically 24 pF in the 0 V to 10 V and ±5 V ranges and typically

12 pF in the ±10 V range. During the conversion phase, when

the switches are opened, the input impedance is limited to C

PIN

Since the input impedance of the AD7610 is very high, it can be

directly driven by a low impedance source without gain error.

To further improve the noise filtering achieved by the AD7610

analog input circuit, an external, one-pole RC filter between the

amplifier’s outputs and the ADC analog inputs can be used, as

shown in

Figure 27. However, large source impedances signifiantly affect the ac performance, especially total harmonic

distortion (THD). The maximum source impedance depends

on the amount of THD that can be tolerated. The THD degrades

as a function of the source impedance and the maximum input

frequency.

.

Rev. 0 | Page 19 of 32

Page 20

AD7610

The

DRIVER AMPLIFIER CHOICE

Although the AD7610 is easy to drive, the driver amplifier must

meet the following requirements:

• For multichannel, multiplexed applications, the driver

amplifier and the AD7610 analog input circuit must be

able to settle for a full-scale step of the capacitor array at a

16-bit level (0.0015%). For the amplifier, settling at 0.1% to

0.01% is more commonly specified. This differs significantly

from the settling time at a 16-bit level and should be verified

prior to driver selection. The

low noise and high gain bandwidth and meets this settling

time requirement even when used with gains of up to 13.

• The noise generated by the driver amplifier needs to be

kept as low as possible to preserve the SNR and transition

noise performance of the AD7610. The noise coming from

the driver is filtered by the external 1-pole low-pass filter

as shown in

Figure 27. The SNR degradation due to the

amplifier is

⎛

⎜

⎜

SNR

LOSS

log20

=

⎜

⎜

⎜

⎝

where:

is the noise of the ADC, which is:

V

NADC

V

INp-p

22

10

SNR

20

V =

NADC

f

is the cutoff frequency of the input filter (3.9 MHz).

–3dB

N is the noise factor of the amplifier (+1 in buffer

configuration).

e

is the equivalent input voltage noise density of the op

N

amp, in nV/√Hz.

The driver needs to have a THD performance suitable to

•

that of the AD7610.

Figure 15 shows the THD vs. frequency

that the driver should exceed.

AD8021 op amp combines ultra-

⎞

⎟

⎟

⎟

⎟

()

NefV

N

⎟

⎠

NADC

V

NADC

π

2

+

dB

−23

2

AD8021 meets these requirements and is appropriate for

almost all applications. The

AD8021 needs a 10 pF external

compensation capacitor that should have good linearity as an

NPO ceramic or mica type. Moreover, the use of a noninverting

+1 gain arrangement is recommended and helps to obtain the

best signal-to-noise ratio.

AD8022 can also be used when a dual version is needed

The

and a gain of 1 is present. The

AD829 is an alternative in appli-

cations where high frequency (above 100 kHz) performance is not

required. In applications with a gain of 1, an 82 pF compensation

capacitor is required. The

AD8610 is an option when low bias

current is needed in low frequency applications.

Since the AD7610 uses a large geometry, high voltage input

switch, the best linearity performance is obtained when using

the amplifier at its maximum full power bandwidth. Gaining

the amplifier to make use of the more dynamic range of the

ADC results in increased linearity errors. For applications

requiring more resolution, the use of an additional amplifier

with gain should precede a unity follower driving the AD7610.

Table 8 for a list of recommended op amps.

See

Table 8. Recommended Driver Amplifiers

Amplifier Typical Application

ADA4841-x

12 V supply, very low noise, low distortion,

low power, low frequency

AD829 ±15 V supplies, very low noise, low frequency

AD8021 ±12 V supplies, very low noise, high frequency

AD8022

±12 V supplies, very low noise, high

frequency, dual

AD8610/AD8620

±13 V supplies, low bias current, low

frequency, single/dual

VOLTAGE REFERENCE INPUT/OUTPUT

The AD7610 allows the choice of either a very low temperature

drift internal voltage reference, an external reference or an external

buffered reference.

The internal reference of the AD7610 provides excellent performance and can be used in almost all applications. However, the

linearity performance is guaranteed only with an external reference.

Rev. 0 | Page 20 of 32

Page 21

AD7610

Internal Reference (REF = 5 V) (PDREF = Low, PDBUF = Low)

To use the internal reference, the PDREF and PDBUF inputs

must be low. This enables the on-chip band gap reference, buffer,

and TEMP sensor resulting in a 5.00 V reference on the REF pin.

The internal reference is temperature-compensated to 5.000 V

±35 mV. The reference is trimmed to provide a typical drift of

3 ppm/°C. This typical drift characteristic is shown in

Figure 19.

External 2.5 V Reference and Internal Buffer (REF = 5 V) (PDREF = High, PDBUF = Low)

To use an external reference with the internal buffer, PDREF

should be high and PDBUF should be low. This powers down

the internal reference and allows the 2.5 V reference to be applied

to REFBUFIN producing 5 V on the REF pin. The internal reference buffer is useful in multiconverter applications since a

buffer is typically required in these applications.

External 5 V Reference (PDREF = High, PDBUF = High)

To use an external reference directly on the REF pin, PDREF

and PDBUF should both be high. PDREF and PDBUF power

down the internal reference and the internal reference buffer,

respectively. For improved drift performance, an external reference such as the

ADR445 or ADR435 is recommended.

Reference Decoupling

Whether using an internal or external reference, the AD7610

voltage reference input (REF) has a dynamic input impedance;

therefore, it should be driven by a low impedance source with

efficient decoupling between the REF and REFGND inputs. This

decoupling depends on the choice of the voltage reference, but

usually consists of a low ESR capacitor connected to REF and

REFGND with minimum parasitic inductance. A 22 µF (X5R,

1206 size) ceramic chip capacitor (or 47 µF tantalum capacitor)

is appropriate when using either the internal reference or the

ADR445/ADR435 external reference.

The placement of the reference decoupling is also important to

the performance of the AD7610. The decoupling capacitor should

be mounted on the same side as the ADC right at the REF pin

with a thick PCB trace. The REFGND should also connect to

the reference decoupling capacitor with the shortest distance

and to the analog ground plane with several vias.

For applications that use multiple AD7610 or other PulSAR

devices, it is more effective to use the internal reference buffer

to buffer the external 2.5 V reference voltage.

The voltage reference temperature coefficient (TC) directly

impacts full scale; therefore, in applications where full-scale

accuracy matters, care must be taken with the TC. For instance, a

±15 ppm/°C TC of the reference changes full-scale by ±1 LSB/°C.

Temperature Sensor

When the internal reference is enabled (PDREF = PDBUF =

low), the on-chip temperature sensor output (TEMP) is enabled

and can be use to measure the temperature of the AD7610. To

improve the calibration accuracy over the temperature range, the

output of the TEMP pin is applied to one of the inputs of the

analog switch (such as

ADG779), and the ADC itself is used to

measure its own temperature. This configuration is shown in

Figure 30.

ANALOG INPUT

ADG779

C

C

Figure 30. Use of the Temperature Sensor

IN+

TEMP

AD7610

TEMPERATURE

SENSOR

POWER SUPPLIES

The AD7610 uses five sets of power supply pins:

AVDD: analog 5 V core supply

•

VCC: analog high voltage positive supply

•

VEE: high voltage negative supply

•

DVDD: digital 5 V core supply

•

•

OVDD: digital input/output interface supply

Core Supplies

The AVDD and DVDD supply the AD7610 analog and digital

cores respectively. Sufficient decoupling of these supplies is

required consisting of at least a 10 F capacitor and 100 nF on

each supply. The 100 nF capacitors should be placed as close as

possible to the AD7610. To reduce the number of supplies needed,

the DVDD can be supplied through a simple RC filter from the

analog supply, as shown in

High Voltage Supplies

The high voltage bipolar supplies, VCC and VEE are required

and must be at least 2 V larger than the maximum input, V

For example, if using the bipolar 10 V range, the supplies should

be ±12 V minimum. Sufficient decoupling of these supplies is

also required consisting of at least a 10 F capacitor and 100 nF

on each supply. For unipolar operation, the VEE supply can be

grounded with some slight THD performance degradation.

Digital Output Supply

The OVDD supplies the digital outputs and allows direct interface

with any logic working between 2.3 V and 5.25 V. OVDD should

be set to the same level as the system interface. Sufficient decoupling is required consisting of at least a 10 F capacitor and 100 nF

with the 100 nF placed as close as possible to the AD7610.

Figure 27.

.

IN

06395-030

Rev. 0 | Page 21 of 32

Page 22

AD7610

Power Sequencing

The AD7610 is independent of power supply sequencing and is

very insensitive to power supply variations on AVDD over a wide

frequency range as shown in

80

75

INT REF

70

65

60

55

PSRR (dB)

50

45

40

35

30

1 10000

10 100 1000

Figure 31. AVDD PSRR vs. Frequency

Figure 31.

EXT REF

FREQUENCY (kHz)

06395-031

Power Dissipation vs. Throughput

The AD7610 automatically reduces its power consumption at

the end of each conversion phase. During the acquisition phase,

the operating currents are very low, which allows a significant

power savings when the conversion rate is reduced (see

Figure 32).

This feature makes the AD7610 ideal for very low power, batteryoperated applications.

It should be noted that the digital interface remains active even

during the acquisition phase. To reduce the operating digital supply

currents even further, drive the digital inputs close to the power

rails (that is, OVDD and OGND).

1000

100

10

POWER DISSIPATION (mW)

Power Down

Setting PD = high powers down the AD7610, thus reducing

supply currents to their minimums as shown in

Figure 23. When

the ADC is in power down, the current conversion (if any) is

completed and the digital bus remains active. To further reduce

the digital supply currents, drive the inputs to OVDD or OGND.

Power down can also be programmed with the configuration

register. See the

Software Configuration section for details. Note

that when using the configuration register, the PD input is a

don’t care and should be tied to either high or low.

CONVERSION CONTROL

The AD7610 is controlled by the

CNVST

on

is all that is necessary to initiate a conversion. Detailed

timing diagrams of the conversion process are shown in

Once initiated, it cannot be restarted or aborted, even by the

power-down input, PD, until the conversion is complete. The

CNVST

signal operates independently of CS and RD signals.

t

1

CNVST

BUSY

MODE

t

3

t

5

t

4

CONVERT ACQUIREACQUIRE CONVERT

t

7

Figure 33. Basic Conversion Timing

Although

CNVST

is a digital signal, it should be designed with

special care with fast, clean edges, and levels with minimum

overshoot, undershoot, or ringing.

The

CNVST

trace should be shielded with ground and a low value

(such as 50 Ω) serial resistor termination should be added close

to the output of the component that drives this line.

For applications where SNR is critical, the

have very low jitter. This can be achieved by using a dedicated

oscillator for

CNVST

generation, or by clocking

high frequency, low jitter clock, as shown in

CNVST

t

2

t

6

input. A falling edge

Figure 33.

t

8

CNVST

signal should

CNVST

with a

Figure 27.

6395-033

1

1 1000000

10 100 1000 10000 100000

SAMPLING RAT E (kSPS)

PDREF = PDBUF = HIG H

06395-032

Figure 32. Power Dissipation vs. Sample Rate

Rev. 0 | Page 22 of 32

Page 23

AD7610

A

INTERFACES

DIGITAL INTERFACE

The AD7610 has a versatile digital interface that can be set up

as either a serial or a parallel interface with the host system. The

serial interface is multiplexed on the parallel data bus. The AD7610

digital interface also accommodates 2.5 V, 3.3 V, or 5 V logic. In

most applications, the OVDD supply pin is connected to the host

system interface 2.5 V to 5.25 V digital supply. Finally, by using

2C

the OB/

coding can be used.

Two signals,

one of these signals is high, the interface outputs are in high

impedance. Usually,

in multicircuit applications and is held low in a single AD7610

design.

the data bus.

RESET

The RESET input is used to reset the AD7610. A rising edge on

RESET aborts the current conversion (if any) and tristates the

data bus. The falling edge of RESET resets the AD7610 and clears

the data bus and configuration register. See

RESET timing details.

input pin, both twos complement or straight binary

CS

and RD, control the interface. When at least

CS

allows the selection of each AD7610

RD

is generally used to enable the conversion result on

Figure 34 for the

CS = RD = 0

CNVST

BUSY

DATA

BUS

t

t

1

t

10

t

3

PREVIOUS CONVERSION DATA NEW DATA

4

t

11

Figure 35. Master Parallel Data Timing for Reading (Continuous Read)

Slave Parallel Interface

In slave parallel reading mode, the data can be read either after

each conversion, which is during the next acquisition phase, or

during the following conversion, as shown in

Figure 36 and

Figure 37, respectively. When the data is read during the conversion, it is recommended that it is read only during the first half

of the conversion phase. This avoids any potential feedthrough

between voltage transients on the digital interface and the most

critical analog conversion circuitry.

CS

06395-035

t

9

RESET

BUSY

DATA

BUS

t

8

CNVST

Figure 34. RESET Timing

PARALLEL INTERFACE

The AD7610 is configured to use the parallel interface when

PA R

SER/

Master Parallel Interface

Data can be continuously read by tying CS and RD low, thus

requiring minimal microprocessor connections. However, in

this mode, the data bus is always driven and cannot be used in

shared bus applications (unless the device is held in RESET).

Figure 35 details the timing for this mode.

is held low.

RD

BUSY

DAT

BUS

6395-034

Figure 36. Slave Parallel Data Timing for Reading (Read After Convert)

CS = 0

CNVST,

RD

BUSY

DATA

BUS

t

t

3

t

12

12

CURRENT

CONVERSION

t

1

PREVIOUS

CONVERSION

t

13

t

4

t

13

06395-036

06395-037

Figure 37. Slave Parallel Data Timing for Reading (Read During Convert)

Rev. 0 | Page 23 of 32

Page 24

AD7610

8-Bit Interface (Master or Slave)

The BYTESWAP pin allows a glueless interface to an 8-bit bus.

As shown in

Figure 38, when BYTESWAP is low, the LSB byte

is output on D[7:0] and the MSB is output on D[15:8]. When

BYTESWAP is high, the LSB and MSB bytes are swapped; the

LSB is output on D[15:8] and the MSB is output on D[7:0]. By

connecting BYTESWAP to an address line, the 16-bit data can

be read in two bytes on either D[15:8] or D[7:0]. This interface

can be used in both master and slave parallel reading modes.

CS

RD

BYTESWAP

PINS D[15:8]

PINS D[7:0]

HI-Z

HI-Z

Figure 38. 8-Bit and 16-Bit Parallel Interface

HIGH BYTE L OW BYTE

t

12

LOW BYTE HIGH BYTE

t

12

t

HI-Z

13

HI-Z

SERIAL INTERFACE

The AD7610 has a serial interface (SPI-compatible) multiplexed

on the data pins D[15:2]. The AD7610 is configured to use the

PA R

serial interface when SER/

Data Interface

The AD7610 outputs 16 bits of data, MSB first, on the SDOUT pin.

This data is synchronized with the 16 clock pulses provided on

the SDCLK pin. The output data is valid on both the rising and

falling edge of the data clock.

Serial Configuration Interface

The AD7610 can be configured through the serial configuration

register only in serial mode as the serial configuration pins are

also multiplexed on the data pins D[15:12]. See the

Configuration

section and Software Configuration section for

more information.

is held high.

Hardware

06395-038

MASTER SERIAL INTERFACE

The pins multiplexed on D[10:2] and used for the master serial

INT

interface are: DIVSCLK[0], DIVSCLK[1], EXT/

INVSCLK, RDC, SDOUT, SDCLK and SYNC.

Internal Clock (SER/

PAR

= High, EXT/

INT

The AD7610 is configured to generate and provide the serial

INT

data clock, SDCLK, when the EXT/

pin is held low. The

AD7610 also generates a SYNC signal to indicate to the host

when the serial data is valid. The SDCLK, and the SYNC signals

can be inverted, if desired using the INVSCLK and INVSYNC

inputs, respectively. Depending on the input, RDC, the data can

be read during the following conversion or after each conver-

Figure 39 and Figure 40 show detailed timing diagrams of

sion.

these two modes.

Read After Convert (RDC = Low, DIVSCLK[1:0] = [0 to 3])

Setting RDC = low, allows the read after conversion mode.

Since the AD7610 is limited to 250kSPS and the time between

conversions, t2 = 4μs, this mode is the most recommended

serial mode. Unlike the other serial modes, the BUSY signal

returns low after the 16 data bits are pulsed out and not at the

end of the conversion phase, resulting in a longer BUSY width

Table 4 for BUSY timing specifications). The

(See

DIVSCLK[1:0] inputs control the SDCLK period and SDOUT

data rate. As a result, the maximum throughput can only be

achieved in two of the DIVSCLK[1:0] settings. In this mode, the

AD7610 generates a discontinuous SDCLK however, a fixed

period and hosts supporting both SPI and serial ports can also

be used.

Read During Convert (RDC = High)

Setting RDC = high, allows the master read (previous conversion result) during conversion mode. In this mode, the serial

clock and data toggle at appropriate instances, minimizing

potential feed through between digital activity and critical

conversion decisions. In this mode, the SDCLK period changes

since the LSBs require more time to settle and the SDCLK is

derived from the SAR conver-sion cycle. In this mode, the

AD7610 generates a discontinuous SDCLK of two different

periods and the host should use an SPI interface.

, INVSYNC,

= Low)

Rev. 0 | Page 24 of 32

Page 25

AD7610

CS, RD

CNVST

EXT/INT = 0

t

3

RDC/SDIN = 0 INVSCLK = INVSYNC = 0

BUSY

SYNC

SDCLK

SDOUT

t

29

t

14

t

15

X

t

16

t

22

t

18

t

19

t

20

123 141516

D15 D14 D2 D1 D0

t

28

t

30

t

25

t

t

21

t

23

24

t

26

t

27

06395-039

Figure 39. Master Serial Data Timing for Reading (Read After Convert)

CS, RD

CNVST

BUSY

SYNC

SDCLK

SDOUT

EXT/INT = 0

t

1

t

3

t

17

t

14

t

15

t

18

D15 D14 D2 D1 D0X

t

16

t

22

RDC/SDIN = 1 INVSCLK = INVSYNC = 0

t

19

t20t

21

123 141516

t

23

t

25

t

24

t

26

t

27

06395-040

Figure 40. Master Serial Data Timing for Reading (Read Previous Conversion During Convert)

Rev. 0 | Page 25 of 32

Page 26

AD7610

+

=

CNVST

SLAVE SERIAL INTERFACE

The pins multiplexed on D[11:4] used for slave serial interface are:

INT

EXT/

External Clock (SER/

Setting the EXT/

externally supplied serial data clock on the SDCLK pin. In this

mode, several methods can be used to read the data. The external

serial clock is gated by

data can be read after each conversion or during the following

conversion. A clock can be either normally high or normally low

when inactive. For detailed timing diagrams, see

Figure 43.

While the AD7610 is performing a bit decision, it is important

that voltage transients be avoided on digital input/output pins,