Datasheet AD707KR-REEL7, AD707KR-REEL, AD707KR, AD707KN, AD707JR-REEL7 Datasheet (Analog Devices)

...Page 1

AD707

7

62

8

1

3

4

5

NULL

NULL

–IN

+IN

–V

S

+V

S

OUTPUT

NC

NC = NO CONNECT

NOTE: PIN 4 CONNECTED

TO CASE

a

Ultralow Drift Op Amp

AD707

FEATURES

Very High DC Precision

15 mV max Offset Voltage

0.1 mV/8C max Offset Voltage Drift

0.35 mV p-p max Voltage Noise (0.1 Hz to 10 Hz}

8 V/mV min Open-Loop Gain

130 dB min CMRR

120 dB min PSRR

1 nA max Input Bias Current

AC Performance

0.3 V/ms Slew Rate

0.9 MHz Closed-Loop Bandwidth

Dual Version: AD708

Available in Tape and Reel in Accordance with

EIA-481A Standard

PRODUCT DESCRIPTION

The AD707 is a low cost, high precision op amp with state-ofthe-art performance that makes it ideal for a wide range of

precision applications. The offset voltage spec of less than 15 µV

is the best available in a bipolar op amp, and maximum input

offset current is 1.0 nA. The top grade is the first bipolar

monolithic op amp to offer a maximum offset voltage drift of

0.1 µV/°C, and offset current drift and input bias current drift

are both specified at 25 pA/°C maximum.

The AD707’s open-loop gain is 8 V/µV minimum over the full

±10 V output range when driving a 1 kΩ load. Maximum input

voltage noise is 350 nV p-p (0.1 Hz to 10 Hz). CMRR and

PSRR are 130 dB and 120 dB minimum, respectively.

The AD707 is available in versions specified over commercial,

industrial and military temperature ranges. It is offered in 8-pin

plastic mini-DIP, small outline (SOIC), hermetic cerdip and

hermetic TO-99 metal can packages. Chips, MIL-STD-883B,

Rev. C, and tape & reel parts are also available.

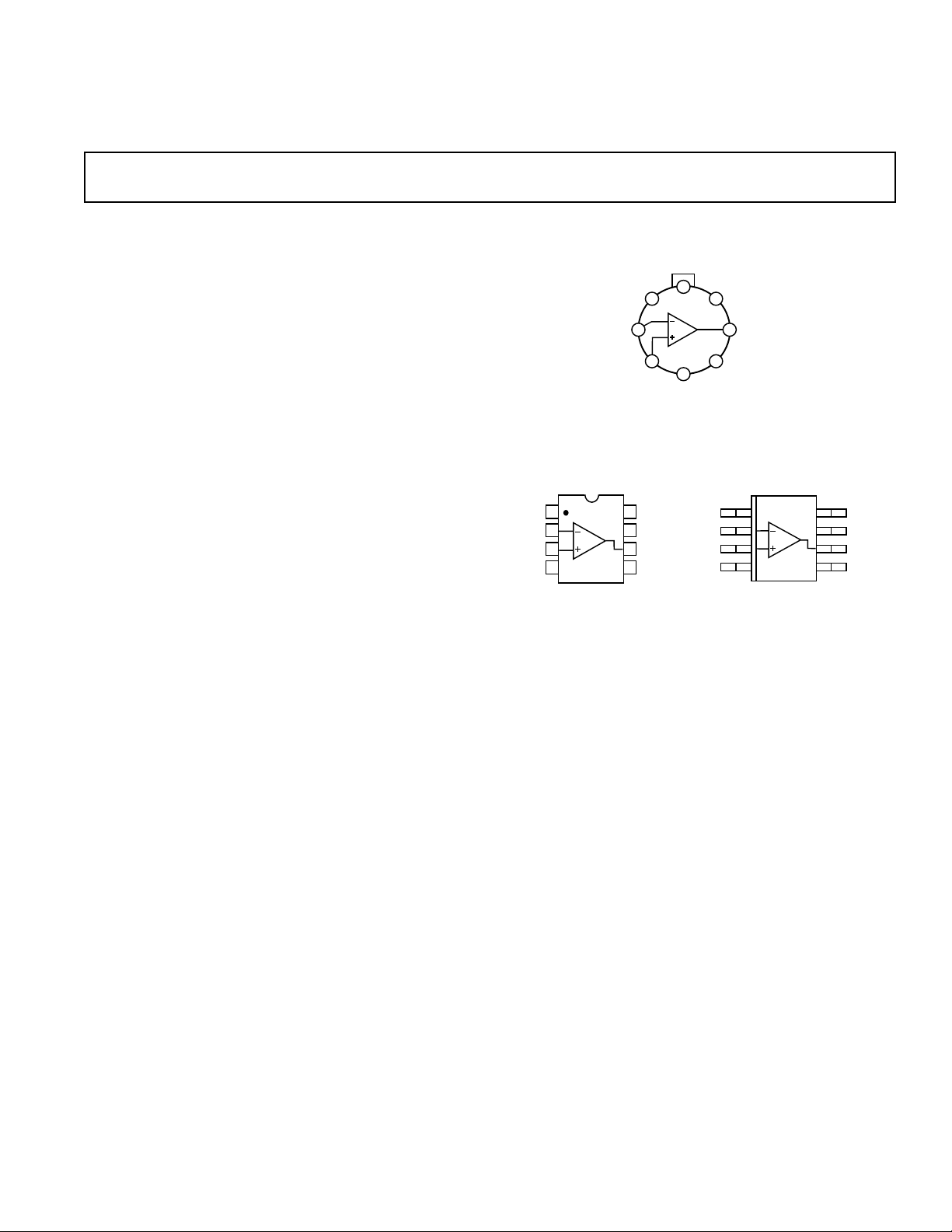

CONNECTION DIAGRAMS

TO-99 (H) Package

Plastic (N) and

Cerdip (Q) Packages SOIC (R) Package

NULL

1

–IN

2

+IN

3

–V

4

S

NC = NO CONNECT

AD707

8

7

6

5

NULL

+V

S

OUTPUT

NC

NULL

–IN

+IN

–V

S

NC = NO CONNECT

1

4

AD707

NULL

8

+V

S

OUTPUT

NC

5

APPLICATION HIGHLIGHTS

1. The AD707’s 13 V/µV typical open-loop gain and 140 dB

typical common-mode rejection ratio make it ideal for

precision instrumentation applications.

2. The precision of the AD707 makes tighter error budgets

possible at a lower cost.

3. The low offset voltage drift and low noise of the AD707 allow

the designer to amplify very small signals without sacrificing

overall system performance.

4. The AD707 can be used where chopper amplifiers are

required, but without the inherent noise and application

problems.

5. The AD707 is an improved pin-for-pin replacement for the

LT1001.

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

© Analog Devices, Inc., 1995

Page 2

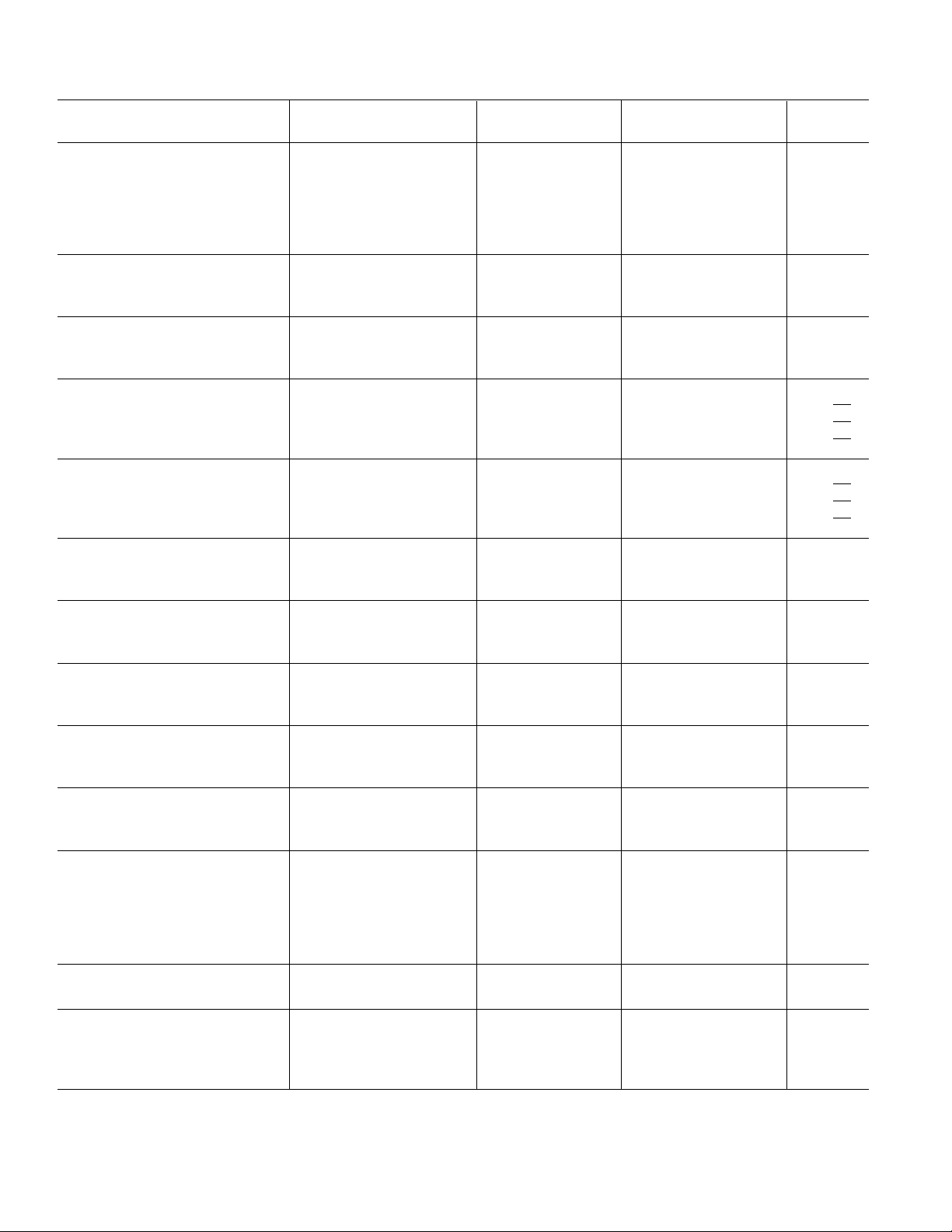

AD707–SPECIFICATIONS

(@ +258C and 615 V, unless otherwise noted)

AD707J/A AD707K/B

Conditions Min Typ Max Min Typ Max Units

INPUT OFFSET VOLTAGE

Initial 30 90 10 25 µV

vs. Temperature 0.3 1.0 0.1 0.3 µV/°C

to T

T

MIN

MAX

50 100 15 45 µV

Long-Term Stability 0.3 0.3 µV/month

Adjustment Range R2 = 20 kΩ (Figure 19) ± 4 ±4mV

INPUT BIAS CURRENT 1.0 2.5 0.5 2.0 nA

T

MIN

to T

MAX

2.0 4.0 1.5 4.0 nA

Average Drift 15 40 15 40/40/40 pA/°C

OFFSET CURRENT V

= 0 V 0.5 2.0 0.3 1.5 nA

CM

to T

T

MIN

MAX

2.0 4.0 1.0 2.0 nA

Average Drift 2 40 1 25/25/35 pA/°C

INPUT VOLTAGE NOISE 0.1 Hz to 10 Hz 0.23 0.6 0.23 0.6 µV p-p

f = 10 Hz 10.3 28 10.3 18 nV/√

f = 100 Hz 10.0 13.0 10.0 12 nV/√

Hz

Hz

f = 1 kHz 9.6 11.0 9.6 11.0 nV/√Hz

INPUT CURRENT NOISE 0.1 Hz to 10 Hz 14 35 14 30 pA p-p

f = 10 Hz 0.32 0.9 0.32 0.8 pA/√

f = 100 Hz 0.14 0.27 0.14 0.23 pA/√

Hz

Hz

f = 1 kHz 0.12 0.18 0.12 0.17 pA/√Hz

COMMON-MODE

REJECTION RATIO V

OPEN-LOOP GAIN V

= ±13 V 120 140 130 140 dB

CM

T

to T

R

T

MIN

O

LOAD

MIN

MAX

= ±10 V

≥ 2 kΩ 3 13 5 13 V/µV

to T

MAX

120 140 120 140 dB

3 13 3 13 V/µV

POWER SUPPLY

REJECTION RATIO V

= ±3 V to ± 18 V 110 130 115 130 dB

S

T

MIN

to T

MAX

110 130 110 130 dB

FREQUENCY RESPONSE

Closed-Loop Bandwidth 0.4 0.9 0.4 0.9 MHz

Slew Rate 0.12 0.3 0.12 0.3 V/µs

INPUT RESISTANCE

Differential 24 100 45 200 MΩ

Common Mode 200 300 GΩ

OUTPUT CHARACTERISTICS

Voltage R

≥ 10 kΩ 13.5 14 13.5 14 ±V

LOAD

≥ 2 kΩ 12.5 13.0 12.5 13.0 ±V

R

LOAD

≥ 1 kΩ 12.0 12.5 12.0 12.5 ±V

R

LOAD

≥ 2 kΩ

R

LOAD

T

MIN

to T

MAX

12.0 13.0 12.0 13.0 ±V

OPEN-LOOP OUTPUT

RESISTANCE 60 60 Ω

POWER SUPPLY

Current, Quiescent 2.5 3 2.5 3 mA

Power Consumption, No Load V

NOTES

All min and max specifications are guaranteed. Specifications in boldface are tested on all production units at final electrical test. Results from those tests are used to

calculate outgoing quality levels.

Specifications subject to change without notice.

= ±15 V 75 90 75 90 mW

S

V

= ±3 V 7.5 9.0 7.5 9.0 mW

S

–2–

REV. B

Page 3

AD707

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±22 V

Internal Power Dissipation

2

. . . . . . . . . . . . . . . . . . . . 500 mW

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±V

1

S

Output Short Circuit Duration . . . . . . . . . . . . . . . . Indefinite

Differential Input Voltage . . . . . . . . . . . . . . . . . +V

and –V

S

S

Storage Temperature Range (Q, H) . . . . . . –65°C to +150°C

Storage Temperature Range (N, R) . . . . . . . –65°C to +125°C

Lead Temperature Range (Soldering 60 sec) . . . . . . . +300°C

NOTES

1

Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2

8-pin plastic package: θJA = 165°C/Watt; 8-pin cerdip package: θJA = 110°C/Watt;

8-pin small outline package: θJA = 155°C/Watt; 8-pin header package: θJA =

200°C/Watt.

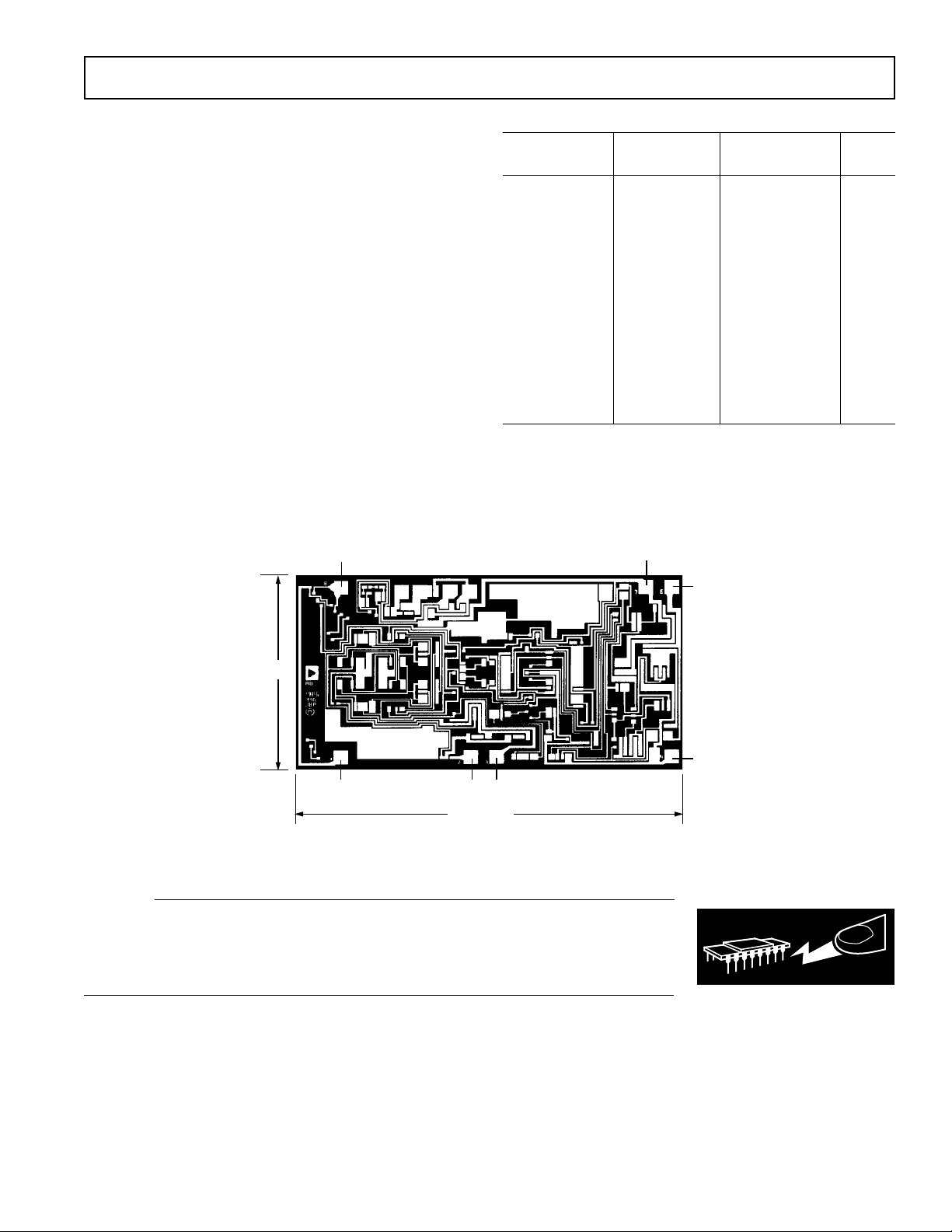

METALIZATION PHOTOGRAPH

Dimensions shown in inches and (mm).

Contact factory for latest dimensions.

NULL

8

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

AD707AH –40°C to +85°C 8-Pin Metal Can H-08A

AD707AQ –40°C to +85°C 8-Pin Ceramic DIP Q-8

AD707AR –40°C to +85°C 8-Pin Plastic SOIC SO-8

AD707AR-REEL –40°C to +85°C 8-Pin Plastic SOIC SO-8

AD707AR-REEL7 –40°C to +85°C 8-Pin Plastic SOIC SO-8

AD707BQ –40°C to +85°C 8-Pin Ceramic DIP Q-8

AD707JN 0°C to +70°C 8-Pin Plastic DIP N-8

AD707JR 0°C to +70°C 8-Pin Plastic SOIC SO-8

AD707JR-REEL 0°C to +70°C 8-Pin Plastic SOIC SO-8

AD707JR-REEL7 0°C to +70°C 8-Pin Plastic SOIC SO-8

AD707KN 0°C to +70°C 8-Pin Plastic DIP N-8

AD707KR 0°C to +70°C 8-Pin Plastic SOIC SO-8

AD707KR-REEL 0°C to +70°C 8-Pin Plastic SOIC SO-8

AD707KR-REEL7 0°C to +70°C 8-Pin Plastic SOIC SO-8

+V

S

7

0.059

(1.51)

3

1

NULL

2

+IN

–IN

0.110 (2.79)

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD707 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

6

V

OUT

4

–V

S

WARNING!

ESD SENSITIVE DEVICE

REV. B –3–

Page 4

AD707–Typical Characteristics

LOAD RESISTANCE – Ω

OUTPUT VOLTAGE – V p -p

35

15

0

10 100 10k

1k

10

25

20

30

5

± 15V SUPPLIES

FREQUENCY – Hz

OUTPUT IMPEDANCE – Ω

100

0.0001

0.1 100k

1 10 100 1k 10k

10

1

0.1

0.001

0.01

IO = 1mA

AV = +1000

AV = +1

10

0%

100

90

TIME – 1sec/Div

VOLTAGE NOISE – 100nV/Div

+V

S

–0.5

–1.0

–1.5

+1.5

+1.0

+0.5

COMMOM-MODE VOLTAGE LIMIT – V

(REFERRED TO SUPPLY VOLTAGES)

–V

S

0255101520

+V

–V

SUPPLY VOLTAGE – ±V

Figure 1. Input Common-Mode

Range vs. Supply Voltage

4

3

2

DUAL-IN-LINE PACKAGE

1

CHANGE IN OFFSET – µV

0

04

PLASTIC (N) or CERDIP (Q)

METAL CAN (H) PACKAGE

123

TIME AFTER POWER ON – Minutes

+V

S

–0.5

–1.0

–1.5

+1.5

+1.0

OUTPUT VOLTAGE SWING – ± V

+0.5

(REFERRED TO SUPPLY VOLTAGES)

–V

S

0255101520

Figure 2. Output Voltage Swing

vs. Supply Voltage

100

90

80

– 55°C TO +125°C

70

60

50

40

30

NUMBER OF UNITS

20

10

0

–0.4 –0.3 0.4

+ V

OUT

RL = 2kΩ

@ +25°C

– V

OUT

SUPPLY VOLTAGE – ±V

256 UNITS

TESTED

–0.2 –0.1 0 0.1 0.2 0.3

OFFSET VOLTAGE DRIFT – µV/°C

Figure 3. Output Voltage Swing

vs. Load Resistance

Figure 4. Offset Voltage Warm-Up

Drift

40

30

20

INVERTING OR

10

NONINVERTING INPUT CURRENT – mA

0

0 1 100

DIFFERENTIAL VOLTAGE – ±V

Figure 7. Input Current vs.

Differential Input Voltage

Figure 5. Typical Distribution of

Offset Voltage Drift

45

40

Hz

√

35

30

25

20

15

10

INPUT VOLTAGE NOISE – nV/

5

10

0

0.01 0.1 100110

I/F CORNER

0.7Hz

FREQUENCY – Hz

Figure 8. Input Noise Spectral

Density

–4–

Figure 6. Output Impedance vs.

Frequency

Figure 9. 0.1 Hz to 10 Hz Voltage

Noise

REV. B

Page 5

AD707

20mV/DIV

CH1

TIME – 2µs/DIV

FREQUENCY – Hz

OPEN-LOOP GAIN – V/µV

140

80

0

0.01 0.1

1 10 100 1k 10k 100k 1M 10M

120

100

40

10

60

20

PHASE – Degrees

30

180

0

90

150

60

120

RL = 2kΩ

CL = 1000pF

PHASE

MARGIN

=58°

GAIN

FREQUENCY – Hz

POWER SUPPLY REJECTION – dB

160

0

0.001 0.01 100k

0.1 1 10 100 1k 10k

140

80

60

40

20

120

100

20mV/DIV

CH1

TIME – 2µs/DIV

16

14

12

10

8

6

4

OPEN-LOOP GAIN – V/µV

2

0

–60 –40 140–20 0 20 40 60 80 100 120

RL = 1kΩ

= ±10V

V

OUT

TEMPERATURE – °C

Figure 10. Open-Loop Gain vs.

Temperature

160

140

120

100

80

60

40

20

COMMON-MODE REJECTION – dB

0

0.1 1

10 100 1k 10k 100k 1M

FREQUENCY – Hz

16

14

12

10

8

6

4

OPEN-LOOP GAIN – V/µV

2

0

0255 101520

SUPPLY VOLTAGE – V

R

= 1kΩ

LOAD

Figure 11. Open-Loop Gain vs.

Supply Voltage

35

F

= 3kHz

MAX

30

25

20

15

10

OUTPUT VOLTAGE – V p-p

5

0

1k 10k 1M100k

FREQUENCY – Hz

RL = 2kΩ

+25°C

V

= ± 15V

S

Figure 12. Open-Loop Gain and

Phase vs. Frequency

Figure 13. Common-Mode

Rejection vs. Frequency

4

3

2

1

SUPPLY CURRENT – mA

0

03 24

Figure 16. Supply Current vs.

Supply Voltage

REV. B –5–

6 9 12 15 18 21

SUPPLY VOLTAGE – ±V

+125°C

+25°C

–55°C

Figure 14. Large Signal Frequency

Response

Figure 17. Small Signal Transient

Response; A

C

= 50 pF

L

= +1, RL = 2 kΩ,

V

Figure 15. Power Supply Rejection

vs. Frequency

Figure 18. Small Signal Transient

Response; A

C

= 1000 pF

L

= +1, RL = 2 kΩ,

V

Page 6

AD707

OFFSET NULLING

The input offset voltage of the AD707 is the lowest available in

a bipolar op amp, but if additional nulling is required, the

circuit shown in Figure 19 offers a null range of 200 µV. For

wider null capability, omit R1 and substitute a 20 kΩ potentiometer for R2.

+V

S

0.1µF

R1

10kΩ

OFFSET

ADJUST

R2

7

2kΩ

1

2

AD707

3

8

6

0.1µF

4

–V

S

Figure 19. External Offset Nulling and Power Supply

Bypassing

GAIN LINEARITY INTO A 1 kΩ LOAD

The gain and gain linearity of the AD707 are the highest

available among monolithic bipolar amplifiers. Unlike other dc

precision amplifiers, the AD707 shows no degradation in gain or

gain linearity when driving loads in excess of 1 kΩ over a ±10 V

output swing. This means high gain accuracy is assured over the

output range. Figure 20 shows the gain of the AD707, OP07, and

the OP77 amplifiers when driving a 1 kΩ load.

The AD707 will drive 10 mA of output current with no significant effect on its gain or linearity.

AD707

OPERATION WITH A GAIN OF 100

Demonstrating the outstanding dc precision of the AD707 in

practical applications, Table I shows an error budget calculation

for the gain of –100 configuration shown in Figure 21.

Table I. Error Budget

Maximum Error Contribution

Av = 100 (C Grade)

Error Source (Full Scale: V

V

OS

I

OS

15 µV/100 mV = 150 ppm

(100 Ω)(1 nA)/100 mV = 1 ppm

Gain (2 kΩ Load) (100 V/8 × 10

= 10 V, VIN = 100 mV)

OUT

6

)100 mV = 13 ppm

Noise 0.35 µV/100 mV = 4 ppm

Drift (0.1 V/°C)/100 mV = 1 ppm/°C

V

OS

= 168 ppm

+1 ppm/°C

Total Unadjusted Error

@ +25°C = 168 ppm > 12 Bits

@ –55°C to +125°C = 268 ppm > 11 Bits

With Offset Calibrated Out

@ +25°C = 17 ppm > 15 Bits

@ –55°C to +125°C = 117 ppm > 13 Bits

10kΩ

+V

S

0.1µF

100Ω

V

IN

99Ω

7

2

0.1µF

6

V

OUT

AD707

3

4

–V

S

OP07

OP77

@ +25°C

CHANGE IN OFFSET VOLTAGE – 10µV/Div

R

= 1kΩ

LOAD

–15 15–10 –5 0 5 10

OUTPUT VOLTAGE – V

Figure 20. Gain Linearity of the AD707 vs.

Other DC Precision Op Amps

Figure 21. Gain of –100 Configuration

Although the initial offset voltage of the AD707 is very low, it is

nonetheless the major contributor to system error. In cases

requiring additional accuracy, the circuit shown in Figure 19

can be used to null out the initial offset voltage. This method

will also cancel the effects of input offset current error. With the

offsets nulled, the AD707C will add less than 17 ppm of error.

This error budget assumes no error in the resistor ratio and no

errors from power supply variation (the 120 dB minimum PSRR

of the AD707C makes this a good assumption). The external

resistors can cause gain error from mismatch and drift over

temperature.

REV. B–6–

Page 7

AD707

18-BIT SETTLING TIME

Figure 22 shows the AD707 settling to within 80 µV of its final

value for a 20 V output step in less than 100 µs (in the test con-

figuration shown in Figure 23). To achieve settling to 18 bits,

any amplifier specified to have a gain of 4 V/µV would appear to

be good enough, however, this is not the case. In order to truly

achieve 18-bit accuracy, the gain linearity must be better than

4 ppm.

The gain nonlinearity of the AD707 does not contribute to the

error, and the gain itself only contributes 0.1 ppm. The gain

error, along with the V

and VOS drift errors do not comprise

OS

1 LSB of error in an 18-bit system over the military temperature

range. If calibration is used to null offset errors, the AD707

resolves up to 20 bits at +25°C.

REFERENCE

SIGNAL

10V/Div

D.U.T.

OUTPUT

ERROR

50µV/Div

OUTPUT:

10V/Div

140 dB CMRR INSTRUMENTATION AMPLIFIER

The extremely tight dc specifications of the AD707 enable the

designer to build very high performance, high gain instrumentation amplifiers without having to select matched op amps for the

crucial first stage. For the second stage, the lowest grade AD707

is ideally suited. The CMRR is typically the same as the high

grade parts, but does not exact a premium for drift performance

(which is less critical in the second stage). Figure 24 shows an

example of the classic instrumentation amp. Figure 25 shows

that the circuit has at least 140 dB of common-mode rejection

for a ±10 V common-mode input at a gain of 1001 (R

2

3

9.9kΩ

R

CM

20,000

R

G

10kΩ

A3

R2

R4

AD707

–IN

+IN

AD707

3

A1

2

10kΩ

R

G

10kΩ

AD707

2

A2

3

CIRCUIT GAIN = –––––– + 1

6

R2

10kΩ

R1

10kΩ

6

200Ω

G

6

= 20 Ω).

FLAT-TOP

PULSE

GENERATOR

DATA

DYNAMICS

5109

OR

EQUIVALENT

TIME – 50µs/Div

Figure 22. 18-Bit Settling

2x HP1N6263

200kΩ

2

OP27

4

–V

1.9kΩ

D.U.T.

AD707

4

–V

7

+V

S

S

2kΩ

100Ω

7

+V

S

S

3

10µF

0.1µF

2kΩ

V

IN

2kΩ

2

3

10µF

0.1µF

6

6

10µF

10µF

V

ERROR

0.1µF

0.1µF

x 100

Figure 24. A 3 Op Amp Instrumentation Amplifier

High CMRR is obtained by first adjusting RCM until the output

does not change as the input is swept through the full commonmode range. The value of R

, should then be selected to achieve

G

the desired gain. Matched resistors should be used for the

output stage so that R

value Of R

, the lower the noise introduced by potentiometer

CM

is as small as possible. The smaller the

CM

wiper vibrations. To maintain the CMRR at 140 dB over a

20°C range, the resistor ratios in the output stage, R1/R2 and

R3/R4, must track each other better than 10 ppm/°C.

INPUT

COMMON-MODE

SIGNAL: 10V/Div

COMMON-MODE

ERROR REFERRED

TO INPUT: 5µV/Div

TIME – 2 sec/Div

CH1

CH2

Figure 25. Instrumentation Amplifier

Common-Mode Rejection

Figure 23. Op Amp Settling Time Test Circuit

REV. B –7–

Page 8

AD707

PRECISION CURRENT TRANSMITTER

The AD707’s excellent dc performance, especially the low offset

voltage, low offset voltage drift and high CMRR, makes it

possible to make a high precision voltage-controlled current

transmitter using a variation of the Howland Current Source

circuit (Figure 26). This circuit provides a bidirectional load

current which is derived from a differential input voltage.

R3

100kΩ

2

V

IN

3

R1

100kΩ

t

= ––––––– –––

L

AD707

V

R

SCALE

R4

100kΩ

0.1µF

+V

S

7

6

0.1µF

4

–V

S

R2

100kΩ

IN

R2

(

R1

R

SCALE

R

)

L

I

L

Figure 26. Precision Current Source/Sink

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

The performance and accuracy of this circuit will depend almost

entirely on the tolerance and selection of the resistors. The scale

resistor (R

) and the four feedback resistors directly affect

SCALE

the accuracy of the load current and should be chosen carefully

or trimmed.

As an example of the accuracy achievable, assume I

10 mA, and the available V

= 10 mV/10 mA = 1 Ω

R

SCALE

due to the AD707C:

I

ERROR

Maximum I

ERROR

is only 10 mV.

IN

= 2(VOS)/R

(100 k/R

I

OS

+ 2(VOS Drift)/R

SCALE

SCALE

)

must be

L

SCALE

+

= 2 (15 µV)/l Ω +2 (0.1 µV/°C)/l Ω

+ 1 nA (100 k)/l Ω (1.5 nA @ 125°C)

= 30 µA + 0.2 µA/°C + 100 µA

(150 µA @ 125°C)

= 130 µA/10 mA = 1.3% @ 25°C

= 180 µA/10 mA = 1.8% @ 125°C

Low drift, high accuracy resistors are required to achieve high

precision.

C1164a–2–12/95

0.335 (8.51)

0.305 (7.75)

0.370 (9.40)

0.335 (8.51)

0.185 (4.70)

0.165 (4.19)

0.040 (1.02) MAX

0.045 (1.14)

0.010 (0.25)

0.005 (0.13) MIN

PIN 1

0.200

(5.08)

MAX

0.200 (5.08)

0.125 (3.18)

0.050

(1.27)

MAX

1

0.405 (10.29) MAX

0.023 (0.58)

0.014 (0.36)

8-Pin Metal Can

(H-08A)

REFERENCE PLANE

0.750 (19.05)

0.500 (12.70)

0.250 (6.35)

MIN

0.200

(5.08)

0.019 (0.48)

0.016 (0.41)

0.021 (0.53)

0.016 (0.41)

BASE & SEATING PLANE

8-Pin Cerdip

(Q-8)

0.055 (1.4) MAX

58

0.310 (7.87)

0.220 (5.59)

4

0.060 (1.52)

0.015 (0.38)

0.070 (1.78)

0.100

(2.54)

0.030 (0.76)

BSC

BSC

SEATING

PLANE

0.100

(2.54)

BSC

0.150

(3.81)

MIN

3

4

2

0.100

(2.54)

BSC

5

1

0.034 (0.86)

0.027 (0.69)

0.320 (8.13)

0.290 (7.37)

0.015 (0.38)

0.008 (0.20)

15°

0°

6

8

45°

BSC

0.160 (4.06)

0.110 (2.79)

7

0.045 (1.14)

0.027 (0.69)

0.210 (5.33)

MAX

0.160 (4.06)

0.115 (2.93)

0.022 (0.558)

0.014 (0.356)

0.1574 (4.00)

0.1497 (3.80)

0.0098 (0.25)

0.0040 (0.10)

SEATING

PLANE

0.430 (10.92)

0.348 (8.84)

8

14

PIN 1

0.100

(2.54)

BSC

0.1968 (5.00)

0.1890 (4.80)

8

PIN 1

0.0500

(1.27)

BSC

8-Pin Plastic DIP

(N-8)

5

0.280 (7.11)

0.240 (6.10)

0.325 (8.25)

0.130

(3.30)

MIN

SEATING

PLANE

0.300 (7.62)

0.060 (1.52)

0.015 (0.38)

0.070 (1.77)

0.045 (1.15)

8-Lead SOIC

(SO-8)

5

0.2440 (6.20)

41

0.2284 (5.80)

0.0688 (1.75)

0.0532 (1.35)

0.0192 (0.49)

0.0138 (0.35)

0.0098 (0.25)

0.0075 (0.19)

0.015 (0.381)

0.008 (0.204)

0.0196 (0.50)

0.0099 (0.25)

8°

0°

0.0500 (1.27)

0.0160 (0.41)

0.195 (4.95)

0.115 (2.93)

PRINTED IN U.S.A.

x 45°

REV. B–8–

Loading...

Loading...