Page 1

12-Bit, 65 MSPS

V

+

VINA

V

V

V

S

FEATURES

SNR = 90 dB in 150 kHz bandwidth (to Nyquist

@ 61.44 MSPS)

Worst harmonic = 83 dBc (to Nyquist @ 61.44 MSPS)

Integrated dual-channel ADC:

Sample rates up to 65 MSPS

IF sampling frequencies to 200 MHz

Internal ADC voltage reference

Integrated ADC sample-and-hold inputs

Flexible analog input range (1 V to 2 V p-p)

Differential analog inputs

ADC clock duty cycle stabilizer

85 dB channel isolation/crosstalk

Integrated wideband digital downconverter (DDC):

Crossbar switched DDC inputs

Digital resampling for noninteger decimation

Programmable decimating FIR filters

Flexible control for multicarrier and phased array

Dual AGC stages for output level control

Dual 16-bit parallel or 8-bit link output ports

User-configurable built-in self-test (BIST) capability

Energy-saving power-down modes

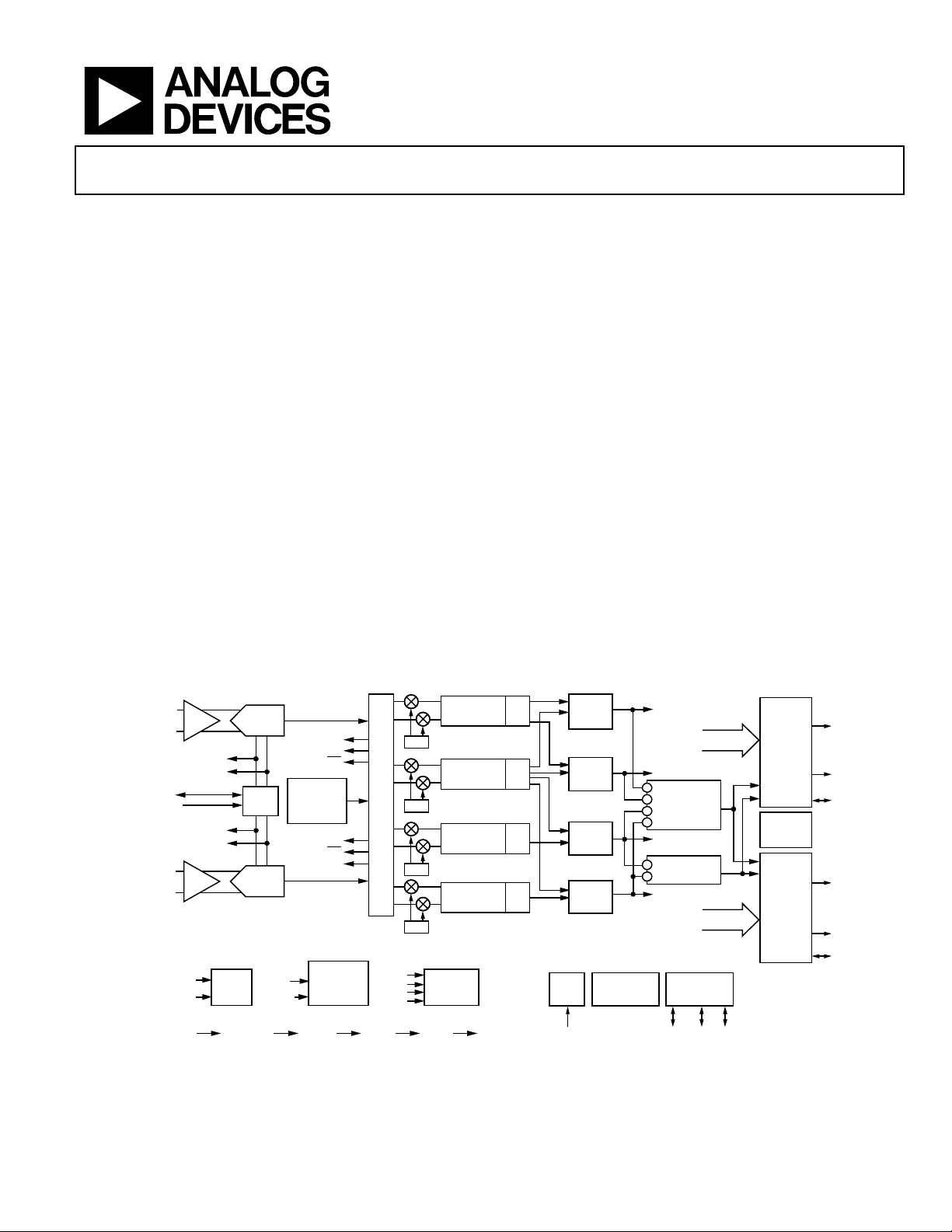

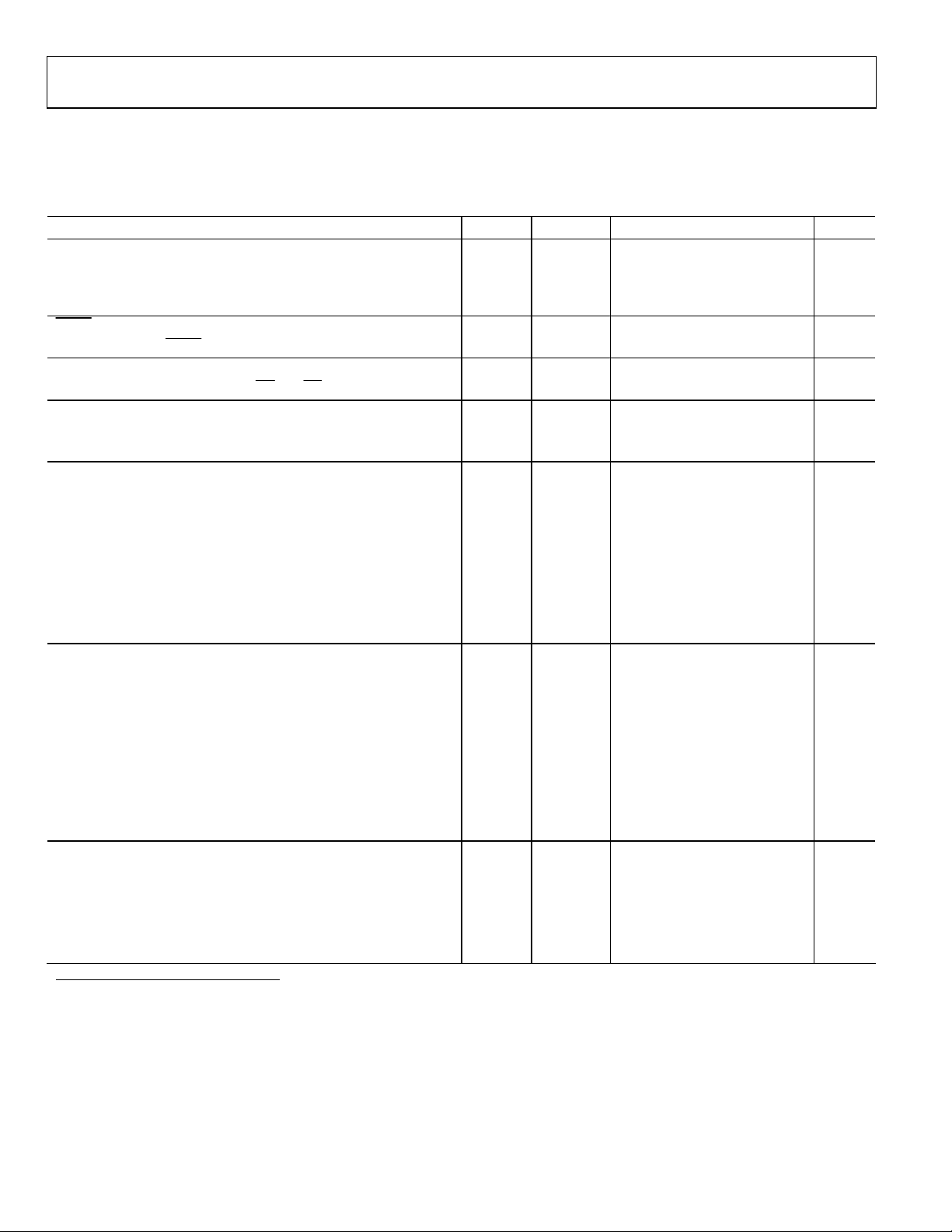

FUNCTIONAL BLOCK DIAGRAM

DUAL-CHANNEL 12-BIT A/D FRONT END WIDEBAND DIGITAL DOWNCONVERTER (DDC)

INA

SHA

–

REF

ENSE

INB+

SHA

INB–

PDWN

SHRDREF

+3.0AVDD +3.3VDDIO 2.5VDD AGND DGND

REFTA

REFBA

REFTB

REFBB

MODE

SELECT

CHANNEL

CHANNEL

ADC

A

VREF

ADC

B

ACLK

DUTYEN

12

CHANNEL A

/

OTRA

LIA

LIA

PSEUDO

RANDOM

NOISE

SEQUENCE

LIB

LIB

OTRB

12

/

CHANNEL B

CLOCK

DUTY

CYCLE

STABILIZER

INPUT MATRIX

SYNCA

SYNCB

SYNCC

SYNCD

NCO

NCO

NCO

NCO

RCIC2

RESAMPLER

RCIC2

RESAMPLER

RCIC2

RESAMPLER

RCIC2

RESAMPLER

EXTERNAL

SYNC.

CIRCUIT

IF to Baseband Diversity Receiver

AD6652

APPLICATIONS

Communications

Diversity radio systems

Multimode digital receivers:

GSM, EDGE, PHS, AMPS, UMTS, WCDMA, CDMA-ONE,

IS95, IS136, CDMA2000, IMT-2000

I/Q demodulation systems

Smart antenna systems

General-purpose software radios

Broadband data applications

Instrumentation and test equipment

CIC5

CIC5

CIC5

CIC5

*DATA INTERLEAVING AND INTERPOLATING HB FILTER

RAM

COEF.

FILTER

CHANNEL 0

RAM

COEF.

FILTER

CHANNEL 1

RAM

COEF.

FILTER

CHANNEL 2

RAM

COEF.

FILTER

CHANNEL 3

DDC

CLK

CLK DATA CONT ADD

BUILT-IN

SELF-TEST

CIRCUITRY

TO OUTPUT PORTS

CHANNELS 0, 1, 2, 3

TO OUTPUT PORTS

TO OUTPUT

PORTS

TO OUTPUT PORTS

CHANNELS 0, 1, 2, 3

Figure 1.

RCF OUTPUTS

AGC A*

AGC B*

RCF OUTPUTS

PROGRAM

MICROPORT

/

/

833

PORT A

8-BIT DSP

LINK

OR

16-BIT

PARALLEL

OUTPUT

CONTROL

OUTPUT

MUX

CIRCUITRY

PORT B

8-BIT DSP

LINK

OR

16-BIT

PARALLEL

OUTPUT

CONTROL

/

03198-0-001

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

Page 2

AD6652

TABLE OF CONTENTS

Product Description......................................................................... 4

Gain Switching............................................................................ 31

Product Highlights....................................................................... 4

Specifications..................................................................................... 5

Recommended Operating Conditions ...................................... 5

ADC DC Specifications ............................................................... 5

ADC Switching Specifications.................................................... 5

ADC AC Specifications ............................................................... 6

Electrical Characteristics ............................................................. 7

General Timing Characteristics ................................................. 8

Microprocessor Port Timing Characteristics ........................... 9

Absolute Maximum Ratings.......................................................... 10

Thermal Characteristics ............................................................10

Test Level .....................................................................................10

ESD Caution................................................................................ 10

Pin Configuration and Function Descriptions........................... 11

Typical Performance Characteristics ...........................................14

Numerically Controlled Oscillator............................................... 33

Frequency Translation to Baseband......................................... 33

NCO Shadow Register............................................................... 33

NCO Frequency Hold-Off Register......................................... 33

Phase Offset................................................................................. 33

NCO Control Register............................................................... 33

Second-Order rCIC Filter ............................................................. 35

rCIC2 Scale Factor ..................................................................... 35

rCIC2 Output Level ................................................................... 36

rCIC2 Rejection.......................................................................... 36

Decimation and Interpolation Registers ................................. 36

rCIC2 Scale Register .................................................................. 36

Fifth-Order CIC Filter ................................................................... 37

CIC5 Rejection ........................................................................... 37

RAM Coefficient Filter .................................................................. 38

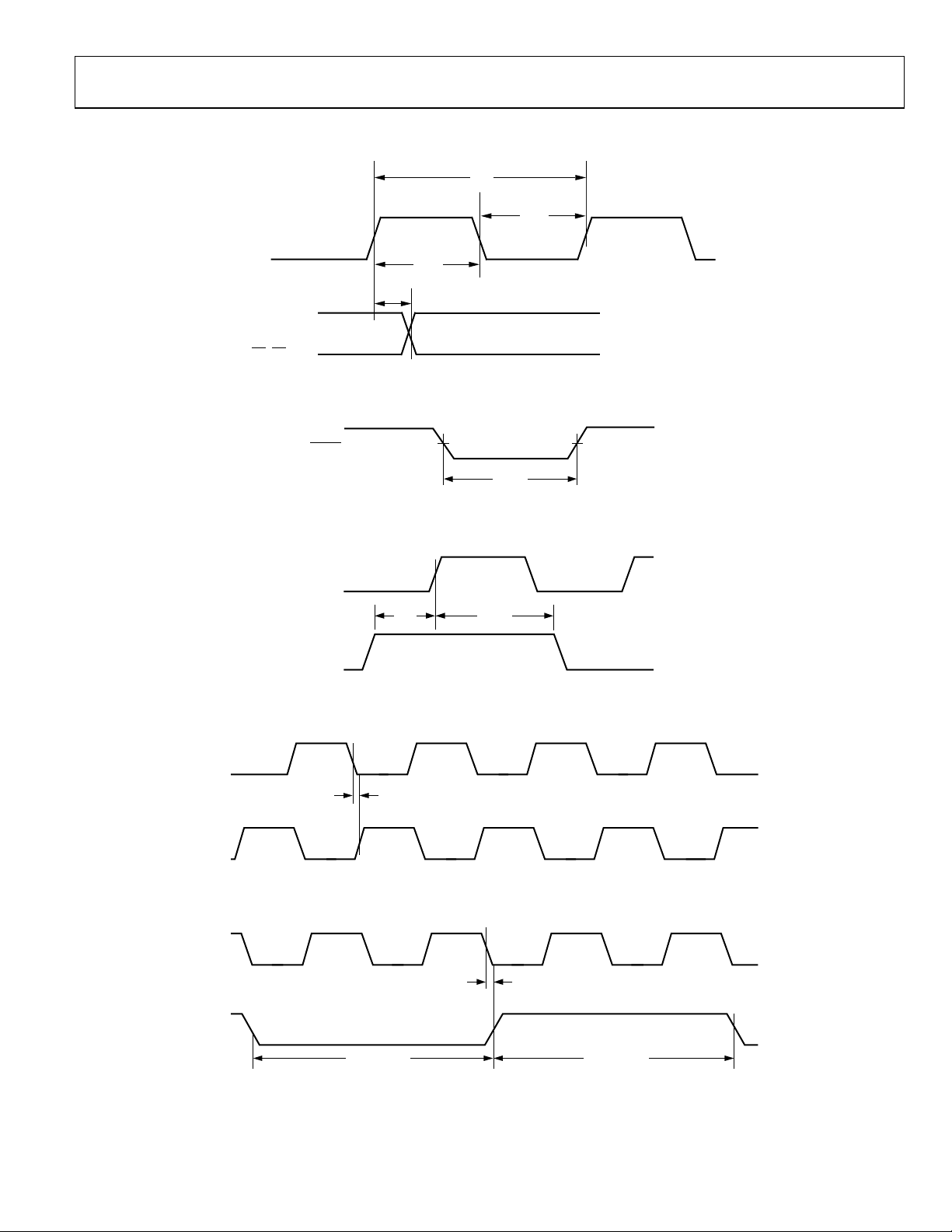

DDC Timing Diagrams .................................................................17

Terminology ....................................................................................23

ADC Equivalent Circuits........................................................... 23

Theory of Operation ...................................................................... 24

ADC Architecture ...................................................................... 24

Digital Downconverter Architecture Overview .........................29

Data Input Matrix....................................................................... 29

Numerically Controlled Oscillator...........................................29

Second-Order rCIC Filter .........................................................29

Fifth-Order CIC Filter ............................................................... 29

RAM Coefficient Filter ..............................................................29

Interpolating Half-Band Filters and AGC............................... 29

Control Register and Memory Map Address Notation .............31

DDC Input Matrix...................................................................... 31

DDC Data Latency ..................................................................... 31

RCF Decimation Register.......................................................... 38

RCF Decimation Phase.............................................................. 38

RCF Filter Length....................................................................... 38

RCF Output Scale Factor and Control Register..................... 39

Interpolating Half-Band Filters .................................................... 40

Automatic Gain Control................................................................ 41

AGC Loop ................................................................................... 41

Desired Signal Level Mode........................................................ 41

Synchronization.......................................................................... 44

User-Configurable Built-In Self-Test (BIST).............................. 45

RAM BIST................................................................................... 45

Channel BIST.............................................................................. 45

Channel/Chip Synchronization.................................................... 46

Start .............................................................................................. 46

Hop............................................................................................... 48

Rev. 0 | Page 2 of 76

Page 3

AD6652

Parallel Output Ports.......................................................................50

Pin_Sync Control Register.........................................................57

Channel Mode .............................................................................50

AGC Mode...................................................................................51

Master/Slave PCLK Modes........................................................52

Parallel Port Pin Functions ........................................................52

Link Port...........................................................................................53

Link Port Data Format ...............................................................53

Link Port Timing.........................................................................53

TigerSHARC Configuration......................................................54

External Memory Map ...................................................................55

Access Control Register (ACR).................................................56

Channel Address Register (CAR) .............................................56

Soft_Sync Control Register........................................................56

REVISION HISTORY

7/04—Revision 0: Initial Version

Sleep Control Register................................................................57

Data Address Registers...............................................................57

Channel Address Registers (CAR)............................................57

Input Port Control Registers .....................................................63

Output Port Control Registers ..................................................64

Microport Control......................................................................71

Applications .....................................................................................73

AD6652 Receiver Applications..................................................73

Design Guidelines.......................................................................73

AD6652 Evaluation Board and Software.....................................75

Outline Dimensions........................................................................76

Ordering Guide ...........................................................................76

Rev. 0 | Page 3 of 76

Page 4

AD6652

PRODUCT DESCRIPTION

The AD6652 is a mixed-signal IF to baseband receiver

consisting of dual 12-bit 65 MSPS ADCs and a wideband

multimode digital downconverter (DDC). The AD6652 is

designed to support communications applications where low

cost, small size, and versatility are desired. The AD6652 is also

suitable for other applications in imaging, medical ultrasound,

instrumentation, and test equipment.

The dual ADC core features a multistage differential pipelined

architecture with integrated output error correction logic. Both

ADCs feature wide bandwidth differential sample-and-hold

analog input amplifiers supporting a variety of user-selectable

input ranges. An integrated voltage reference eases design

considerations. A duty cycle stabilizer is provided to compensate for variations in the ADC clock duty cycle, allowing the

converters to maintain excellent performance.

ADC data outputs are internally connected directly to the

receiver’s digital downconverter (DDC) input matrix, simplifying layout and reducing interconnection parasitics. Overrange

bits are provided for each ADC channel to alert the user to

ADC clipping. Level indicator bits are also provided for each

DDC input port that can be used for external digital VGA

control.

The digital receiver has four reconfigurable channels and

provides extraordinary processing flexibility. The receiver input

matrix routes the ADC data to individual channels, or to all four

receive processing channels. Each receive channel has five

cascaded signal processing stages: a 32-bit frequency translator

(numerically controlled oscillator (NCO)), two fixed-coefficient

decimating filters (CIC), a programmable RAM coefficient

decimating FIR filter (RCF), and an interpolating half-band

filter/AGC stage. Following the CIC filters, one, several, or all

channels can be configured to use one, several, or all the RCF

filters. This permits the processing power of four 160-tap RCF

FIR filters to be combined or used individually.

After FIR filtering, data can be routed directly to the two

external 16-bit output ports. Alternatively, data can be routed

through two additional half-band interpolation stages, where up

to four channels can be combined (interleaved), interpolated,

and processed by an automatic gain control (AGC) circuit with

96 dB range. The outputs from the two AGC stages are also

routed directly to the two external 16-bit output ports. Each

output port has a 16-bit parallel output and an 8-bit link port to

permit seamless data interface with DSP devices such as the

TS-101 TigerSHARC® DSP. A multiplexer for each port selects

one of six data sources to appear on the device outputs pins.

digitizes a wide spectrum of IF frequencies and then downconverts the desired signals to baseband using individual

channel NCOs. The AD6652 provides user-configurable digital

filters for removal of undesired baseband components, and the

data is then passed on to an external DSP, where demodulation

and other signal processing tasks are performed to complete the

information retrieval process. Each receive channel is independently configurable to provide simultaneous reception of the

carrier to which it is tuned. This IF sampling architecture

greatly reduces component cost and complexity compared with

traditional analog techniques or less integrated digital methods.

High dynamic range decimation filters offer a wide range of

decimation rates. The RAM-based architecture allows easy

reconfiguration for multimode applications. The decimating

filters remove unwanted signals and noise from the channel of

interest. When the channel occupies less bandwidth than the

input signal, this rejection of out-of-band noise is referred to as

processing gain. By using large decimation factors, this processing gain can improve the SNR of the ADC by 20 dB or more. In

addition, the programmable RAM coefficient filter allows

antialiasing, matched filtering, and static equalization functions

to be combined in a single, cost-effective filter.

Flexible power-down options allow significant power savings,

when desired.

PRODUCT HIGHLIGHTS

• Integrated dual 12-bit 65 MSPS ADC.

• Integrated wideband digital downconverter (DDC).

• Proprietary, differential SHA input maintains excellent

SNR performance for input frequencies up to 200 MHz.

• Crossbar-switched digital downconverter input ports.

• Digital resampling permits noninteger relationships

between the ADC clock and the digital output data rate.

• Energy-saving power-down modes.

• 32-bit NCOs with selectable amplitude and phase dithering

for better than −100 dBc spurious performance.

• CIC filters with user-programmable decimation and

interpolation factors.

• 160-tap RAM coefficient filter for each DDC channel.

• Dual 16-bit parallel output ports and dual 8-bit link ports.

The AD6652 is part of the Analog Devices SoftCell® multimode

and multicarrier transceiver chipset. The SoftCell receiver

Rev. 0 | Page 4 of 76

• 8-bit microport for register programming, register read-

back, and coefficient memory programming.

Page 5

AD6652

SPECIFICATIONS

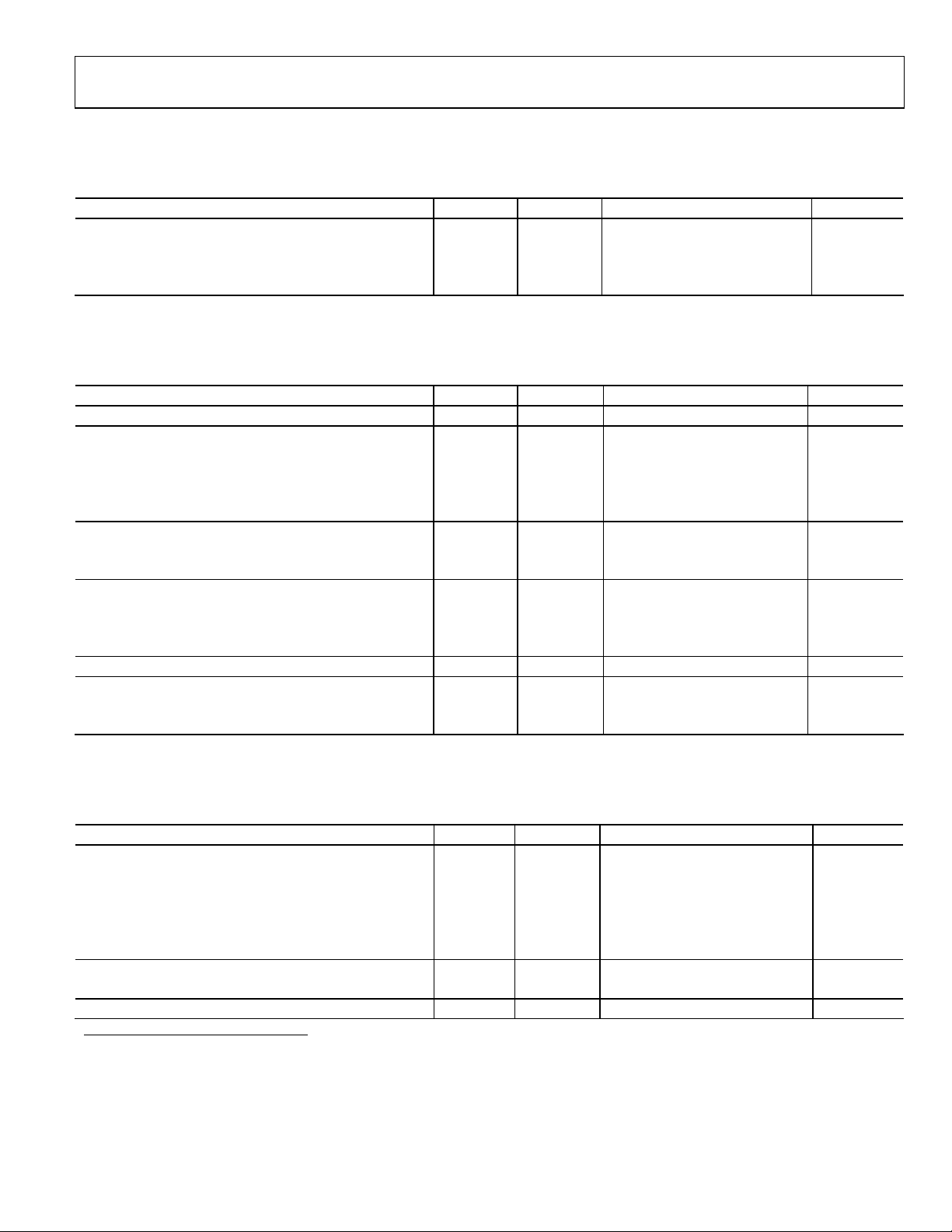

RECOMMENDED OPERATING CONDITIONS

Table 1.

Parameter Temp Test Level Min Typ Max Unit

AVDD Full IV 2.75 3.0 3.3 V

VDD Full IV 2.25 2.5 2.75 V

VDDIO Full IV 3.0 3.3 3.6 V

T

AMBIENT

ADC DC SPECIFICATIONS

AVDD = 3.0 V, VDD = 2.5 V, VDDIO = 3.3 V, 61.44 MSPS, −1.0 dBFS differential input, 1.0 V internal reference, unless otherwise noted.

Table 2.

Parameter (Conditions) Temp Test Level Min Typ Max Unit

RESOLUTION Full IV 12 Bits

INTERNAL VOLTAGE REFERENCE

Output Voltage Error (1 V Mode) Full IV ±5 ±35 mV

Load Regulation @ 1.0 mA Full V 0.8 mV

Output Voltage Error (0.5 V Mode) Full V ±2.5 mV

Load Regulation @ 0.5 mA Full V 0.1 mV

INPUT REFERRED NOISE

Input Span = 1 V Internal 25°C V 0.54 LSB rms

Input Span = 2 V Internal 25°C V 0.27 LSB rms

ANALOG INPUT

Input Span = 1.0 V Full IV 1 V p-p

Input Span = 2.0 V Full IV 2 V p-p

Input Capacitance Full V 7 pF

REFERENCE INPUT RESISTANCE Full V 7 kΩ

MATCHING CHARACTERISTICS

Offset Error Full V ±0.1 % FSR

Gain Error Full V ±0.1 % FSR

IV −40 +25 +85 °C

ADC SWITCHING SPECIFICATIONS

AVDD = 3.0 V, VDD = 2.5 V, VDDIO = 3.3 V, 61.44 MSPS, −1.0 dBFS differential input, 1.0 V internal reference, unless otherwise noted.

Table 3.

Parameter (Conditions) Temp Test Level Min Typ Max Unit

SWITCHING PERFORMANCE

Maximum Conversion Rate Full IV 65 MSPS

Minimum Conversion Rate Full V 1 MSPS

ACLK Period Full V 15.4 ns

ACLK Pulse Width High

ACLK Pulse Width Low1 Full V 6.2 ACLK/2 ns

DATA OUTPUT PARAMETERS

Wake-Up Time

2

OUT-OF-RANGE RECOVERY TIME Full V 2 Cycles

1

Duty cycle stabilizer enabled.

2

Wake-up time is dependent on the value of decoupling capacitors, typical values shown with 0.1 µF and 10 µF capacitors on REFT and REFB.

1

Full V 6.2 ACLK/2 ns

Full V 2.5 ms

Rev. 0 | Page 5 of 76

Page 6

AD6652

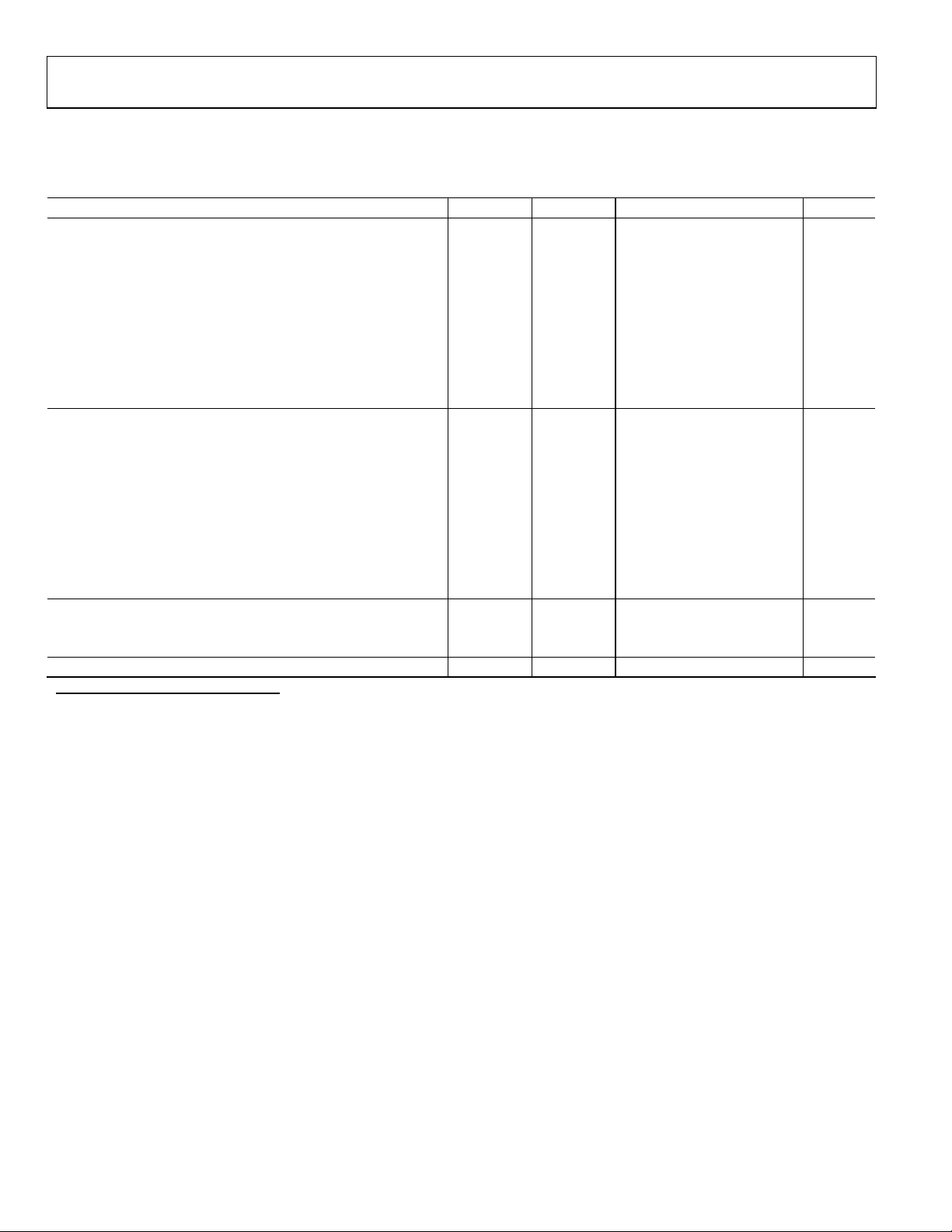

ADC AC SPECIFICATIONS

AVDD = 3.0 V, VDD = 2.5 V, VDDIO = 3.3 V, 61.44 MSPS, −1.0 dBFS differential input, 1.0 V internal reference.

Table 4.

Parameter (Conditions) Temp Test Level Min Typ Max Unit

SIGNAL-TO-NOISE RATIO1 (WITHOUT HARMONICS)

Analog Input Frequency 10.4 MHz 25°C V 90 dB

Full V 90 dB

25.0 MHz 25°C II 85 90 dB

Full V 90 dB

68.0 MHz 25°C II 84 89.5 dB

Full V 88.5 dB

101 MHz 25°C V 88.0 dB

150 MHz 25°C V 87.5 dB

200 MHz 25°C V 85 dB

WORST HARMONIC (2nd or 3rd)1

Analog Input Frequency 10.4 MHz 25°C V −85 dBc

Full V −83 dBc

25 MHz 25°C II −83 −71 dBc

Full V −80 dBc

68 MHz 25°C II −80 dBc

Full V −76 dBc

101 MHz 25°C V −79 dBc

150 MHz 25°C V −72 dBc

200 MHz 25°C V −69 dBc

TWO-TONE IMD REJECTION (TWO TONES SEPARATED BY 1 MHz)2

Analog Inputs = 15/16 MHz 25°C V −81 dBc

Analog Inputs = 55/56 MHz 25°C V −79 dBc

CHANNEL ISOLATION/CROSSTALK

1

Analog Input A or B = single tone @ −1 dB below full scale, 150 kHz DDC filter bandwidth.

2

Analog Input A or B = each single tone @ −7 dB below full scale, 5 MHz DDC filter bandwidth.

3

Analog Inputs A and B = each single tone @ −1 dB below full scale at 4.3 MHz and 68 MHz, 150 kHz DDC filter bandwidth.

3

Full V 85 dB

Rev. 0 | Page 6 of 76

Page 7

AD6652

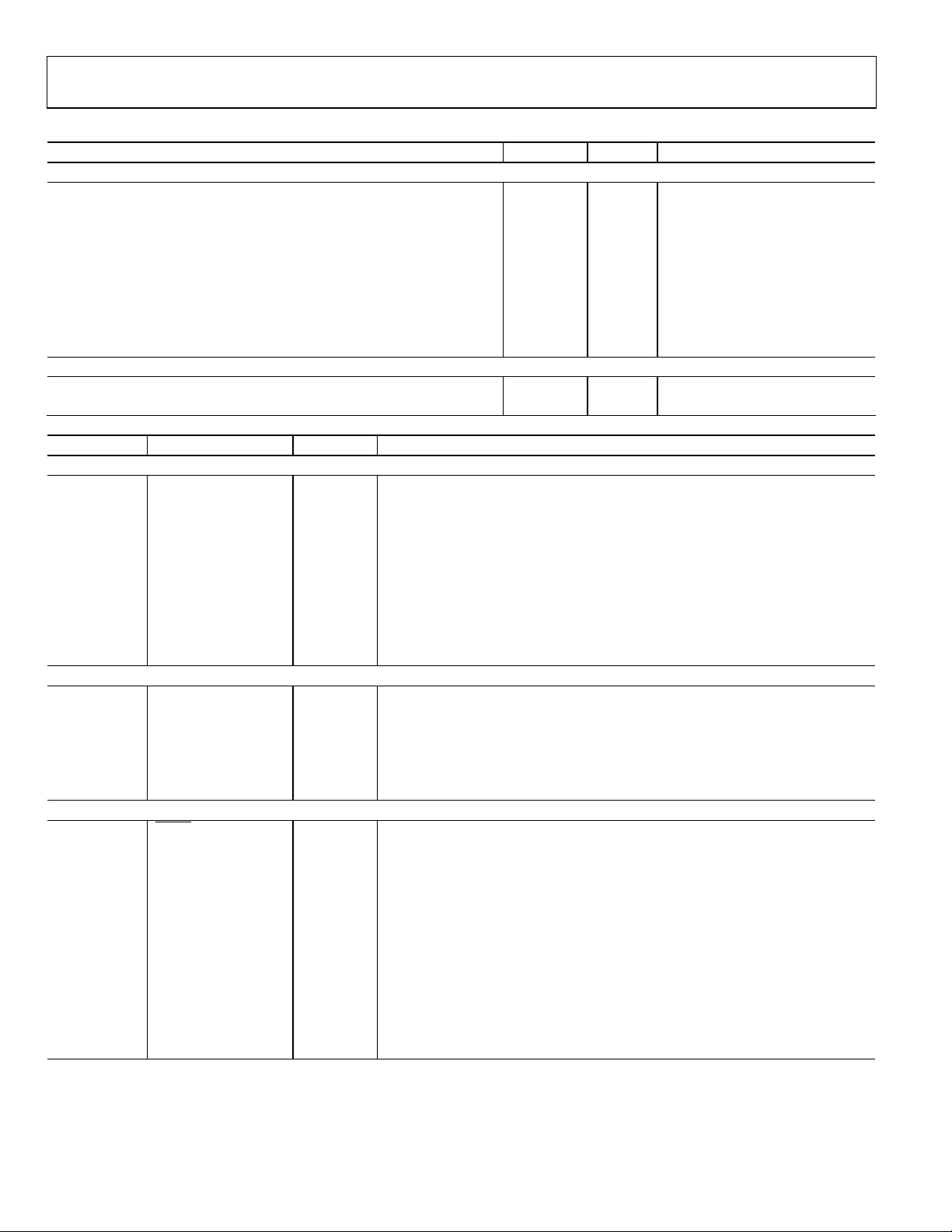

ELECTRICAL CHARACTERISTICS

AVDD = 3.0 V, VDD = 2.5 V, VDDIO = 3.3 V, 61.44 MSPS, −1.0 dBFS differential input, 1.0 V internal reference, unless otherwise noted.

Table 5.

Parameter (Conditions) Temp Test Level Min Typ Max Unit

LOGIC INPUTS

Logic Compatibility Full IV 3.3 V CMOS

Logic 1 Voltage Full IV 2.0 V

Logic 0 Voltage Full IV 0.8 V

Logic 1 Current Full IV −10 +10 µA

Logic 0 Current Full IV −10 +10 µA

Input Capacitance 25°C V 4 pF

LOGIC OUTPUTS

Logic Compatibility Full IV 3.3 V CMOS/TTL

Logic 1 Voltage (VOH) (IOH = 0.25 mA) Full IV 2.4 VDDIO − 0.2 V

Logic 0 Voltage (VOL) (IOL = 0.25 mA) Full IV 0.2 0.4 V

SUPPLY CURRENTS

Narrow Band (150 kHz BW) (61.44 MHz CLK)

Four Individual Channels

I

AVDD

I

VDD

I

VDDIO

CDMA (1.25MHz BW) (61.44 MHz CLK) Example

I

AVDD

I

VDD

I

VDDIO

1

WCDMA (5 MHz BW) (61.44 MHz CLK) Example1

I

AVDD

I

VDD

I

VDDIO

TOTAL POWER DISSIPATION

Narrow Band (150 kHz BW) (61.44 MHz CLK)

Four Individual Channels

CDMA (61.44 MHz)1

WCDMA (61.44 MHz)1

ADC in Standby and DDC in Sleep Mode

2

25°C II 160 200 215 mA

25°C II 240 280 300 mA

25°C II 25 40 45 mA

25°C V 200 mA

25°C V 336 mA

25°C V 68 mA

25°C V 200 mA

25°C V 330 mA

25°C V 89 mA

25°C II 1.2 1.5 1.6 W

25°C

25°C

25°C

V 1.7 W

V 1.7 W

V 2.3 mW

1

All signal processing stages and all DDC channels active.

2

ADC standby power measured with ACLK inactive.

Rev. 0 | Page 7 of 76

Page 8

AD6652

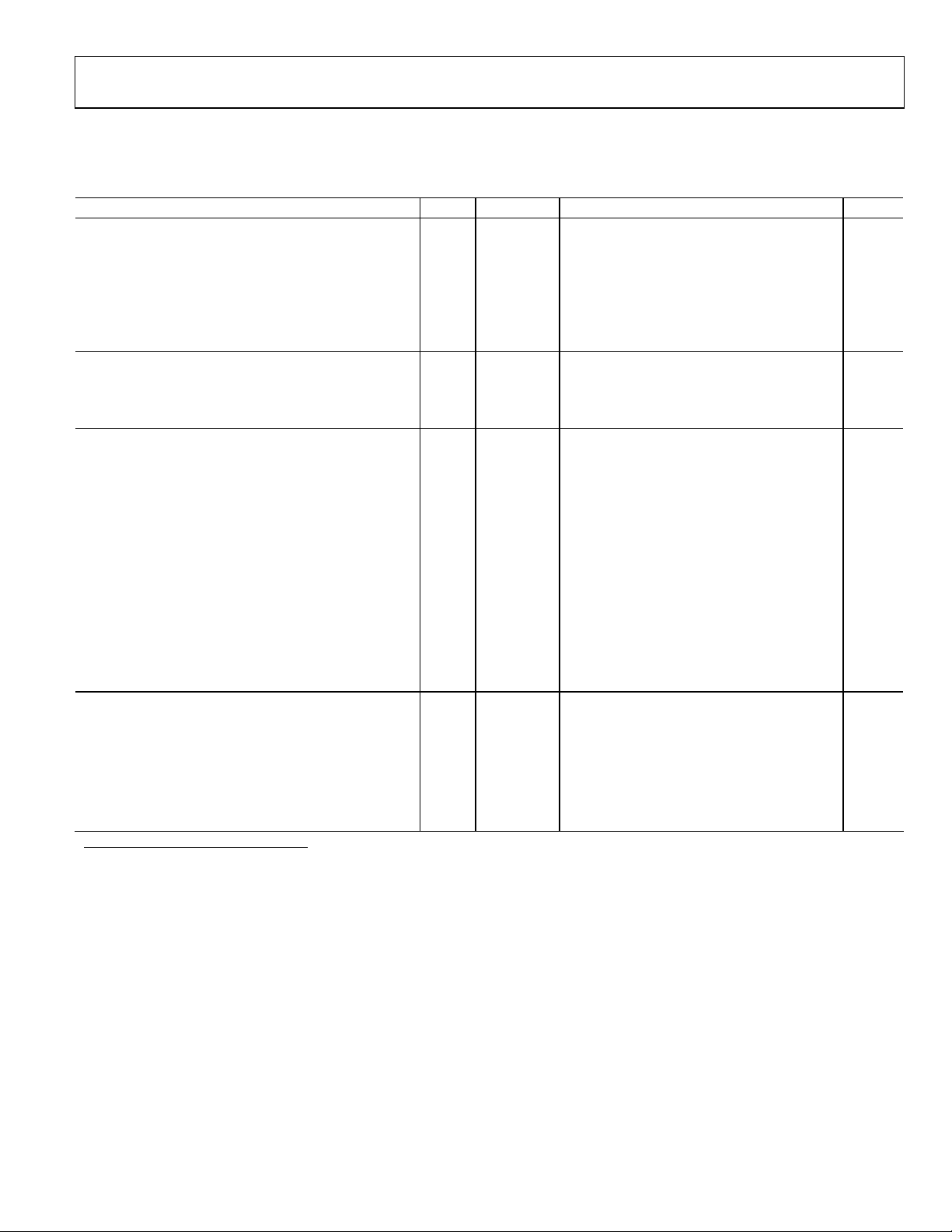

GENERAL TIMING CHARACTERISTICS

All timing specifications valid over VDD range of 2.25 V to 2.75 V and VDDIO range of 3.0 V to 3.6 V.

CLOAD = 40 pF on all outputs, unless otherwise specified.

Table 6.

Parameter (Conditions) Temp Test Level Min Typ Max Unit

CLK TIMING REQUIREMENTS

t

CLK

t

CLKL

t

CLKH

RESET TIMING REQUIREMENTS

t

RESL

LEVEL INDICATOR OUTPUT SWITCHING CHARACTERISTICS

t

DLI

SYNC TIMING REQUIREMENTS

t

SS

t

HS

PARALLEL PORT TIMING REQUIREMENTS (MASTER MODE)

Switching Characteristics

t

DPOCLKL

t

DPOCLKLL

t

DPREQ

t

DPP

Input Characteristics

t

SPA

t

HPA

PARALLEL PORT TIMING REQUIREMENTS (SLAVE MODE)

Switching Characteristics1

t

POCLK

t

POCLKL

t

POCLKH

t

DPREQ

t

DPP

Input Characteristics

t

SPA

t

HPA

LINK PORT TIMING REQUIREMENTS

Switching Characteristics1

t

RDLCLK

t

FDLCLK

t

RLCLKDAT

t

FLCLKDAT

1

The timing parameters for Px[15:0], PxREQ, and PxACK apply for Port A and B (x stands for A or B).

CLK Period Full IV 15.4 ns

CLK Width Low Full IV 6.2 t

CLK Width High Full IV 6.2 t

/2 ns

CLK

/2 ns

CLK

RESET Width Low

↑CLK to LI (LIA, LIA; LIB, LIB) Output Delay Time

SYNC(A,B,C,D) to ↑CLK Setup Time

SYNC(A,B,C,D) to ↑CLK Hold Time

1

↓CLK to ↑PCLK Delay (Divide-by-1)

↓CLK to ↑PCLK Delay (Divide-by-2, -4, or -8)

↑PCLK to ↑PxREQ Delay

↑PCLK to Px[15:0] Delay

PxACK to ↓PCLK Setup Time

PxACK to ↓PCLK Hold Time

Full IV 30.0 ns

Full IV 3.3 10.0 ns

Full IV 2.0 ns

Full IV 1.0 ns

Full IV 6.5 10.5 ns

Full IV 8.3 14.6 ns

1.0 ns

0.0 ns

7.0 ns

−3.0 ns

PCLK Period Full IV 12.5 ns

PCLK Low Period (when PCLK Divisor = 1) Full IV 2.0 0.5 × t

PCLK High Period (when PCLK Divisor = 1) Full IV 2.0 0.5 × t

↑PCLK to ↑PxREQ Delay

↑PCLK to Px[15:0] Delay

PxACK to ↓PCLK Setup Time

PxACK to ↓PCLK Hold Time

10.0 ns

11.0 ns

IV 1.0 ns

IV 1.0 ns

↑PCLK to ↑LxCLKOUT Delay

↓PCLK to ↓LxCLKOUT Delay

↑LCLKOUT to Lx[7:0] Delay

↓LCLKOUT to Lx[7:0] Delay

Full IV 2.5 ns

Full IV 0 ns

Full IV 0 2.9 ns

Full IV 0 2.2 ns

POCLK

POCLK

ns

ns

Rev. 0 | Page 8 of 76

Page 9

AD6652

MICROPROCESSOR PORT TIMING CHARACTERISTICS

All timing specifications valid over VDD range of 2.25 V to 2.75 V and VDDIO range of 3.0 V to 3.6 V.

CLOAD = 40 pF on all outputs, unless otherwise specified.

Table 7.

MICROPROCESSOR PORT, MODE INM (MODE = 0) Temp Test Level Min Typ Max Unit

MODE INM WRITE TIMING

t

t

t

t

t

t

t

SC

HC

HWR

SAM

HAM

DRDY

ACC

Control1 to ↑CLK Setup Time

Control1 to ↑CLK Hold Time

WR(R/W) to RDY(DTACK) Hold Time

Address/Data to WR(R/W) Setup Time

Address/Data to RDY(DTACK) Hold Time

WR(R/W) to RDY(DTACK) Delay

WR(R/W) to RDY(DTACK) High Delay

MODE INM READ TIMING

t

t

t

t

t

t

SC

HC

SAM

HAM

DRDY

ACC

Control1 to ↑CLK Setup Time

Control1 to ↑CLK Hold Time

Address to RD(DS) Setup Time

Address to Data Hold Time Full IV 5.0 ns

RD(DS) to RDY(DTACK) Delay

RD(DS) to RDY(DTACK) High Delay

MICROPROCESSOR PORT, MODE MNM (MODE = 1) Temp Test Level Min Typ Max Unit

MODE MNM WRITE TIMING

t

SC

t

HC

t

HDS

t

HRW

t

SAM

t

HAM

t

DDTACK

t

ACC

Control1 to ↑CLK Setup Time

Control1 to ↑CLK Hold Time

DS(RD) to DTACK(RDY) Hold Time

R/W(WR) to DTACK(RDY) Hold Time

Address/Data To R/W(WR) Setup Time

Address/Data to R/W(WR) Hold Time

DS(RD) to DTACK(RDY) Delay

R/W(WR) to DTACK(RDY) Low Delay

MODE MNM READ TIMING

t

SC

t

HC

t

HDS

t

SAM

t

HAM

t

DDTACK

t

ACC

Control1 to ↑CLK Setup Time

Control1 to ↑CLK Hold Time

DS(RD) to DTACK(RDY) Hold Time

Address to DS(RD) Setup Time

Address to Data Hold Time Full IV 5.0 ns

DS(RD) to DTACK(RDY) Delay

DS(RD) to DTACK(RDY) Low Delay

Full IV 2.0 ns

Full IV 2.5 ns

Full IV 7.0 ns

Full IV 3.0 ns

Full IV 5.0 ns

Full IV 8.0 ns

Full IV 4 × t

CLK

5 × t

CLK

9 × t

CLK

ns

Full IV 5.0 ns

Full IV 2.0 ns

Full IV 0.0 ns

Full IV 8.0 ns

Full IV 8 × t

CLK

10 × t

CLK

13 × t

CLK

ns

Full IV 2.0 ns

Full IV 2.5 ns

Full IV 8.0 ns

Full IV 7.0 ns

Full IV 3.0 ns

Full IV 5.0 ns

Full IV 8.0 ns

Full IV 4 × t

CLK

5 × t

CLK

9 × t

CLK

ns

Full IV 5.0 ns

Full IV 2.0 ns

Full IV 8.0 ns

Full IV 0.0 ns

Full IV 8.0 ns

Full IV 8 × t

CLK

10 × t

CLK

13 × t

CLK

ns

1

Specification pertains to control signals: R/W, (WR), DS, (RD), and CS.

Rev. 0 | Page 9 of 76

Page 10

AD6652

ABSOLUTE MAXIMUM RATINGS

Table 8.

Parameter Rating

ELECTRICAL

AVDD Voltage −0.3 V to +3.9 V

VDD Voltage −0.3 V to +2.75 V

VDDIO Voltage −0.3 V to +3.9 V

AGND, DGND −0.3 V to +0.3 V

ADC VINA, VINB Analog Input Voltage −0.3 V to AVDD + 0.3 V

ADC Digital Input Voltage −0.3 V to AVDD + 0.3 V

ADC OTRA, OTRB Digital Output Voltage

ADC VREF, REFA, REFB Input Voltage −0.3 V to AVDD + 0.3 V

DDC Digital Input Voltage −0.3 V to VDDIO + 0.3 V

DDC Digital Output Voltage −0.3 V to VDDIO + 0.3 V

ENVIRONMENTAL

Operating Temperature Range

(Ambient)

Maximum Junction Temperature

Under Bias

Storage Temperature Range (Ambient) −65°C to +150°C

−0.3 V to VDDIO + 0.3 V

−40°C to +85°C

150°C

Stresses above those listed under the Absolute Maximum

Ratings may cause permanent damage to the device. This is a

stress rating only; functional operation of the device at these or

any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL CHARACTERISTICS

256-lead CSPBGA, 17 mm sq.

= 23°C/W, still air.

θ

JA

Estimate based on JEDEC JC51-2 model using horizontally

positioned 4-layer board.

TEST LEVEL

I. 100% production tested.

II.

100% production tested at 25°C.

III. Sample tested only.

IV. Parameter guaranteed by design and characterization testing.

V. Parameter is a typical value only.

VI.

100% production tested at 25°C; guaranteed by design and

characterization testing for industrial temperature range.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. 0 | Page 10 of 76

Page 11

AD6652

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

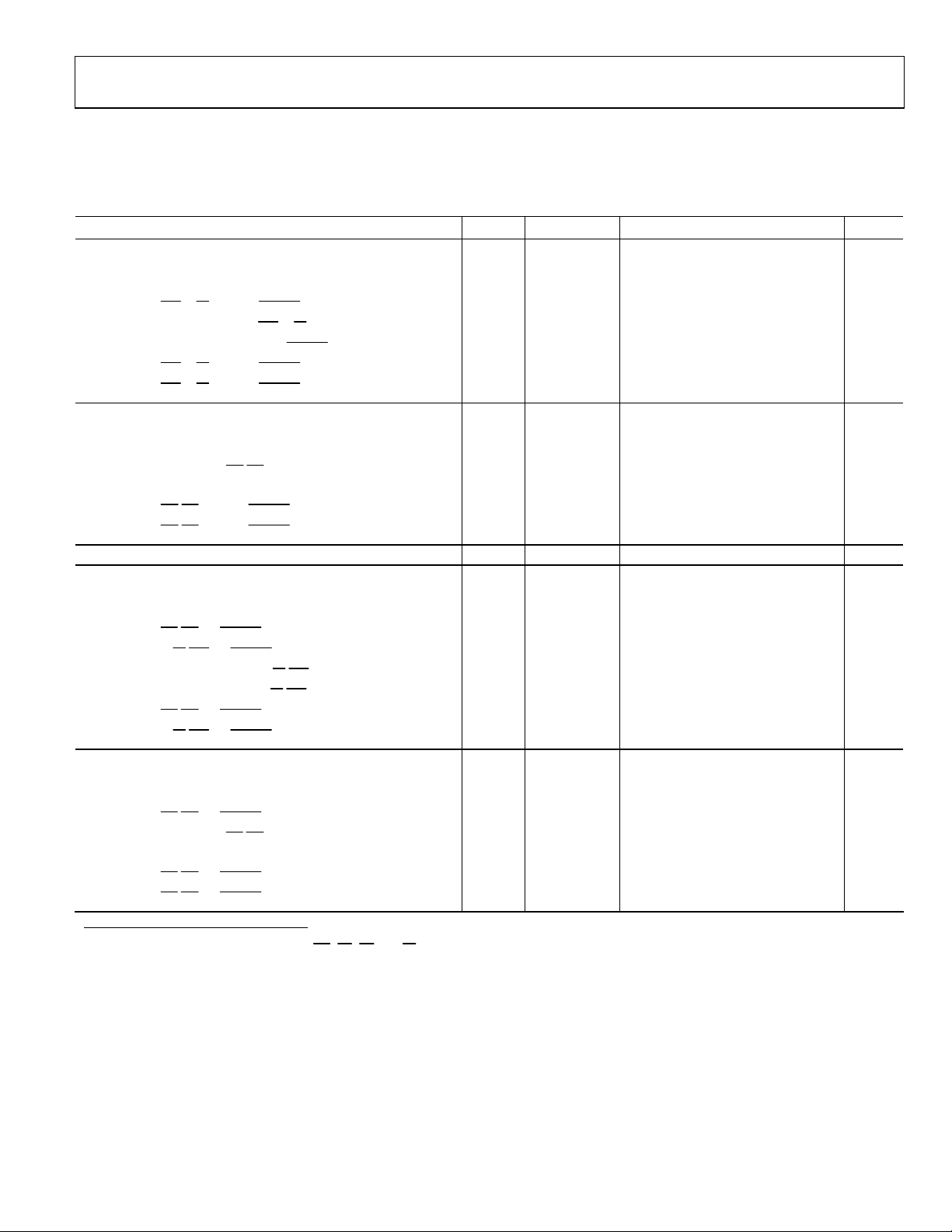

Table 9. BGA Pin Configuration (Top View)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

DGND PA7_LA7 A2 PA6_LA6 D1 D3

A

Do Not

Connect

PA4_LA4

B

PA9 PA3_LA3 A1

C

PA1_LA1 PA2_LA2

D

PA8 PA5_LA5 n.c. VDD VDD VDD VDD VDDIO VDDIO VDDIO VDDIO VDDIO AVDD AVDD AGND AGND

E

PA0_LA0 DGND PA10 DGND DGND DGND DGND DGND DGND DGND DGND VDDIO AVDD AGND AGND AGND

F

PA12 PA11 PA13 DGND DGND DGND DGND DGND DGND DGND DGND VDDIO AVDD AGND REFBB REFTB

G

PAR EQ PA 15 PA1 4 DGND DGND DGND DGND DGND DGND DGND DGND VDDIO AVDD AGND AGND SENSE

H

CHIP_ID1 DGND DGND DGND DGND DGND DGND DGND DGND DGND DGND VDDIO AVDD AGND AGND VREF

J

CHIP_ID3 PAACK CHIP_ID0 DGND DGND DGND DGND DGND DGND DGND DGND VDDIO AVDD AGND REFBA REFTA

K

PB6_LB6 PB7_LB7 DGND DGND DGND DGND DGND DGND DGND DGND DGND VDDIO AVDD AGND AGND AGND

L

PAC H0 _

LACLK

OUT

PAC H1 _

LACLKIN

A0

DS (RD

VDD VDD VDD VDD VDDIO VDDIO VDDIO VDDIO VDDIO AVDD AVDD AGND VI N−B

DGND

D0 D2 D5 D7

)

R/

CS RESE T

W (WR

D4 D6 SYNCC SYNCA LIA DUTYEN

)

MODE SYNCD OTRA PDWN AVDD AVDD AGND AGND

DTACK

(RDY)

SYNCB

LIA

AVDD AVDD AGND AGND

LIB AVDD AVDD AGND VIN+B

CHIP_ID2 PB3_LB3 PB4_LB4 VDDIO VDDIO VDDIO VDDIO VDD VDD VDD VDD VDDIO AVDD AVDD AG ND AGND

M

PAI Q

N

P

PBIQ

R

DGND PCLK PB5_ LB5 PB11 PB13 PBREQ n.c. n.c. n.c. n.c. DCLK SHRDREF AVDD ACLK AGND AGND

T

PBCH1_

LBCLK IN

DGND PB0_LB0 PB8 PB10 PB14 VDDIO PBACK

PBCH0_L

BCLKOUT

PB2_LB2

PB1_ LB1 PB9 PB12 PB15 n.c. n.c. n.c. n.c. n.c. PDWN

VDDIO VDDIO VDDIO VDDIO VDD VDD VDD VDD VDDIO AVDD AVDD AGND VI N−A

LIB

n.c. n.c. OTRB n.c. AVDD AVDD AGN D VIN+A

AVDD AVDD AGND AGND

Rev. 0 | Page 11 of 76

Page 12

AD6652

Table 10. Pin Function Descriptions

Pin No. Mnemonic Type Function

POWER SUPPLY

A13, B13, C13, D13, E13, F13, G13, H13, J13, K13, L13, M13, N13, P13, R13,

T13, A14, B14, C14, D14, E14, M14, N14, P14, R14

D4, D5, D6, D7, E4, E5, E6, E7, M8, M9, M10, M11, N8, N9, N10, N11 VDD Power 2.5 V Digital Core Supply, 16 Pins.

D8, D9, D10, D11, D12, E8, E9, E10, E11, E12, F12, G12, H12, J12, K12, L12,

M4, M5, M6, M7, M12, N4, N5, N6, N7, N12, P6

A1, B5, F2, F4, F5, F6, F7, F8, F9, F10, F11, G4, G5, G6, G7, G8, G9, G10, G11,

H4, H5, H6, H7, H8, H9, H10, H11, J2, J3, J4, J5, J6, J7, J8, J9, J10, J11, K4,

K5, K6, K7, K8, K9, K10, K11, L3, L4, L5, L6, L7, L8, L9, L10, L11, P1, T1

A15, A16, B15, B16, C15, D15, E15, E16, F14, F15, F16, G14, H14, H15, J14,

J15, K14, L14, L15, L16, M15, M16, N15, P15, R15, R16, T15, T16

MISCELLANEOUS

E3, P9, P10, P12, R7, R8, R9, R10, R11, T7, T8, T9, T10 NC N/A No Connect, 13 Pins.

B1 DNC N/A Do Not Connect.

Pin No. Mnemonic Type Function

ADC INPUTS

P16 VIN+A Input Differential Analog Input Pin (+) for Channel A.

N16 VIN−A Input Differential Analog Input Pin (−) for Channel A.

C16 VIN+B Input Differential Analog Input Pin (+) for Channel B.

D16 VIN−B Input Differential Analog Input Pin (−) for Channel B.

J16 VREF I/O Voltage Reference Input/Output.

H16 SENSE Input Voltage Reference Mode Select.

T14 ACLK Input ADC Master Clock.

B12 DUTYEN Input Duty Cycle Stabilizer, Active High.

A12, R12 PDWN

1

Input Power-Down Enable, Active High.

T12 SHRDREF Input Shared Voltage Reference Select, Low = Independent, High = Shared.

ADC OUTPUTS

A11 OTRA Output Out-of-Range Indicator for Channel A, High = Overrange.

P11 OTRB Output Out-of-Range Indicator for Channel B, High = Overrange.

K16 REFTA Output Top Reference Voltage, Channel A.

G16 REFTB Output Top Reference Voltage, Channel B.

K15 REFBA Output Bottom Reference Voltage, Channel A.

G15 REFBB Output Bottom Reference Voltage, Channel B.

DDC INPUTS

A8

RESET

Input Master Reset, Active Low.

T11 DCLK Input DDC Master Clock.

T2 PCLK I/O Link Port Clock Output or Parallel Port Clock Input.

D3 PACH1_LACLKIN

2

I/O

Channel ID Output Bit, MSB, for Parallel Port A, or Link Port A Data Ready Input.

Function depends on logic state of 0x1B:7 of output port control register.

N2 PBCH1_LBCLKIN2 I/O

Channel ID Output Bit, MSB, for Parallel Port B, or Link Port B Data Ready Input.

Function depends on logic state of 0x1D:7 of output port control register.

B10 SYNCA

3

Input Hardware Sync, Pin A, Routed to All Receiver Channels.

C10 SYNCB3 Input Hardware Sync, Pin B, Routed to All Receiver Channels.

B9 SYNCC3 Input Hardware Sync, Pin C, Routed to All Receiver Channels.

A10 SYNCD3 Input Hardware Sync, Pin D, Routed to All Receiver Channels.

3

K3, J1, M1,

K1

CHIP_ID[3:0]

Input

Chip ID Selector, Four Pins, Used in Conjunction with Access Control Register

Bits 5–2.

AVDD Power 3.0 V Analog Supply, 25 Pins.

VDDIO Power 3.3 V Digital I/O Supply, 27 Pins.

DGND Ground Digital Ground, 56 Pins.

AGND Ground Analog Ground, 28 Pins.

Rev. 0 | Page 12 of 76

Page 13

AD6652

Pin No. Mnemonic Type Function

DDC OUTPUTS

B11 LIA Output Level Indicator, Input A, Data A.

C11

LIA

C12 LIB Output Level Indicator, Input B, Data B.

P8

LIB

B3 PACH0_LACLKOUT2 Output

R2 PACH0_LBCLKOUT2 Output

F1, D1, D2,

PA[7:0]_LA[7:0] Output Link Port A Data or Parallel Port A Data [7:0], Eight Pins.

C2, B2, E2,

A4, A2

P2, R3, N3,

PB[7:0_LB[7:0] Output Link Port B Data or Parallel Port B Data [7:0], Eight Pins.

M2, M3, T3,

L1, L2

E1, C1, F3,

PA[15:8] Output Parallel Port A Data [15:8], Eight Pins.

G2, G1, G3,

H3, H2

P3, R4, P4,

PB[15:8] Output Parallel Port B Data [15:8], Eight Pins.

T4, R5, T5,

P5, R6

N1 PAIQ Output Parallel Port A I or Q Data Indicator, I = High, Q = Low.

R1 PBIQ Output Parallel Port B I or Q Data Indicator, I = High, Q = Low.

PARALLEL OUTPUT PORT CONTROL

K2 PAACK Input Parallel Port A Acknowledge.

H1 PAREQ Output Parallel Port A Request.

P7 PBACK Input Parallel Port B Acknowledge.

T6 PBREQ Output Parallel Port B Request.

MICROPORT CONTROL

C5, A5, C6,

D[7:0] I/O

A6, B7, C7,

B8, C8

B4, C3, A3 A[2:0] Input Microport Address Bus, 3 Pins.

C4

C9

B6

4

DS(RD)

DTACK(RDY)

W (WR)4

R/

4, 5

A9 MODE4 Input Mode Select Pin. 0 = Intel mode, 1 = Motorola mode.

A7

CS3

Output

Output

Level Indicator, Input A, Data

Level Indicator, Input B, Data

A.

B.

Channel ID Output Bit, LSB, for Parallel Port A, or Link Port A Clock Output.

Function depends on logic state of 0x1B:7 of output port control register.

Channel ID Output Bit, LSB, for Parallel Port B, or Link Port B Clock Output.

Function depends on logic state of 0x1D:7 of output port control register.

Bidirectional Microport Data, Eight Pins. This bus is three-stated when CS is high.

Input Function depends upon MODE pin.

Active Low Data Strobe when MODE = 1.

Active Low Read Strobe when MODE = 0.

Output Function depends upon MODE pin.

Active Low Data Acknowledge when MODE = 1.

Microport Status Pin when MODE = 0.

Input Read/Write Strobe when MODE = 1. Active Low Write strobe when MODE = 0.

Input Active Low Chip Select. Logic 1 three-states the microport data bus.

1

PDWN pins must be the same logic level: both logic high or both logic low.

2

PACH0 and PACH1 form a 2-bit output word in the parallel output mode that identifies the processing channel (0, 1, 2, or 3) whose data appears on Port A parallel

outputs. Likewise, PBCH0 and PBCH1 identify the channel for Port B.

3

Pins with a pull-down resistor of nominal 70 kΩ.

4

Mode 0 is Intel nonmultiplexed (IMN), and Mode 1 is Motorola nonmultiplexed (MNM). Pin logic level corresponds to mode.

5

Pins with a pull-up resistor of nominal 70 kΩ.

Rev. 0 | Page 13 of 76

Page 14

AD6652

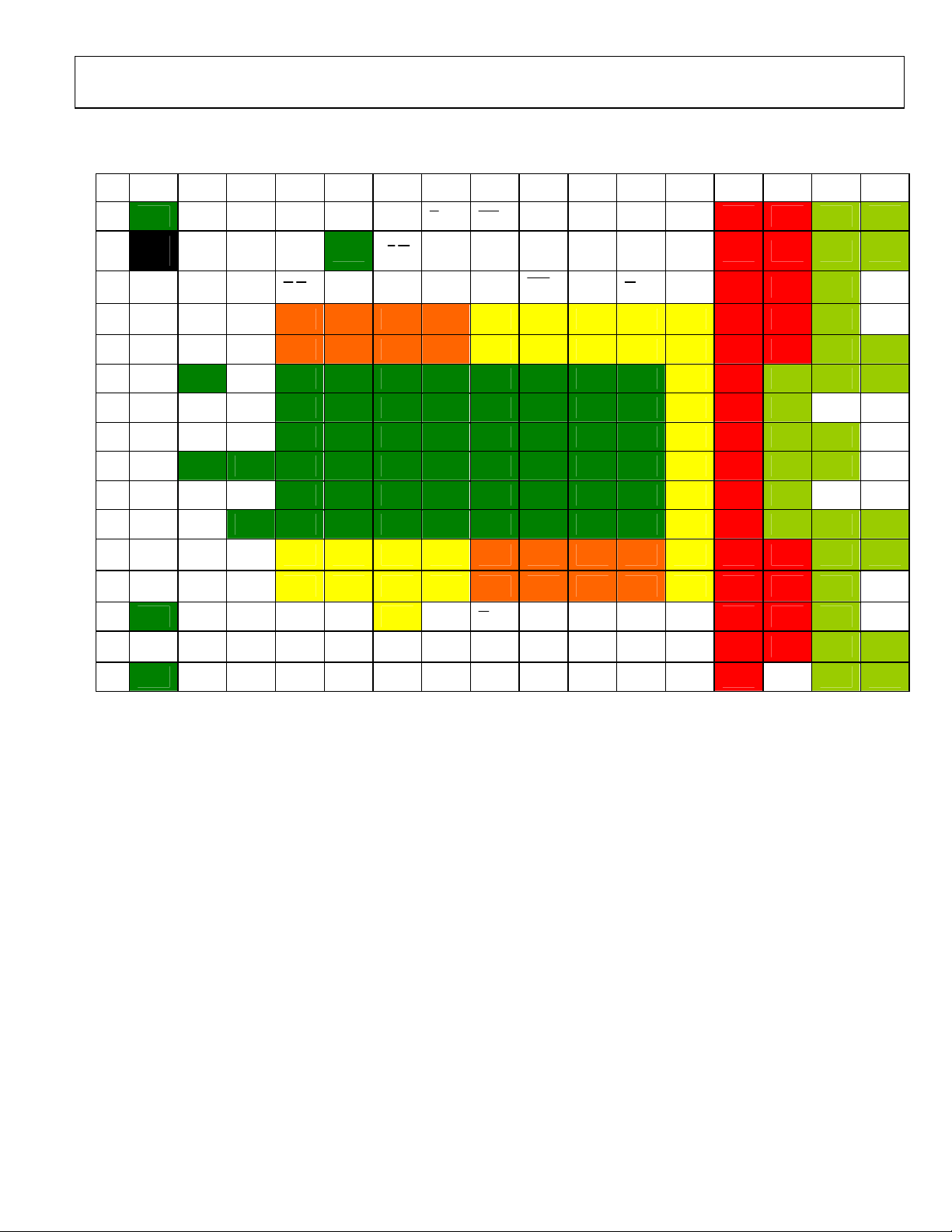

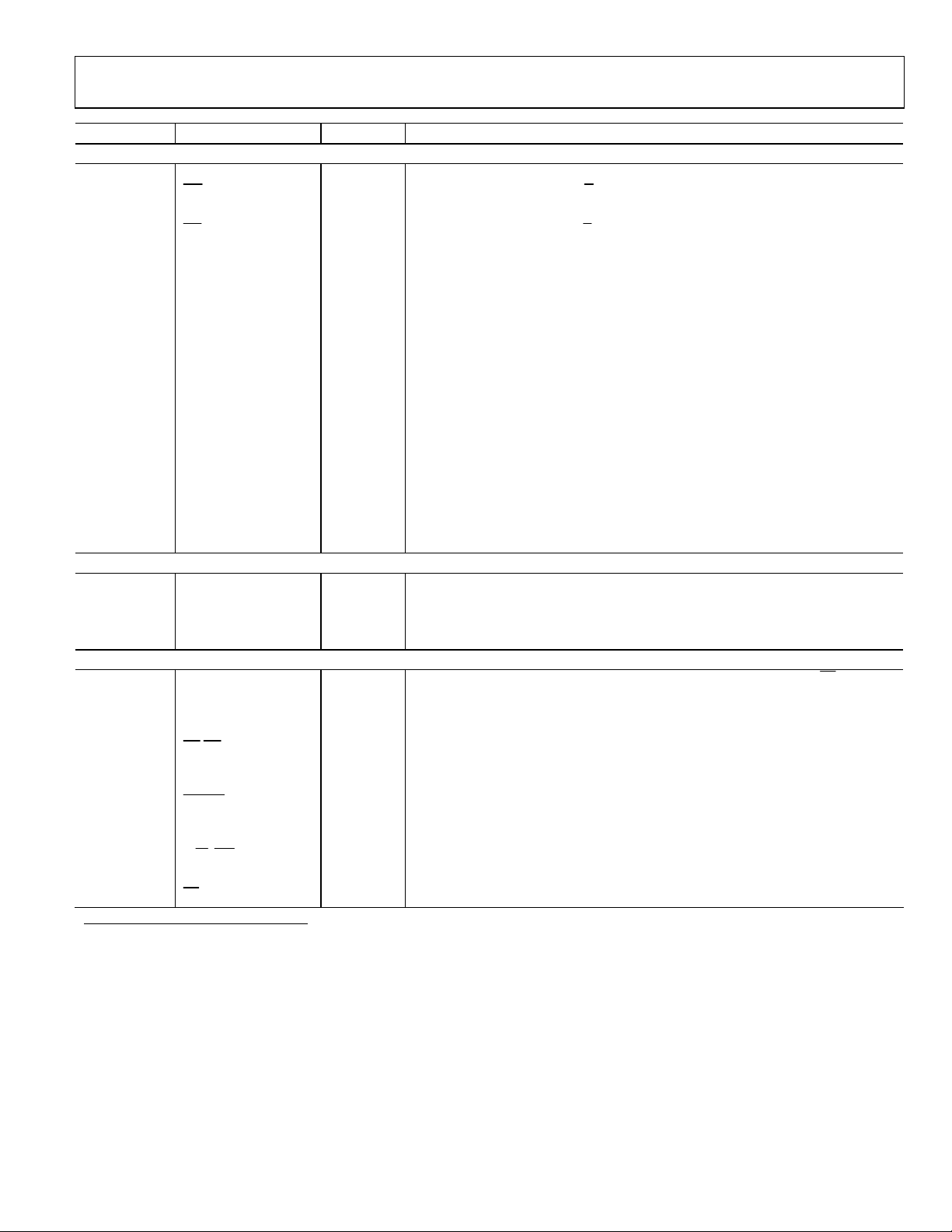

TYPICAL PERFORMANCE CHARACTERISTICS

0

AIN = –1dBFS

–10

SNR = 90dB (200kHz BW)

–20

32k FFT

–30

–40

–50

–60

–70

–80

dBFS

–90

–100

–110

–120

–130

–140

–150

–300 –200 –100 0 100 200 300

FREQUENCY (kHz)

Figure 2. GSM/EDGE with Single Tone A

= 30 MHz; Encode = 61.44 MSPS

IN

0

AIN = –1dBFS

–10

SNR = 80dB (1.25MHz BW)

–20

32k FFT

–30

–40

–50

–60

–70

–80

dBFS

–90

–100

–110

–120

–130

–140

–150

–1.2 –0.8 –0.4 0 0.4 0.8 1.2

FREQUENCY (MHz)

Figure 3. CDMA2000 with Single Tone A

= 76 MHz; Encode = 61.44 MSPS

IN

0

AIN = –1dBFS

–10

SNR = 70dB (5MHz BW)

–20

32k FFT

–30

–40

–

50

–60

–70

–80

dBFS

–90

–100

–110

–120

–130

–140

–150

Figure 4. WCDMA with Single Tone A

–101234–3 –2–4

FREQUENCY (MHz)

= 169 MHz; Encode = 61.44 MSPS

IN

03198-0-060

03198-0-062

03198-0-064

0

–10

–20

–30

–40

–50

–60

–70

–80

dBFS

–90

–100

–110

–120

–130

–140

–150

–300 –200 –100 0 100 200 300

FREQUENCY (kHz)

Figure 5. GSM/EDGE Carrier A

= 30 MHz; Encode = 61.44 MSPS

IN

0

–10

–20

–30

–40

–50

–60

–70

–80

dBFS

–90

–100

–110

–120

–130

–140

–150

–1.2 –0.8 –0.4 0 0.4 0.8 1.2

FREQUENCY (MHz)

Figure 6. CDMA2000 Carrier A

= 76 MHz; Encode = 61.44 MSPS

IN

0

–10

–20

–30

–40

–50

–60

–70

–80

dBFS

–90

–100

–110

–120

–130

–140

–150

Figure 7. WCDMA Carrier A

–101234–3 –2–4

FREQUENCY (MHz)

= 169 MHz; Encode = 61.44 MSPS

IN

32k FFT

32k FFT

32k FFT

03198-0-059

03198-0-061

03198-0-063

Rev. 0 | Page 14 of 76

Page 15

AD6652

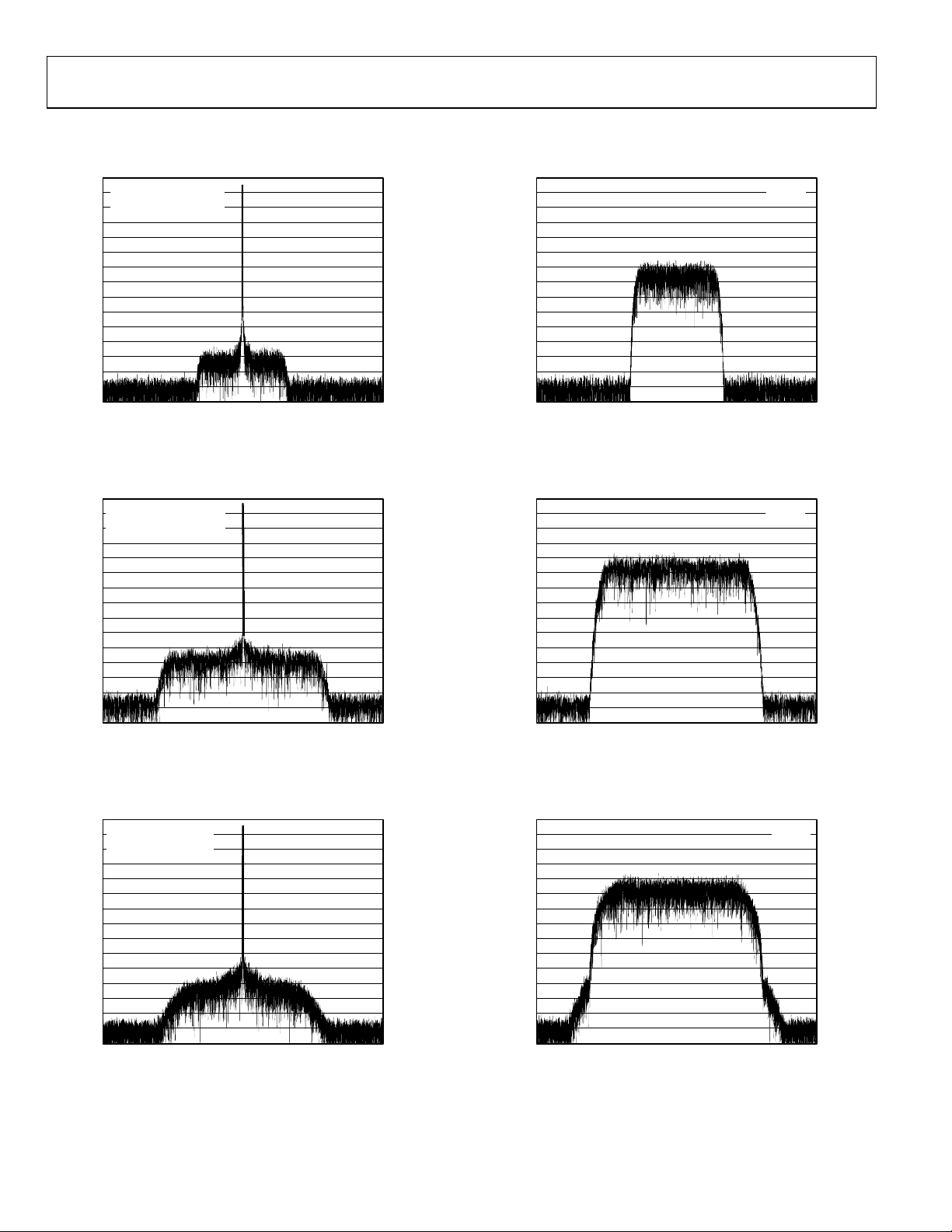

0

ENCODE = 61.44MSPS

–10

A

IN

–20

32k FFT

–30

–40

–50

–60

–70

–80

dBFS

–90

–100

–110

–120

–130

–140

–150

100

= –7dBFS

–101234–3 –2–4

FREQUENCY (MHz)

Figure 8. Two Tones at 15 MHz and 16 MHz

03198-0-070

0

ENCODE = 61.44MSPS

–10

A

IN

–20

32k FFT

–30

–40

–50

–60

–70

–80

dBFS

–90

–100

–110

–120

–130

–140

–150

100

= –7dBFS

–101234–3 –2–4

FREQUENCY (MHz)

Fig z ure 11. Two Tones at 55 MHz and 56 MH

03198-0-066

90

80

70

60

SNR (dB) [150kHz BW]

50

40

SNR

–40 –30–60 –50 –20 –10 0

ANALOG INPUT AMPLITUDE (dBFS)

03198-0-071

Figure 9. Noise vs. Analog Amplitude at 25 MHz

100

90

80

70

60

HARMONICS (dBc)

HARMONICS

HARMONICS = 80dB

REFERENCE LINE

90

80

70

60

SNR (dB) [150kHz BW]

50

40

SNR

–40 –30–60 –50 –20 –10 0

ANALOG INPUT AMPLITUDE (dBFS)

03198-0-072

Figure 12. Noise vs. Analog Amplitude at 68 MHz

100

90

80

70

60

HARMONICS (dBc)

HARMONICS

HARMONICS = 80dB

REFERENCE LINE

50

40

–40 –30–60 –50 –20 –10 0

ANALOG INPUT AMPLITUDE (dBFS)

Figure 10. Harmonics vs. Analog Amplitude at 25 MHz

03198-0-073

Rev. 0 | Page 15 of 76

50

40

–40 –30–60 –50 –20 –10 0

ANALOG INPUT AMPLITUDE (dBFS)

Figure 13. Harmonics vs. Analog Amplitude at 68 MHz

03198-0-074

Page 16

AD6652

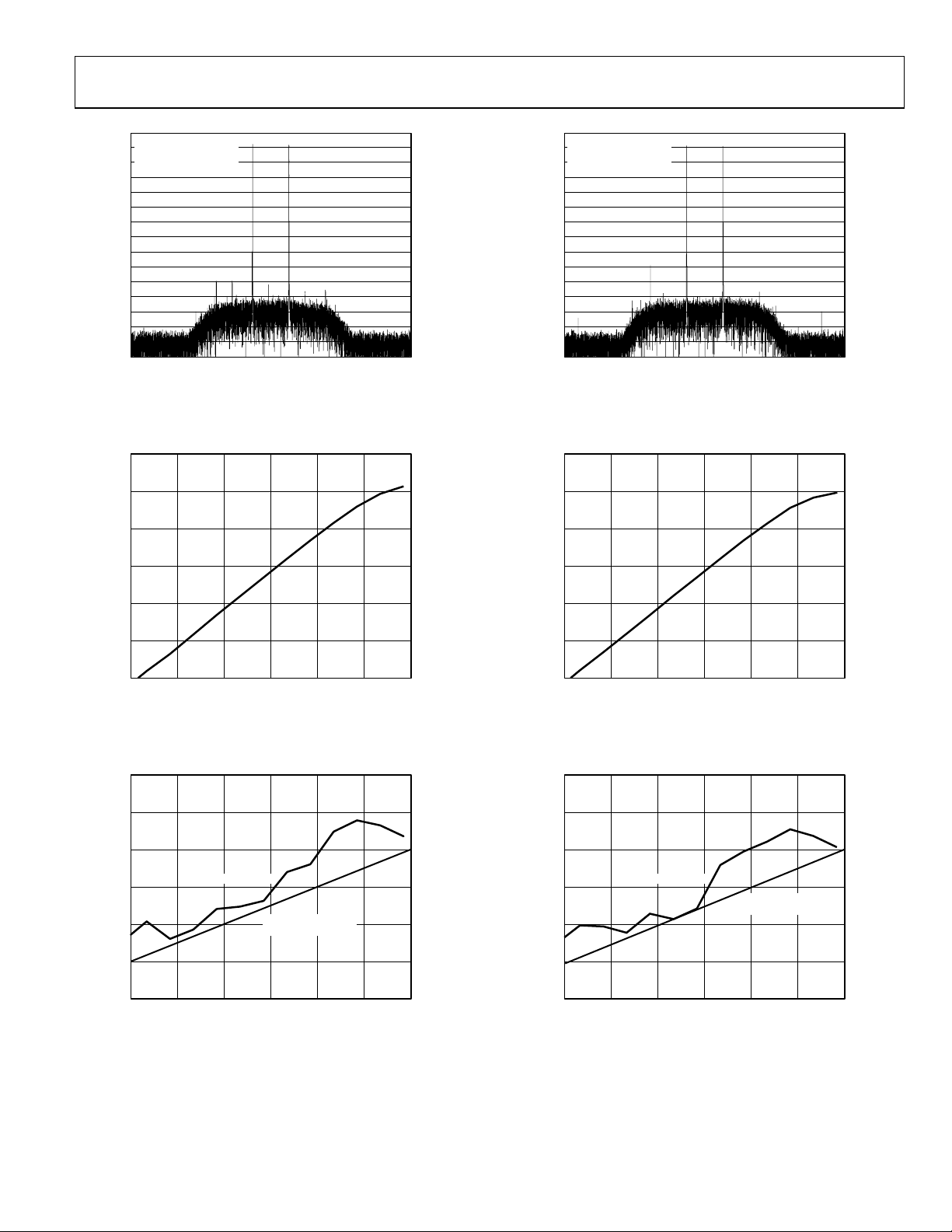

92

AIN = –1dBFS

92

AIN = –1dBFS

25°C

90

= 150kH

88

SNR (dB) [BW z]

86

0 10203040506070

ANALOG INPUT FREQUENCY (MHz)

85°C

–40°C

Figure 14. Noise vs. Analog Frequency

90

AIN = –1dBFS

85

80

25°C

75

03198-0-068

90

88

SNR (dB) [BW = 150kHz]

86

84

0 20 40 60 80 100 120 140 160 180 200

ANALOG INPUT FREQUENCY (MHz)

Figure 16. Noise vs. Analog Frequency (IF)

25°C

03198-0-067

70

WORST-CASE HARMONIC (dBc)

65

75 100 125 150 175 20025 500

ANALOG FREQUENCY (MHz)

03198-0-069

Figure 15. Harmonics vs. Analog Frequency

Rev. 0 | Page 16 of 76

Page 17

AD6652

K

K

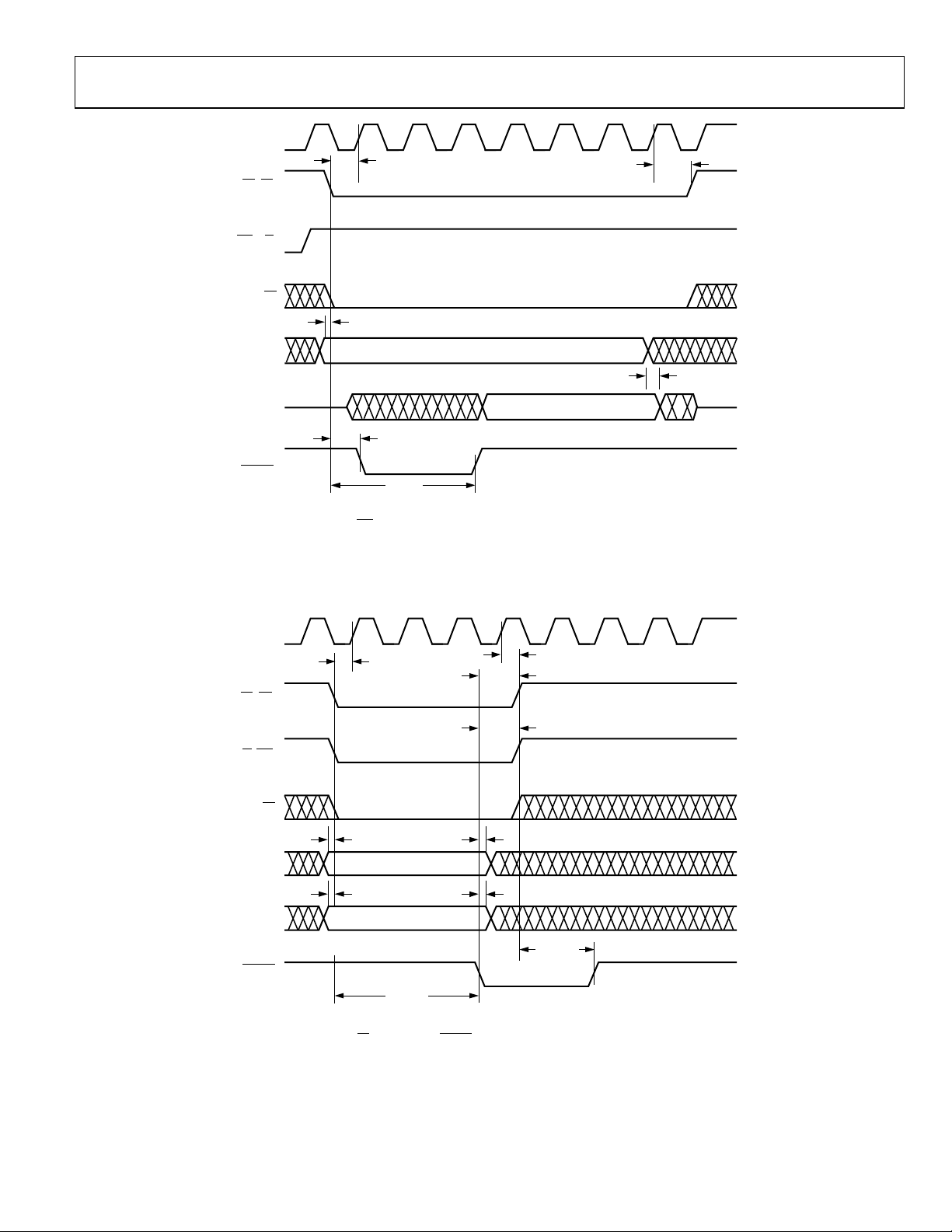

DDC TIMING DIAGRAMS

t

CLK

t

CLKL

CL

t

CLKH

t

DLI

LIA, LIB

LIA, LIB

03198-0-065

Figure 17. Level Indicator Output Switching Characteristics

RESET

t

RESL

03198-0-003

Figure 18. Reset Timing Requirements

CLK

t

HS

03198-0-006

SYNCA

SYNCB

SYNCC

SYNCD

t

SS

Figure 19. SYNC Timing Inputs

CLK

t

DPOCLKL

PCL

03198-0-007

Figure 20. PCLK to CLK Switching Characteristics Divide-by-1

CLK

t

DPOCLKLL

PCLK

t

POCLKH

t

POCLKL

03198-0-008

Figure 21. PCLK to CLK Switching Characteristics Divide-by-2, -4, or -8

Rev. 0 | Page 17 of 76

Page 18

AD6652

K

PCLK

PxREQ

PxACK

PCLK

PxACK

t

HPA

t

SPA

03198-0-009

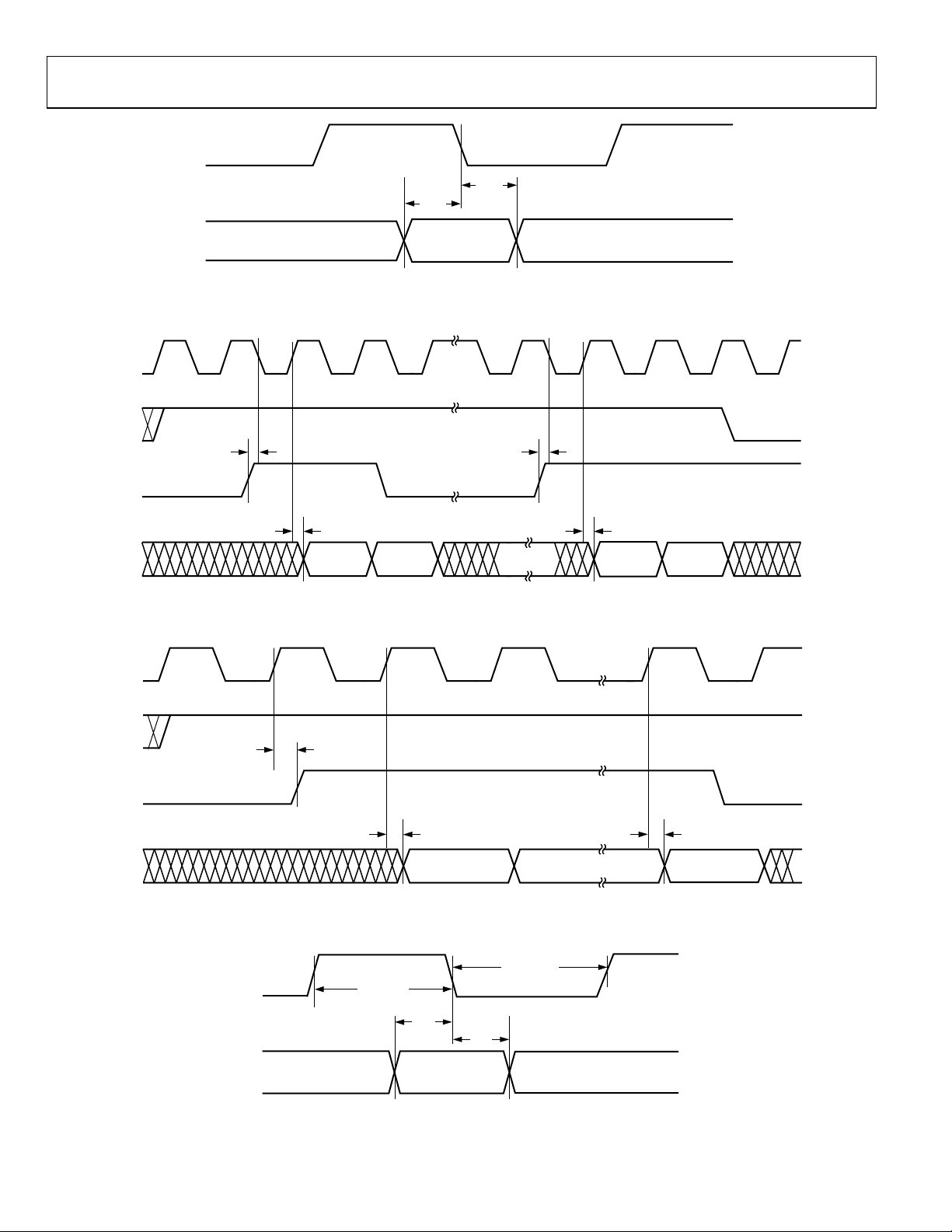

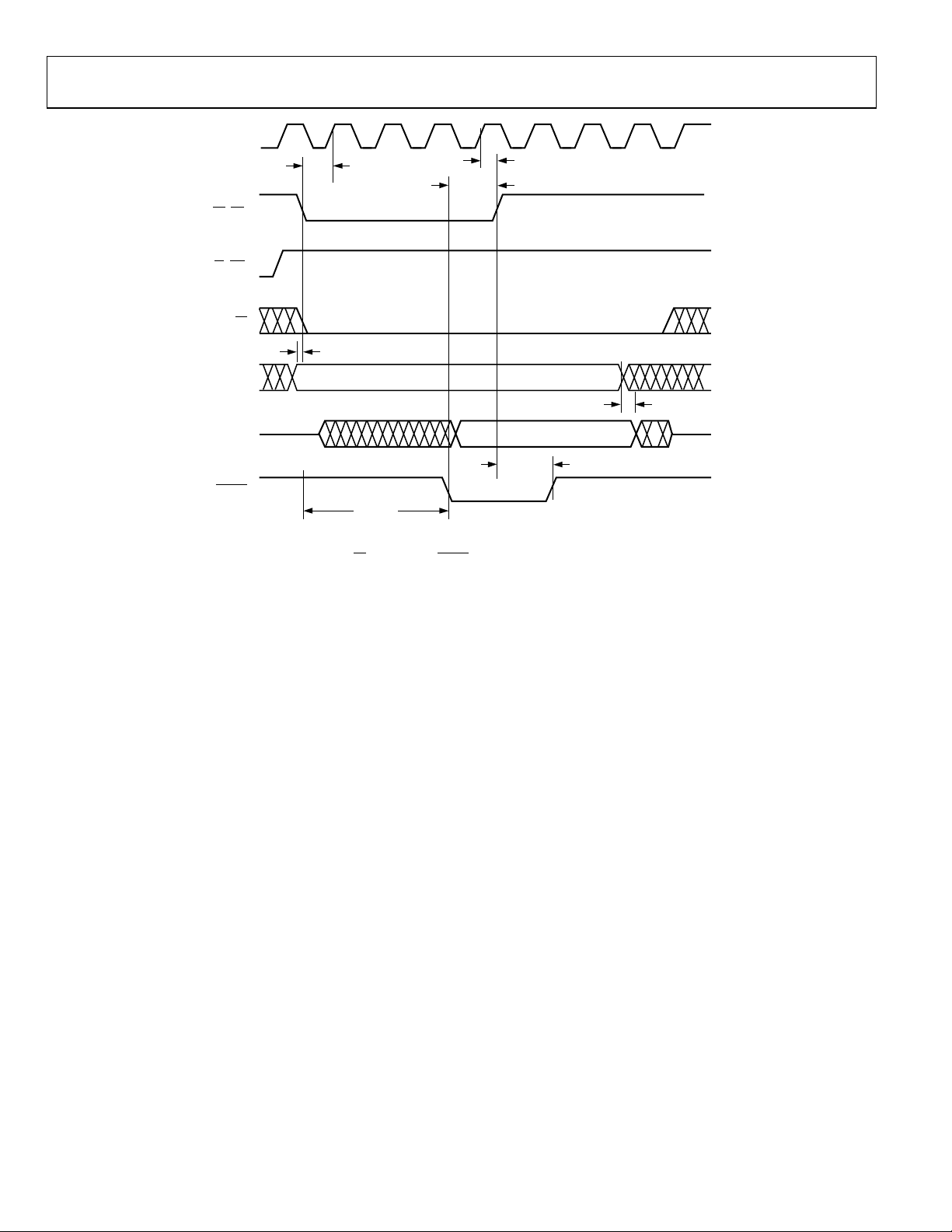

Figure 22. Master Mode PxACK to PCLK Setup and Hold Characteristics

t

SPA

t

SPA

Px[15:0]

t

DPP

DATA 1 DATA 2 DATA N – 1 DATA N

t

DPP

03198-0-010

Figure 23. Master Mode PxACK to PCLK Switching Characteristics

PCLK

PxACK

t

DPREQ

PxREQ

Px[15:0]

t

DPP

DATA 1 DATA N

t

DPP

03198-0-011

Figure 24. Master Mode PxREQ to PCLK Switching Characteristics

t

PCLK

t

POCLKH

POCLKL

t

SPA

PxAC

t

HPA

03198-0-012

Figure 25. Slave Mode PxACK to PCLK Setup and Hold Characteristics

Rev. 0 | Page 18 of 76

Page 19

AD6652

PCLK

PxREQ

PxACK

t

SPA

t

SPA

Px[15:0]

t

DPP

DATA 1 DATA 2 DATA N – 1 DATA N

t

DPP

03198-0-013

Figure 26. Slave Mode PxACK to PCLK Switching Characteristics

PCLK

PxACK

t

DPREQ

PxREQ

Px[15:0]

t

DPP

DATA 1 DATA N

t

DPP

03198-0-014

Figure 27. Slave Mode PxREQ to PCLK Switching Characteristics

PCLK

LxCLKOUT

t

RDLCLK

t

FDLCL

03198-0-015

Figure 28. LxCLKOUT to PCLK Switching Characteristics

Rev. 0 | Page 19 of 76

Page 20

AD6652

LxCLKOUT

LxCLKIN

WAIT ≥ 6 CYCLES

ONE TIME CONNECTIVITY CHECK

8 LxCLKOUT CYCLES

NEXT TRANSFER

ACKNOWLEDGE

NEXT TRANSFER

BEGINS

Lx[7:0]

LxCLKOUT

Lx[7:0]

CLK

RD (DS)

WR (R/W)

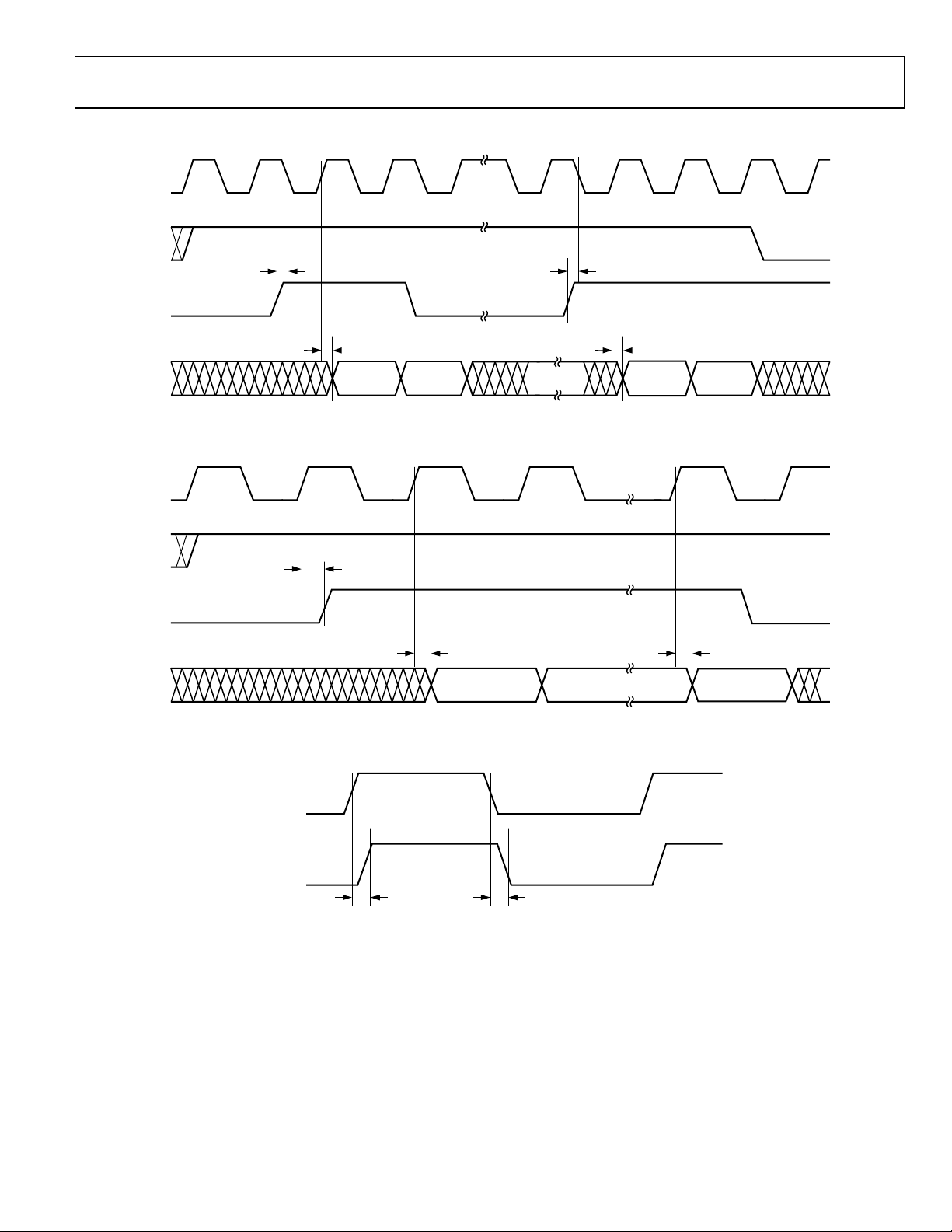

Figure 29. LxCLKIN to LxCL

t

FDLCLKDAT

Figure 30. LxCLKOUT to Lx

t

SC

D0

D1

t

RDLCLKDAT

D2 D3 D4 D15 D3

KOUT Data witching Characteristics

S

D0 D1 D2

[7:0] Data Switching Characteristics

t

HC

t

HWR

03198-0-016

03198-0-017

CS

t

t

HAM

HAM

03198-0-018

A[2:0]

D[7:0]

RDY

(DTACK)

t

SAM

VALID ADDRESS

t

SAM

LID DATA

VA

t

DRDY

t

ACC

NOTES

1.

t

ACCESS TIME DEPENDS ON THE ADDRESS ACCESSED. ACCESS TIME IS MEASURED

ACC

FROM FE OF WR TO RE OF RDY.

t

REQUIRES A MAXIMUM OF 9 CLK PERIODS.

2.

ACC

Figure 31. INM Microport Write Timing Requirements

Rev. 0 | Page 20 of 76

Page 21

AD6652

CLK

t

RD (DS)

WR (RW)

CS

SC

t

SAM

t

HC

A[2:0]

D[7:0]

RDY

(DTACK)

t

DRDY

NOTES

1.

t

ACCESS TIME DEPEND

ACC

FROM FE OF WR TO RE OF RDY.

t

REQUIRES A MAXIMUM OF 13

2.

ACC

VALID ADDRESS

t

ACC

S ON THE ADDRESS

CLK PERIOD

t

HA

VALID DATA

ACCESSED. ACCESS TIME IS MEASURED

S.

03198-0-019

iming Requirements Figure 32. INM Micropor t Read T

CLK

t

HC

DS (RD)

RW (WR)

t

SC

t

HDS

t

HRW

CS

t

HAM

t

HAM

t

ACC

HE FE OF DTACK.

XIMUM OF 9 CLK PERIODS.

THE ADDRESS ESS TIME IS MEASURED

ort Write Timing Requirements

t

DDTACK

ACCESSED. ACC

03198-0-020

A[2:0]

D[7:0]

DTACK

(RDY)

t

SAM

VALID ADDRESS

t

SAM

NOTES

t

ACCESS TIME DEPENDS ON

1.

ACC

FROM FE OF DS TO T

2.

t

REQUIRES A MA

ACC

Figure 33. MNM Microp

VALID DATA

Rev. 0 | Page 21 of 76

Page 22

AD6652

CLK

DS (RD)

R/W (WR)

CS

A[2:0]

t

t

SC

t

HDS

t

SAM

HC

VALID ADDRESS

t

HA

D[7:0]

DTACK

(RDY)

t

ACC

NOTES

1.

t

ACCESS TIME DEPENDS ON T

ACC

FROM THE FE OF DS TO THE FE O

t

REQUIRES A MAXIMUM OF 13

2.

ACC

HE ADDRESS ACC

F DTACK.

CLK PERIOD

S.

Timing Requirements Figure 34. MNM Microport Read

VALID DATA

t

DDTACK

ESSED. ACCESS TIME IS MEASURED

03198-0-021

Rev. 0 | Page 22 of 76

Page 23

AD6652

TERMINOLOGY

Crosstalk

Coupling onto one channel being driven by a (−0.5 dBFS) signal

when the adjacent interfering channel is driven by a full-sc

ale

signal. Measurement includes all spurs resulting from both

direct coupling and mixing components.

IF Sampling (Undersampling)

Due to the effects of aliasing, an ADC is not necessarily limited

to Nyquist sampling. Frequencies above Nyquist are aliased and

appear in the first Nyquist zone (dc to Sample Rate/2). Care

must be taken to limit the bandwidth of the sampled signal so

that it does not overlap Nyq

sam y the bandwidth of the input

pling performance is limited b

HA (sample-and-hold amplifier) and clock jitter. (Jitter adds

S

uist zones and alias onto itself. IF

more noise at higher input frequencies.)

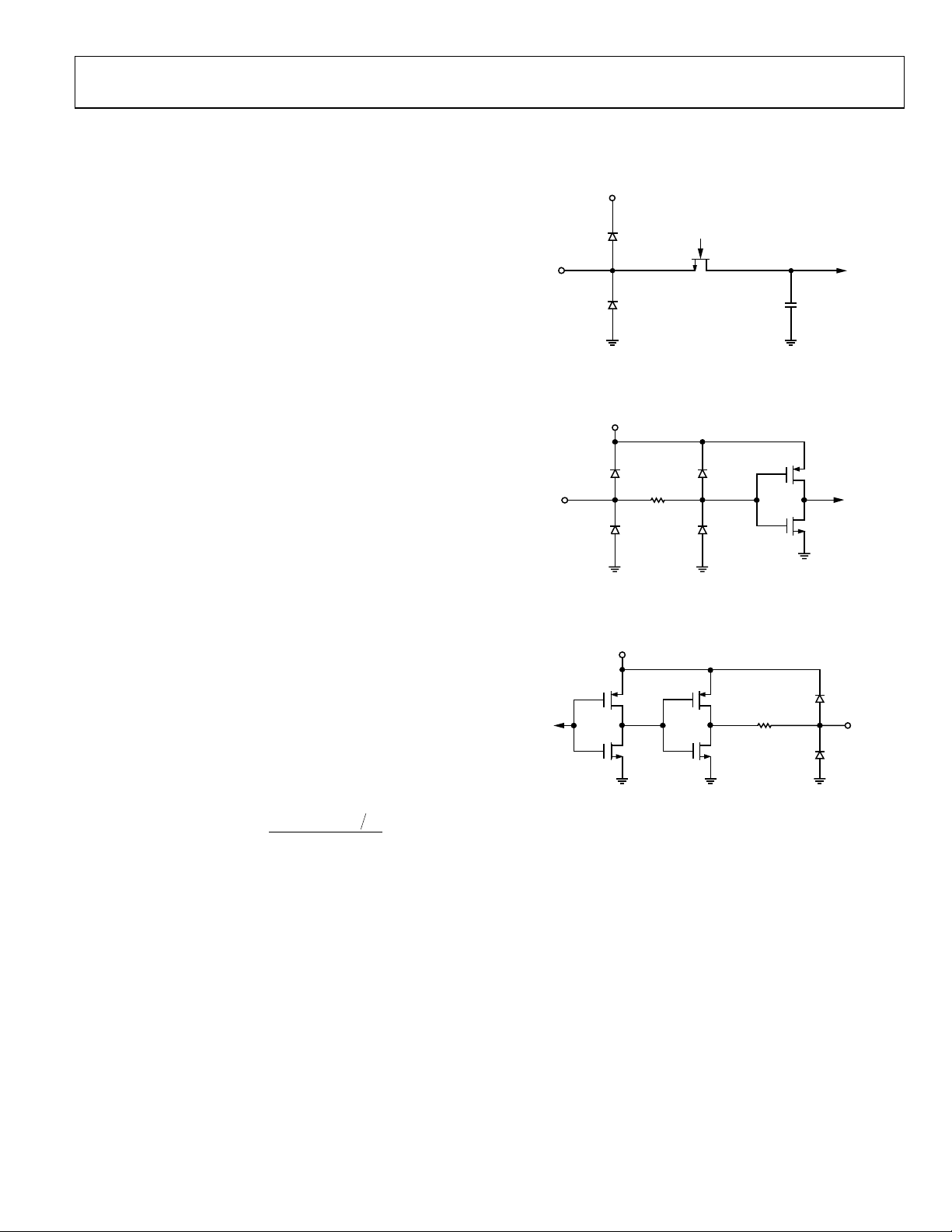

ADC EQUIVALENT CIRCUITS

AVDD

Figure 35. Analog Input Circuit

AVDD

03198-0-022

Nyquist Samplin ling)

Oversampling occu frequen f the

analog input signal are be e Nyqu

and requires that the analo ut frequency b at least

g (Oversamp

rs when the cy components o

low th ist frequency (F

g inp e sampled

/2),

clo

ck

two samples per cycle.

ut-of-Range Recovery Time

O

Out-of-range recovery time is th time it takes for the analogto-digital co after a

transient fro ove

nverter (ADC) to reacquire the analog input

m 10% above positive full scale to 10% ab

e

negative full scale, or from 10% below negative full scale to 10%

below positive full scale.

Processing Gain

When the tuned channel occupies less bandwidth than the

input signal, this rejection of out-of-band noise is referred to as

processing gain. By using large decimation factors, this processing gain can improve the SNR of the ADC by 20 dB or more.

The following equation can be used to estimate processing gain:

RateSample

2_

=

_GainProcessing

⎡

log10

⎢

⎣

BandwidthFilter

_

⎤

⎥

⎦

Signal-to-Noise Ratio (SNR)

The ratio of the rms value of the measured input signal to the

rms sum of all other spectral components within the programmed DDC filter bandwidth, excluding the first six

harmonics

cibels (dB).

de

and dc. The value for SNR is expressed in

03198-0-023

Figure 36. Digital Input

VDD

03198-0-024

Figure 37. Digital Output

Two -Ton e I MD Rejection

The ratio of the rms value of either input tone to the rms value

of the worst third-order intermodulation product; reported

in dBc.

Rev. 0 | Page 23 of 76

Page 24

AD6652

THEORY OF OPERATIO

The AD6652 has two analog input channels, four digital filtering channels, and two digital output channels. The IF input

signal passes through several stages before it appears at th

output port(s) as a well-filtered, decimated digital baseba

signal:

•

12-bit A/D conversio

•

Frequency translation from IF to baseband using

quadrature mixers and NCOs

•

Second-order resampling decimating CIC FIR filter

(rCIC2)

•

Fifth-order decimating CIC FIR filter (CIC5)

•

RAM coefficient decimating FIR filter (RCF)

•

Automatic gain control (AGC)

•

2× interpolation and channel interleave

Any stage can be bypassed with the exception of the ADC f

end. Any combination of processing channels can be combined

or interleaved after the R

filtering objectives that are not possible with just one channel.

In the following sections, each st ge is examined to allow the

user to f

The dual ADC design is useful for diversity reception of signals,

where the ADCs are operating identically on the same carrier

but from two separate antennae. The ADCs can also be

operated with independent analog inputs. The user can sample

any fs/2 frequency segment from dc to 100 MHz using

appropriate low-pass or band-pass filtering at the ADC inputs

with little loss in ADC performance. Operation to 200 MHz

analog input is permitted, but at the expense of increased ADC

distortion.

In nondiversity applications, up to four GSM/EDGE-type

carriers can be concurrently processed from the ADC stage.

Wideband signals, such as WCDMA/CDMA2000, require the

power of two AD6652 processing channels per carrier to

adequately remove adjacent channel interference. When

diversity techniques a er of carriers that

can be processed is halv ocessing requirement of diversity reception.

Flexi

(D

one output port. Four synch

frequency hop, and AGC functions to be precisely orchestr

with other devices. The NCO’s phase can be set to produce a

known offset relative to another channel or device.

ully utilize the AD6652’s capabilities.

ble channel multiplexing in the digital downconverter

DC) stage allows one to four channels to be interleaved onto

n

CF stages to achieve demanding

re employed, the numb

ed due to the dual pr

N

e

nd

ront

a

ronization input pins allow startup,

ated

ADC ARCHITECTU

The AD6652 front-end consists of two high performance, 12-bit

ADCs, preceded by differential sample-and-hold amplifiers

(SHA) that provide excellent SNR performance from dc to

200 MHz. A flexible, integrated voltage reference allows analog

inputs up to 2 V p-p. Each channel is equipped with an

overrange pin that toggles high whenever the analog input

exceeds the upper or lower reference voltage boundary. ADC

outputs are internally routed to the input matrix of the DDC

stage for channel distribution. The ADC data outputs are not

directly accessible to the user.

Each sample-and-hold amplifier (SHA) is followed by a pipelined switched capacitor ADC. The pipelined ADC is divided

into three sections, consisting of a 4-bit first stage followed by

eight 1.5-bit stages and a final 3-bit flash. Each stage provides

sufficient overlap to correct for flash errors in the preceding

stages. The quantized outputs from each stage are combined

into a final 12-bit result in the digital correction logic. The

pipelined architecture permits the first stage to operate on a

new input sample while the remaining stages operate on the

preceding samples. Sampling occurs on the rising edge of the

clock.

RE

Analog Input Operation

The analog inputs to the AD6652 are differential switched

capacitor SHAs that have been designed for optimum performance while processing differential input signals. The AD6652

accepts inputs over a wide common-mode range; however, an

input common-mode voltage V

recommended to maintain optimal performance and to

minimize signal-dependent errors.

Referring to Figure 38, the clock signal alternatively switches the

SHA between sample mode and hold mode. When the SHA is

switched into sample mode, the signal source must be capable

of charging the sample capacitors and settling within one-half

of a clock cycle. A small resistor in series with each input can

help reduce the peak transient current required from the output

stage of the driving source. Also, a small shunt capacitor can be

placed across the inputs to provide dynamic charging currents.

This passive network creates a low-pass filter at the ADC’s

input; therefore, the precise values are dependent upon the

application. In IF undersampling applications, any shunt capacitors should be removed. In combination with the driving source

impedance, the shunt capacitors would limit the input

bandwidth.

, one-half of AVDD, is

CM

Programming and control of the AD6652 is accomplished using

an 8-bit parallel interface.

Rev. 0 | Page 24 of 76

Page 25

AD6652

e source impedances driving For best dynamic performance, th

the differential analog inputs should be matched such that

common-mode settling errors are symmetrical. These errors are

reduced by the common-mode rejection of the ADC.

H

S

VINA+

S

VINA–

Figure 38. Switched-Capacitor SHA Input for One ADC Channel

5pF

S = SAMPLE

H = HOLD

5pF

S

S

H

03198-0-025

The SHA should be driven from a source that keeps the signal

peak e

s within the allowable range for the selected referenc

voltage. m put

The minimum and maximum common- ode in

levels are defined as follows:

VCM

VCM

The minimum common-mode input level allows the AD66

= VREF/2

MIN

= (AV D D + VREF)/2

MAX

52 to

accommodate ground-referenced inputs.

This is especially true in IF undersampling applications in

which input frequencies in the range of 70 MHz to 200 MHz are

being sampled. For these applications, differential transform

coupling is the recommended input configuration, as shown i

Figure 39. Transforme

ratio broadband RF transfor

r T1 is a center-tapped, 1:4 impedance

mer. The signal characteristics must

be considered when selecting a transformer. Most RF

transformers saturate at frequencies below a few MHz, and

excessive signal power can also cause core saturation, which

leads to distortion.

AVDD

VINA

AD6652

VINB

AGND

1V p-p

Figure 39. Differential AC-

49.9Ω

T1

Coupled Input for One Channel of the AD6652

1kΩ

1kΩ0.1µF

50Ω

10pF

50

10pF

Ω

ADC Voltage Reference

A stable and accurate 0.5 V voltage reference is built into the

AD6652. The input span of the ADC tracks reference voltage

changes linearly. An internal differential reference buffer creates

positive and negative reference voltages, REFT and REFB,

respectively, that define the span of the ADC core. The output

common mode of the reference buffer is set to midsupply, and

the REFT and REFB voltages and span are defined as follows:

er

n

03198-0-028

Although optimum performance is achieved with a differ

put, a single-ended source can be driven into VIN+ or VIN−.

in

n this configuration, one input accepts the signal, while the

I

ential

opposite input should be set to midscale by connecting it to an

appropriate reference. For example, a 2 V p-p signal can be

applied to VIN+, while a 1 V reference is applied to VIN−. The

AD6652 then accepts a signal varying between 2 V and 0 V. In

the single-ended configuration, distortion performance might

degrade significantly, compared to the differential case.

However, the effect is less noticeable at lower analog input

frequencies.

Differential Input Configurations

Optimum performance is achieved while driving the AD6652

inputs in a differential input configuration. For baseband

applications to Nyquist, the AD8138 Differential Driver

provides excellent performance and a flexible interface to the

ADC The output common-mode voltage of the AD8138 is

easily set to one-half of AVDD, and the driver can be configured

in a Sallen-Key filter topology to provide band limiting of the

input signal.

At input frequencies above Nyquist, the performance of most

amplifiers is not adequate to achieve the true performance of

the AD6652 ADC stage.

1/2 (AV D D + VREF)

REFT =

REFB = 1/2 (AV D D − VREF)

Span = 2 × (REFT − REFB) = 2 × VREF

As shown by the equations above, the REFT and REFB voltages

are symmetrical about the midsupply voltage and, by definition,

the input span is twice the value of the VREF voltage. Proper

operation of the AD6652 requires that VREF be no less than

0.5 V and no greater than 1.0 V.

The internal voltage reference can be pin-strapped to fixed

values of 0.5 V or 1.0 V, or adjusted within the same range, as

discussed in the Internal Reference Connection section. Maximum SNR performance is achieved with the reference set to the

largest input span of 2 V p-p. The relative SNR degradation is

3 dB when changing from 2 V p-p mode to 1 V p-p mode.

If operation using an external reference voltage is desired, it can

be substituted for the internal reference, as detailed in the

External Reference Operation section.

Rev. 0 | Page 25 of 76

Page 26

AD6652

0

Internal Reference Connection

A comparator within the AD6

SENSE pin and configures t

652 detects the potential at the

he reference into four possible

states, which are summarized in Table 11. If SENSE is grounde

d,

In all referen

conversion core and establish its in

the ADC always equals twice the v

either an internal or an external reference.

the reference amplifier switch is connected to the internal

resistor divider (see Figure 40), setting VREF to a FIXED 1 V

reference output. Connecting the SENSE pin directly to V

REF

switches the reference amplifier output to the SENSE pin,

completing the loop and providing a fixed 0.5 V reference

output. If a resistor divider is connected, as shown in Figure 41,

the switch is again set to the SENSE pin. This puts the reference

amplifier in a noninverting mode with the VREF programmab

le

The reference amplifier switch is located near the bottom left.

The SENSE pin is shown connected to ground, which sets VREF

to 1 V. Decoupling capacitors must be duplicated for the

Channel B ADC core, if it is used. The Channel B ref amp an

ADC core are identical to those of Channel A, but a

shown.

output defined as follows:

VREF = 0.5 × (1 + R2/R1)

Table 11. Reference SENSE Operation

Selected Mode SENSE Voltage Resu (V) Resulting Differential Span (V p-p)

lting VREF

External Reference AVDD External Reference 2 × External Reference

Internal Fixed Reference VREF 0.5 1.0

Programmable Reference 0.2 V to VREF 0.5 × (1 + R2/R1) 2 × VREF (See Figure 42)

Internal Fixed Reference AGND to 0.2 V 1.0 2.0

ce configurations, REFT and REFB drive the A/D

put span. The input range of

oltage at the reference pin for

d

re not

.1µF

VINA+

VINA–

CH A

ADC

CORE

0.5V

VREF

10µF

SENSE

R

R

INT

INT

TO CH B

REF AMP

SELECT

LOGIC

REF

AMP A

VREF

Figure 40. Fixed Internal Reference Configuration

REFT_A

0.1µF

REFB_A

0.1µF

0.1µF

10µF

03198-0-029

0.1 F

µ

VINA+

VINA–

REF

AMP A

R

R

INT

INT

TO CH B

REF AMP

SELECT

LOGIC

VREF

WHERE R1 + R2 =

10kΩ TO 20kΩ

10µF

R2

R1

VREF

SENSE

Figure 41. Programmable Reference Configuration

CH A

ADC

CORE

0.5V

REFT_A

REFB_A

0.1µF

0.1µF

0.1µF

10µ

F

03198-0-030

Rev. 0 | Page 26 of 76

Page 27

AD6652

External Reference Operation

An external reference voltage can be used to enhance the gain

accuracy of the ADC or improve thermal drift characteristics.

When multiple ADCs track one another, a single reference

(internal or external) might be necessary to reduce gainmatching errors to an acceptable level. A high-precision

external reference can also be selected to provide lower gain and

offset temperature drift.

When the SENSE pin is tied to AVDD as in Figure 42, the

internal reference is disabled, allowing the use of an external

reference. An internal reference buffer loads the external

reference with an equivalent 7 kΩ load. The internal buffer still

generates the positive and negative full-scale references, REFT

and REFB, for the ADC core. The input span is always twice the

value of the reference voltage; therefore, the external reference

must be limited to a maximum of 1 V.

If the internal reference of the AD6652

s, the loading on VREF by the other converters must be

IC

onsidered. Figure 44 shows how the internal reference voltage

c

is used to drive multiple

is affected by loading.

VINA+

0.5V TO 1.0V

EXTERNAL

REFERENCE IN

0.1µF

VINA–

CH A

ADC

CORE

10µF

SENSE

+3.0V

VREF

R

R

INT

INT

TO CH B

REF AMP

SELECT

LOGIC

REF

AMP A

VREF

Figure 42. External Reference Operation with Connections

Shown for Channel A Only

REFT_A

0.1µF

0.1µF

10µF

REFB_A

0.1µF

0.5V

03198-0-031

1.2

1.0

V

= 1V

REF

0.8

= 0.5V

V

0.6

ERROR (%)

REF

V

0.4

0.2

0

–40 –30 –20 –10 0 20 6010 30 40 50 70 80 90

TEMPERATURE (°C)

REF

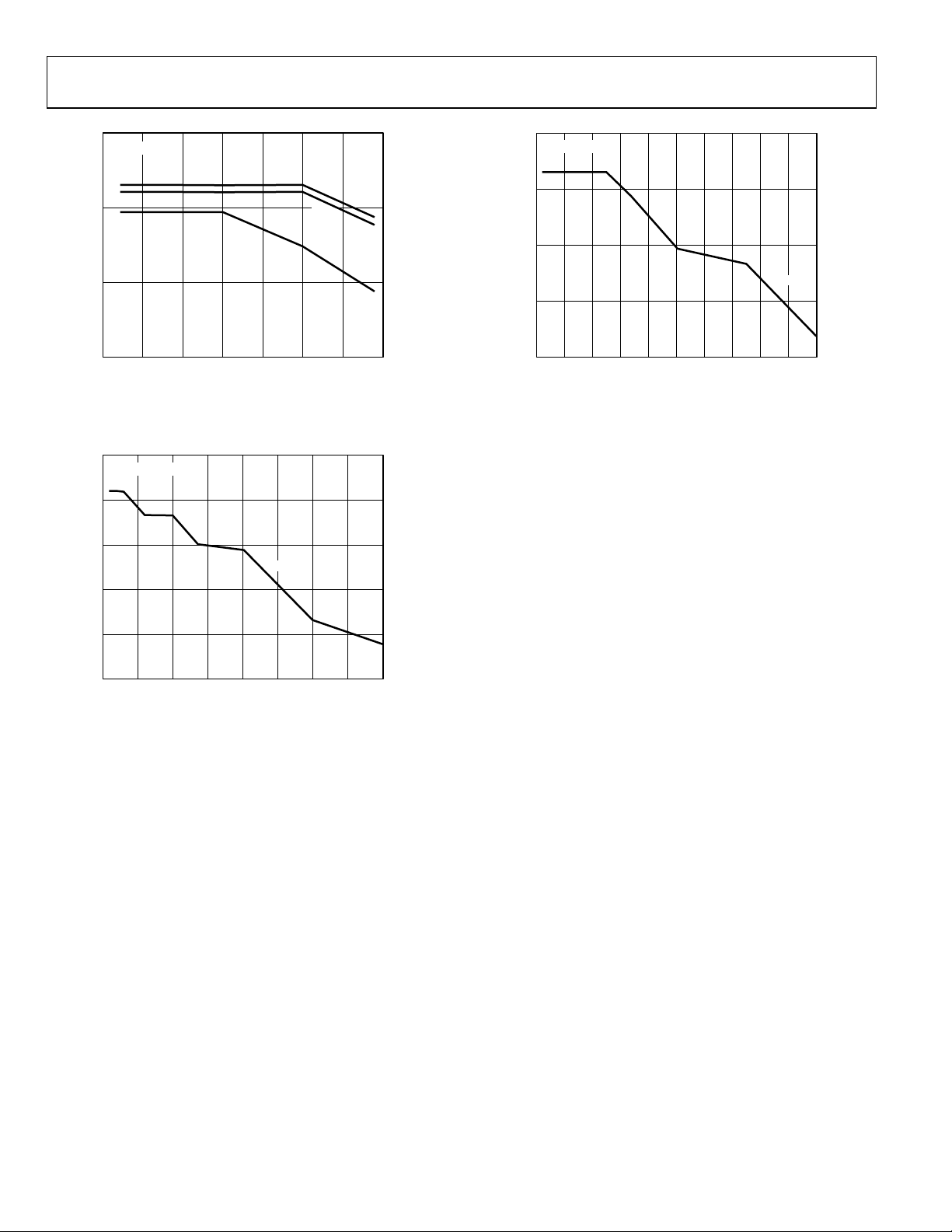

Figure 43. Typical VREF Drift

0.05

0

–0.05

–0.10

RROR (%)

E

–0.15

–0.20

–0.25

1V ERROR

1.0 1.50 0.5 2.0 2.5 3.0

LOAD (mA)

0.5V ERROR

Figure 44. VREF Accuracy vs. Load

Shared Reference Mode

The shared reference mode allows the user to connect the

references from the dual ADCs together for superior gain and

offset matching performance. If the ADCs are to function

independently, the reference decoupling should be treated

independently and can provide superior isolation between the

dual ADC channels. To enable shared reference mode, the

SHRDREF pin must be tied high and the differential references

must be externally shorted together, that is, REFTA must be

shorted externally to REFTB and REFBA must be shorted

externally to REFBB.

03198-0-075

03198-0-076

Rev. 0 | Page 27 of 76

Page 28

AD6652

Clock Input Considerations

Typical high speed ADCs use both clock edges to generate a

variety of internal timing signals, and as a result can be sensiti

to ACLK clock duty cycle. Commonly a 5% tolerance is

required on the clock duty cycle to maintain dynamic performance characteristics. The AD6652 contains a clock duty cycle

stabilizer that re-times the nonsampling edge, providing a

internal clock signal

b

sta ilizing is engaged by setting DUTYEN to logic high. This

w

allo s a wide range of ACLK clock input duty cycles without

affec

ting the performance of the AD6652 ADC stage.

e

Th duty cycle stabilizer uses a delay-locked loop (DLL) to

crea

te the nonsampling edge. As a result, any changes to the

sam low

pling frequency require approximately 2 ms to 3 ms to al

the quire and lock to the new rate.

DLL to ac

gh

Hi speed, high resolution ADCs are sensitive to the quality of

the c

lock input. The degradation in SNR at a given full-scale

inpu f

t frequency (

with a nominal 50% duty cycle. Duty cycle

) due only to aperture jitter (tA) can be

INPUT

calculated with the following equation:

SNR degradation = 20 × log10 [1/2 × p × f

In the equation, the rms aperture jitter, t

, represents the root-

A

INPUT

× tA]

sum square of all jitter sources, which include the clock inpu

analog input signal, and ADC aperture jitter specification.

Undersampling applications are particularly sensitive to jitter.

To minimize clock jitter, treat the ACLK clock input as an

analog signal. Power supplies for clock drivers should be

separated from the ADC output driver supplies to avoid

ve

n

t,

modulating the clock

crystal-controlled osci

signal with digital noise. Low jitter,

llators make the best clock sources. If the

ACLK clock is generated from another type of source (by

gating, dividing, or other methods), re-time it by the origi

clock at the tep.

last s

nal

ADC Power-Down Mode

e power dissip d by the AD6652 front-end AD is propor-

Th ate C

nal to its samp g rate. Norma DC operation uires that

tio lin l A req

th PDWN pin e set to logic lo he ADC can placed in

bo s b w. T be

a p od th o lo

ower-down m e by setting bo PDWN pins t gic high.

w power dissi ion in power-d n mode is ach ed by

Lo pat ow iev

shu e r two

tting down th eference buffers and biasing ne rks of

bo els down e d

th ADC chann . Both power- pins must b riven

tog igh pe ion

ether either h or low for pro r ADC operat .

Fo ow AC g in

r maximum p er savings, the LK and analo put(s)

ould remain st while in stan mode, result in a

sh atic dby ing

typ nsum W If t

ical power co ption of 1 m for the ADC. he clock

inp tive dby

uts remain ac while in stan mode, typical power

co th .

nsumption for e ADC is 12 mW

ADC Wake-Up Time

The deco

when entering standby mo

upling capacitors on REFT and REFB are discharged

de, and then must be recharged when

returning to normal operation. As a result, the wake-up time is

related to the time spent in standby mode. Shorter standby

cycles result in proportionally shorter wake-up times. With

recommended 0.1 µF and 10 µF deco

REFB, it takes approximately 1 s to full

and y discharge the

referenc

operatio

e buffer decoupling capacitors, and 5 ms to restore full

n.

upling capacitors on REFT

the

Rev. 0 | Page 28 of 76

Page 29

AD6652

DIGITAL DOWNCONVERTER ARCHITE RVIEW

DATA INPUT MATRIX

The digital downconverter (DDC) section features dual high

speed 12-bit input ports that are capable of crossbar multiplexing of data to the four processing channels that follow the inpu

matrix. In addition, a third input option to the matrix is

available to facilitate BIST (built-in self-test). This option is a

pseudorandom noise (PN) sequence. The dual input ports

permit diversity reception of a carrier, or they can be treated as

unrelated and independent inputs. Either input port or the P

sequence can be routed to any or all four tuner channels. This

flexibility allows up to four signals to be processed simultane

ously. Refer to the DDC Input Matrix section for a

complete description.

NUMERICALLY CONTROLLED OSCILLATOR

Frequency translation is accomplished with a 32-bit complex

numerically controlled oscillator (NCO). Each of the four

processing channels contains a separate NCO. Real data

entering this stage is separated

(Q) components. This stage translates the input signal from a

digital intermediate frequency (IF) to digital baseband. Phase

and amplitude dither can be enabled on-chip to improve

spurious performance of the NCO. A phase-offset word is

available to create a known phase relationship between multiple

AD6652s or between channels.

SECOND-ORDER rCIC FILTER

Following frequency translation is a resampling, fixed

coefficient, high s g cascade

integrator comb (rCIC2) filter, which reduces the sample rate

based on the ratio between the decimation and interpolation

registers. The resampler allows for noninteger relationships

etween the master clock and the output data rate. This stage

b

can be bypassed by setting the decimation/interpolation ratio

to 1.

peed, second-order, resamplin

FIFTH-ORDER CIC FILTER

The next stage is a fifth-order cascaded integrator comb (CIC5)

filter, whose response is defined by the decimation rate. The

purpose of these filters is to reduce the data rate to the final

filter stage and to provide antialias filtering. The reduced data

rate allows the RAM coefficient filter (RCF) stage to calculate

more taps per output.

into in-phase (I) and quadrature

CTURE OVE

more

N

-

RAM COEFFICIENT FILTER

The RAM coefficient filter (RCF) stage is a sum-of-products

FIR filter with programmable 20-bit coefficients, and decima-

t

tion rates programmable from 1 to 256 (1 to 32 in practice).

Each RAM coefficient FIR filter (RCF in Figure 1) can handle

maximum of 160 taps. Two or more RCF stages can be combined using flexible channel configuration to increase the

processing powe

The RCF outputs of each channel can be directly routed to one

or both output ports or to an AGC stage, where selected DDC

channels can be interleaved and interpolated in a half-band

filter, if desired.

INTERPOLATING HALF-BAND FILTERS AND AGC

Processed RCF data can also be routed to two half-band

interpolation stages, where up to four channels can be

combined (interleaved), interpolated by a factor of two, and

automatic gain control (AGC) applied. Each AGC stage ha

dynamic range of 96.3 dB. These stages can be bypassed

independently of each other. The outputs from the two AGC

stages are routed to both output port multiplexers. Each outpu

has a link port to permit seamless data interface with DSP

devices such as the T

selects one of the six data sources to appear at the device

parallel or link output pins.

The overall filter response for the AD6652 is the composite o

all decimating and interpolating stages. Each successive filter

stage is capable of narrower transition bandwidths, but requires

a greater number of CLK cycles to calculate the output. Mor

decimation in the first filter stage helps to minimize overal

power consumption.

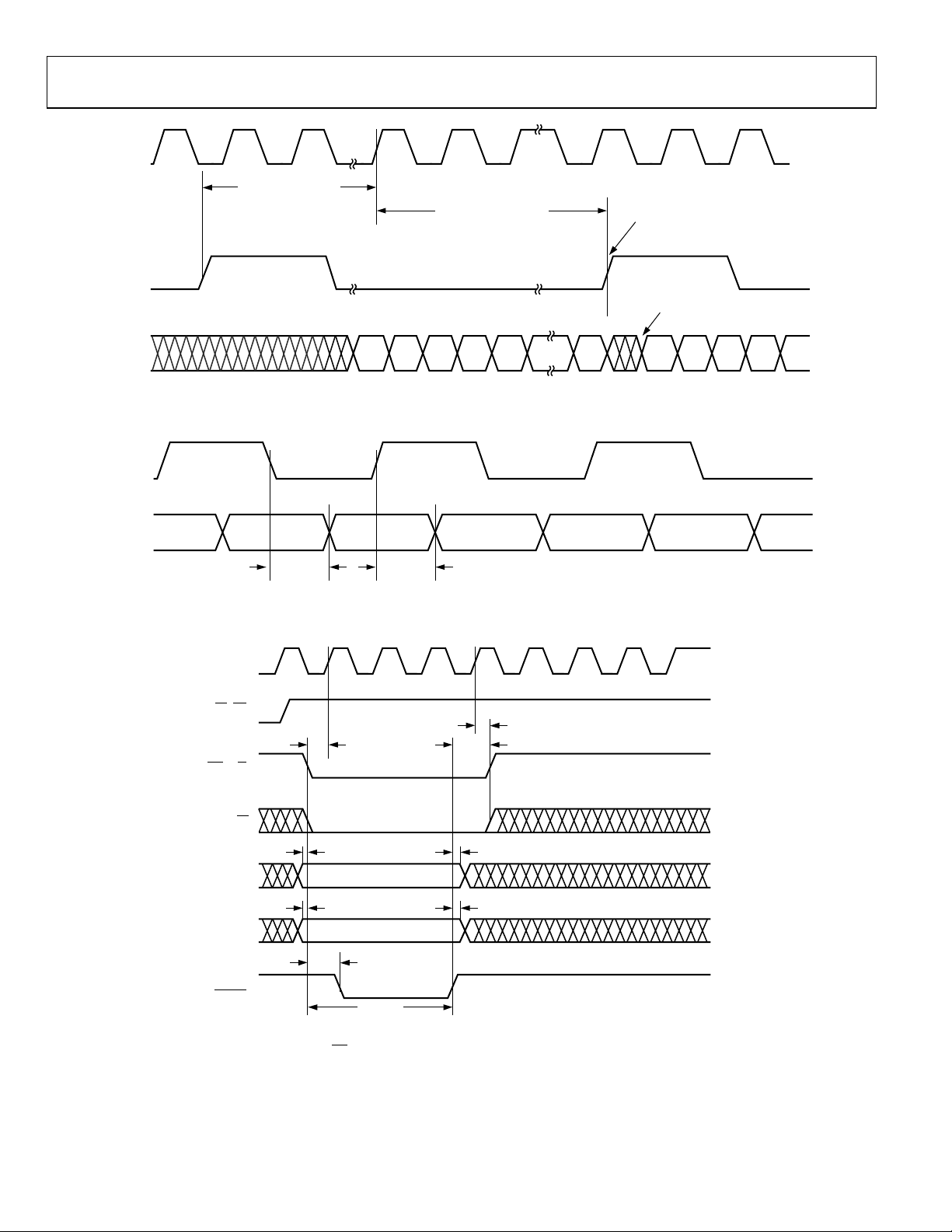

Figure 45 illustrates the basic function of the AD6652, that is, to

select and filter a single carrier from a wide input spectrum and

to down-convert it to baseband data. Figure 46 shows examples

of the combined filter response of the rCIC2, CIC5, and RCF for

narrowband and wideband carriers.

a

r beyond the 160 tap maximum.

s a

t

igerSHARC. A multiplexer for each port

f

e

l

Rev. 0 | Page 29 of 76

Page 30

AD6652

–

–

f

/2

S

f

/2 3

S

20

0

–20

–40

dBc

–60

–80

–100

–120

–1.53 104–1.03 10

(–

f

/2 TO +

f

WIDEBAND INPUT SPECTRUM

SIGNAL OF INTEREST IMAGE SIGNAL OF INTEREST

–f

f

/8 –5

S

f

/8 –5

S

–f

/4

f

f

/16

S

f

S

S

AFTER FREQUENCY TRANSLATION NCO TUNES SIGNAL TO BASEBAND

–f

/16

/4

S

/16–3

–3

S

WIDEBAND INPUT SPECTRUM (FOR EXAMPLE, 30MHz FROM HIGH SPEED ADC)

f

/16–3

S