Datasheet AD623BR-REEL7, AD623BR-REEL, AD623BR, AD623BN, AD623ARM-REEL7 Datasheet (Analog Devices)

...Page 1

Single Supply, Rail-to-Rail, Low Cost

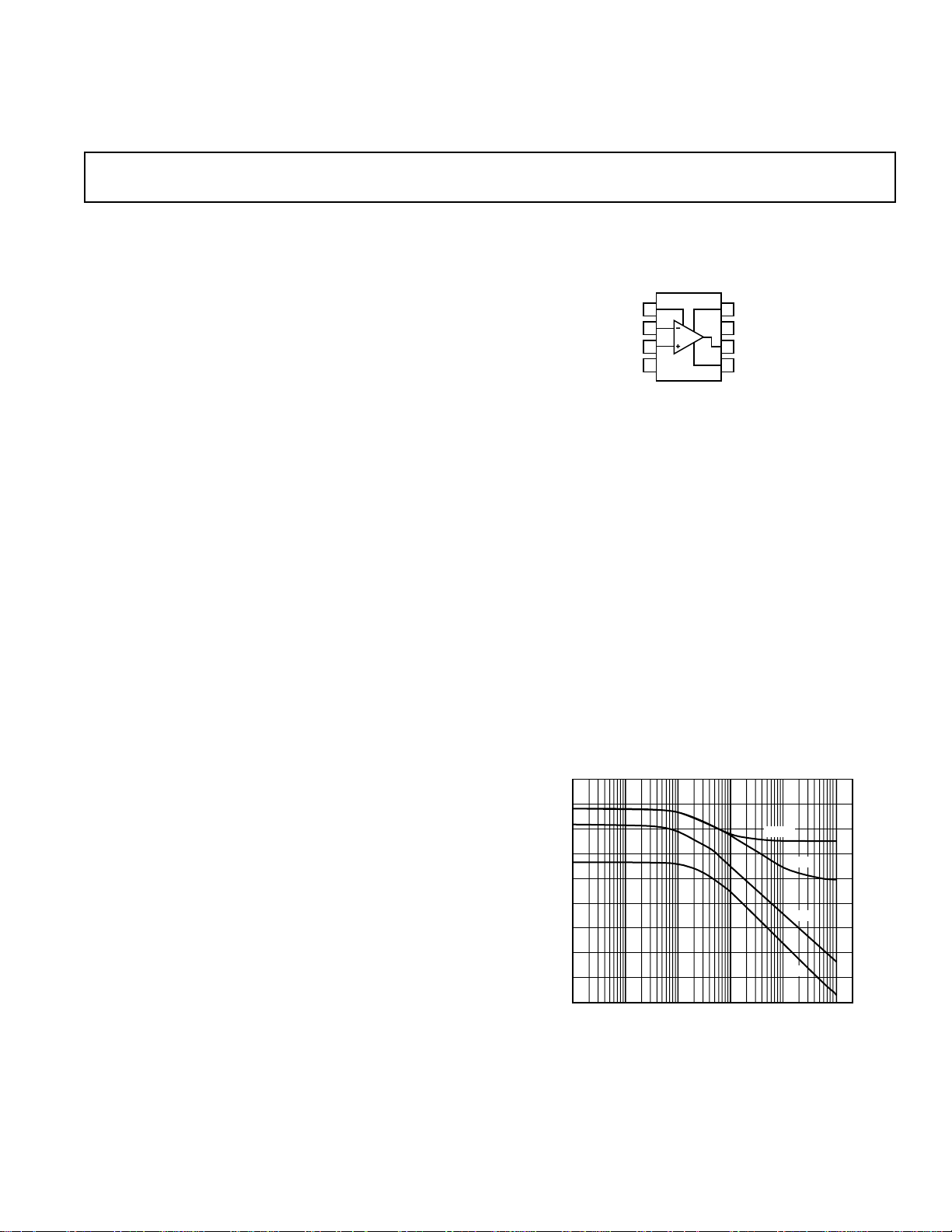

8

7

6

5

3

4

2R

G

2IN

1IN

2V

S

1R

G

1V

S

OUTPUT

REF

AD623

1

2

a

FEATURES

Easy to Use

Higher Performance than Discrete Design

Single and Dual Supply Operation

Rail-to-Rail Output Swing

Input Voltage Range Extends 150 mV Below Ground

(Single Supply)

Low Power, 575 mA Max Supply Current

Gain Set with One External Resistor

Gain Range 1 (No Resistor) to 1,000

HIGH ACCURACY DC PERFORMANCE

0.1% Gain Accuracy (G = 1)

0.35% Gain Accuracy (G > 1)

25 ppm Gain Drift (G = 1)

200 mV Max Input Offset Voltage (AD623A)

2 mV/8C Max Input Offset Drift (AD623A)

100 mV Max Input Offset Voltage (AD623B)

1 mV/8C Max Input Offset Drift (AD623B)

25 nA Max Input Bias Current

NOISE

35 nV/√Hz RTI Noise @ 1 kHz (G = 1)

EXCELLENT AC SPECIFICATIONS

90 dB Min CMRR (G = 10); 84 dB Min CMRR (G = 5)

(@ 60 Hz, 1K Source Imbalance)

800 kHz Bandwidth (G = 1)

20 ms Settling Time to 0.01% (G = 10)

APPLICATIONS

Low Power Medical Instrumentation

Transducer Interface

Thermocouple Amplifier

Industrial Process Controls

Difference Amplifier

Low Power Data Acquisition

PRODUCT DESCRIPTION

The AD623 is an integrated single supply instrumentation amplifier that delivers rail-to-rail output swing on a single supply

(+3 V to +12 V supplies). The AD623 offers superior user flexibility by allowing single gain set resistor programming, and

conforming to the 8-lead industry standard pinout configuration. With no external resistor, the AD623 is configured for

unity gain (G = 1) and with an external resistor, the AD623 can

be programmed for gains up to 1,000.

The AD623 holds errors to a minimum by providing superior

AC CMRR that increases with increasing gain. Line noise, as

well as line harmonics, will be rejected since the CMRR remains constant up to 200 Hz. The AD623 has a wide input

Instrumentation Amplifier

AD623

CONNECTION DIAGRAM

8-Lead Plastic DIP (N),

SOIC (R) and mSOIC (RM) Packages

common-mode range and can amplify signals that have a

common-mode voltage 150 mV below ground. Although the

design of the AD623 has been optimized to operate from a single

supply, the AD623 still provides superior performance when

operated from a dual voltage supply (± 2.5 V to ±6.0 V).

Low power consumption (1.5 mW at 3 V), wide supply voltage

range, and rail-to-rail output swing make the AD623 ideal for

battery powered applications. The rail-to-rail output stage maximizes the dynamic range when operating from low supply voltages. The AD623 replaces discrete instrumentation amplifier

designs and offers superior linearity, temperature stability and

reliability in a minimum of space. Until the AD623, this level of

instrumentation amplifier performance has not been achieved.

120

110

100

90

80

70

CMR – dB

60

50

40

30

1

10 100 1k 10k

FREQUENCY – Hz

Figure 1. CMR vs. Frequency, +5 VS, 0 V

x1000

x100

x10

x1

100k

S

REV. C

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

Page 2

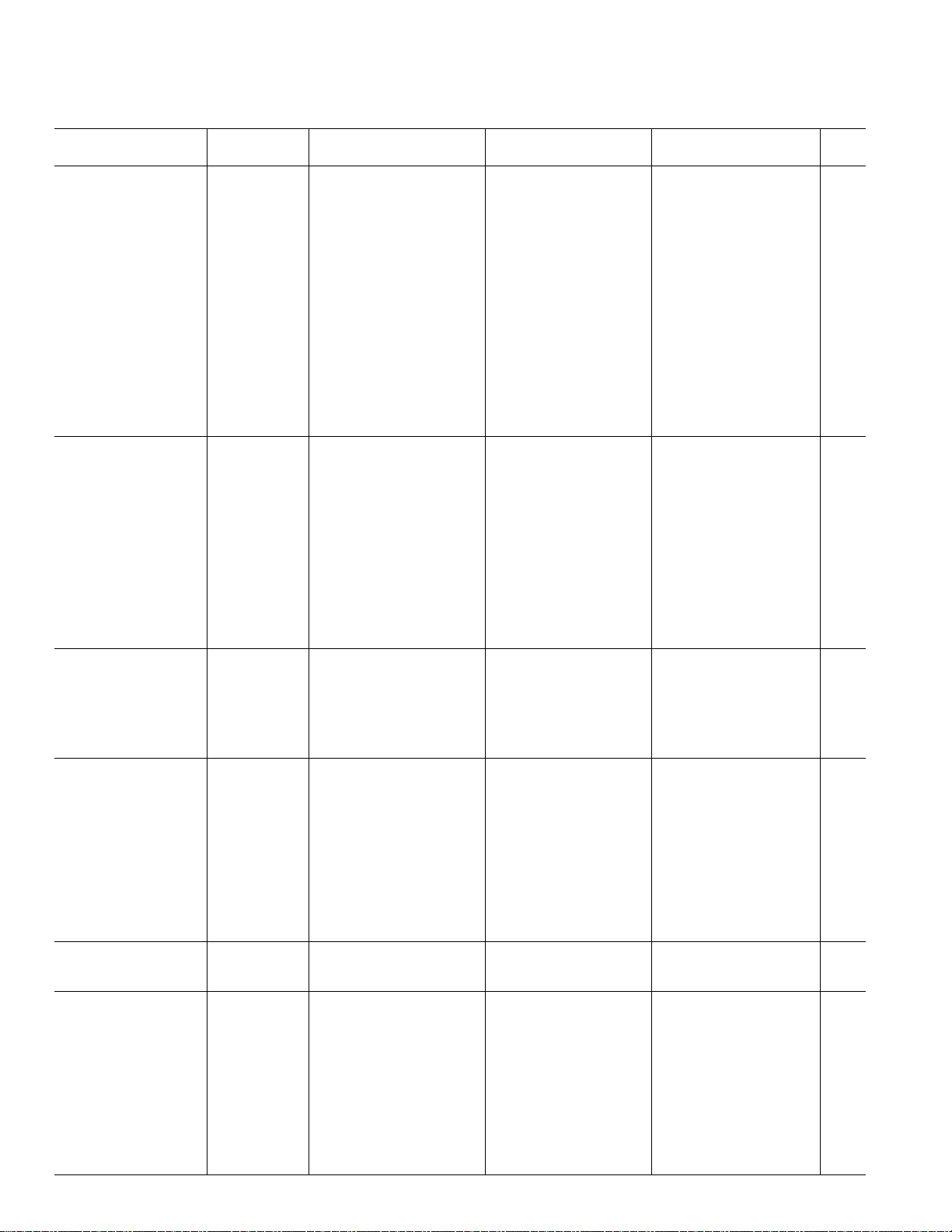

AD623–SPECIFICATIONS

SINGLE SUPPLY

(typical @ +258C Single Supply, VS = +5 V, and RL = 10 kV, unless otherwise noted)

Model AD623A AD623ARM AD623B

Specification Conditions Min Typ Max Min Typ Max Min Typ Max Units

GAIN G = 1 + (100 k/RG)

Gain Range 1 1000 1 1000 1 1000

Gain Error

1

G1 V

OUT

=

0.05 V to 3.5 V

G > 1 V

OUT

=

0.05 V to 4.5 V

G = 1 0.03 0.10 0.03 0.10 0.03 0.05 %

G = 10 0.10 0.35 0.10 0.35 0.10 0.35 %

G = 100 0.10 0.35 0.10 0.35 0.10 0.35 %

G = 1000 0.10 0.35 0.10 0.35 0.10 0.35 %

Nonlinearity, G1 V

OUT

=

0.05 V to 3.5 V

G > 1 V

OUT

=

0.05 V to 4.5 V

G = 1–1000 50 50 50 ppm

Gain vs. Temperature

G = 1 5 10 5 10 5 10 ppm/°C

1

G > 1

50 50 50 ppm/°C

VOLTAGE OFFSET Total RTI Error =

V

+ V

Input Offset, V

OSI

OSI

OSO

/G

25 200 200 500 25 100 µV

Over Temperature 350 650 160 µV

Average TC 0.1 2 0.1 2 0.1 1 µV/°C

Output Offset, V

OSO

200 1000 500 2000 200 500 µV

Over Temperature 1500 2600 1100 µV

Average TC 2.5 10 2.5 10 2.5 10 µV/°C

Offset Referred to the Input

vs. Supply (PSR)

G = 1 80 100 80 100 80 100 dB

G = 10 100 120 100 120 100 120 dB

G = 100 120 140 120 140 120 140 dB

G = 1000 120 140 120 140 120 140 dB

INPUT CURRENT

Input Bias Current 17 25 17 25 17 25 nA

Over Temperature 27.5 27.5 27.5 nA

Average TC 25 25 25 pA/°C

Input Offset Current 0.25 2 0.25 2 0.25 2 nA

Over Temperature 2.5 2.5 2.5 nA

Average TC 5 5 5 pA/°C

INPUT

Input Impedance

Differential 2i22i22i2GΩipF

Common-Mode 2i22i22i2GΩipF

Input Voltage Range

2

VS = +3 V to +12 V (–VS) – 0.15 (+VS) – 1.5 (–VS) – 0.15 (+VS) – 1.5 (–VS) – 0.15 (+VS) – 1.5 V

Common-Mode Rejection at

60 Hz with 1 kΩ Source

Imbalance

G = 1 VCM = 0 V to 3 V 70 80 70 80 77 86 dB

G = 10 VCM = 0 V to 3 V 90 100 90 100 94 100 dB

G = 100 VCM = 0 V to 3 V 105 110 105 110 105 110 dB

G = 1000 VCM = 0 V to 3 V 105 110 105 110 105 110 dB

OUTPUT

Output Swing R

= 10 kΩ +0.01 (+V

L

R

= 100 kΩ +0.01 (+V

L

) – 0.5 +0.01 (+VS) – 0.5 +0.01 (+VS) – 0.5 V

S

) – 0.15 +0.01 (+VS) – 0.15 +0.01 (+VS) – 0.15 V

S

DYNAMIC RESPONSE

Small Signal –3 dB

Bandwidth

G = 1 800 800 800 kHz

G = 10 100 100 100 kHz

G = 100 10 10 10 kHz

G = 1000 2 2 2 kHz

Slew Rate 0.3 0.3 0.3 V/µs

Settling Time to 0.01% VS = +5 V

G = 1 Step Size: 3.5 V 30 30 30 µ s

G = 10 Step Size: 4 V,

V

= 1.8 V 20 20 20 µs

CM

–2–

REV. C

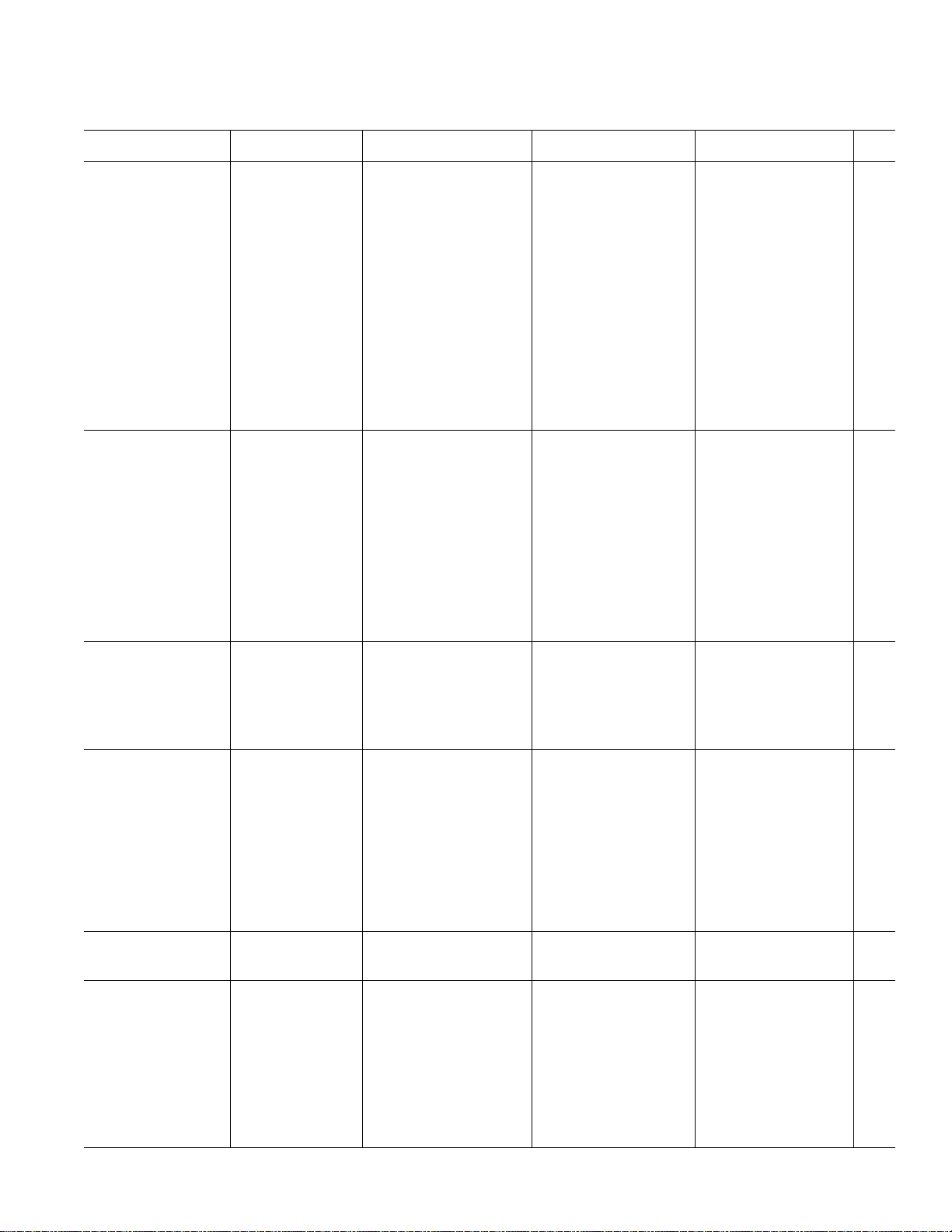

Page 3

AD623

DUAL SUPPLIES

(typical @ +258C Dual Supply, VS = 65 V, and RL = 10 kV, unless otherwise noted)

Model AD623A AD623ARM AD623B

Specification Conditions Min Typ Max Min Typ Max Min Typ Max Units

GAIN G = 1 + (100 k/RG)

Gain Range 1 1000 1 1000 1 1000

Gain Error

1

G1 V

OUT

=

–4.8 V to 3.5 V

G > 1 V

OUT

=

0.05 V to 4.5 V

G = 1 0.03 0.10 0.03 0.10 0.03 0.05 %

G = 10 0.10 0.35 0.10 0.35 0.10 0.35 %

G = 100 0.10 0.35 0.10 0.35 0.10 0.35 %

G = 1000 0.10 0.35 0.10 0.35 0.10 0.35 %

Nonlinearity, G1 V

OUT

=

–4.8 V to 3.5 V

G > 1 V

OUT

=

–4.8 V to 4.5 V

G = 1–1000 50 50 50 ppm

Gain vs. Temperature

G = 1 5 10 5 10 5 10 ppm/°C

1

G > 1

50 50 50 ppm/°C

VOLTAGE OFFSET Total RTI Error =

V

+ V

Input Offset, V

OSI

OSI

OSO

/G

25 200 200 500 25 100 µV

Over Temperature 350 650 160 µV

Average TC 0.1 2 0.1 2 0.1 1 µV/°C

Output Offset, V

OSO

200 1000 500 2000 200 500 µV

Over Temperature 1500 2600 1100 µV

Average TC 2.5 10 2.5 10 2.5 10 µV/°C

Offset Referred to the Input

vs. Supply (PSR)

G = 1 80 100 80 100 80 100 dB

G = 10 100 120 100 120 100 120 dB

G = 100 120 140 120 140 120 140 dB

G = 1000 120 140 120 140 120 140 dB

INPUT CURRENT

Input Bias Current 17 25 17 25 17 25 nA

Over Temperature 27.5 27.5 27.5 nA

Average TC 25 25 25 pA/°C

Input Offset Current 0.25 2 0.25 2 0.25 2 nA

Over Temperature 2.5 2.5 2.5 nA

Average TC 5 5 5 pA/°C

INPUT

Input Impedance

Differential 2i22i22i2GΩipF

Common-Mode 2i22i22i2GΩipF

Input Voltage Range

2

V

= +2.5 V to ±6 V (–V

S

) – 0.15 (+VS) – 1.5 (–VS) –0.15 (+VS) – 1.5 (–VS) – 0.15 (+VS) – 1.5 V

S

Common-Mode Rejection at

60 Hz with 1 kΩ Source

Imbalance

G = 1 VCM = +3.5 V to –5.15 V 70 80 70 80 77 86 dB

G = 10 VCM = +3.5 V to –5.15 V 90 100 90 100 94 100 dB

G = 100 VCM = +3.5 V to –5.15 V 105 110 105 110 105 110 dB

G = 1000 VCM = +3.5 V to –5.15 V 105 110 105 110 105 110 dB

OUTPUT

Output Swing R

= 10 kΩ, VS = ±5 V (–V

L

R

= 100 kΩ (–V

L

) +0. 2 (+VS) – 0.5 (–VS) + 0.2 (+VS) – 0.5 (–VS) + 0.2 (+VS) – 0.5 V

S

) + 0.05 (+VS) – 0.15 (–VS) + 0.05 (+VS) – 0.15 (–VS) + 0.05 (+VS) – 0.15 V

S

DYNAMIC RESPONSE

Small Signal –3 dB

Bandwidth

G = 1 800 800 800 kHz

G = 10 100 100 100 kHz

G = 100 10 10 10 kHz

G = 1000 2 2 2 kHz

Slew Rate 0.3 0.3 0.3 V/µs

Settling Time to 0.01% V

= ±5 V, 5 V Step

S

G = 1 30 30 30 µ s

G = 10 20 20 20 µ s

–3–REV. C

Page 4

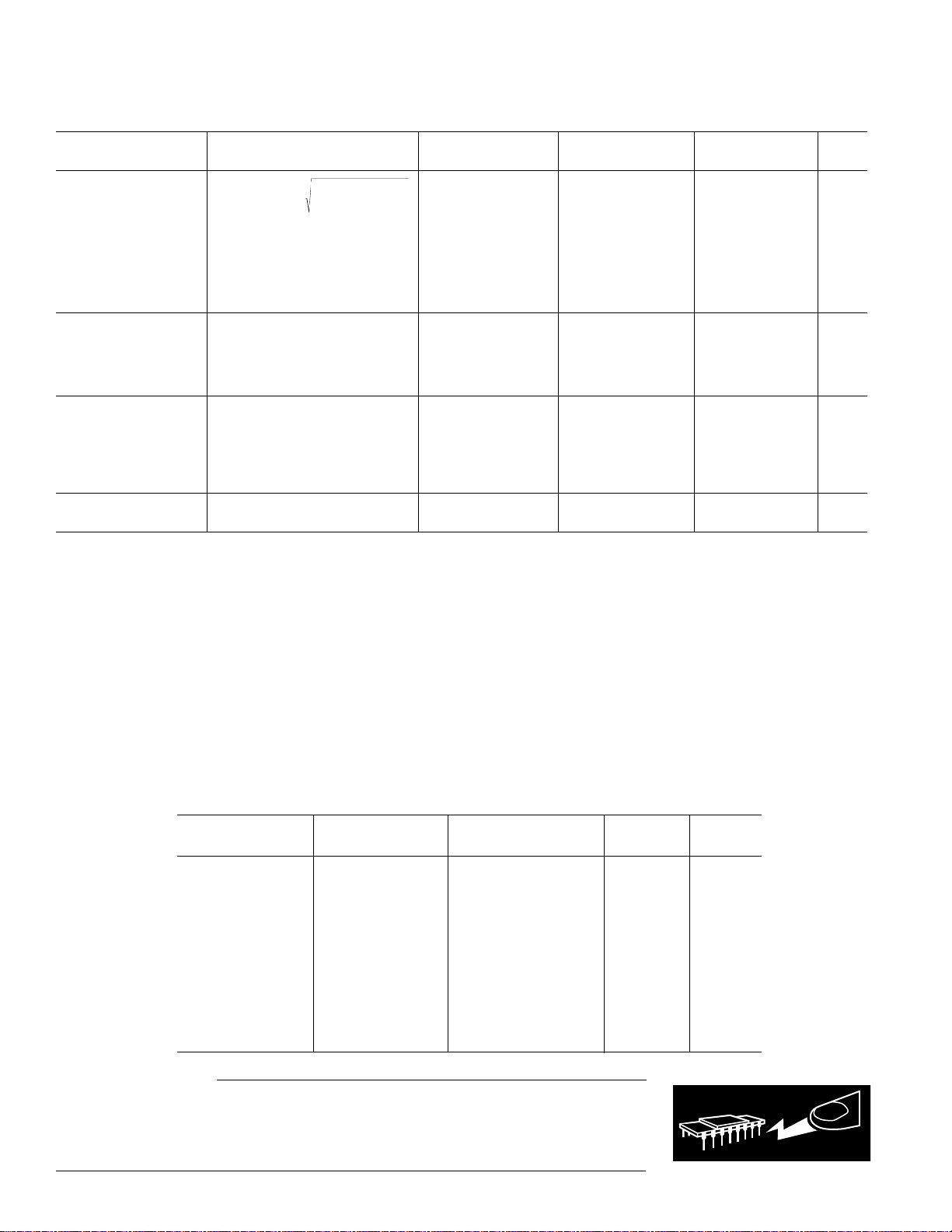

AD623–SPECIFICATIONS

WARNING!

ESD SENSITIVE DEVICE

BOTH DUAL AND SINGLE SUPPLIES

Model AD623A AD623ARM AD623B

Specification Conditions Min Typ Max Min Typ Max Min Typ Max Units

NOISE

Voltage Noise, 1 kHz Total RTI Noise =

Input, Voltage Noise, e

Output, Voltage Noise, e

RTI, 0.1 Hz to 10 Hz

G = 1 3.0 3.0 3.0 µV p-p

G = 1000 1.5 1.5 1.5 µV p-p

Current Noise f = 1 kHz 100 100 100 fA/√Hz

0.1 Hz to 10 Hz 1.5 1.5 1.5 pA p-p

REFERENCE INPUT

R

IN

I

IN

Voltage Range –V

Gain to Output 1 ± 0.0002 1 ± 0.0002 1 ± 0.0002 V

POWER SUPPLY

Operating Range Dual Supply ±2.5 ±6 ±2.5 ±6 ±2.5 ±6V

Quiescent Current Dual Supply 375 550 375 550 375 550 µA

Over Temperature 625 625 625 µA

TEMPERATURE RANGE

For Specified Performance –40 to +85 –40 to +85 –40 to +85 °C

NOTES

1

Does not include effects of external resistor RG.

2

One input grounded. G = 1.

Specifications subject to change without notice.

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±6 V

Internal Power Dissipation

ni

no

V

, V

= 0 +50 +60 +50 +60 +50 +60 µA

IN+

REF

Single Supply +2.7 +12 +2.7 +12 +2.7 +12 V

Single Supply 305 480 305 480 305 480 µA

1

2

. . . . . . . . . . . . . . . . . . . . 650 mW

e

ni

2

+ e

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . ±6 V

Output Short Circuit Duration . . . . . . . . . . . . . . . . Indefinite

Storage Temperature Range

(N, R, RM) . . . . . . . . . . . . . . . . . . . . . . . –65°C to +125°C

Operating Temperature Range

(A) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –40°C to +85°C

2

/G

no

ORDERING GUIDE

35 35 35 nV/√Hz

50 50 50 nV/√Hz

100 ±20% 100 ±20% 100 ±20% kΩ

S

+VS–V

S

+VS–V

S

+V

S

Lead Temperature Range

(Soldering 10 seconds) . . . . . . . . . . . . . . . . . . . . . . +300°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Specification is for device in free air:

8-Lead Plastic DIP Package: θ

8-Lead SOIC Package: θ

8-Lead µSOIC Package: θJA = 200°C/W

= 95°C/W

JA

= 155°C/W

JA

V

Temperature Package Package Brand

Model Range Description Option Code

AD623AN –40°C to +85°C 8-Lead Plastic DIP N-8

AD623AR –40°C to +85°C 8-Lead SOIC SO-8

AD623ARM –40°C to +85°C 8-Lead µSOIC RM-8 J0A

AD623AR-REEL –40°C to +85°C 13" Tape and Reel SO-8

AD623AR-REEL7 –40°C to +85°C 7" Tape and Reel SO-8

AD623ARM-REEL –40°C to +85°C 13" Tape and Reel RM-8 J0A

AD623ARM-REEL7 –40°C to +85°C 7" Tape and Reel RM-8 J0A

AD623BN –40°C to +85°C 8-Lead Plastic DIP N-8

AD623BR –40°C to +85°C 8-Lead SOIC SO-8

AD623BR-REEL –40°C to +85°C 13" Tape and Reel SO-8

AD623BR-REEL7 –40°C to +85°C 7" Tape and Reel SO-8

ESD SUSCEPTIBILITY

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 volts, which

readily accumulate on the human body and on test equipment, can discharge without detection.

Although the AD623 features proprietary ESD protection circuitry, permanent damage may still

occur on these devices if they are subjected to high energy electrostatic discharges. Therefore, proper

ESD precautions are recommended to avoid any performance degradation or loss of functionality.

–4–

REV. C

Page 5

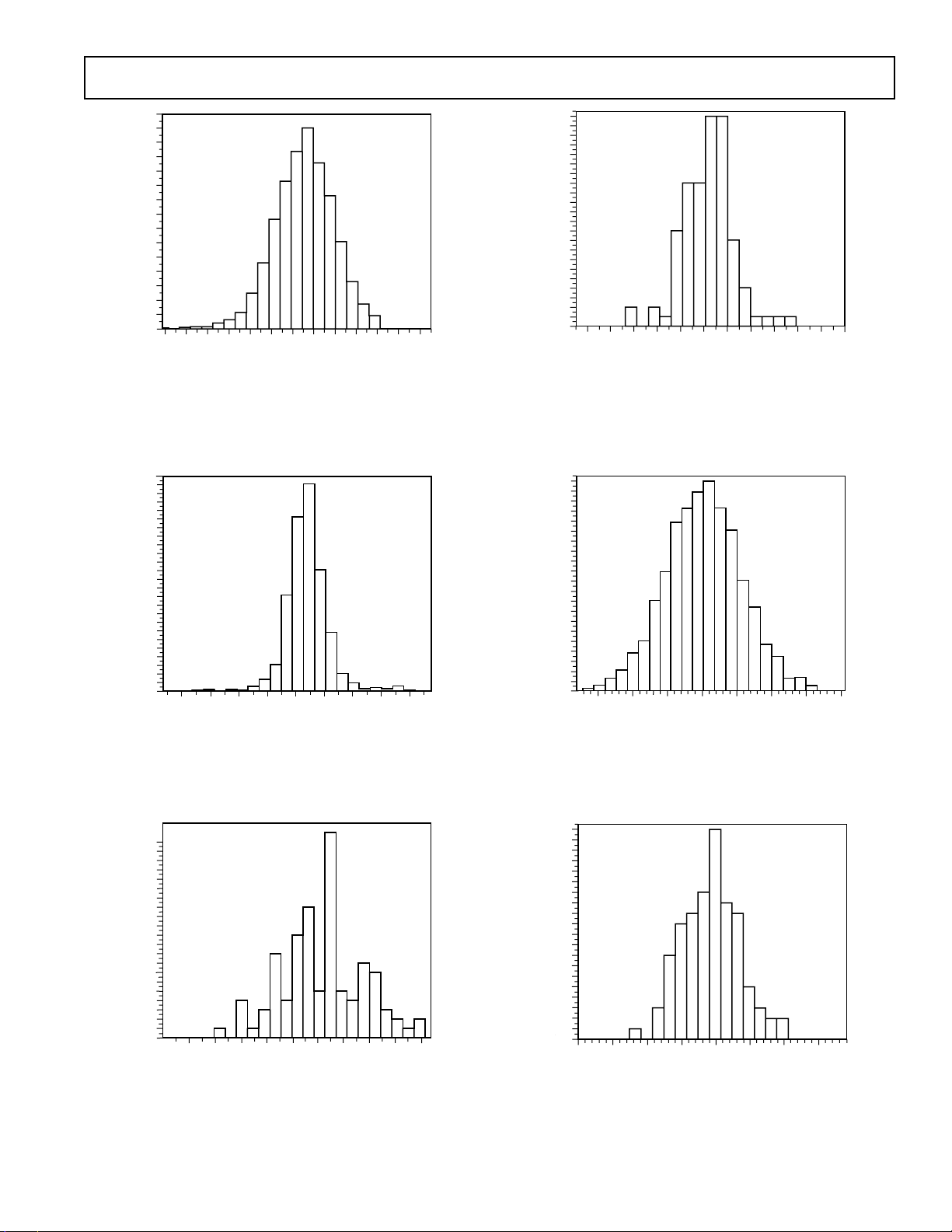

Typical Characteristics

INPUT OFFSET CURRENT – nA

150

0

–0.245 –0.21

UNITS

–0.24 –0.235 –0.23 –0.225 –0.22 –0.215

90

60

30

120

180

210

(@ +258C VS = 65 V, R

= 10 kV unless otherwise noted)–

L

AD623

300

280

260

240

220

200

180

160

140

UNITS

120

100

80

60

40

20

0

–100

–80

–60 –20–40

INPUT OFFSET VOLTAGE – mV

20 120

140

1008060400

Figure 2. Typical Distribution of Input Offset Voltage;

Package Option N-8, SO-8

480

420

360

300

240

UNITS

180

120

60

0

–800 –600

–400 –200

OUTPUT OFFSET VOLTAGE 2 mV

0 200 400 600 800

22

20

18

16

14

12

10

UNITS

8

6

4

2

0

–600

–300 –200 –100

–5000–400

OUTPUT OFFSET VOLTAGE – mV

100 200 300 400

500

Figure 5. Typical Distribution of Output Offset Voltage,

V

= +5, Single Supply, V

S

= –0.125 V; Package Option

REF

N-8, SO-8

Figure 3. Typical Distribution of Output Offset Voltage;

Package Option N-8, SO-8

22

20

18

16

14

12

10

UNITS

8

Figure 4. Typical Distribution of Input Offset Voltage,

V

S

6

4

2

0

–80 –60

–40 –20

INPUT OFFSET VOLTAGE – mV

= +5, Single Supply, V

N-8, SO-8

0 20 40 60 80 100

= –0.125 V; Package Option

REF

Figure 6. Typical Distribution for Input Offset Current;

Package Option N-8, SO-8

20

18

16

14

12

10

UNITS

8

6

4

2

0

–0.025

–0.02

–0.015 –0.01 –0.005

INPUT OFFSET CURRENT – nA

0 0.005

Figure 7. Typical Distribution for Input Offset Current,

= +5, Single Supply, V

V

S

= –0.125 V; Package Option

REF

N-8, SO-8

–5–REV. C

0.01

Page 6

AD623

1600

1400

1200

1000

800

UNITS

600

400

200

0

75 80

85 90 95

105 110 115 120 125 130

100

CMRR 2 dB

Figure 8. Typical Distribution for CMRR (G = 1)

1k

100

GAIN = 1

30

25

20

– nA

15

BIAS

I

10

5

0

–60 –40

1k

100

–20 0 20 40 60 80 100 120

TEMPERATURE – 8C

Figure 11. I

vs. Temp

BIAS

140

NOISE – nV/!Hz, RTI

10

GAIN = 100

GAIN = 1000

1

10 100

FREQUENCY – Hz

1k

GAIN = 10

10k

100k

Figure 9. Voltage Noise Spectral Density vs. Frequency

21

20

19

– nA

18

BIAS

I

17

16

15

–5 4

–4

Figure 10. I

–2

CMV – Volts

BIAS

02

vs. CMV, VS = ±5 V

CURRENT NOISE – fA/!Hz

10

1

FREQUENCY – Hz

100

1k10

Figure 12. Current Noise Spectral Density vs. Frequency

19.5

19.0

18.5

– nA

18.0

BIAS

I

17.5

17.0

16.5

–3 –2 –1

Figure 13. I

CMV – Volts

vs. CMV, VS = ±2.5 V

BIAS

01

–6–

REV. C

Page 7

120

110

100

90

80

70

60

50

40

30

1

10 100 1k 10k

100k

FREQUENCY – Hz

CMR – dB

x1000

x10

x1

x100

100 1k 10k 100k 1M

FREQUENCY – Hz

70

60

50

40

30

20

10

0

–10

–20

–30

GAIN – dB

AD623

Figure 14. 0.1 Hz to 10 Hz Current Noise (0.71 pA/Div)

RTO

RTI

Figure 15. 0.1 Hz to 10 Hz RTI Voltage Noise

µ

(1 Div = 1

120

110

100

90

80

70

CMR – dB

60

50

40

30

1

Figure 16. CMR vs. Frequency, +5, 0 VS, V

V p-p)

10 100 1k 10k

FREQUENCY – Hz

x1000

x100

x1

x10

100k

= 2.5 V

REF

Figure 17. CMR vs. Frequency, ±5 V

S

Figure 18. Gain vs. Frequency (VS = +5 V, 0 V), V

5

4

3

2

1

0

–1

OUTPUT – Volts

–2

–3

–4

–5

–6

–5

–4 –3 –2 –1 0 1 2 3 4 5

COMMON MODE INPUT – Volts

VS = 65

VS = 62.5

Figure 19. Maximum Output Voltage vs. Common Mode,

G = 1, R

= 100 k

L

Ω

–7–REV. C

= 2.5 V

REF

Page 8

AD623

5

4

3

2

1

0

–1

OUTPUT – Volts

–2

–3

–4

–5

–6

–5

VS = 62.5

–4 –3 –2 –1 0 1 2 3 4 5

COMMON MODE INPUT – Volts

VS = 65

Figure 20. Maximum Output Voltage vs. Common Mode,

≥

10, RL = 100 k

G

5

4

3

Ω

140

120

100

80

60

PSRR – dB

40

20

0

1

10 100 1k 10k

FREQUENCY – Hz

G = 1000

G = 100

G = 10

G = 1

Figure 23. Positive PSRR vs. Frequency, ±5 V

140

120

100

80

G = 1000

G = 100

100k

S

2

OUTPUT – Volts

1

0

–1 50

1234

COMMON MODE INPUT – Volts

Figure 21. Maximum Output Voltage vs. Common Mode,

G = 1, V

= +5 V, RL = 100 k

S

5

4

3

2

OUTPUT – Volts

1

0

–1 50

Ω

1234

COMMON MODE INPUT – Volts

60

PSRR – dB

40

20

0

1

10 100 1k 10k

FREQUENCY – Hz

G = 10

G = 1

100k

Figure 24. Positive PSRR vs. Frequency, +5 VS, 0 V

140

120

100

80

60

PSRR – dB

40

20

0

1

10 100 1k 10k

FREQUENCY – Hz

G = 1000

G = 100

G = 10

G = 1

100k

S

Figure 22. Maximum Output Voltage vs. Common Mode,

≥

10, VS = +5 V, RL = 100 k

G

Ω

–8–

Figure 25. Negative PSRR vs. Frequency, ±5 V

S

REV. C

Page 9

10

8

6

V p–p

4

2

0

AD623

= 65

V

S

V

= 62.5

S

0

20

40

FREQUENCY – kHz

60

80

100

Figure 26. Large Signal Response, G ≤ 10

1000

100

10

SETTLING TIME – ms

1

1

10

GAIN – V/V

100

1000

Figure 27. Settling Time to 0.01% vs. Gain, for a 5 V Step

at Output, C

= 100 pF, VS = ±5 V

L

Figure 29. Large Signal Pulse Response and Settling Time,

G = –10 (0.250 mV = 0.01%), C

= 100 pF

L

Figure 30. Large Signal Pulse Response and Settling

Time, G = 100, C

= 100 pF

L

Figure 28. Large Signal Pulse Response and Settling

Time, G = –1 (0.250 mV = 0.01%), C

= 100 pF

L

Figure 31. Large Signal Pulse Response and Settling

Time, G = –1000 (5 mV = 0.01%), C

= 100 pF

L

–9–REV. C

Page 10

AD623

Figure 32. Small Signal Pulse Response, G = 1, RL = 10 kΩ,

= 100 pF

C

L

Figure 33. Small Signal Pulse Response, G = 10,

R

= 10 kΩ, CL = 100 pF

L

Figure 35. Small Signal Pulse Response, G = 1000,

R

= 10 kΩ, CL = 100 pF

L

Figure 36. Gain Nonlinearity, G = –1 (50 ppm/Div)

Figure 34. Small Signal Pulse Response G = 100,

R

= 10 kΩ, CL = 100 pF

L

–10–

Figure 37. Gain Nonlinearity, G = –10 (6 ppm/Div)

REV. C

Page 11

AD623

The output voltage at Pin 6 is measured with respect to the

potential at Pin 5. The impedance of the reference pin is 100 kΩ ,

so in applications requiring V/I conversion, a small resistor

between Pins 5 and 6 is all that is needed.

POS SUPPLY

7

Figure 38. Gain Nonlinearity (G = –100, 15 ppm/Div)

V+

(V+) –0.5

(V+) –1.5

(V+) –1.5

SWING – Volts

(V–) +0.5

V–

0 0.5

OUTPUT CURRENT – mA

1

1.5

2

Figure 39. Output Voltage Swing vs. Output Current

THEORY OF OPERATION

The AD623 is an instrumentation amplifier based on a modified

classic three op amp approach, to assure single or dual supply

operation even at common-mode voltages at the negative supply

rail. Low voltage offsets, input and output, as well as absolute

gain accuracy, and one external resistor to set the gain, make the

AD623 one of the most versatile instrumentation amplifiers in

its class.

The input signal is applied to PNP transistors acting as voltage

buffers and providing a common-mode signal to the input

amplifiers (Figure 40). An absolute value 50 kΩ resistor in each

of the amplifiers’ feedback assures gain programmability.

The differential output is

= 1+

100 kΩ

V

O

V

C

R

G

The differential voltage is then converted to a single-ended

voltage using the output amplifier, which also rejects any commonmode signal at the output of the input amplifiers.

Since all the amplifiers can swing to either supply rails, as well

as have their common-mode range extended to below the negative supply rail, the range over which the AD623 can operate is

further enhanced (Figures 19 and 20).

4

7

4

+

–

50kV 50kV

50kV

50kV

–

+

50kV

–

+

50kV

OUT

REF

6

5

INVERTING

2

1

GAIN

8

NON-

INVERTING

3

NEG SUPPLY

Figure 40. Simplified Schematic

The bandwidth of the AD623 is reduced as the gain is increased,

since all the amplifiers are of voltage feedback type. At unity

gain, it is the output amplifier that limits the bandwidth. Therefore even at higher gains the AD623 bandwidth does not roll off

as quickly.

APPLICATIONS

Basic Connection

Figure 41 shows the basic connection circuit for the AD623.

The +V

The supply can be either bipolar (V

single supply (–V

and –VS terminals are connected to the power supply.

S

= 0 V, +VS = 3.0 V to 12 V). Power supplies

S

= ±2.5 V to ±6 V) or

S

should be capacitively decoupled close to the devices power

pins. For best results, use surface mount 0.1 µF ceramic chip

capacitors and 10 µF electrolytic tantalum capacitors.

The input voltage, which can be either single-ended (tie either

–IN or +IN to ground) or differential is amplified by the programmed gain. The output signal appears as the voltage difference

between the Output pin and the externally applied voltage on

the REF input. For a ground referenced output, REF should be

grounded.

GAIN SELECTION

The AD623’s gain is resistor programmed by RG, or more precisely, by whatever impedance appears between Pins 1 and 8.

The AD623 is designed to offer accurate gains using 0.1%–1%

tolerance resistors. Table I shows required values of R

various gains. Note that for G = 1, the R

nected (R

= `). For any arbitrary gain, RG can be calculated

G

terminals are uncon-

G

G

for

by using the formula

R

= 100 kΩ/(G – 1)

G

REFERENCE TERMINAL

The reference terminal potential defines the zero output voltage

and is especially useful when the load does not share a precise

ground with the rest of the system. It provides a direct means of

injecting a precise offset to the output. The reference terminal is

also useful when bipolar signals are being amplified as it can be

used to provide a virtual ground voltage. The voltage on the

reference terminal can be varied from –V

to +VS.

S

–11–REV. C

Page 12

AD623

+V

S

+2.5V TO +6V

10mF

0.1mF

R

G

R

V

G

IN

R

G

–V

OUTPUT

REF

0.1mF

–2.5V TO –6V

S

10mF

V

OUT

REF (INPUT)

a. Dual Supply b. Single Supply

Figure 41. Basic Connections

Table I. Required Values of Gain Resistors

Desired 1% Std Table Calculated Gain

Gain Value of RG, V Using 1% Resistors

2 100 k 2

5 24.9 k 5.02

10 11 k 10.09

20 5.23 k 20.12

33 3.09 k 33.36

40 2.55 k 40.21

50 2.05 k 49.78

65 1.58 k 64.29

100 1.02 k 99.04

200 499 201.4

500 200 501

1000 100 1001

INPUT AND OUTPUT OFFSET VOLTAGE

The low errors of the AD623 are attributed to two sources,

input and output errors. The output error is divided by the

programmed gain when referred to the input. In practice, the

input errors dominate at high gains and the output errors dominate at low gains. The total V

for a given gain is calculated as:

OS

Total Error RTI = Input Error + (Output Error/G)

×

Total Error RTO = (Input Error

G) + Output Error

RTI offset errors and noise voltages for different gains are shown

below in Table II.

Table II. RTI Error Sources

Max Max

Total Input Total Input Total Input

Offset Error Offset Drift Referred Noise

Gain mV mV mV/8C mV/8C (nV/√Hz)

AD623A AD623B AD623A AD623B AD623A & AD623B

1 1200 600 12 11 62

2 700 350 7 6 45

5 400 200 4 3 38

10 300 150 3 2 35

20 250 125 2.5 1.5 35

50 220 110 2.2 1.2 35

100 210 105 2.1 1.1 35

1000 200 100 2 1 35

+V

S

+3V TO +12V

0.1mF

R

G

R

V

G

IN

R

G

OUTPUT

REF

10mF

V

OUT

REF (INPUT)

INPUT PROTECTION

Internal supply referenced clamping diodes allow the input,

reference, output and gain terminals of the AD623 to safely

withstand overvoltages of 0.3 V above or below the supplies.

This is true for all gains, and for power on and off. This last

case is particularly important since the signal source and amplifier may be powered separately.

If the overvoltage is expected to exceed this value, the current

through these diodes should be limited to about 10 mA using

external current limiting resistors. This is shown in Figure 42.

The size of this resistor is defined by the supply voltage and the

required overvoltage protection.

+V

S

1 = 10mA MAX

R

V

V

OVER

OVER

LIM

R

R

LIM

G

AD623

2V

S

OUTPUT

V

2VS +0.7V

OVER

R

=

LIM

10mA

Figure 42. Input Protection

RF INTERFERENCE

All instrumentation amplifiers can rectify high frequency out-ofband signals. Once rectified, these signals appear as dc offset

errors at the output. The circuit of Figure 43 provides good RFI

suppression without reducing performance within the in amps

pass band. Resistor R1 and capacitor C1 (and likewise, R2 and

C2) form a low-pass RC filter that has a –3 dB BW equal to:

F = 1/(2 π R1C1). Using the component values shown, this

filter has a –3 dB bandwidth of approximately 40 kHz. Resistors

R1 and R2 were selected to be large enough to isolate the

circuit’s input from the capacitors, but not large enough to

significantly increase the circuit’s noise. To preserve commonmode rejection in the amplifier’s pass band, capacitors C1 and

C2 need to be 5% or better units, or low cost 20% units can be

tested and “binned” to provide closely matched devices.

Capacitor C3 is needed to maintain common-mode rejection at

the low frequencies. R1/R2 and C1/C2 form a bridge circuit

whose output appears across the in amp’s input pins. Any

mismatch between C1 and C2 will unbalance the bridge and

reduce common-mode rejection. C3 ensures that any RF signals

–12–

REV. C

Page 13

AD623

R

G

2

–INPUT

+INPUT

100V

AD623

V

OUT

AD8031

+V

S

REFERENCE

–V

S

R

G

2

are common mode (the same on both in amp inputs) and are

not applied differentially. This second low pass network, R1+R2

and C3, has a –3 dB frequency equal to: 1/(2 π (R1+R2) (C3)).

Using a C3 value of 0.047 µF as shown, the –3 dB signal BW of

this circuit is approximately 400 Hz. The typical dc offset shift

over frequency will be less than 1.5 µV and the circuit’s RF

signal rejection will be better than 71 dB. The 3 dB signal bandwidth of this circuit may be increased to 900 Hz by reducing

resistors R1 and R2 to 2.2 kΩ. The performance is similar to

that using 4 kΩ resistors, except that the circuitry preceding the

in amp must drive a lower impedance load.

The circuit of Figure 43 should be built using a PC board with a

ground plane on both sides. All component leads should be as

short as possible. Resistors R1 and R2 can be common 1% metal

film units but capacitors C1 and C2 need to be ±5% tolerance

devices to avoid degrading the circuit’s common-mode rejection.

Either the traditional 5% silver mica units or Panasonic ±2%

PPS film capacitors are recommended.

+V

S

AD623

–V

S

0.01mF0.33mF

REFERENCE

0.01mF

V

OUT

R1

4.02kV

–IN

+IN

1%

R2

4.02kV

1%

LOCATE C1–C3 AS CLOSE

TO THE INPUT PINS AS POSSIBLE

C1

1000pF

5%

C3

0.047mF

C2

1000pF

5%

R

G

0.33mF

Figure 43. Circuit to Attenuate RF Interference

In many applications shielded cables are used to minimize noise;

for best CMR over frequency the shield should be properly

driven. Figure 44 shows an active guard drive that is configured

to improve ac common-mode rejection by “bootstrapping” the

capacitances of input cable shields, thus minimizing the capacitance mismatch between the inputs.

Figure 44. Common-Mode Shield Driver

GROUNDING

Since the AD623 output voltage is developed with respect to the

potential on the reference terminal, many grounding problems

can be solved by simply by tying the REF pin to the appropriate “local ground.” The REF pin should, however, be tied to a

low impedance point for optimal CMR.

The use of ground planes is recommended to minimize the

impedance of ground returns (and hence the size of dc errors).

In order to isolate low level analog signals from a noisy digital

environment, many data-acquisition components have separate

analog and digital ground returns (Figure 45). All ground pins

from mixed signal components such as analog-to-digital converters

should be returned through the “high quality” analog ground

DIGITAL POWER SUPPLY

+5V

GND

0.1mF

AGND V

12

mPROCESSOR

DD

0.1mF

AD623

ANALOG POWER SUPPLY

+5V –5V

0.1mF

GND

0.1mF

VDDAGND DGND

V

IN1

ADC

V

IN2

AD7892-2

Figure 45. Optimal Grounding Practice for a Bipolar Supply Environment with Separate Analog and Digital Supplies

POWER SUPPLY

+5V

0.1mF

V

AD623

V

IN

GND

0.1mF

0.1mF

DGND

AGND

DD

ADC

AD7892-2

V

12

DGND

DD

mPROCESSOR

Figure 46. Optimal Ground Practice in a Single Supply Environment

–13–REV. C

Page 14

AD623

plane. Maximum isolation between analog and digital is achieved

by connecting the ground planes back at the supplies. The digital return currents from the ADC, which flow in the analog ground

plane will, in general, have a negligible effect on noise performance.

If there is only a single power supply available, it must be shared

by both digital and analog circuitry. Figure 46 shows how to

minimize interference between the digital and analog circuitry.

As in the previous case, separate analog and digital ground

planes should be used (reasonably thick traces can be used as an

alternative to a digital ground plane). These ground planes

should be connected at the power supply’s ground pin. Separate

traces should be run from the power supply to the supply pins of

the digital and analog circuits. Ideally, each device should have

its own power supply trace, but these can be shared by a number of devices as long as a single trace is not used to route current to both digital and analog circuitry.

Ground Returns for Input Bias Currents

Input bias currents are those dc currents that must flow in order

to bias the input transistors of an amplifier. These are usually

transistor base currents. When amplifying “floating” input sources

such as transformers or ac-coupled sources, there must be a

direct dc path into each input in order that the bias current can

flow. Figure 47 shows how a bias current path can be provided

for the cases of transformer coupling, capacitive ac-coupling and

for a thermocouple application. In dc-coupled resistive bridge

+V

AD623

–V

S

S

REFERENCE

LOAD

V

OUT

TO POWER

SUPPLY

GROUND

–INPUT

+INPUT

R

G

Figure 47a. Ground Returns for Bias Currents with

Transformer Coupled Inputs

+V

AD623

–V

S

S

REFERENCE

LOAD

V

OUT

TO POWER

SUPPLY

GROUND

–INPUT

+INPUT

R

G

Figure 47b. Ground Returns for Bias Currents with

Thermocouple Inputs

+V

AD623

–V

S

S

REFERENCE

LOAD

V

OUT

TO POWER

SUPPLY

GROUND

–INPUT

+INPUT

100kV 100kV

R

G

Figure 47c. Ground Returns for Bias Currents with AC

Coupled Inputs

applications, providing this path is generally not necessary as the

bias current simply flows from the bridge supply through the

bridge and into the amplifier. However, if the impedances that

the two inputs see are large and differ by a large amount (>10 kΩ),

the offset current of the input stage will cause dc errors proportional with the input offset voltage of the amplifier.

Output Buffering

The AD623 is designed to drive loads of 10 kΩ or greater. If the

load is less that this value, the AD623’s output should be buffered with a precision single supply op amp such as the OP113.

This op amp can swing from 0 V to 4 V on its output while

driving a load as small as 600 Ω. Table III summarizes the per-

formance of some other buffer op amps.

+5V

0.1mF

R

V

IN

AD623

G

REF

+5V

OP113

0.1mF

V

OUT

Figure 48. Output Buffering

Table III. Buffering Options

Op Amp Comments

OP113 Single Supply, High Output Current

OP191 Rail-to-Rail Input and Output, Low Supply Current

OP150 Rail-to-Rail Input and Output, High Output Current

A Single Supply Data Acquisition System

Interfacing bipolar signals to single supply analog to digital

converters (ADCs) presents a challenge. The bipolar signal

must be “mapped” into the input range of the ADC. Figure 49

shows how this translation can be achieved.

+5V

610mV

R

1.02kV

+5V

0.1mF

G

AD623

REF

+5V

AD7776

A

IN

REF

OUT

REF

IN

0.1mF

Figure 49. A Single Supply Data Acquisition System

The bridge circuit is excited by a +5 V supply. The full-scale

output voltage from the bridge (± 10 mV) therefore has a

common-mode level of 2.5 V. The AD623 removes the commonmode component and amplifies the input signal by a factor of

100 (R

= 1.02 kΩ). This results in an output signal of ±1V.

GAIN

In order to prevent this signal from running into the AD623’s

ground rail, the voltage on the REF pin has to be raised to at

least 1 V. In this example, the 2 V reference voltage from the

AD7776 ADC is used to bias the AD623’s output voltage to 2 V

±1 V. This corresponds to the input range of the ADC.

–14–

REV. C

Page 15

AD623

Amplifying Signals with Low Common-Mode Voltage

Because the common-mode input range of the AD623 extends

0.1 V below ground, it is possible to measure small differential

signals which have low, or no, common mode component. Figure 50 shows a thermocouple application where one side of the

J-type thermocouple is grounded.

+5V

0.1mF

J-TYPE

THERMOCOUPLE

R

1.02kV

G

AD623

REF

V

OUT

2V

Figure 50. Amplifying Bipolar Signals with Low CommonMode Voltage

Over a temperature range from –200°C to +200°C, the J-type

thermocouple delivers a voltage ranging from –7.890 mV to

10.777 mV. A programmed gain on the AD623 of 100 (R

=

G

1.02 kΩ) and a voltage on the AD623 REF pin of 2 V, results in

the AD623’s output voltage ranging from 1.110 V to 3.077 V

relative to ground.

INPUT DIFFERENTIAL AND COMMON-MODE RANGE VS. SUPPLY AND GAIN

Figure 51 shows a simplified block diagram of the AD623. The

voltages at the outputs of the amplifiers A1 and A2 are given by

the equations

V

= VCM + V

A2

= VCM + 0.6 V + V

= VCM – V

V

A1

= VCM + 0.6 V – V

POS SUPPLY

INVERTING

2

V

DIFF

2

V

CM

V

DIFF

2

3

NONINVERTING

NEG SUPPLY

/2 + 0.6 V + V

DIFF

/2 + 0.6 V – V

DIFF

7

4

R

GAIN

7

4

1

G

8

DIFF

× Gain/2

DIFF

DIFF

× Gain/2

DIFF

A1

R

F

50kV

R

F

50kV

A2

× RF/R

× RF/R

50kV

50kV

G

G

50kV

V

A3

50kV

OUT

REF

6

5

Figure 51. Simplified Block Diagram

The voltages on these internal nodes are critical in determining

whether or not the output voltage will be clipped. The voltages

V

and VA2 can swing from about 10 mV above the negative

A1

supply (V– or Ground) to within about 100 mV of the positive

rail before clipping occurs. Based on this and from the above

equations, the maximum and minimum input common-mode

voltages are given by the equations

V

V

= V+ – 0.7 V – V

CMMAX

= V– – 0.590 V + V

CMMIN

× Gain/2

DIFF

DIFF

× Gain/2

These equations can be rearranged to give the maximum possible

differential voltage (positive or negative) for a particular commonmode voltage, gain, and power supply. Because the signals on A1

and A2, can clip on either rail, the maximum differential voltage

will be the lesser of the two equations.

|V

DIFFMAX

|V

DIFFMAX

| = 2 (V+ – 0.7 V – VCM)/Gain

| = 2 (VCM – V– +0.590 V)/Gain

However, the range on the differential input voltage range is also

constrained by the output swing. So the range of V

may have

DIFF

to be lower according the equation.

Input Range ≤ Available Output Swing/Gain

For a bipolar input voltage with a common-mode voltage that is

roughly half way between the rails, V

DIFFMAX

will be half the

value that the above equations yield because the REF pin will be

at midsupply. Note that the available output swing is given for

different supply conditions in the Specifications section.

The equations can be rearranged to give the maximum gain for a

fixed set of input conditions. Again, the maximum gain will be

the lesser of the two equations.

Gain

Gain

= 2 (V+ – 0.7 V – VCM)/V

MAX

= 2 (VCM – V– +0.590 V)/V

MAX

DIFF

DIFF

Again, we must ensure that the resulting gain times the input

range is less than the available output swing. If this is not the

case, the maximum gain is given by,

Gain

Also for bipolar inputs (i.e., input range = 2 V

= Available Output Swing/Input Range

MAX

DIFF

), the maximum gain will be half the value yielded by the above equations

because the REF pin must be at midsupply.

The maximum gain and resulting output swing for different

input conditions is given in Table IV. Output voltages are referenced to the voltage on the REF pin.

For the purposes of computation, it is necessary to break down

the input voltage into its differential and common-mode component. So when one of the inputs is grounded or at a fixed voltage,

the common-mode voltage changes as the differential voltage

changes. Take the case of the thermocouple amplifier in Figure

50. The inverting input on the AD623 is grounded. So when the

input voltage is –10 mV, the voltage on the noninverting input is

–10 mV. For the purposes of signal swing calculations, this input

voltage should be considered to be composed of a common-mode

voltage of –5 mV (i.e., (+IN + –IN)/2) and a differential input

voltage of –10 mV (i.e., +IN – –IN).

–15–REV. C

Page 16

AD623

Table IV. Maximum Attainable Gain and Resulting Output Swing for Different Input Conditions

Supply Max Closest 1% Resulting Output

V

CM

0 V ±10 mV 2.5 V +5 V 118 866 116 ±1.2 V

0 V ±100 mV 2.5 V +5 V 11.8 9.31 k 11.7 ±1.1 V

0 V ±10 mV 0 V ±5 V 490 205 488 ±4.8 V

0 V ±100 mV 0 V ±5 V 49 2.1 k 48.61 ±4.8 V

0 V ±1 V 0 V ±5 V 4.9 26.1 k 4.83 ±4.8 V

2.5 V ±10 mV 2.5 V +5 V 242 422 238 ±2.3 V

2.5 V ±100 mV 2.5 V +5 V 24.2 4.32 k 24.1 ±2.4 V

2.5 V ±1 V 2.5 V +5 V 2.42 71.5 k 2.4 ±2.4 V

1.5 V ±10 mV 1.5 V +3 V 142 715 141 ±1.4 V

1.5 V ±100 mV 1.5 V +3 V 14.2 7.68 k 14 ±1.4 V

0 V ±10 mV 1.5 V +3 V 118 866 116 ±1.1 V

0 V ±100 mV 1.5 V +3 V 11.8 9.31 k 11.74 ±1.1 V

V

DIFF

8-Lead Plastic DIP

REF Pin Voltages Gain Gain Resistor, V Gain Swing

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

(N-8)

8-Lead mSOIC

(RM-8)

C3202c–0–9/99

0.210 (5.33)

MAX

0.160 (4.06)

0.115 (2.93)

0.022 (0.558)

0.014 (0.356)

0.1574 (4.00)

0.1497 (3.80)

0.0098 (0.25)

0.0040 (0.10)

SEATING

PLANE

0.430 (10.92)

0.348 (8.84)

8

14

PIN 1

0.100

0.070 (1.77)

(2.54)

0.045 (1.15)

BSC

0.1968 (5.00)

0.1890 (4.80)

8

5

41

PIN 1

0.0500

(1.27)

BSC

0.0688 (1.75)

0.0532 (1.35)

0.0192 (0.49)

0.0138 (0.35)

5

0.280 (7.11)

0.240 (6.10)

0.060 (1.52)

0.015 (0.38)

0.130

(3.30)

MIN

SEATING

PLANE

8-Lead SOIC

(SO-8)

0.2440 (6.20)

0.2284 (5.80)

0.0098 (0.25)

0.0075 (0.19)

0.325 (8.25)

0.300 (7.62)

0.015 (0.381)

0.008 (0.204)

0.0196 (0.50)

0.0099 (0.25)

88

08

0.0500 (1.27)

0.0160 (0.41)

0.195 (4.95)

0.115 (2.93)

3 458

0.122 (3.10)

0.114 (2.90)

0.006 (0.15)

0.002 (0.05)

SEATING

0.122 (3.10)

0.114 (2.90)

8

1

PIN 1

0.0256 (0.65) BSC

0.120 (3.05)

0.112 (2.84)

0.018 (0.46)

0.008 (0.20)

PLANE

5

4

0.199 (5.05)

0.187 (4.75)

0.043 (1.09)

0.037 (0.94)

0.011 (0.28)

0.003 (0.08)

0.120 (3.05)

0.112 (2.84)

33°

27°

0.028 (0.71)

0.016 (0.41)

PRINTED IN U.S.A.

–16–

REV. C

Loading...

Loading...