Datasheet AD606JR-REEL, AD606JR, AD606JN, AD606JCHIPS, AD606JR-REEL7 Datasheet (Analog Devices)

Page 1

50 MHz, 80 dB Demodulating

a

Logarithmic Amplifier with Limiter Output

FEATURES

Logarithmic Amplifier Performance

–75 dBm to +5 dBm Dynamic Range

≤1.5 nV/√Hz Input Noise

Usable to >50 MHz

37.5 mV/dB Voltage Output

On-Chip Low-Pass Output Filter

Limiter Performance

ⴞ1 dB Output Flatness over 80 dB Range

ⴞ3ⴗ Phase Stability at 10.7 MHz over 80 dB Range

Adjustable Output Amplitude

Low Power

+5 V Single Supply Operation

65 mW Typical Power Consumption

CMOS-Compatible Power-Down to 325 W typ

<5 s Enable/Disable Time

APPLICATIONS

Ultrasound and Sonar Processing

Phase-Stable Limiting Amplifier to 100 MHz

Received Signal Strength Indicator (RSSI)

Wide Range Signal and Power Measurement

PRODUCT DESCRIPTION

The AD606 is a complete, monolithic logarithmic amplifier

using a 9-stage “successive-detection” technique. It provides

both logarithmic and limited outputs. The logarithmic output is

from a three-pole post-demodulation low-pass filter and provides

AD606

a loadable output voltage of +0.1 V dc to +4 V dc. The logarithmic scaling is such that the output is +0.5 V for a sinusoidal

input of –75 dBm and +3.5 V at an input of +5 dBm; over this

range the logarithmic linearity is typically within ±0.4 dB. All

scaling parameters are proportional to the supply voltage.

The AD606 can operate above and below these limits, with

reduced linearity, to provide as much as 90 dB of conversion

range. A second low-pass filter automatically nulls the input

offset of the first stage down to the submicrovolt level. Adding

external capacitors to both filters allows operation at input frequencies as low as a few hertz.

The AD606’s limiter output provides a hard-limited signal

output as a differential current of ±1.2 mA from open-collector

outputs. In a typical application, both of these outputs are

loaded by 200 Ω resistors to provide a voltage gain of more than

90 dB from the input. Transition times are 1.5 ns, and the

phase is stable to within ±3° at 10.7 MHz for signals from

–75 dBm to +5 dBm.

The logarithmic amplifier operates from a single +5 V supply

and typically consumes 65 mW. It is enabled by a CMOS logic

level voltage input, with a response time of <5 µs. When dis-

abled, the standby power is reduced to <1 mW within 5 µs.

The AD606J is specified for the commercial temperature range

of 0°C to +70°C and is available in 16-lead plastic DIPs or

SOICs. Consult the factory for other packages and temperature

ranges.

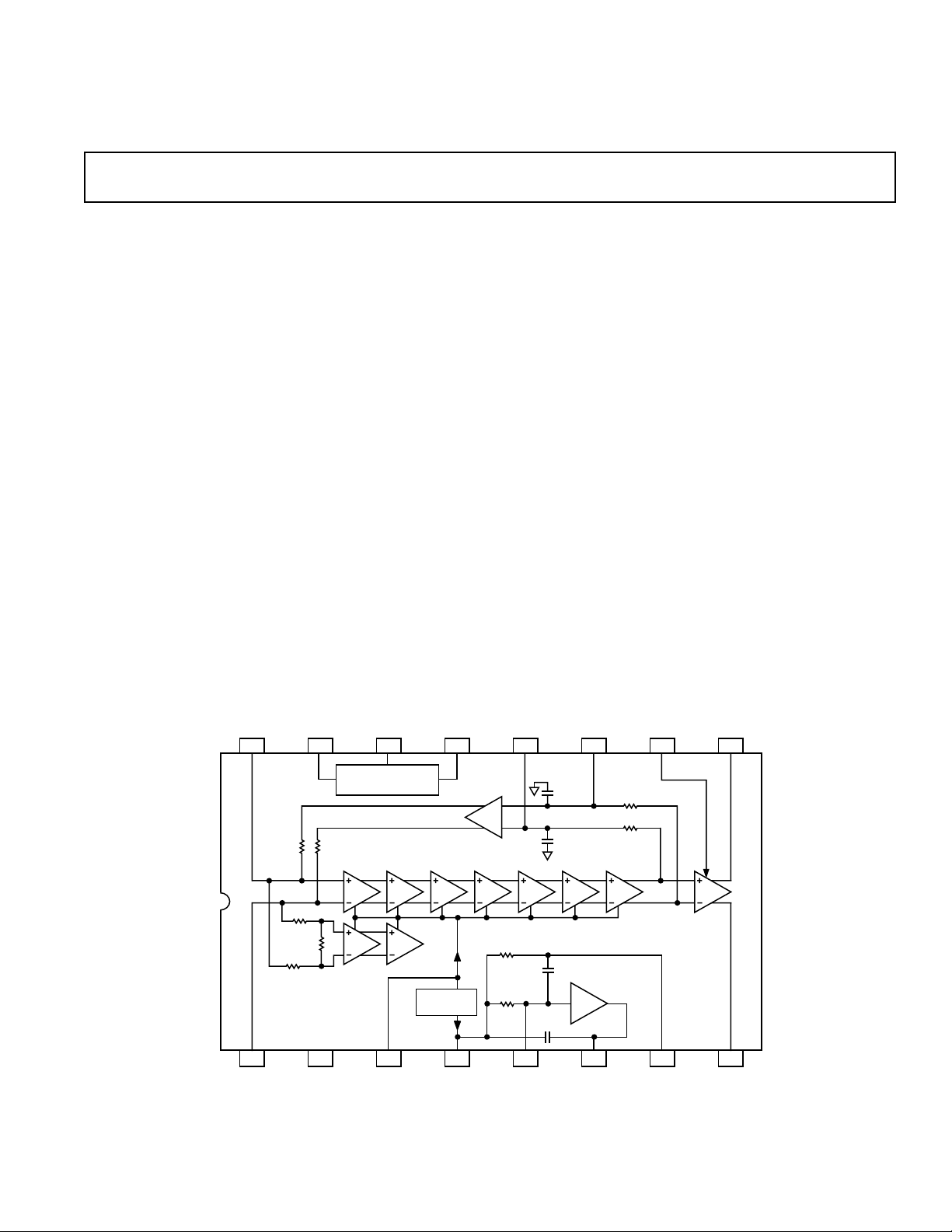

FUNCTIONAL BLOCK DIAGRAM

REFERENCE

AND POWER-UP

30kV 30kV

1.5kV

250V

1.5kV

HIGH-END

DETECTORS

AD606

12345678

INLO COMM ISUM ILOG BFIN VLOG OPCM LMLO

12mA/dB

ONE-POLE

FILTER

2mA/dB

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

LMHILADJFIL2FIL1VPOSPRUPCOMMINHI

910111213141516

30pF

X1

30pF

MAIN SIGNAL PATH

9.375kV

9.375kV

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

OFFSET-NULL

LOW-PASS FILTER

11.15dB/STAGE

2pF

2pF

360kV

360kV

TWO-POLE

SALLEN-KEY

FILTER

X2

FINAL

LIMITER

Page 2

AD606–SPECIFICATIONS

(@ TA = +25ⴗC and supply = +5 V unless otherwise noted; dBm assumes 50 ⍀)

Model AD606J

Parameter Conditions Min Typ Max Units

SIGNAL INPUT

Log Amp f

Limiter f

MAX

MAX

AC Coupled; Sinusoidal Input 50 MHz

AC Coupled; Sinusoidal Input 100 MHz

Dynamic Range 80 dB

Input Resistance Differential Input 500 2,500 Ω

Input Capacitance Differential Input 2 pF

SIGNAL OUTPUT

Limiter Flatness –75 dBm to +5 dBm Input Signal at 10.7 MHz –1.5 +1.5 dB

With Pin 9 to V

and Pin 8 to V

Output Current At Pins 8 or 9, Proportional to V

via a 200 Ω Resistor

POS

via a 200 Ω Resistor

POS

, LADJ Grounded 1.2 mA

POS

LADJ Open Circuited 0.48 mA

Phase Variation with Input Level –75 dBm to +5 dBm Input Signal at 10.7 MHz ±3 Degrees

LOG (RSSI) OUTPUT

Nominal Slope At 10.7 MHz; (0.0075 × V

)/dB 37.5 mV/dB

POS

At 45 MHz 35 mV/dB

Slope Accuracy Untrimmed at 10.7 MHz –15 ±5 +15 %

Intercept Sinusoidal Input; Independent of V

POS

–88.33 dBm

Logarithmic Conformance –75 dBm to +5 dBm Input Signal at 10.7 MHz –1.5 0.4 +1.5 dB

Nominal Output Input Level = –75 dBm 0.5 V

Input Level = –35 dBm 2 V

Input Level = +5 dBm 3.5 V

Accuracy over Temperature After Calibration at –35 dBm at 10.7 MHz –3 +3 dB

to T

T

MIN

MAX

Video Response Time From Onset of Input Signal Until Output Reaches 400 ns

95% of Final Value

POWER-DOWN INTERFACE

Power-Up Response Time Time Delay Following HI Transition Until 3.5 µs

Device Meets Full Specifications

AC Coupled with 100 pF Coupling Capacitors

Input Bias Current Logical HI Input (See Figure 12) 1 nA

Logical LO Input 4 µA

POWER SUPPLY

Operating Range 4.5 5.5 V

Powered-Up Current Zero Signal Input 13 mA

T

Powered-Down Current T

Specifications subject to change without notice.

MIN

MIN

to T

to T

MAX

MAX

13 20 mA

65 200 µA

–2–

REV. B

Page 3

AD606

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

Supply Voltage V

Internal Power Dissipation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . +9 V

POS

2

. . . . . . . . . . . . . . . . . . . 600 mW

1

Operating Temperature Range . . . . . . . . . . . . . 0°C to +70°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering 60 sec) . . . . . . . . +300°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Specification is for device in free air:

16-Lead Plastic DIP Package: θJA = 85°C/W

16-Lead SOIC Package: θJA = 100°C/W

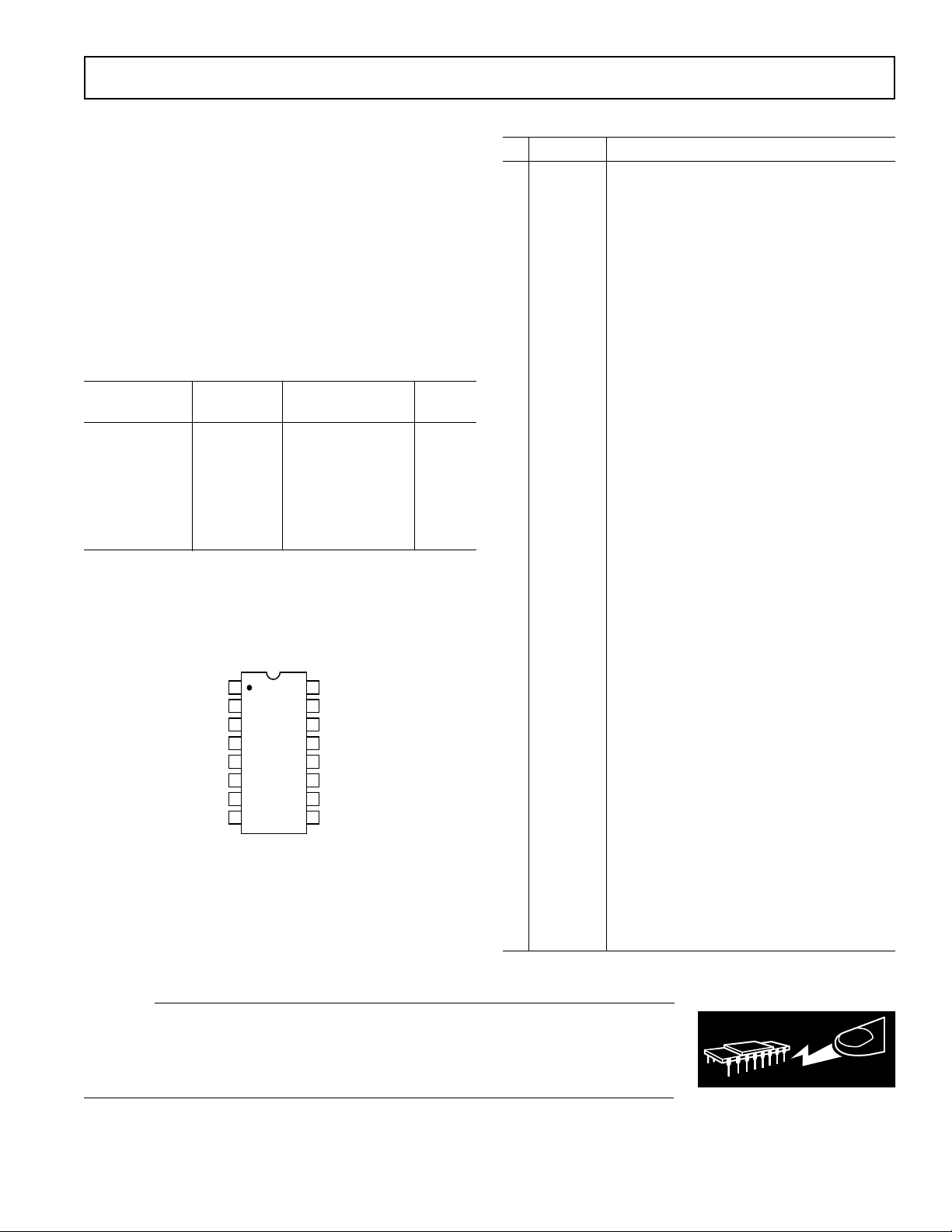

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

AD606JN 0°C to +70°C 16-Lead Plastic DIP N-16

AD606JR 0°C to +70°C 16-Lead Narrow-Body R-16A

SOIC

AD606JR-REEL 0°C to +70°C 13" Tape and Reel R-16A

AD606JR-REEL7 0°C to +70°C 7" Tape and Reel R-16A

AD606-EB Evaluation Board

AD606JCHIPS 0°C to +70°C Die

PIN DESCRIPTION

Plastic DIP (N)

and

Small Outline (R)

Packages

1

INLO INHI

COMM COMM

2

ISUM PRUP

3

ILOG VPOS

4

AD606

BFIN FIL1

VLOG FIL2

OPCM LADJ

LMLO LMHI

TOP VIEW

5

(Not to Scale)

6

7

8

16

15

14

13

12

11

10

9

PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Function

1 INLO DIFFERENTIAL RF INPUT

–75 dBm to +5 dBm, Inverting, AC Coupled.

2 COMM POWER SUPPLY COMMON

Connect to Ground.

3 ISUM LOG DETECTOR SUMMING NODE

4 ILOG LOG CURRENT OUTPUT

Normally No Connection; 2 µA/dB Output

Current.

5 BFIN BUFFER INPUT

Optionally Used to Realize Low Frequency

Post-Demodulation Filters.

6 VLOG BUFFERED LOG OUTPUT

37.5 mV/dB (100 mV to 4.5 V).

7 OPCM OUTPUT COMMON

Connect to Ground.

8 LMLO DIFFERENTIAL LIMITER OUTPUT

1.2 mA Full-Scale Output Current. Open

Collector Output Must Be “Pulled” Up to

VPOS with R ≤ 400 Ω.

9 LMHI DIFFERENTIAL LIMITER OUTPUT

1.2 mA Full-Scale Output Current. Open

Collector Output Must Be “Pulled” Up to

VPOS with R ≤ 400 Ω.

10 LADJ LIMITER LEVEL ADJUSTMENT

Optionally Used to Adjust Limiter Output

Current.

11 FIL1 OFFSET LOOP LOW-PASS FILTER

Normally No Connection; a Capacitor Between

FIL1 and FIL2 May Be Added to Lower the

Filter Cutoff Frequency.

12 FIL2 OFFSET LOOP LOW-PASS FILTER

Normally No Connection; See Above.

13 VPOS POSITIVE SUPPLY

Connect to +5 V at 13 mA.

14 PRUP POWER UP

CMOS (5 V) Logical High = Device On

(≈ 65 mW).

CMOS (0 V) Logical Low = Device Off

(≈ 325 µW).

15 COMM POWER SUPPLY COMMON

Connect to Ground.

16 INHI DIFFERENTIAL RF INPUT

–75 dBm to +5 dBm, Noninverting, AC-Coupled.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD606 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. B

–3–

Page 4

AD606

INPUT LEVEL CONVENTIONS

RF logarithmic amplifiers usually have their input specified in

“dBm,” meaning “decibels with respect to 1 mW.” Unfortunately, this is not precise for several reasons.

1. Log amps respond not to power but to voltage. In this respect, it would be less ambiguous to use “dBV” (decibels

referred to 1 V) as the input metric. Also, power is dependent

on the rms (root mean-square) value of the signal, while log

amps are not inherently rms responding.

2. The response of a demodulating log amp depends on the

waveform. Convention assumes that the input is sinusoidal.

However, the AD606 is capable of accurately handling any

input waveform, including ac voltages, pulses and square

waves, Gaussian noise, and so on. See the AD640 data sheet,

which covers the effect of waveform on logarithmic intercept,

for more information.

3. The impedance in which the specified power is measured is

not always stated. In the log amp context it is invariably

assumed to be 50 Ω. Thus, 0 dBm means “1 mW rms in 50 Ω,”

and corresponds to an rms voltage of

224 mV.

(1 mW × 50 Ω),

or

Popular convention requires the use of dBm to simplify the

comparison of log amp specifications. Unless otherwise stated,

sinusoidal inputs expressed as dBm in 50 Ω are used to specify

the performance of the AD606 throughout this data sheet. We

will also show the corresponding rms voltages where it helps to

clarify the specification. Noise levels will likewise be given in

dBm; the response to Gaussian noise is 0.5 dB higher than for a

sinusoidal input of the same rms value.

Note that dynamic range, being a simple ratio, is always specified simply as “dB”, and the slope of the logarithmic transfer

function is correctly specified as “mV/dB,” NOT as “mV/dBm.”

LOGARITHMIC SLOPE AND INTERCEPT

A generalized logarithmic amplifier having an input voltage V

and output voltage V

must satisfy a transfer function of the

LOG

IN

form

VV VV

= log ( / )

LOG Y IN X

10

where, in the case of the AD606, the voltage VIN is the difference between the voltages on pins INHI and INLO, and the

voltage V

V

are fixed voltages that determine the slope and intercept of

X

is that measured at the output pin VLOG. VY and

LOG

the logarithmic amplifier, respectively. These parameters are

inherent in the design of a particular logarithmic amplifier,

although may be adjustable, as in the AD606. When V

the logarithmic argument is one, hence the logarithm is zero. V

= VX,

IN

X

is, therefore, called the logarithmic intercept voltage because the

output voltage V

age V

is can also be interpreted as the “volts per decade” when

Y

crosses zero for this input. The slope volt-

LOG

using base-10 logarithms as shown here.

Note carefully that V

and VLOG in the above paragraph

LOG

(and elsewhere in this data sheet) are different. The first is a

voltage; the second is a pin designation.

This equation suggests that the input V

is positive, that VIN must likewise be positive, since the

if V

X

is a dc quantity, and,

IN

logarithm of a negative number has no simple meaning. In fact,

in the AD606, the response is independent of the sign of V

IN

because of the particular way in which the circuit is built. This

is part of the demodulating nature of the amplifier, which

–4–

results in an alternating input voltage being transformed into a

quasi-dc (rectified and filtered) output voltage.

The single supply nature of the AD606 results in common-mode

level of the inputs INHI and INLO being at about +2.5 V (using the recommended +5 V supply). In normal ac operation,

this bias level is developed internally and the input signal is

coupled in through dc blocking capacitors. Any residual dc

offset voltage in the first stage limits the logarithmic accuracy for

small inputs. In ac operation, this offset is automatically and

continuously nulled via a feedback path from the last stage, provided that the pins INHI and INLO are not shorted together, as

would be the case if transformer coupling were used for the signal.

While any logarithmic amplifier must eventually conform to the

basic equation shown above, which, with appropriate elaboration, can also fully account for the effect of the signal waveform

on the effective intercept,

1

it is more convenient in RF applications to use a simpler expression. This simplification results

from first, assuming that the input is always sinusoidal, and

second, using a decibel representation for the input level. The

standard representation of RF levels is (incorrectly, in a log amp

context) in terms of power, specifically, decibels above 1 milli-

watt (dBm) with a presumed impedance level of 50 Ω. That

being the case, we can rewrite the transfer function as

= ( –)

VVPP

LOG Y IN X

where it must be understood that PIN means the sinusoidal input

power level in a 50 Ω system, expressed in dBm, and P

intercept, also expressed in dBm. In this case, P

simple, dimensionless numbers. (P

is sometimes called the

X

IN

is the

X

and PX are

“logarithmic offset,” for reasons which are obvious from the

above equation.) V

is still defined as the logarithmic slope,

Y

usually specified as so many millivolts per decibel, or mV/dB.

In the case of the AD606, the slope voltage, V

750 mV when operating at V

= 5 V. This can also be ex-

POS

, is nominally

Y

pressed as 37.5 mV/dB or 750 mV/decade; thus, the 80 dB

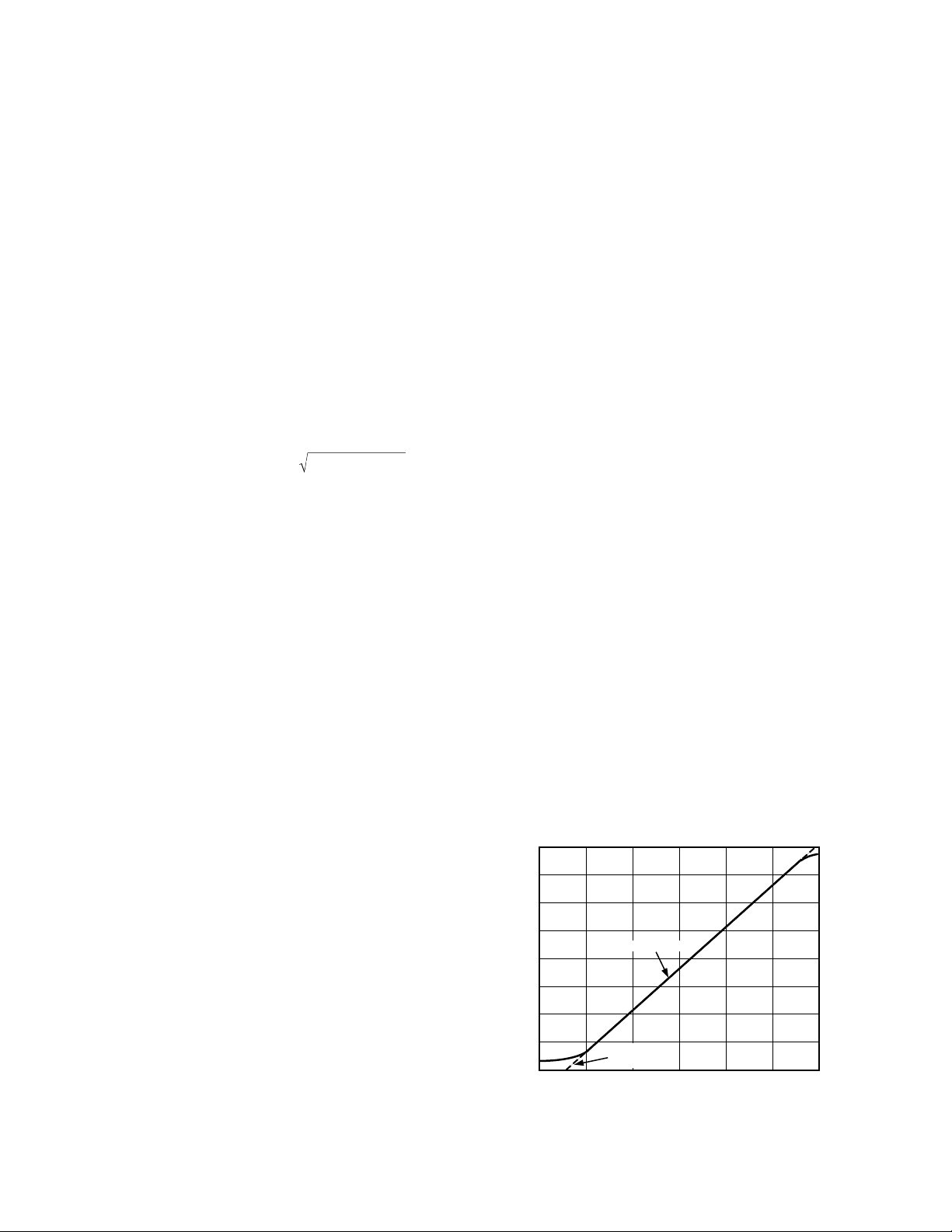

range equates to 3 V. Figure 1 shows the transfer function of the

AD606. The slope is closely proportional to V

generally be stated as V

= 0.15 × V

Y

Thus, in those applica-

POS.

, and can more

POS

tions where the scaling must be independent of supply voltage,

this must be stabilized to the required accuracy. In applications

where the output is applied to an A/D converter, the reference

4

3.5

3

2.5

2

1.5

VLOG – Volts DC

1

0.5

0

SLOPE = 37.5mV/dB

INTERCEPT

AT –88.33dBm

–80–100

INPUT SIGNAL – dBm

+20

0–20–40–60

Figure 1. Nominal Transfer Function

1

See, for example, the AD640 data sheet, which is published in Section 3 of

the Special Linear Reference Manual or Section 9.3 of the 1992 Amplifier

Applications Guide.

REV. B

Page 5

AD606

for that converter should be a fractional part of V

, if possible.

POS

The slope is essentially independent of temperature.

The intercept P

is essentially independent of either the supply

X

voltage or temperature. However, the AD606 is not factory

calibrated, and both the slope and intercept may need to be

externally adjusted. Following calibration, the conformance to

an ideal logarithmic law will be found to be very close, particularly at moderate frequencies (see Figure 14), and still acceptable at the upper end of the frequency range (Figure 15).

CIRCUIT DESCRIPTION

Figure 2 is a block diagram of the AD606, which is a complete

logarithmic amplifier system in monolithic form. It uses a total

of nine limiting amplifiers in a “successive detection” scheme to

closely approximate a logarithmic response over a total dynamic

range of 90 dB (Figure 2). The signal input is differential, at

nodes INHI and INLO, and will usually be sinusoidal and ac

coupled. The source may be either differential or single-sided;

the input impedance is about 2.5 kΩ in parallel with 2 pF. Seven

of the amplifier/detector stages handle inputs from –80 dBm

(32 µV rms) up to about –14 dBm (45 mV rms). The noise floor

is about –83 dBm (18 µV rms). Another two stages receive the

input attenuated by 22.3 dB, and respond to inputs up to

+10 dBm (707 mV rms). The gain of each of these stages is

11.15 dB and is accurately stabilized over temperature by a

precise biasing system.

The detectors provide full-wave rectification of the alternating

signal present at each limiter output. Their outputs are in the

form of currents, proportional to the supply voltage. Each cell

incorporates a low-pass filter pole, as the first step in recovering

the average value of the demodulated signal, which contains

appreciable energy at even harmonics of the input frequency. A

further real pole can be introduced by adding a capacitor between the summing node ISUM and VPOS. The summed detector output currents are applied to a 6:1 reduction current

mirror. Its output at ILOG is scaled 2 µA/dB, and is converted

to voltage by an internal load resistor of 9.375 kΩ between

ILOG and OPCM (output common, which is usually grounded).

The nominal slope at this point is 18.75 mV/dB (375 mV/

decade).

In applications where V

is taken to an A/D converter which

LOG

allows the use of an external reference, this reference input

should also be connected to the same +5 V supply. The power

supply voltage may be in the range +4.5 V to +5.5 V, providing

a range of slopes from nominally 33.75 mV/dB (675 mV/ decade) to 41.25 mV/dB (825 mV/decade).

A buffer amplifier, having a gain of two, provides a final output

scaling at V

of 37.5 mV/dB (750 mV/decade). This low-

LOG

impedance output can run from close to ground to over +4 V

(using the recommended +5 V supply) and is tolerant of resistive and capacitive loads. Further filtering is provided by a conjugate pole pair, formed by internal capacitors which are an

integral part of the output buffer. The corner frequency of the

overall filter is 2 MHz, and the 10%–90% rise time is 150 ns.

Later, we will show how the slope and intercept can be altered

using simple external adjustments. The direct buffer input

BFIN is used in these cases.

The last limiter output is available as complementary currents

from open collectors at pins LMHI and LMLO. These currents

are each 1.2 mA typical with LADJ grounded and may be converted to voltages using external load resistors connected to

VPOS; typically, a 200 Ω resistor is used on just one output.

The voltage gain is then over 90 dB, resulting in a hard-limited

output for all input levels down to the noise floor. The phasing

is such that the voltage at LMHI goes high when the input

(INHI to INLO) is positive. The overall delay time from the

signal inputs to the limiter outputs is 8 ns. Of particular importance is the phase stability of these outputs versus input level. At

50 MHz, the phase typically remains within ±4° from –70 dBm

to +5 dBm. The rise time of this output (essentially a square

wave) is about 1.2 ns, resulting in clean operation to more than

70 MHz.

REV. B

LMHILADJFIL2FIL1VPOSPRUPCOMMINHI

910111213141516

REFERENCE

AND POWER-UP

X1

30kV 30kV

1.5kV

250V

1.5kV

HIGH-END

DETECTORS

AD606

12345678

INLO COMM ISUM ILOG BFIN VLOG OPCM LMLO

12mA/dB

ONE-POLE

FILTER

2mA/dB

9.375kV

9.375kV

30pF

30pF

MAIN SIGNAL PATH

OFFSET-NULL

LOW-PASS FILTER

11.15dB/STAGE

2pF

SALLEN-KEY

X2

2pF

TWO-POLE

FILTER

360kV

360kV

FINAL

LIMITER

Figure 2. Simplified Block Diagram

–5–

Page 6

AD606

Offset-Control Loop

The offset-control loop nulls the input offset voltage, and sets

up the bias voltages at the input pins INHI and INLO. A full

understanding of this offset-control loop is useful, particularly

when using larger input coupling capacitors and an external

filter capacitor to lower the minimum acceptable operating

frequency. The loop’s primary purpose is to extend the lower

end of the dynamic range in the case where the offset voltage of

the first stage should be high enough to cause later stages to

prematurely enter limiting, because of the high dc gain (about

8000) of the main amplifier system. For example, an offset

voltage of only 20 µV would become 160 mV at the output of

the last stage in the main amplifier (before the final limiter section), driving the last stage well into limiting. In the absence of

noise, this limiting would simply result in the logarithmic output

ceasing to become any lower below a certain signal level at the

input. The offset would also degrade the logarithmic conformance in this region. In practice, the finite noise of the first stage

also plays a role in this regard, even if the dc offset were zero.

Figure 3 shows a representation of this loop, reduced to essentials. The figure closely corresponds to the internal circuitry,

and correctly shows the input resistance. Thus, the forward gain

of the main amplifier section is 7 × 11.15 dB, but the loop gain

is lowered because of the attenuation in the network formed by

RB1 and RB2 and the input resistance RA. The connection

polarity is such as to result in negative feedback, which reduces

the input offset voltage by the dc loop gain, here about 50 dB,

that is, by a factor of about 316. We use a differential representation, because later we will examine the consequences to the

power-up response time in the event that the ac coupling capacitors C

and CC2 do not exactly match. Note that these capaci-

C1

tors, as well as forming a high-pass filter to the signal in the

forward path, also introduce a pole in the feedback path.

+1

CF2

RB1

30kV

C

C1

RA

78dB

2.5kV

C

C2

RB2

30kV

+1

30pF

CF1

30pF

0V

RF2

360kV

RF1

360kV

FIL2

TO FINAL

LIMITER

STAGE

FIL1

C

Z

R

Z

Figure 3. Offset Control Loop

Internal resistors RF1 and RF2 in conjunction with grounded

capacitors CF1 and CF2 form a low-pass filter at 15 kHz. This

frequency can optionally be lowered by the addition of an external capacitor C

, and in some cases a series resistor RZ. This, in

Z

conjunction with the low-pass section formed at the input coupling, results in a two-pole high-pass response, falling of at

40 dB/decade below the corner frequency. The damping factor

of this filter depends on the ratio C

also on the value of R

.

Z

(when CZ>>CF) and

Z/CC

The inclusion of this control loop has no effect on the high frequency

response of the AD606. Nor does it have any effect on the low frequency response when the input amplitude is substantially above the

input offset voltage.

The loop’s effect is felt only at the lower end of the dynamic

range, that is, from about 80 dBm to –70 dBm, and when the

signal frequency is near the lower edge of the passband. Thus,

the small signal results which are obtained using the suggested

model are not indicative of the ac response at moderate to high

signal levels. Figure 4 shows the response of this model for the

default case (using C

150 pF. In general, a maximally flat ac response occurs when C

= 100 pF and CZ = 0) and with CZ =

C

Z

is roughly twice CC (making due allowance for the internal

30 pF capacitors). Thus, for audio applications, one can use

= 2.7 µF and CZ = 4.7 µF to achieve a high-pass corner

C

C

(–3 dB) at 25 Hz.

90

80

70

60

50

40

30

20

10

RELATIVE OUTPUT – dB

0

–10

–20

CZ = 150pF

100k 100M10M1M10k

INPUT FREQUENCY – Hz

CZ = 0pF

Figure 4. Frequency Response of Offset Control Loop for

= 0 pF and CZ = 150 pF (CC = 100 pF)

C

Z

However, the maximally flat ac response is not optimal in two

special cases. First, where the RF input level is rapidly pulsed,

the fast edges will cause the loop filter to ring. Second, ringing

can also occur when using the power-up feature, and the ac

coupling capacitors do not exactly match in value. We will examine the latter case in a moment. Ringing in a linear amplifier

is annoying, but in a log amp, with its much enhanced sensitivity to near zero signals, it can be very disruptive.

To optimize the low level accuracy, that is, achieve a highly

damped pulse response in this filter, it is recommended to include a resistor RZ in series with an increased value of CZ. Some

experimentation may be necessary, but for operation in the

range 3 MHz to 70 MHz, values of C

and R

= 2 kΩ are near optimal. For operation down to 100 kHz

Z

use C

= 10 nF, C

C

= 0.1 µF and RZ = 13 kΩ. Figure 5 shows

Z

= 100 pF, CZ = 1 nF

C

typical connections for the AD606 with these filter components

added.

R

FIL1

BFIN

Z

FIL2

VLOG

LADJ

OPCM

LMHI

LMLO

Z

INHI

INLO

COMM

COMM

C

PRUP

VPOS

AD606JN

ISUM

ILOG

Figure 5. Use of CZ and RZ for Offset Control Loop

Compensation

–6–

REV. B

Page 7

AD606

For operation above 10 MHz, it is not necessary to add the

external capacitors CF1, CF2, and C

, although an improve-

Z

ment in low frequency noise can be achieved by so doing (see

APPLICATIONS). Note that the offset control loop does not

materially affect the low-frequency cutoff at high input levels,

when the offset voltage is swamped by the signal.

Power-Up Interface

The AD606 features a power-saving mode, controlled by the

logic level at Pin 14 (PRUP). When powered down, the quies-

cent current is typically 65 µA, or about 325 µW. A CMOS

logical HIGH applied to PRUP activates both internal references, and the system becomes fully functional within about

3.5 µs. When this input is a CMOS logical LOW, the system

shuts down to the quiescent level within about 5 µs.

The power-up time is somewhat dependent on the signal level

and can be degraded by mismatch of the input coupling capacitors. The explanation is as follows. When the AD606 makes the

transition from powered-down to fully active, the dc bias voltage

at the input nodes INHI and INLO (about +2.5 V) inevitably

changes slightly, as base current in the input transistors flows in

the bias resistors. In fact, first-order correction for this is included in the specially designed offset buffer amplifier, but even

a few millivolts of change at these inputs represents a significant

equivalent “dBm” level.

Now, if the coupling capacitors do not match exactly, some

fractional part of this residual voltage step becomes coupled into

the amplifier. For example, if there is a 10% capacitor mismatch, and INHI and INLO jump 20 mV at power-up, there is

a 2 mV pulse input to the system, which may cause the offset

control loop to ring. Note that 2 mV is roughly 40 times greater

than the amplitude of a sinusoidal input at –75 dBm. As long as

the ringing persists, the AD606 will be “blind” to the actual

input, and V

will show major disturbances.

LOG

The solution to this problem is first, to ensure that the loop

filter does not ring, and second, to use well-matched capacitors

at the signal input. Use the component values suggested above

to minimize ringing.

APPLICATIONS

Note that the AD606 has more than 70 MHz of input bandwidth and 90 dB of gain! Careful shielding is needed to realize

its full dynamic range, since nearly all application sites will be

pervaded by many kinds of interference, radio and TV stations,

etc., all of which the AD606 faithfully hears. In bench evaluation, we recommend placing all of the components in a shielded

box and using feedthrough decoupling networks for the supply

voltage. In many applications, the AD606’s low power drain

allows the use of a 6 V battery inside the box.

Basic RSSI Application

Figure 6 shows the basic RSSI (Receiver Signal Strength Indicator) application circuit, including the calibration adjustments,

either or both of which may be omitted in noncritical applications. This circuit may be used “as is” in such measurement

applications as the log/IF strip in a spectrum or network analyzer or, with the addition of an FM or QPSK demodulator fed

by the limiter outputs, as an IF strip in such communications

applications as a GSM digital mobile radio or FM receiver.

The slope adjustment works in this way: the buffer amplifier

(which forms part of a Sallen-Key two-pole filter, see Figure 2)

has a dc gain of plus two, and the resistance from BFIN (buffer

in) to OPCM (output common) is nominally 9.375 kΩ. This

resistance is driven from the logarithmic detector sections with a

current scaled 2 µA/dB, generating 18.75 mV/dB at BFIN,

hence 37.5 mV/dB at V

Now, a resistor (R4 in Figure 6)

LOG

connected directly between BFIN and VLOG would form a

controlled positive-feedback network with the internal 9.375 kΩ

resistor which would raise the gain, and thus increase the slope

voltage, while the same external resistor connected between

BFIN and ground would form a shunt across the internal resistor and reduce the slope voltage. By connecting R4 to a potentiometer R2 across the output, the slope may be adjusted either

way; the value for R4 shown in Figure 6 provides approximately

±10% range, with essentially no effect on the slope at the

midposition.

The intercept may be adjusted by adding a small current into

BFIN via R1 and R3. The AD606 is designed to have the nominal intercept value of –88 dBm when R1 is centered using this

network, which provides a range of ±5 dB.

REV. B

+5V

NC

NC

FIL1

VPOS

AD606

ILOG

BFIN

R3

412kVR4174kV

FIL2

VLOG

LMHI

LADJ

OPCM

LMLO

R2

50kV

SLOPE

ADJUSTMENT

610%

R5

200V

LIMITER OUTPUT

LOGARITHMIC

OUTPUT

RF INPUT

NC = NO CONNECT

100pF

51.1V

100pF

0.1mF

INHI

COMM

INLO

COMM

200kV

INTERCEPT

ADJUSTMENT

65dB

PRUP

ISUM

+5V

R1

Figure 6. Basic Application Circuit Showing Optional Slope and Intercept Adjustments

–7–

Page 8

AD606

Adjustment Procedure

The slope and intercept adjustments interact; this can be minimized by reducing the resistance of R1 and R2, chosen here to

minimize power drain. Calibration can be achieved in several

ways: The simplest is to apply an RF input at the desired operating frequency which is amplitude modulated at a relatively

low frequency (say 1 kHz to 10 kHz) to a known modulation

index. Thus, one might choose a ratio of 2 between the maximum and minimum levels of the RF amplitude, corresponding

to a 6 dB (strictly, 6.02 dB) change in input level. The average

RF level should be set to about –35 dBm (the midpoint of the

AD606’s range). R2 is then adjusted so that the 6 dB input

change results in the desired output voltage change, for example, 226 mV at 37.5 mV/dB.

A better choice would be a 4:1 ratio (12.04 dB), to spread the

residual error out over a larger segment of the whole transfer

function. If a pulsed RF generator is available, the decibel increment might be enlarged to 20 dB or more. Using just a fixedlevel RF generator, the procedure is more time consuming, but

is carried out in just the same way: manually change the level by

a known number of decibels and adjust R2 until V

varies by

LOG

the corresponding voltage.

Having adjusted the slope, the intercept may now be simply adjusted using a known input level. A value of –35 dBm (397.6 mV

rms, or 400 mV to within 0.05 dB) is recommended, and if the

standard scaling is used (P

then V

should be set to +2 V at this input level.

LOG

= –88.33 dBm, VY = 37.5 mV/dB),

X

A Low Cost Audio Through RF Power Meter

Figure 7 shows a simple power meter that uses the AD606 and

an ICL7136 3-1/2 digit DMM IC driving an LCD readout. The

circuit operates from a single +5 V supply and provides direct

readout in dBm, with a resolution of 0.1 dBm.

In contrast to the limited dynamic range of the diode and

thermistor-styled sensors used in power meters, the AD606 can

measure signals from below –80 dBm to over +10 dBm. An

optional 50 Ω termination is included in the figure; this could

form the lower arm of an external attenuator to accommodate

larger signal levels. By the simple expedient of using a 13 dB

attenuator, the LCD reading now becomes dBV (decibels above

1 V rms). This requires a series resistor of 174 Ω, presenting an

input resistance of 224 Ω. Alternatively, the input resistance can

be raised to 600 Ω using 464 Ω and 133 Ω. It is important to

note that the AD606 inputs must be ac coupled. To extend the

low frequency range, use larger coupling capacitors and an

external loop filter, as outlined earlier.

The nominal 0.5 V to 3.5 V output of the AD606 (for a –75 dBm

to +5 dBm input) must be scaled and level shifted to fit within

the +1 V to +4.5 V common-mode range of the ICL7136 for

the +5 V supply used. This is achieved by the passive resistor

network of R1, R2, and R3 in conjunction with the bias networks of R4 through R7, which provide the ICL7136 with its

reference voltage, and R9 through R11, which set the intercept.

The ICL7136 measures the differential voltage between INHI

and INLO, which ranges from –75 mV to +5 mV for a

–75 dBm to +5 dBm input.

To calibrate the power meter, first adjust R6 for 100 mV between REF HI and REF LO. This sets the initial slope. Then

adjust R10 to set INLO 80 mV higher than INHI. This sets the

initial intercept. The slope and intercept may now be adjusted

using a calibrated signal generator as outlined in the previous

section.

To extend the low frequency limit of the system to audio fre-

quencies, simply change C1, C2, and C3 to 4.7 µF.

The limiter output of the AD606 may be used to drive the highimpedance input of a frequency counter.

dBV

INPUT

dBm

INPUT

174V

INHI

INLO

0.1mF

COMM

COMM

C1*

100pF

51.1V

C2*

100pF

*

FOR AUDIO MEASUREMENTS CHANGE

C1, C2, AND C3 TO 4.7mF; POSITIVE POLARITY

CONNECT TO PINS 1, 16

NC = NO CONNECT

PRUP

AD606JN

ISUM

NC

+5V

NC

OPTIONAL

DRIVE TO

VPOS

ILOG

150pF

FIL1

BFIN

NC

C3*

FIL2

VLOG

LADJ

OPCM

FREQUENCY

COUNTER

200V

LMHI

LMLO

R1

1MV

+5V

100kV

5kV

R10

100kV

54.9kV

54.9kV

+5V

R8

R9

+5V

R2

R3

Figure 7. A Low Cost RF Power Meter

4.99kV

4.32kV

500V

162V

2.513V NOM

80mV

FOR

0dBm

SIGNAL

INPUT

2.433V NOM

+5V

+5V

R4

36

R5

R6

R7

100mV

C4

1mF

REF HI

35

REF LO

32

COMM

INLO

ICL7136CPL

31

INHI

0.1mF

DISPLAY

–75.0

40

180kV

39

50pF

38

34

0.1mF

33

0.1mF

1.8MV

0.047mF

V–

–8–

REV. B

Page 9

AD606

C1

4.7mF

C2

4.7mF

+

+

LOW-PASS

FILTER

R1

100V

C3

680pF

R2

100V

INHI

INLO

AC

INPUT

20dB

ATTENUATOR

R4

453V

R5

51.1V

DIECAST BOX

Figure 8. Circuit for Low Frequency Measurements

Low Frequency Applications

With reasonably sized input coupling capacitors and an optional

input low-pass filter, the AD606 can operate to frequencies as

low as 200 Hz with good log conformance. Figure 8 shows the

schematic, with the low-pass filter included in the dashed box.

This circuit should be built inside a die cast box and the signal

brought in through a coaxial connector. The circuit must also

have a low-pass filter to reject the attenuated RF signals that

would otherwise be rectified along with the desired signal and

be added to the log output. The shielded and filtered circuit has

a 90 dB dynamic range, as shown in Figure 9.

In this circuit, R4 and R5 form a 20 dB attenuator that extends

the input range to 10 V rms. R3 isolates loads from VLOG.

Capacitors C1 and C2 (4.7 µF each), R1, R2, and the AD606’s

input resistance of 2.5 kΩ form a 100 Hz high-pass filter that is

before the AD606; the corner frequency of this filter must be

well below the lowest frequency of interest. In addition, the

offset-correction loop introduces another pole at low signal

levels that is transformed into another high-pass filter because it

is in a feedback path. This indicates that there has to be a

gradual transition from a 40 dB roll off at low signal levels to a

20 dB roll off at high signal levels, at which point the feedback

low pass filter is effectively disabled since the incoming signal

swamps the feedback signal.

0.1mF

COMM

PRUP

VPOS

C4

4.7mF

FIL1

FIL2

LADJ

LMHI

+5V

AD606JN

COMM

ISUM

ILOG

BFIN

VLOG

OPCM

LMLO

NC

NC

NC

R3

1kV

NC = NO CONNECT

TO

DVM

This low-pass filter introduces some attenuation due to R1 and

R2 in conjunction with the 2.5 kΩ input resistance of the

AD606. To minimize this effect, the value of R1 and R2 should

be kept as small as possible–100 Ω is a good value since it bal-

ances the need to reduce the attenuation as mentioned above

with the requirement for R1 and R2 to be much larger then the

impedance of C1 and C2 at the low-pass corner frequency, in

our case about 1 MHz.

4

3

2

– Volts DC

LOG

V

1

0

–80 40

1kHz – 10MHz

–60

90dB

3.5V

100Hz

020–20–40

INPUT SIGNAL – dBm

REV. B

Figure 9. Performance of Low Frequency Circuit at 100 Hz

and 1 kHz to 10 MHz (Note Attenuation)

–9–

Page 10

8/30/99 9 AM

AD606–Typical Performance Characteristics

0.5

–0.5

–1.5

–2.5

–3.5

–4.5

–5.5

NORMALIZED LIMITER OUTPUT – dB

–6.5

–80

70MHz

45MHz

10.7MHz

–60

–50–70 –10–30

INPUT LEVEL – dBm

0

–20–40

20

Figure 10. Normalized Limiter

Amplitude Response vs. Input Level

at 10.7 MHz, 45 MHz and 70 MHz

4.5

TA = +258C

4

3.5

3

2.5

2

– Volts DC

LOG

1.5

V

1

0.5

0

–60–80

Figure 13. V

INPUT POWER – dBm

LOG

VS = 5.5V

VS = 5V

VS = 4.5V

0–20–40

Plotted vs. Input

10

Level at 10.7 MHz as a Function of

Power Supply Voltage

5

0

45MHz

–5

–10

–15

–20

NORMALIZED PHASE SHIFT – Degrees

–25

–80

10.7MHz

70MHz

–60

INPUT LEVEL – dBm

0

–20–40

20

Figure 11. Normalized Limiter

Phase Response vs. Input Level at

10.7 MHz, 45 MHz, and 70 MHz

4

3

2

TA = –258C

1

0

–1

–2

LOGARITHMIC ERROR – dB

–3

–4

–60

–80

INPUT AMPLITUDE – dBm

TA = +258C

TA = +708C

–20

0–40

10

Figure 14. Logarithmic Conformance as a Function of Input Level at

10.7 MHz at –25°C, +25°C, and

°

C

+70

14

12

10

8

6

4

2

POWER SUPPLY CURRENT – mA

0

0

0.5

PRUP VOLTAGE – Volts

5

4.543.532.521.51

Figure 12. Supply Current vs. PRUP

°

Voltage at +25

5

4

3

2

1

0

–1

–2

–3

LOGARITHMIC ERROR – dB

–4

–5

–80

C

TA = –258C

TA = +708C

–60

INPUT AMPLITUDE – dBm

TA = +258C

0–40 –20

10

Figure 15. Logarithmic Conformance as a Function of Input Level at

45 MHz at –25°C, +25°C, and +70°C

Figure 16. Limiter Response at

Onset of 10.7 MHz Modulated Pulse

at –75 dBm Using 200 pF Input

Coupling Capacitors

Figure 17. V

Response to a

LOG

10.7 MHz CW Signal Modulated by

a 25 µs Wide Pulse with a 25 kHz

Repetition Rate Using 200 pF Input

Coupling Capacitors. The Input Signal Goes from +5 dBm to –75 dBm

in 20 dB Steps.

–10–

Figure 18. Limiter Response at

Onset of 70 MHz Modulated Pulse

at –55 dBm Using 200 pF Input

Coupling Capacitors

REV. B

Page 11

AD606

Figure 19. V

Output for a Pulsed

LOG

10.7 MHz Input; Top Trace: –35 dBm

to +5 dBm; Middle Trace: –15 dBm to

–55 dBm; Bottom Trace: –35 dBm to –

75 dBm

–10dB TO +30dB

(10.7MHz SWEPT

GAIN TESTS ONLY)

FLUKE 6082A

SYNTHESIZED

SIGNAL

GENERATOR

MODULATED

PULSE

TESTS

HEWLETT PACKARD

8112A PULSE

GENERATOR

AD602

SWEPT GAIN

TESTS

Figure 20. Example of Test Signal

Used for Figure 19

+5V

0.1mF

NC

VPOS

ILOG

150pF

FIL1

BFIN

NC

C3

FIL2

VLOG

RF

INPUT

51.1V

C1

100pF

INHI

INLO

C2

100pF

NC = NO CONNECT

COMM

COMM

PRUP

AD606JN

ISUM

NC

Figure 21. V

Output for 10.7 MHz

LOG

CW Input with PRUP Toggled ON

and OFF; Top Trace: +5 dBm Input;

Middle Trace: –35 dBm Input; Bottom

Trace: –75 dBm; PRUP Input from

µ

HP8112A: 0 to 4 V, 10

s Pulsewidth

with 10 kHz Repetition Rate

200V

LMHI

LADJ

+5V

LMLO

200V

10 x

ATTN

TEKTRONIX 7704A

MAINFRAME

OSCILLOSCOPE

P6201

PROBES

6137

PROBES

7A18

AMP

7A24

AMP

TIME-BASE

OPCM

7B53A

REV. B

Figure 22. Test Setup for Characterization Data

–11–

Page 12

AD606

0.31 (7.87)

PIN 1

0.125 (3.18)

0.1574 (4.00)

0.1497 (3.80)

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

16-Lead Plastic DIP

(N-16)

0.87 (22.1) MAX

16

18

MIN

0.018

0.100

(0.46)

(2.54)

BSC

9

0.033

(0.84)

0.25 (6.35)

0.35

(0.89)

(4.57)

SEATING

PLANE

0.18

16-Lead Narrow-Body SOIC

(R-16A)

0.3937 (10.00)

0.3859 (9.80)

16 9

0.2440 (6.20)

0.2284 (5.80)

81

0.300 (7.62)

0.011

(0.28)

0.18 (4.57)

MAX

C1698b–0–8/99

PIN 1

0.0098 (0.25)

0.0040 (0.10)

0.050 (1.27)

BSC

0.0192 (0.49)

0.0138 (0.35)

0.0688 (1.75)

0.0532 (1.35)

SEATING

PLANE

0.0099 (0.25)

0.0075 (0.19)

0.0196 (0.50)

0.0099 (0.25)

88

08

0.0500 (1.27)

0.0160 (0.41)

3 458

PRINTED IN U.S.A.

–12–

REV. B

Loading...

Loading...