Page 1

Dual, Low Noise, Wideband

a

FEATURES

2 Channels with Independent Gain Control

"Linear in dB" Gain Response

2 Gain Ranges:

AD600: 0 dB to 40 dB

AD602: –10 dB to +30 dB

Accurate Absolute Gain: 0.3 dB

Low Input Noise: 1.4 nV/√Hz

Low Distortion: –60 dBc THD at 1 V Output

High Bandwidth: DC to 35 MHz (–3 dB)

Stable Group Delay: 2 ns

Low Power: 125 mW (Max) per Amplifier

Signal Gating Function for Each Amplifier

Drives High Speed A/D Converters

MIL-STD-883-Compliant and DESC Versions Available

APPLICATIONS

Ultrasound and Sonar Time-Gain Control

High Performance Audio and RF AGC Systems

Signal Measurement

GENERAL DESCRIPTION

The AD600 and AD602 dual channel, low noise, variable gain

amplifiers are optimized for use in ultrasound imaging systems,

but are applicable to any application requiring very precise gain,

low noise and distortion, and wide bandwidth. Each independent channel provides a gain of 0 dB to +40 dB in the AD600

and –10 dB to +30 dB in the AD602. The lower gain of the

AD602 results in an improved signal-to-noise ratio at the output. However, both products have the same 1.4 nV/√Hz input

noise spectral density. The decibel gain is directly proportional

to the control voltage, is accurately calibrated, and is supplyand temperature-stable.

To achieve the difficult performance objectives, a proprietary

circuit form—the X-AMP

nel of the X-AMP comprises a variable attenuator of 0 dB to

–42.14 dB followed by a high speed fixed gain amplifier. In this

way, the amplifier never has to cope with large inputs, and can

benefit from the use of negative feedback to precisely define the

gain and dynamics. The attenuator is realized as a seven-stage

R-2R ladder network having an input resistance of 100 Ω, lasertrimmed to ±2%. The attenuation between tap points is 6.02 dB;

the gain-control circuit provides continuous interpolation between

these taps. The resulting control function is linear in dB.

*Patented.

®

—has been developed. Each chan-

Variable Gain Amplifiers

AD600/AD602

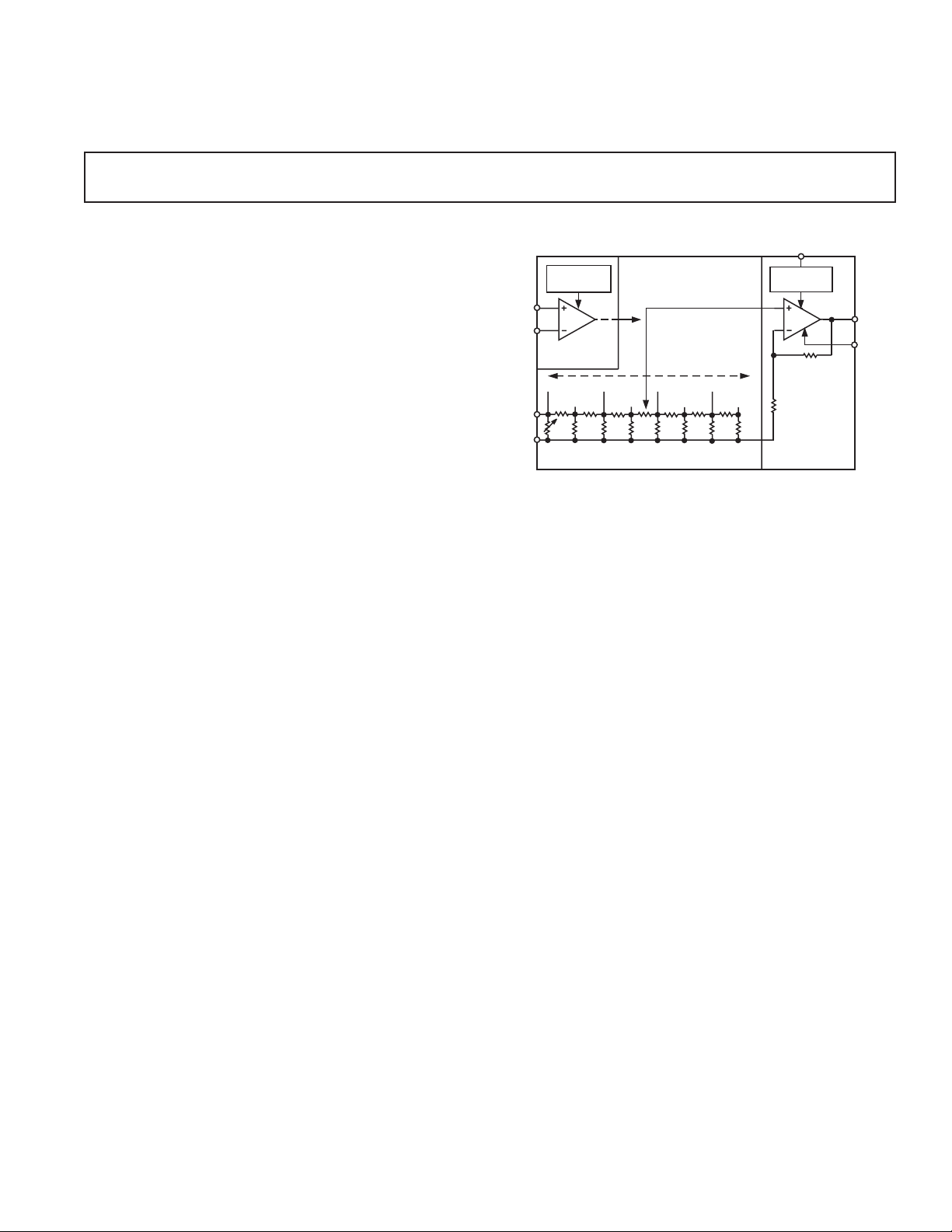

FUNCTIONAL BLOCK DIAGRAM

GAT1

SCALING

REFERENCE

C1HI

V

G

C1LO

GAIN CONTROL

INTERFACE

A1HI

A1LO

0dB

500

–12.04dB

–6.02dB

R-2R LADDER NETWORK

The gain-control interfaces are fully differential, providing an

input resistance of ~15 MΩ and a scale factor of 32 dB/V (that

is, 31.25 mV/dB) defined by an internal voltage reference. The

response time of this interface is less than 1 µs. Each channel

also has an independent gating facility that optionally blocks

signal transmission and sets the dc output level to within a few

millivolts of the output ground. The gating control input is TTL

and CMOS compatible.

The maximum gain of the AD600 is 41.07 dB, and that of the

AD602 is 31.07 dB; the –3 dB bandwidth of both models is

nominally 35 MHz, essentially independent of the gain. The

signal-to-noise ratio (SNR) for a 1 V rms output and a 1 MHz

noise bandwidth is typically 76 dB for the AD600 and 86 dB for

the AD602. The amplitude response is flat within ±0.5 dB from

100 kHz to 10 MHz; over this frequency range the group delay

varies by less than ±2 ns at all gain settings.

Each amplifier channel can drive 100 Ω load impedances with

low distortion. For example, the peak specified output is ±2.5 V

minimum into a 500 Ω load, or ± 1 V into a 100 Ω load. For a

200 Ω load in shunt with 5 pF, the total harmonic distortion for

a ±1 V sinusoidal output at 10 MHz is typically –60 dBc.

The AD600J and AD602J are specified for operation from 0°C

to 70°C, and are available in both 16-lead plastic DIP (N) and

16-lead SOIC (R) packages. The AD600A and AD602A are

specified for operation from –40°C to +85°C and are available in

both 16-lead Cerdip (Q) and 16-lead SOIC (R) packages.

The AD600S and AD602S are specified for operation from

–55°C to +125°C, are available in a 16-lead Cerdip (Q) package,

and are MIL-STD-883 compliant. The AD600S and AD602S

are also available under DESC SMD 5962-94572.

PRECISION PASSIVE

INPUT ATTENUATOR

–22.08dB

–18.06dB

–30.1dB

–36.12dB

–42.14dB

62.5

GATING

INTERFACE

RF2

2.24k(AD600)

694(AD602)

RF1

20

FIXED-GAIN

AMPLIFIER

41.07dB(AD600)

31.07(AD602)

*

A1OP

A1CM

REV. D

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

Page 2

AD600/AD602–SPECIFICATIONS

(Each amplifier section, at TA = 25C, VS = 5 V, –625 mV ≤ VG ≤

+625 mV, RL = 500 , and CL = 5 pF, unless otherwise noted. Specifications for the AD600 and AD602 are identical unless otherwise noted.)

Parameter Conditions Min Typ Max Min Typ Max Unit

AD600J/AD602J AD600A/AD602A

INPUT CHARACTERISTICS

Input Resistance Pins 2 to 3; Pins 6 to 7 98 100 102 95 100 105 Ω

Input Capacitance 22pF

Input Noise Spectral Density

Noise Figure R

1

= 50 Ω, Maximum Gain 5.3 5.3 dB

S

1.4 1.4 nV/√Hz

RS = 200 Ω, Maximum Gain 2 2 dB

Common-Mode Rejection Ratio f = 100 kHz 30 30 dB

OUTPUT CHARACTERISTICS

–3 dB Bandwidth V

Slew Rate 275 275 V/µs

Peak Output

2

= 100 mV rms 35 35 MHz

OUT

RL ≥ 500 Ω±2.5 ± 3 ±2.5 ±3V

Output Impedance f ≤ 10 MHz 2 2 Ω

Output Short-Circuit Current 50 50 mA

Group Delay Change vs. Gain f = 3 MHz; Full Gain Range ±2 ±2ns

Group Delay Change vs. Frequency VG = 0 V, f = 1 MHz to 10 MHz ±2 ±2ns

Total Harmonic Distortion RL= 200 Ω, V

= ±1 V Peak, Rpd = 1 kΩ –60 –60 dBc

OUT

ACCURACY

AD600

Gain Error 0 dB to 3 dB Gain 0 +0.5 +1 –0.5 +0.5 +1.5 dB

3 dB to 37 dB Gain –0.5 ± 0.2 +0.5 –1.0 ±0.2 +1.0 dB

37 dB to 40 dB Gain –1 –0.5 0 –1.5 –0.5 +0.5 dB

Maximum Output Offset Voltage3VG = –625 mV to +625 mV 10 50 10 65 mV

Output Offset Variation VG = –625 mV to +625 mV 10 50 10 65 mV

AD602

Gain Error –10 dB to –7 dB Gain 0 +0.5 +1 –0.5 +0.5 +1.5 dB

–7 dB to +27 dB Gain –0.5 ± 0.2 +0.5 –1.0 ±0.2 +1.0 dB

27 dB to 30 dB Gain –1 –0.5 0 –1.5 –0.5 +0.5 dB

Maximum Output Offset Voltage3VG = –625 mV to +625 mV 5 30 10 45 mV

Output Offset Variation VG = –625 mV to +625 mV 5 30 10 45 mV

GAIN CONTROL INTERFACE

Gain Scaling Factor 3 dB to 37 dB (AD600); –7 dB to +27 dB (AD602) 31.7 32 32.3 30.5 32 33.5 dB/V

Common-Mode Range –0.75 +2.5 –0.75 +2.5 V

Input Bias Current 0.35 1 0.35 1 µA

Input Offset Current 10 50 10 50 nA

Differential Input Resistance Pins 1 to 16; Pins 8 to 9 15 15 MΩ

Response Rate Full 40 dB Gain Change 40 40 dB/µs

SIGNAL GATING INTERFACE

Logic Input “LO” (Output ON) 0.8 0.8 V

Logic Input “HI” (Output OFF) 2.4 2.4 V

Response Time ON to OFF, OFF to ON 0.3 0.3 µs

Input Resistance Pins 4 to 3; Pins 5 to 6 30 30 kΩ

Output Gated OFF

Output Offset Voltage ±10 100 ± 10 400 mV

Output Noise Spectral Density 65 65 nV/√Hz

Signal Feedthrough @ 1 MHz

AD600 –80 –80 dB

AD602 –70 –70 dB

POWER SUPPLY

Specified Operating Range ±4.75 ±5.25 ±4.75 ±5.25 V

Quiescent Current 11 12.5 11 14 mA

NOTES

1

Typical open or short-circuited input; noise is lower when the system is set to maximum gain and the input is short-circuited. This figure includes the effects of both

voltage and current noise sources.

2

Using resistive loads of 500 Ω or greater, or with the addition of a 1 k Ω pull-down resistor when driving lower loads.

3

The dc gain of the main amplifier in the AD600 is ⫻113; thus an input offset of only 100 µV becomes an 11.3 mV output offset. In the AD602, the amplifier’s gain is

⫻35.7; thus, an input offset of 100 µV becomes a 3.57 mV output offset.

Specifications shown in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min

and max specifications guaranteed, although only those shown in boldface are tested on all production units.

Specifications subject to change without notice.

–2–

REV. D

Page 3

AD600/AD602

ABSOLUTE MAXIMUM RATINGS

1

Supply Voltage ±VS . . . . . . . . . . . . . . . . . . . . . . . . . . . ±7.5 V

Input Voltages

Pins 1, 8, 9, 16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±V

S

Pins 2, 3, 6, 7 . . . . . . . . . . . . . . . . . . . . . . ±2 V Continuous

. . . . . . . . . . . . . . . . . . . . . . . . . ±V

Pins 4, 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± V

for 10 ms

S

S

Internal Power Dissipation2 . . . . . . . . . . . . . . . . . . . . 600 mW

Operating Temperature Range (J) . . . . . . . . . . . . 0°C to 70°C

Operating Temperature Range (A) . . . . . . . . –40°C to +85°C

Operating Temperature Range (S) . . . . . . . –55°C to +125°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering 60 sec) . . . . . . . . . 300°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Thermal characteristics:

16-lead plastic package: θJA = 85°C/W

16-lead SOIC package: θJA = 100°C/W

16-lead Cerdip package: θJA = 120°C/W

ORDERING GUIDE

Model Gain Range Range Option

Temperature Package

1

AD600AQ 0 dB to 40 dB –40°C to +85°C Q-16

AD600AR 0 dB to 40 dB –40°C to +85°C R-16

AD600AR-REEL 0 dB to 40 dB –40°C to +85°C R-16

AD600AR-REEL7 0 dB to 40 dB –40°C to +85°C R-16

AD600ARZ

AD600ARZ-R7

AD600ARZ-RL

2

0 dB to 40 dB –40°C to +85°C R-16

2

0 dB to 40 dB –40°C to +85°C R-16

2

0 dB to 40 dB –40°C to +85°C R-16

AD600JCHIPS DIE

AD600JN 0 dB to 40 dB 0°C to 70°C N-16

AD600JR 0 dB to 40 dB 0°C to 70°C R-16

AD600JR-REEL 0 dB to 40 dB 0°C to 70°C R-16

AD600JR-REEL7 0 dB to 40 dB 0°C to 70°C R-16

AD600JRZ

AD600JRZ-R7

AD600JRZ-RL

AD600SQ/883B

2

0 dB to 40 dB 0°C to 70°C R-16

2

0 dB to 40 dB 0°C to 70°C R-16

2

0 dB to 40 dB 0°C to 70°C R-16

3

0 dB to 40 dB –55°C to +125°C Q-16

AD602AQ –10 dB to +30 dB –40°C to +85°C Q-16

AD602AR –10 dB to +30 dB –40°C to +85°C R-16

AD602AR-REEL –10 dB to +30 dB –40°C to +85°C R-16

AD602AR-REEL7 –10 dB to +30 dB –40°C to +85°C R-16

AD602JCHIPS DIE

AD602JN –10 dB to +30 dB 0°C to 70°C N-16

AD602JR –10 dB to +30 dB 0°C to 70°C R-16

AD602JR-REEL –10 dB to +30 dB 0°C to 70°C R-16

AD602JR-REEL7 –10 dB to +30 dB 0°C to 70°C R-16

AD602SQ/883B4–10 dB to +30 dB –55°C to +150°C Q-16

NOTES

1

N = plastic DIP; Q = Cerdip; R = small outline IC (SOIC).

2

Z = Pb-free part.

3

Refer to AD600/AD602 Military data sheet. Also available as 5962-9457201MEA.

4

Refer to AD600/AD602 Military data sheet. Also available as 5962-9457202MEA.

PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Description

1 C1LO CH1 Gain-Control Input “LO” (Positive

Voltage Reduces CH1 Gain)

2 A1HI CH1 Signal Input “HI” (Positive Voltage

Increases CH1 Output)

3 A1LO CH1 Signal Input “LO” (Usually Taken to

CH1 Input Ground)

4 GAT1 CH1 Gating Input (A Logic “HI” Shuts Off

CH1 Signal Path)

5 GAT2 CH2 Gating Input (A Logic “HI” Shuts Off

CH2 Signal Path)

6 A2LO CH2 Signal Input “LO” (Usually Taken to

CH2 Input Ground)

7 A2HI CH2 Signal Input “HI” (Positive Voltage

Increases CH2 Output)

8 C2LO CH2 Gain-Control Input “LO” (Positive

Voltage Reduces CH2 Gain)

9 C2HI CH2 Gain-Control Input “HI” (Positive

Voltage Increases CH2 Gain)

10 A2CM CH2 Common (Usually Taken to CH2

Output Ground)

11 A2OP CH2 Output

12 VNEG Negative Supply for Both Amplifiers

13 VPOS Positive Supply for Both Amplifiers

14 A1OP CH1 Output

15 A1CM CH1 Common (Usually Taken to CH1

Output Ground)

16 C1HI CH1 Gain-Control Input “HI” (Positive

Voltage Increases CH1 Gain)

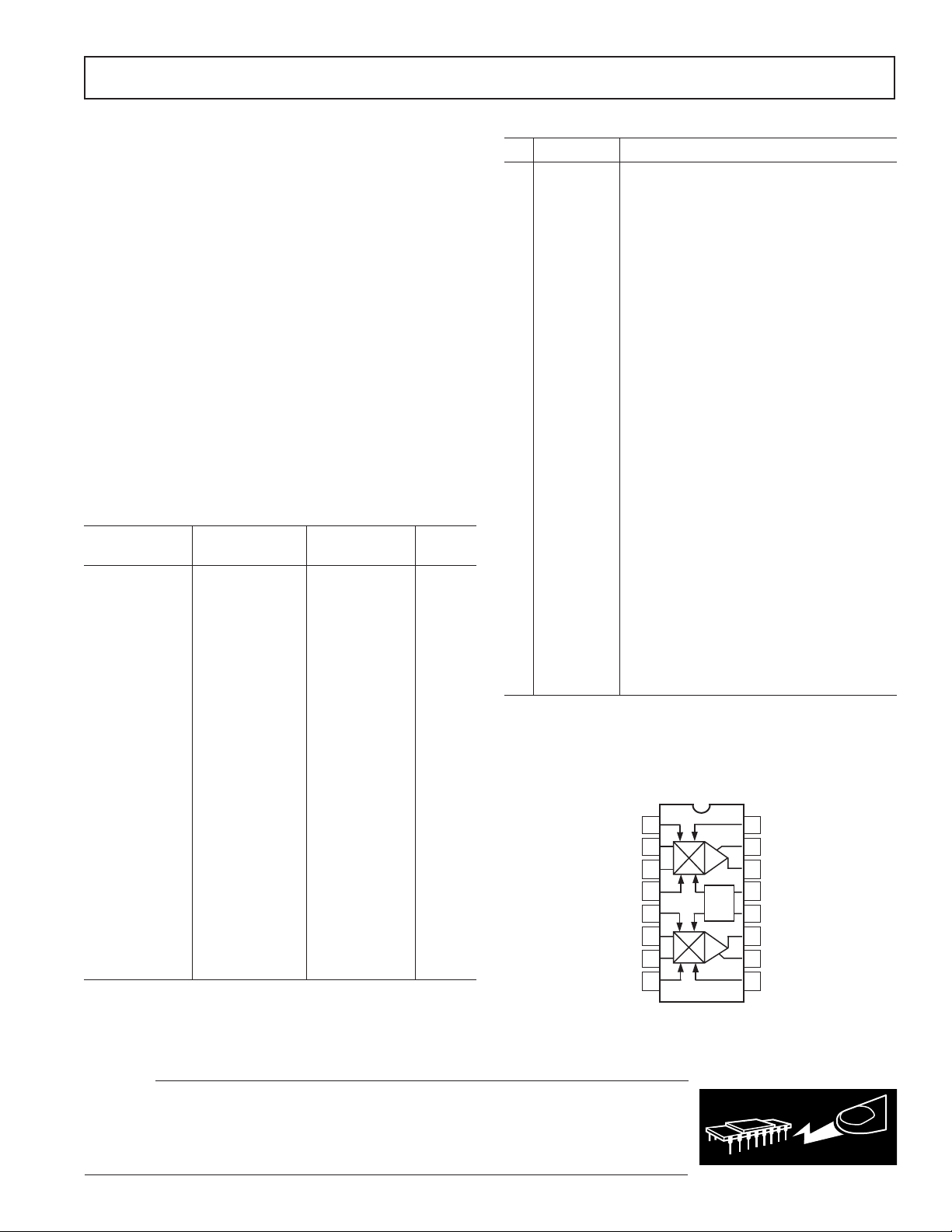

CONNECTION DIAGRAM

16-Lead Plastic DIP (N) Package

16-Lead Plastic SOIC (R) Package

16-Lead Cerdip (Q) Package

C1LO

A1HI

A1LO

GAT1

GAT2

A2LO

A2HI

C2LO

1

2

+

3

–

4

5

–

6

7

+

8

AD600 / AD602

A1

REF

A2

C1HI

16

A1CM

15

A1OP

14

VPOS

13

VNEG

12

11

A2OP

10

A2CM

9

C2HI

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD600/AD602 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

REV. D

–3–

WARNING!

ESD SENSITIVE DEVICE

Page 4

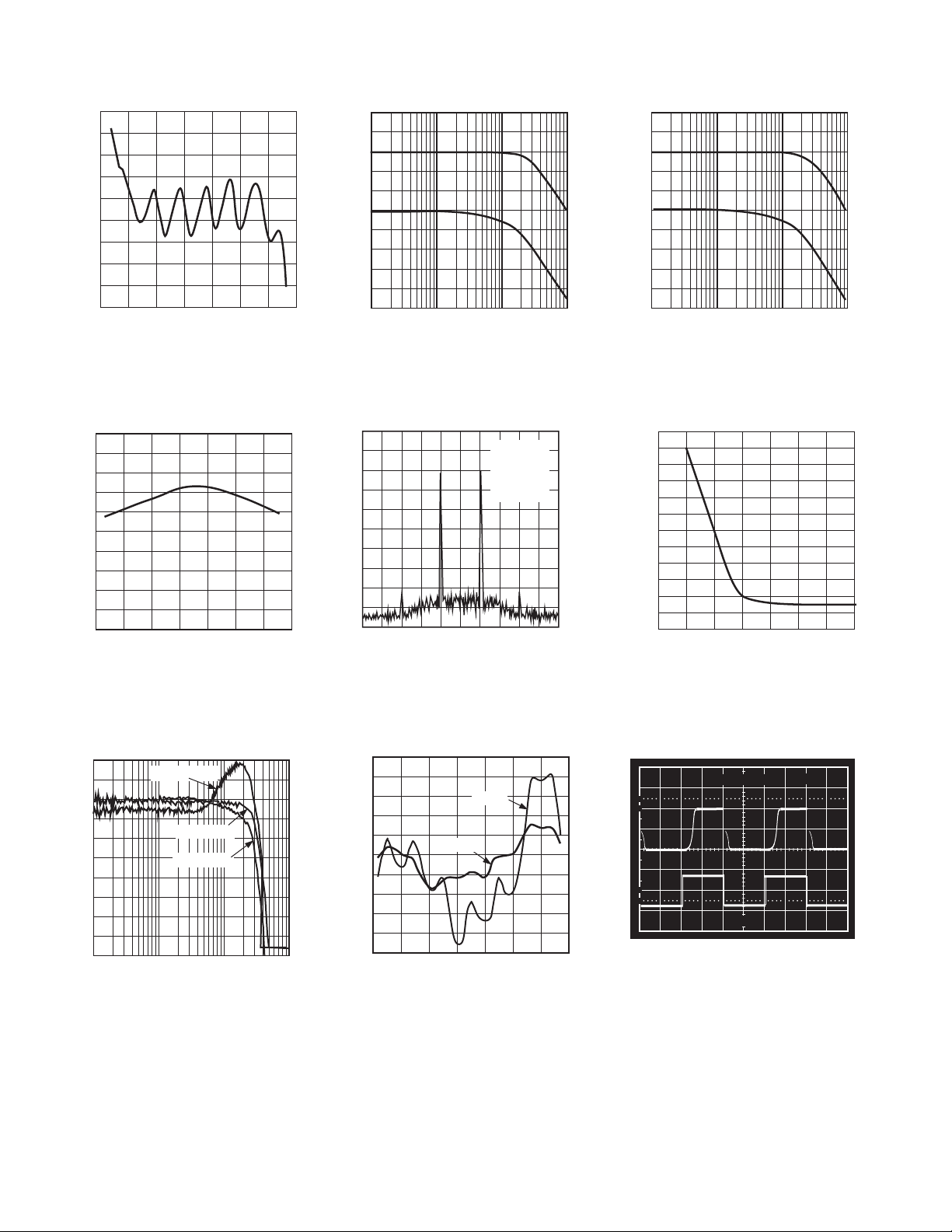

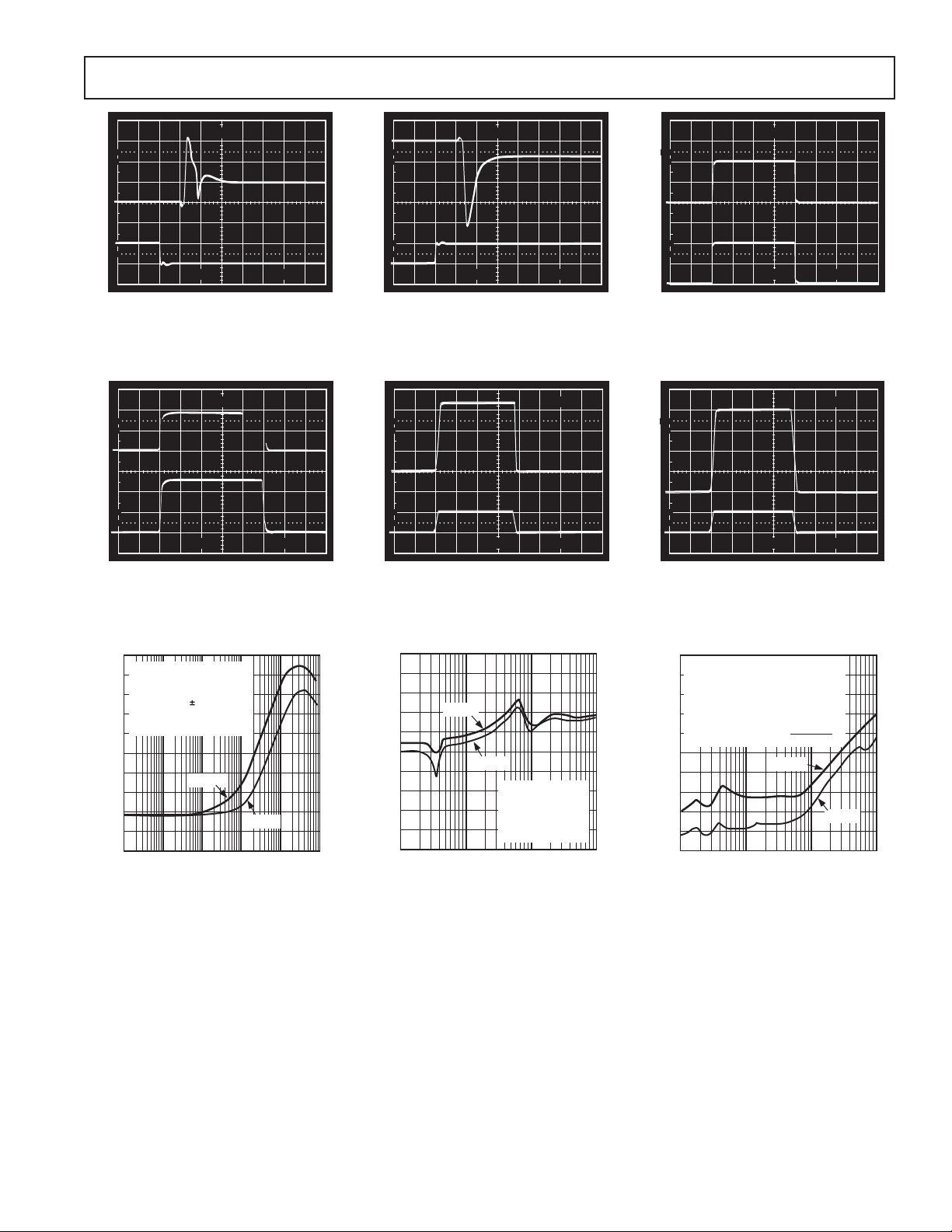

AD600/AD602–Typical Performance Characteristics

0.45

0.35

0.25

0.15

0.05

–0.05

–0.15

GAIN ERROR – dB

–0.25

–0.35

–0.45

–0.5–0.7

GAIN CONTROL VOLTAGE – V

0.50.30.1–0.1–0.3

0.7

20dB

17dB

0

–45

–90

100k 1M 100M10M

FREQUENCY – Hz

10dB

7dB

0

–45

–90

100k 1M 100M10M

FREQUENCY – Hz

TPC 1. Gain Error vs. Gain Control

Voltage

10.0

9.8

9.6

9.4

9.2

9.0

8.8

8.6

GROUP DELAY – ns

8.4

8.2

8.0

GAIN CONTROL VOLTAGE – V

0.7–0.5–0.7 0.50.30.1–0.1–0.3

TPC 4. AD600 and AD602 Typical

Group Delay vs. V

102

101

100

99

98

97

96

95

INPUT IMPEDANCE –

94

93

92

100k 1M 100M10M

FREQUENCY – Hz

C

GAIN = 40dB

GAIN = 20dB

GAIN = 0dB

TPC 2. AD600 Frequency and Phase

Response vs. Gain

VG = 0V

10dB/DIV

CENTER

FREQ 1MHz

10kHz/DIV

TPC 5. Third Order Intermodulation Distortion, V

RL = 500

–1

–2

OUTPUT OFFSET VOLTAGE – mV

–3

–4

Ω

6

5

4

3

2

1

0

–0.5

–0.7

GAIN CONTROL VOLTAGE – V

OUT

AD602

= 2 V p-p,

AD600

0.7

0.50.1 0.3–0.3 –0.1

TPC 3. AD602 Frequency and Phase

Response vs. Gain

–1.0

–1.2

–1.4

–1.6

–1.8

–2.0

–2.2

–2.4

–2.6

–2.8

–3.0

–3.2

NEGATIVE OUTPUT VOLTAGE LIMIT – V

–3.4

50

0

LOAD RESISTANCE –

20001000500200100

TPC 6. Typical Output Voltage vs.

Load Resistance (Negative Output

Swing Limits First)

1µs

100

90

OUTPUTINPUT

10

0%

1V VOUT

1V VC

TPC 7. Input Impedance vs.

Frequency

TPC 8. Output Offset vs. Gain

Control Voltage (Control Channel

Feedthrough)

–4–

TPC 9. Gain Control Channel

Response Time. Top: Output Voltage, 2 V max, Bottom: Gain Control Voltage V

= ±625 mV

C

REV. D

Page 5

AD600/AD602

50mV

100

90

OUTPUT

10

0%

INPUT

5V

100ns

TPC 10. Gating Feedthrough to

Output, Gating Off to On

500mV

100

90

OUTPUTINPUT

10

0%

1V

200ns

TPC 13. Input Stage Overload

Recovery Time

50mV

100

90

OUTPUTINPUT

10

0%

5V

100ns

TPC 11. Gating Feedthrough to

Output, Gating On to Off

1V

100

90

OUTPUTINPUT

10

0%

200mV

500ns

TPC 14. Output Stage Overload

Recovery Time

1V

100

90

OUTPUT

10

0%

INPUT

100mV

TPC 12. Transient Response,

Medium and High Gain

500mV

100

90

OUTPUTINPUT

10

0%

1V

TPC 15. Transient Response

Minimum Gain

500ns

500ns

10

AD600: G = 20dB

5

AD602: G = 10dB

BOTH: V

0

V

R

–5

T

–10

–15

–20

CMRR – dB

–25

–30

–35

–40

1k 10k 100k 1M 10M 100M

= 100mV RMS

CM

= 5V

S

= 500

L

= 25C

A

AD600

FREQUENCY – Hz

AD602

TPC 16. CMRR vs. Frequency

20

10

0

–10

–20

–30

–40

PSRR – dB

–50

–60

–70

–80

100k 1M 100M10M

AD600

AD602

FREQUENCY – Hz

AD600: G = 40dB

AD602: G = 30dB

BOTH: R

V

R

TPC 17. PSRR vs. Frequency

= 500

L

= 0V

IN

= 50

S

10

AD600: CH1 G = 40dB, V

0

–10

–20

–30

–40

–50

CROSSTALK – dB

–60

–70

–80

–90

100k 1M 100M10M

CH2 G = 20dB, V

AD602: CH1 G = 30dB, V

CH2 G = 0dB, V

BOTH: V

CROSSTALK = 20log

= 1V RMS1, RS = 50,

OUT

= 500

R

L

FREQUENCY – Hz

= 0

IN

= 100mV

IN

= 0

IN

= 316mV

IN

CH1 V

OUT

{}

CH2 V

IN

AD600

AD602

TPC 18. Crosstalk between A1

and A2 vs. Frequency

REV. D

–5–

Page 6

AD600/AD602

THEORY OF OPERATION

The AD600 and AD602 have the same general design and

features. They comprise two fixed gain amplifiers, each preceded by a voltage-controlled attenuator of 0 dB to 42.14 dB

with independent control interfaces, each having a scaling factor

of 32 dB per volt. The gain of each amplifier in the AD600 is

laser trimmed to 41.07 dB (⫻113), providing a control range

of –1.07 dB to +41.07 dB (0 dB to +40 dB with overlap). The

AD602 amplifiers have a gain of 31.07 dB (⫻35.8) and pro-

vide an overall gain of –11.07 dB to +31.07 dB (–10 dB to

+30 dB with overlap).

The advantage of this topology is that the amplifier can use

negative feedback to increase the accuracy of its gain. Also, since

the amplifier never has to handle large signals at its input, the

distortion can be very low. Another feature of this approach is

that the small-signal gain and phase response, and thus the

pulse response, are essentially independent of gain.

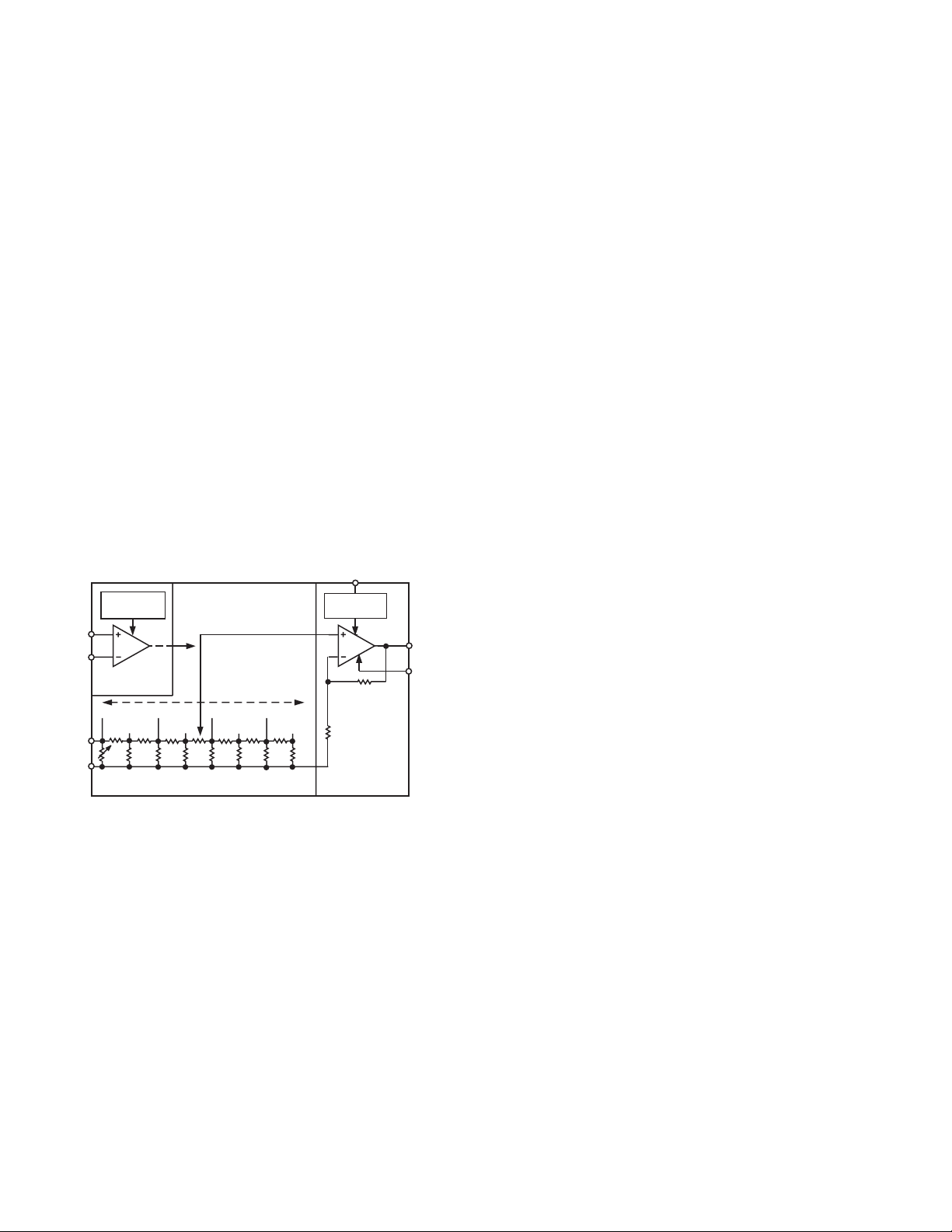

The following describes the AD600. Figure 1 is a simplified

schematic of one channel. The input attenuator is a seven-section

R-2R ladder network, using untrimmed resistors of nominally

R = 62.5 Ω, which results in a characteristic resistance of

125 Ω ± 20%. A shunt resistor is included at the input and laser

trimmed to establish a more exact input resistance of 100 Ω ± 2%,

which ensures accurate operation (gain and HP corner frequency)

when used in conjunction with external resistors or capacitors.

GAT1

PRECISION PASSIVE

INPUT ATTENUATOR

–22.08dB

–18.06dB

–30.1dB

–36.12dB

–42.14dB

62.5

GATING

INTERFACE

RF2

2.24k(AD600)

694(AD602)

RF1

20

FIXED-GAIN

AMPLIFIER

41.07dB(AD600)

31.07(AD602)

A1OP

A1CM

C1HI

C1LO

A1HI

A1LO

SCALING

REFERENCE

V

G

GAIN CONTROL

INTERFACE

0dB

500

–12.04dB

–6.02dB

R-2R LADDER NETWORK

Figure 1. Simplified Block Diagram of Single Channel of

the AD600 and AD602

The nominal maximum signal at input A1HI is 1 V rms (±1.4 V

peak) when using the recommended ±5 V supplies, although

operation to ±2 V peak is permissible with some increase in HF

distortion and feedthrough. Each attenuator is provided with a

separate signal “LO” connection for use in rejecting common

mode, the voltage between input and output grounds. Circuitry

is included to provide rejection of up to ±100 mV.

The signal applied at the input of the ladder network is attenuated by 6.02 dB by each section; thus, the attenuation to each of

the taps is progressively 0, 6.02, 12.04, 18.06, 24.08, 30.1, 36.12,

and 42.14 dB. A unique circuit technique is employed to interpolate between these tap points, indicated by the “slider” in

Figure 1, providing continuous attenuation from 0 dB to 42.14 dB.

To understand the AD600, it helps to think in terms of a

mechanical means for moving this slider from left to right; in

fact, it is voltage controlled. The details of the control interface

are discussed later. Note that the gain is exactly determined

at all times, and a linear decibel relationship is automatically

guaranteed between the gain and the control parameter that

determines the position of the slider. In practice, the gain

deviates from the ideal law by about ±0.2 dB peak (see Figure 6).

Note that the signal inputs are not fully differential. A1LO,

A1CM (for CH1), A2LO, and A2CM (for CH2) provide

separate access to the input and output grounds. This recognizes that even when using a ground plane, small differences

arise in the voltages at these nodes. It is important that A1LO

and A2LO be connected directly to the input ground(s).

Significant impedance in these connections reduces the gain

accuracy. A1CM and A2CM should be connected to the load

ground(s).

Noise Performance

An important reason for using this approach is the superior

noise performance that can be achieved. The nominal resistance

seen at the inner tap points of the attenuator is 41.7 Ω (one third

of 125 Ω), which, at 27°C, exhibits a Johnson noise spectral density (NSD) of 0.84 nV/√Hz (that is, √4kTR), a large fraction of

the total input noise. The first stage of the amplifier contributes

another 1.12 nV/√Hz, for a total input noise of 1.4 nV/√Hz.

The noise at the 0 dB tap depends on whether the input is

short-circuited or open-circuited. When shorted, the minimum

NSD of 1.12 nV/√Hz is achieved. When open, the resistance

of 100 Ω at the first tap generates 1.29 nV/√Hz, so the noise

increases to a total of 1.71 nV/√Hz. This last calculation would

be important if the AD600 were preceded, for example, by a

900 Ω resistor to allow operation from inputs up to ±10 V rms.

However, in most cases the low impedance of the source

limits the maximum noise resistance.

It is apparent from the foregoing that it is essential to use a low

resistance in the design of the ladder network to achieve low

noise. In some applications this may be inconvenient, requiring

the use of an external buffer or preamplifier. However, very few

amplifiers combine the needed low noise with low distortion at

maximum input levels, and the power consumption required to

achieve this performance is quite high (due to the need to maintain

very low resistance values while also coping with large inputs).

On the other hand, there is little value in providing a buffer

with high input impedance since the usual reason for this—

the minimization of loading of a high resistance source—is not

compatible with low noise.

Apart from the small variations just mentioned, the signal-tonoise (S/N) ratio at the output is essentially independent of the

attenuator setting, since the maximum undistorted output is

1Vrms and the NSD at the output of the AD600 is fixed at

113 ⫻ 1.4 nV/√Hz, or 158 nV/√Hz. Thus, in a 1 MHz bandwidth, the output S/N ratio would be 76 dB. The input NSD

of the AD600 and AD602 are the same, but because of the

10 dB lower gain in the AD602’s fixed amplifier, its output S/N

ratio is 10 dB better, or 86 dB in a 1 MHz bandwidth.

–6–

REV. D

Page 7

AD600/AD602

The Gain-Control Interface

The attenuation is controlled through a differential, high impedance (15 MΩ) input, with a scaling factor that is laser trimmed to

32 dB per volt, that is, 31.25 mV/dB. Each of the two amplifiers

has its own control interface. An internal band gap reference

ensures stability of the scaling with respect to supply and temperature variations, and is the only circuitry common to both channels.

When the differential input voltage V

= 0 V, the attenuator

G

slider is centered, providing an attenuation of 21.07 dB,

resulting in an overall gain of 20 dB (= –21.07 dB + 41.07 dB).

When the control input is –625 mV, the gain is lowered by

20 dB (= 0.625 × 32) to 0 dB; when set to 625 mV, the gain is

increased by 20 dB to 40 dB. When this interface is overdriven in either direction, the gain approaches either –1.07 dB

(= –42.14 dB + 41.07 dB) or 41.07 dB (= 0 + 41.07 dB),

respectively.

The gain of the AD600 can be calculated using the following

simple expression:

Gain (dB) = 32 V

where V

is in volts. For the AD602, the expression is:

G

Gain (dB) = 32 V

Operation is specified for V

+ 20 (1)

G

+ 10 (2)

G

in the range from –625 mV dc

G

to +625 mV dc. The high impedance gain-control input ensures

minimal loading when driving many amplifiers in multiple-channel

applications. The differential input configuration provides flexibility in choosing the appropriate signal levels and polarities for

various control schemes.

For example, the gain-control input can be fed differentially to

the inputs, or single-ended by simply grounding the unused

input. In another example, if the gain is to be controlled by

a DAC providing a positive only ground referenced output,

the Gain Control LO pin (either C1LO or C2LO) should be

biased to a fixed offset of 625 mV to set the gain to 0 dB when

Gain Control HI (C1HI or C2HI) is at zero, and to set the

gain to 40 dB when at 1.25 V.

It is a simple matter to include a voltage divider to achieve other

scaling factors. When using an 8-bit DAC with an FS output of

2.55 V (10 mV/bit), a 1.6 divider ratio (generating 6.25 mV/bit)

results in a gain setting resolution of 0.2 dB/bit. Later in this data

sheet, cascading the two sections of an AD600 or AD602

when various options exist for gain control is explained.

Signal-Gating Inputs

Each amplifier section of the AD600 and AD602 is equipped

with a signal gating function, controlled by a TTL or CMOS

logic input (GAT1 or GAT2). The ground references for these

inputs are the signal input grounds A1LO and A2LO, respectively. Operation of the channel is unaffected when this input is

LO or left open-circuited. Signal transmission is blocked when

this input is HI. The dc output level of the channel is set to

within a few millivolts of the output ground (A1CM or A2CM),

and simultaneously the noise level drops significantly. The

reduction in noise and spurious signal feedthrough is useful

in ultrasound beam-forming applications, where many amplifier

outputs are summed.

Common-Mode Rejection

A special circuit technique provides rejection of voltages appearing between input grounds (A1LO and A2LO) and output

grounds (A1CM and A2CM). This is necessary because of the

op amp form of the amplifier, as shown in Figure 1. The

feedback voltage is developed across the resistor RF1 (which, to

achieve low noise, has a value of only 20 Ω). The voltage

developed across this resistor is referenced to the input common,

so the output voltage is also referred to that node.

For zero differential signal input between A1HI and A1LO,

the output A1OP simply follows the voltage at A1CM. Note that

the range of voltage differences that can exist between A1LO

and A1CM (or A2LO and A2CM) is limited to about ±100 mV.

TPC 16 shows typical common-mode rejection ratio versus

frequency.

ACHIEVING 80 dB GAIN RANGE

The two amplifier sections of the X-AMP can be connected

in series to achieve higher gain. In this mode, the output of

A1 (A1OP and A1CM) drives the input of A2 via a high-pass

network (usually just a capacitor) that rejects the dc offset. The

nominal gain range is now –2 dB to +82 dB for the AD600 or

–22 dB to +62 dB for the AD602.

There are several options in connecting the gain-control inputs.

The choice depends on the desired signal-to-noise ratio (SNR)

and gain error (output ripple). The following examples feature

the AD600; the arguments generally apply to the AD602, with

appropriate changes to the gain values.

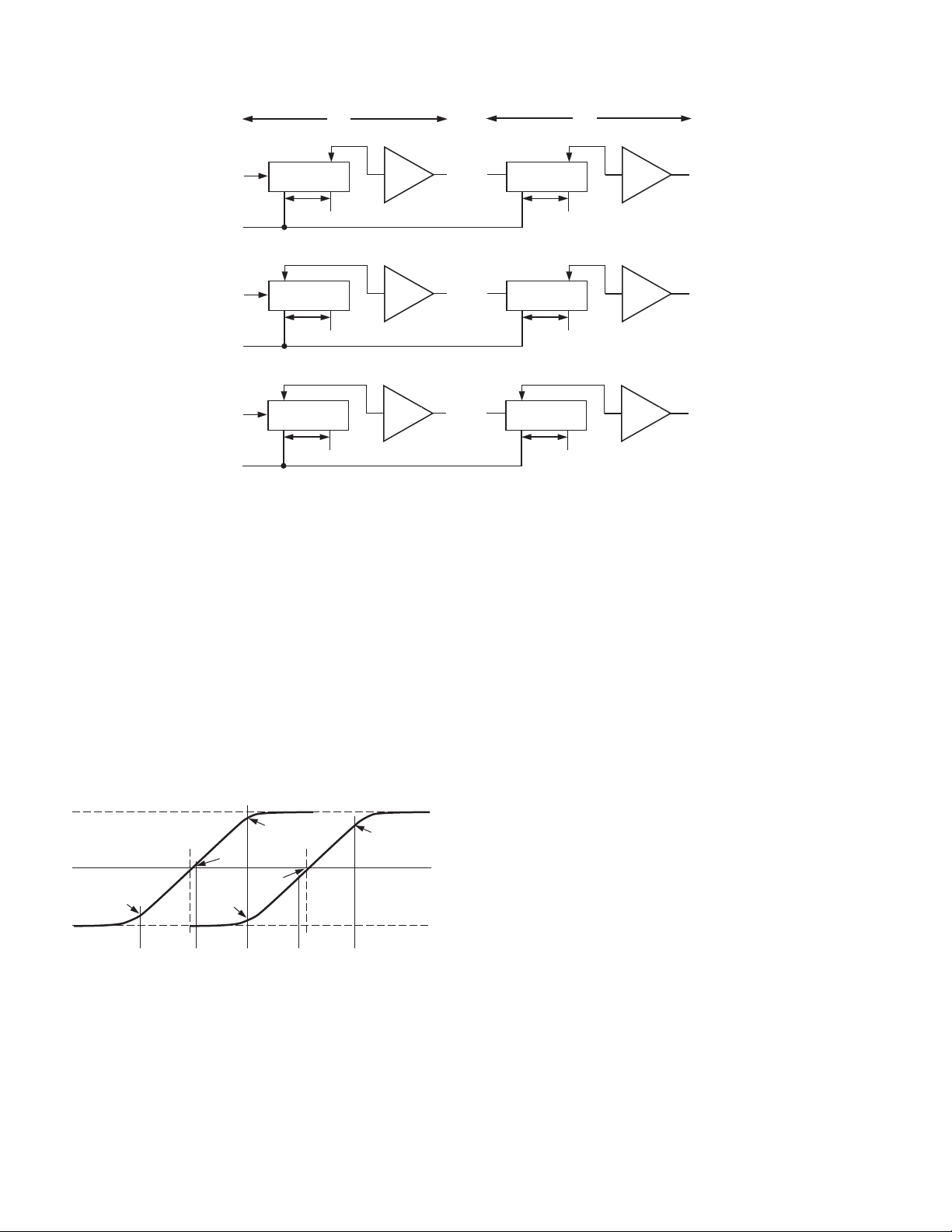

Sequential Mode (Maximum S/N Ratio)

In the sequential mode of operation, the SNR is maintained at

its highest level for as much of the gain control range possible,

as shown in Figure 2. Note here that the gain range is 0 dB to

80 dB. Figure 3 shows the general connections to accomplish

this. Both gain-control inputs, C1HI and C2HI, are driven in

parallel by a positive only, ground referenced source with a

range of 0 V to 2.5 V.

85

80

75

70

65

60

55

50

S/N RATIO – dB

45

40

35

30

–0.5

0.0

V

G

3.0

2.52.01.51.00.5

Figure 2. S/N Ratio vs. Control Voltage Sequential Control

(1 MHz Bandwidth)

An auxiliary amplifier that senses the voltage difference

between input and output commons is provided to reject

this common voltage.

REV. D

–7–

Page 8

AD600/AD602

A1

–40.00dB

–40.00dB

C1HI C1LO

V

G1

VO1 = 0.592V

–0.51dB

C1HI C1LO

V

G1

VO1 = 0.592V

0dB

C1HI C1LO

V

G1

VO1 = 0.592V

–0.51dB

0dB

41.07dB

41.07dB

41.07dB

1.07dB

(a)

40.56dB

(b)

41.07dB

(c)

= 1.25V

V

C

V

C

INPUT

0dB

= 0V

V

C

INPUT

0dB

INPUT

0dB

= 2.5V

Figure 3. AD600 Gain Control Input Calculations for Sequential Control Operation

The gains are offset (Figure 4) such that A2’s gain is increased

only after A1’s gain has reached its maximum value. Note that

for a differential input of –700 mV or less, the gain of a single

amplifier (A1 or A2) is at its minimum value of –1.07 dB; for a

differential input of +700 mV or more, the gain is at its maximum value of 41.07 dB. Control inputs beyond these limits do

not affect the gain and can be tolerated without damage or

foldover in the response. See the Specifications section of this

data sheet for more details on the allowable voltage range. The

gain is now

Gain (dB) = 32 V

where V

is the applied control voltage.

C

+41.07dB

20dB

C

A1 A2

40.56dB

*

+38.93dB

(3)

*

+1.07dB

GAIN

(dB)

0 0.625 1.25 1.875 2.5

020406080–2.14 82.14

*

Figure 4. Explanation of Offset Calibration for

Sequential Control

–0.56dB

–1.07dB

0.592 1.908

VC (V)

GAIN OFFSET OF 1.07dB, OR 33.44mV

A2

–41.07dB

–42.14dB

C2HI C2LO

V

G2

VO2 = 1.908V

–1.07dB

–41.63dB

C2HI C2LO

V

G2

V

O2

–2.14dB

C2HI C2LO

V

G2

V

O2

41.07dB

41.07dB

= 1.908V

38.93dB

41.07dB

= 1.908V

OUTPUT

0dB

OUTPUT

40dB

OUTPUT

80dB

When VC is set to zero, VG1 = –0.592 V and the gain of A1 is

1.07 dB (recall that the gain of each amplifier section is 0 dB for

= 625 mV); meanwhile, VG2 = –1.908 V, so the gain of A2

V

G

is –1.07 dB. The overall gain is thus 0 dB (see Figure 3a).

When V

sets the gain of A1 to 40.56 dB, while V

= 1.25 V, VG1 = 1.25 V – 0.592 V = 0.658 V, which

C

= 1.25 V – 1.908 V =

G2

–0.658 V, which sets A2’s gain at –0.56 dB. The overall gain is

now 40 dB (see Figure 3b). When V

= 2.5 V, the gain of A1 is

C

41.07 dB and that of A2 is 38.93 dB, resulting in an overall gain

of 80 dB (see Figure 3c). This mode of operation is further

clarified by Figure 5, which is a plot of the separate gains of A1

and A2 and the overall gain versus the control voltage. Figure 6

is a plot of the gain error of the cascaded amplifiers versus the

control voltage.

Parallel Mode (Simplest Gain-Control Interface)

In this mode, the gain-control voltage is applied to both inputs

in parallel—C1HI and C2HI are connected to the control voltage, and C1LO and C2LO are optionally connected to an offset

voltage of 0.625 V. The gain scaling is then doubled to 64 dB/V,

requiring only 1.25 V for an 80 dB change of gain. The amplitude of the gain ripple in this case is also doubled, as shown in

Figure 7, and the instantaneous signal-to-noise ratio at the

output of A2 decreases linearly as the gain is increased (Figure 8).

Low Ripple Mode (Minimum Gain Error)

As can be seen in Figures 6 and 7, the output ripple is periodic.

By offsetting the gains of A1 and A2 by half the period of the

ripple, or 3 dB, the residual gain errors of the two amplifiers

can be made to cancel. Figure 9 shows the much lower gain

ripple when configured in this manner. Figure 10 plots the

S/N ratio as a function of gain; it is very similar to that in the

Parallel Mode.

–8–

REV. D

Page 9

90

75

30

1.4

40

35

0.20.0

45

50

55

60

65

70

1.21.00.80.60.4

S/N RATIO – dB

V

C

80

70

60

50

40

30

OVERALL GAIN – dB

20

10

0

–10

–0.5

0.0

A1

COMBINED

V

C

A2

3.0

2.52.01.51.00.5

Figure 5. Plot of Separate and Overall Gains in

Sequential Control

AD600/AD602

Figure 8. SNR for Cascaded Stages–Parallel

Control

REV. D

5

4

3

2

1

0

–1

–2

–3

GAIN ERROR – dB

–4

–5

–6

–7

–8

–0.5

0.0

V

C

2.0 2.51.51.00.5

Figure 6. Gain Error for Cascaded Stages—

Sequential Control

5

4

3

2

1

0

–1

–2

GAIN ERROR – dB

–3

–4

–5

–6

–0.1

0

V

C

Figure 7. Gain Error for Cascaded Stages—

Parallel Control

1.2

1.0

0.8

0.6

0.4

0.2

0.0

–0.2

GAIN ERROR – dB

–0.4

–0.6

–0.8

–1.0

3.0

–1.2

0.0

0.1

1.3

1.21.11.00.90.70.60.50.40.30.2 0.8

V

C

Figure 9. Gain Error for Cascaded Stages—

Low Ripple Mode

80

75

70

65

60

55

S/N RATIO – dB

50

45

40

1.21.00.80.40.2 0.6

35

0.20.0

V

C

1.4

1.21.00.80.60.4

Figure 10. ISNR vs. Control Voltage—Low

Ripple Mode

–9–

Page 10

AD600/AD602

APPLICATIONS

The full potential of any high performance amplifier can only be

realized by careful attention to details in its applications. The

following pages describe fully tested circuits in which many such

details have already been considered. However, as is always true

of high accuracy, high speed analog circuits, the schematic is

only part of the story; this is no less true for the AD600 and

AD602. Appropriate choices in the overall board layout and the

type and placement of power supply decoupling components are

very important. As explained previously, the input grounds

A1LO and A2LO must use the shortest possible connections.

The following circuits show examples of time-gain control for

ultrasound and sonar, methods for increasing the output

drive, and AGC amplifiers for audio and RF/IF signal processing using both peak and rms detectors. These circuits also

illustrate methods of cascading X-AMPs for either maintaining

the optimal S/N ratio or maximizing the accuracy of the gaincontrol voltage for use in signal measurement. These AGC

circuits may be modified for use as voltage-controlled amplifiers

in sonar and ultrasound applications by removing the

detector and substituting a DAC or other voltage source for

supplying the control voltage.

Time-Gain Control (TGC) and Time-Variable Gain (TVG)

Ultrasound and sonar systems share a similar requirement: both

need to provide an exponential increase in gain in response to a

linear control voltage, that is, a gain control that is linear in

dB. Figure 11 shows the AD600/AD602 configured for a control voltage ramp starting at –625 mV and ending at +625 mV

for a gain-control range of 40 dB. The polarity of the gain-control

voltage may be reversed and the control voltage inputs C1HI and

C1LO reversed to achieve the same effect. The gain-control

voltage can be supplied by a voltage-output DAC such as the

AD7242, which contains two complete DACs, operates from ±5 V

supplies, has an internal reference of +3 V, and provides ±3 V of

output swing. As such, it is well suited for use with the AD600/

AD602, needing only a few resistors to scale the output voltage of the DACs to the levels needed by the AD600/AD602.

CONTROL VOLTAGE,

V

+625mV

0dB 40dB

G

–625mV

A1

GAIN

C1LO

A1HI

A1LO

GAT1

GAT2

A2LO

A2HI

C2LO

VOLTAGE- OUTPUT

DAC

1

2

+

3

–

4

5

–

6

7

+

8

AD600 or AD602

A1

A2

REF

V

G

C1HI

16

A1CM

15

A1OP

14

VPOS

13

VNEG

12

A2OP

11

A2CM

10

C2HI

9

+5V

–5V

Figure 11. The Simplest Application of the X-AMP Is as a

TGC or TVG Amplifier in Ultrasound or Sonar. Only the A1

connections are shown for simplicity.

Increasing Output Drive

The AD600/AD602’s output stage has limited capability for

negative-load driving capability. For driving loads less than

500 Ω, the load drive may be increased by approximately 5 mA

by connecting a 1 kΩ pull-down resistor from the output to the

negative supply (Figure 12).

Driving Capacitive Loads

For driving capacitive loads of greater than 5 pF, insert a 10 Ω

resistor between the output and the load. This lowers the possibility of oscillation.

GAIN-CONTROL

VOLTAGE

C1LO

1

V

IN

A1HI

A1LO

GAT1

GAT2

A2LO

A2HI

C2LO

2

+

–

–

+

A1

REF

A2

AD600/

3

4

5

6

7

8

C1HI

16

A1CM

15

A1OP

14

VPOS

+5V

13

VNEG

12

A2OP

11

A2CM

10

C2HI

9

1k⍀

–5V

ADDED

PULL-DOWN

RESISTOR

AD602

Figure 12. Adding a 1 kΩ Pull-Down Resistor Increases the

X-AMP’s Output Drive by About 5 mA. Only the A1 connections are shown for simplicity.

Realizing Other Gain Ranges

Larger gain ranges can be accommodated by cascading amplifiers. Combinations built by cascading two amplifiers include

–20 dB to +60 dB (using one AD602), –10 dB to +70 dB (1/2

of an AD602 followed by 1/2 of an AD600), and 0 dB to 80 dB

(one AD600). In multiple-channel applications, extra protection

against oscillation can be provided by using amplifier sections

from different packages.

An Ultralow Noise VCA

The two channels of the AD600 or AD602 can operate in

parallel to achieve a 3 dB improvement in noise level, providing

1 nV/√Hz without any loss of gain accuracy or bandwidth.

In the simplest case, as shown in Figure 13, the signal inputs

A1HI and A2HI are tied directly together. The outputs A1OP

and A2OP are summed via R1 and R2 (100 Ω each), and the

control inputs C1HI/C2HI and C1LO/C2LO operate in parallel.

Using these connections, both the input and output resistances

are 50 Ω. Thus, when driven from a 50 Ω source and terminated in a 50 Ω load, the gain is reduced by 12 dB, so the gain

range becomes –12 dB to +28 dB for the AD600 and –22 dB to

+18 dB for the AD602. The peak input capability remains unaffected (1 V rms at the IC pins, or 2 V rms from an unloaded

50 Ω source). The loading on each output, with a 50 Ω load, is

effectively 200 Ω because the load current is shared between

the two channels, so the overall amplifier still meets its specified

maximum output and distortion levels for a 200 Ω load. This ampli-

fier can deliver a maximum sine wave power of 10 dBm to the load.

–10–

REV. D

Page 11

AD600/AD602

GAIN-CONTROL

VOLTAGE

V

G

– +

C1LO

1

A1HI

2

+

A1LO

3

GAT1

V

IN

GAT2

A2LO

A2HI

C2LO

4

5

6

7

8

A1

–

REF

–

A2

+

AD600 or AD602

C1HI

16

A1CM

15

A1OP

14

VPOS

13

VNEG

12

A2OP

11

A2CM

10

C2HI

9

+5V

–5V

100

100

V

50

OUT

Figure 13. An Ultralow Noise VCA Using the AD600 or

AD602

A Low Noise, 6 dB Preamplifier

In some ultrasound applications, a high input impedance preamplifier is needed to avoid the signal attenuation that results

from loading the transducer by the 100 Ω input resistance of the

X-AMP. High gain cannot be tolerated because the peak transducer signal is typically ±0.5 V, while the peak input capability

of the AD600 or AD602 is only slightly more than ±1 V. A

gain of 2 is a suitable choice. It can be shown that if the

preamplifier’s overall referred-to-input (RTI) noise is to be

the same as that due to the X-AMP alone (1.4 nV/√Hz), the

input noise of nX2 preamplifier must be √(3/4) times as large,

that is, 1.2 nV/√Hz.

+5V

R1

49.9

R2

174

1F

R4

42.2

V

IN

R5

42.2

1F

R7

174

R8

49.9

–5V

+5V

–5V

R3

562

R6

562

1F

Q1

MRF904

INPUT

GROUND

Q2

MM4049

1F

0.1F

0.1F

100

R

OUTPUT

GROUND

OF X-AMP

IN

Figure 14. A Low Noise Preamplifier for the AD600 and

AD602

An inexpensive circuit using complementary transistor types

chosen for their low r

is shown in Figure 14. The gain is

bb

determined by the ratio of the net collector load resistance to

the net emitter resistance. It is an open-loop amplifier. The gain

will be ⫻2 (6 dB) only into a 100 Ω load, assumed to be provided by the input resistance of the X-AMP; R2 and R7 are in

shunt with this load, and their value is important in defining the

gain. For small-signal inputs, both transistors contribute an

equal transconductance that is rendered less sensitive to signal

level by the emitter resistors R4 and R5. They also play a dominant role in setting the gain.

This is a Class AB amplifier. As VIN increases in a positive

direction, Q1 conducts more heavily and its r

becomes lower

e

while Q2 increases. Conversely, increasingly negative values

result in the re of Q2 decreasing, while the re of Q1

of V

IN

increases. The design is chosen such that the net emitter

resistance is essentially independent of the instantaneous value

, resulting in moderately low distortion. Low values of

of V

IN

resistance and moderately high bias currents are important in

achieving the low noise, wide bandwidth, and low distortion of

this preamplifier. Heavy decoupling prevents noise on the power

supply lines from being conveyed to the input of the X-AMP.

Table I. Measured Preamplifier Performance

Measurement Value Unit

Gain (f = 30 MHz) 6 dB

Bandwidth (–3 dB) 250 MHz

Input Signal for

1 dB Compression 1 V p-p

Distortion

= 200 mV p-p HD2 0.27 %

V

IN

HD3 0.14 %

= 500 mV p-p HD2 0.44 %

V

IN

HD3 0.58 %

System Input Noise 1.03 nV/√Hz

Spectral Density (NSD)

(Preamp plus X-AMP)

Input Resistance 1.4 kΩ

Input Capacitance 15 pF

Input Bias Current ±150 µA

Power Supply Voltage ±5V

Quiescent Current 15 mA

A Low Noise AGC Amplifier with 80 dB Gain Range

Figure 15 provides an example of the ease with which the AD600

can be connected as an AGC amplifier. A1 and A2 are cascaded,

with 6 dB of attenuation introduced by the 100 Ω resistor R1,

while a time constant of 5 ns is formed by C1 and the 50 Ω of

net resistance at the input of A2. This has the dual effect of

(a) lowering the overall gain range from 0 dB–80 dB to 6 dB–74

dB and (b) introducing a single-pole low-pass filter with a –3 dB

frequency of about 32 MHz. This ensures stability at the maximum gain for a slight reduction in the overall bandwidth. The

capacitor C4 blocks the small dc offset voltage at the output of

A1 (which might otherwise saturate A2 at its maximum gain)

and introduces a high-pass corner at about 8 kHz, useful in

eliminating low frequency noise and spurious signals that may

be present at the input.

REV. D

–11–

Page 12

AD600/AD602

RF

INPUT

5V

R3

C1LO

A1HI

A1LO

GAT1

GAT2

A2LO

A2HI

C2LO

46.4k⍀

R4

3.74k⍀

1

2

+

3

–

4

5

–

6

7

+

8

AD600

A1

REF

A2

V

G

C1HI

16

A1CM

15

A1OP

14

VPOS

13

VNEG

12

A2OP

11

A2CM

10

C2HI

9

C4

0.1F

+5V DEC

–5V DEC

R1

100⍀

100pF

C1

1F

15pF

C2

C3

AD590

806⍀

R2

1%

5V

300A

(at 300K)

Q1

2N3904

+

V

PTAT

–

RF

OUTPUT

Figure 15. This Accurate HF AGC Amplifier Uses Just Three Active Components

+5V

FB

+5V DEC

–5V DEC

POWER SUPPLY

DECOUPLING NETWORK

0.1F

0.1F

FB

–5V

A simple half-wave detector is used, based on Q1 and R2. The

average current into capacitor C2 is just the difference between

the current provided by the AD590 (300 µA at 300 K, 27°C)

and the collector current of Q1. In turn, the control voltage V

G

is the time integral of this error current. When VG (thus the gain)

is stable, the rectified current in Q1 must, on average, exactly

balance the current in the AD590. If the output of A2 is too

small to do this, V

will ramp up, causing the gain to increase,

G

until Q1 conducts sufficiently. The operation of this control

system will now be described in detail.

First, consider the particular case where R2 is zero and the output voltage V

the corner frequency of the control loop. During the time V

is negative, Q1 conducts. When V

is a square wave at, say, 100 kHz, well above

OUT

is positive, it is cut off.

OUT

OUT

Since the average collector current is forced to be 300 µA and the

square wave has a 50% duty-cycle, the current when conducting

must be 600 µA. With R2 omitted, the peak value of V

OUT

would be just the VBE of Q1 at 600 µA (typically about 700 mV)

or 2 V

p-p. This voltage, thus the amplitude at which the output

BE

stabilizes, has a strong negative temperature coefficient (TC),

typically –1.7 mV/°C. While this may not be troublesome in

some applications, the correct value of R2 renders the output

stable with temperature.

To understand this, first note that the current in the AD590 is

closely proportional to absolute temperature (PTAT). In fact,

this IC is intended for use as a thermometer. For the moment,

assume that the signal is a square wave. When Q1 is conducting,

is the sum of VBE. V

V

OUT

is also a voltage that is PTAT and

OUT

that can be chosen to have a TC equal but opposite to the TC

of the base-to-emitter voltage. This is actually nothing more than

the band gap voltage reference principle in thinly veiled disguise.

When R2 is chosen so that the sum of the voltage across it and

of Q1 is close to the band gap voltage of about 1.2 V,

the V

BE

is stable over a wide range of temperatures, provided Q1

V

OUT

and the AD590 share the same thermal environment.

Since the average emitter current is 600 µA during each half-cycle

of the square wave, a resistor of 833 Ω would add a PTAT voltage of 500 mV at 300 K, increasing by 1.66 mV/°C. In practice,

the optimum value of R2 depends on the transistor used and, to a

lesser extent, on the waveform for which the temperature

stability is to be optimized; for the devices shown and sine wave

signals, the recommended value is 806 Ω. This resistor also

serves to lower the peak current in Q1 and the 200 Hz LP

filter it forms with C2 helps to minimize distortion due to ripple

in V

. Note that the output amplitude under sine wave condi-

G

tions is higher than for a square wave since the average value of

the current for an ideal rectifier would be 0.637 times as large,

causing the output amplitude to be 1.88 (= 1.2/0.637) V, or

1.33 V rms. In practice, the somewhat nonideal rectifier results

in the sine wave output being regulated to about 1.275 V rms.

An offset of 375 mV is applied to the inverting gain-control

inputs C1LO and C2LO. Thus the nominal –625 mV to +625 mV

range for V

is translated upwards (at VG´) to –0.25 V for mini-

G

mum gain to 1 V for maximum gain. This prevents Q1 from

going into heavy saturation at low gains and leaves sufficient

headroom of 4 V for the AD590 to operate correctly at high

gains when using a 5 V supply.

In fact, the 6 dB interstage attenuator means that the overall

gain of this AGC system actually runs from –6 dB to +74 dB.

Thus, an input of 2 V rms would be required to produce a 1 V

rms output at the minimum gain, which exceeds the 1 V rms

maximum input specification of the AD600. The available gain

range is therefore 0 dB to 74 dB (or, X1 to X5000). Since the

gain scaling is 15.625 mV/dB (because of the cascaded stages)

the minimum value of V

´ is actually increased by 6 × 15.625 mV,

G

or about 94 mV, to –156 mV, so the risk of saturation in Q1

is reduced.

The emitter circuit of Q1 is somewhat inductive (due its finite f

t

and base resistance). Consequently, the effective value of R2

increases with frequency. This would result in an increase in

the stabilized output amplitude at high frequencies, but for

the addition of C3, determined experimentally to be 15 pF for the

2N3904 for maximum response flatness. Alternatively, a faster

transistor can be used here to reduce HF peaking. Figure 16 shows

the ac response at the stabilized output level of about 1.3 V rms.

Figure 17 demonstrates the output stabilization for sine wave

inputs of 1 mV to 1 V rms at frequencies of 100 kHz, 1 MHz,

and 10 MHz.

–12–

REV. D

Page 13

3dB

AGC OUTPUT CHANGE – dB

0.1

1

FREQUENCY – MHz

10

100

Figure 16. AC Response at the Stabilized Output Level

of 1.3 V RMS

+0.2

0

–0.2

–0.4

RELATIVE OUTPUT – dB

0.001 0.01 10.1

INPUT AMPLITUDE – V RMS

100kHz

1MHz

10MHz

Figure 17. Output Stabilization vs. RMS Input for

Sine Wave Inputs at 100 kHz, 1 MHz, and 10 MHz

While the band gap principle used here sets the output amplitude to 1.2 V (for the square wave case), the stabilization point

can be set to any higher amplitude, up to the maximum output

– 2) V that the AD600 can support. It is only necessary

of ±(V

S

to split R2 into two components of appropriate ratio whose

parallel sum remains close to the zero-TC value of 806 Ω. This

is illustrated in Figure 18, which shows how the output can be

raised without altering the temperature stability.

5V

R2A

300A

(at 300K)

Q1

2N3904

R2B

+

R2 = R2A R2B ≈ 806

V

PTAT

–

RF

OUTPUT

TO AD600 PIN 16

TO AD600 PIN 11

1F

15pF

AD590

C2

C3

Figure 18. Modification in Detector to Raise Output to

2 V RMS

AD600/AD602

A Wide Range, RMS-Linear dB Measurement System (2 MHz AGC Amplifier with RMS Detector)

Monolithic rms-dc converters provide an inexpensive means to

measure the rms value of a signal of arbitrary waveform; they

also may provide a low accuracy logarithmic (decibel-scaled)

output. However, they have certain shortcomings. The first of

these is their restricted dynamic range, typically only 50 dB.

More troublesome is that the bandwidth is roughly proportional

to the signal level; for example, the AD636 provides a 3 dB

bandwidth of 900 kHz for an input of 100 mV rms, but has

a bandwidth of only 100 kHz for a 10 mV rms input. Its logarithmic output is unbuffered, uncalibrated, and not stable

over temperature. Considerable support circuitry, including at

least two adjustments and a special high TC resistor, is required

to provide a useful output.

All of these problems can be eliminated using an AD636 as

the detector element in an AGC loop, in which the difference

between the rms output of the amplifier and a fixed dc reference are nulled in a loop integrator. The dynamic range and

the accuracy with which the signal can be determined are now

entirely dependent on the amplifier used in the AGC system. Since

the input to the rms-dc converter is forced to a constant amplitude, close to its maximum input capability, the bandwidth is no

longer signal dependent. If the amplifier has an exactly exponential (linear-dB) gain-control law, its control voltage V

by the AGC loop to be have the general form:

V

IN RMS

VV

= log

OUT SCALE

10

()

V

REF

Figure 19 shows a practical wide dynamic range rms-responding

measurement system using the AD600. Note that the signal

output of this system is available at A2OP, and the circuit can

be used as a wideband AGC amplifier with an rms-responding

detector. This circuit can handle inputs from 100 µV to 1 V rms

with a constant measurement bandwidth of 20 Hz to 2 MHz,

limited primarily by the AD636 rms converter. Its logarithmic

output is a loadable voltage accurately calibrated to 100 mV/dB,

or 2 V per decade, which simplifies the interpretation of the

reading when using a DVM and is arranged to be –4 V for an

input of 100 µV rms input, zero for 10 mV, and +4 V for a

1 V rms input. In terms of Equation 4, V

is 2 V.

V

SCALE

is 10 mV and

REF

Note that the peak log output of ±4 V requires the use of

±6 V supplies for the dual op amp U3 (AD712) although lower

supplies would suffice for the AD600 and AD636. If only ±5 V

supplies are available, it is necessary to either use a reduced value

for V

(say 1 V, in which case the peak output would be only

SCALE

±2 V) or restrict the dynamic range of the signal to about 60 dB.

As in the previous case, the two amplifiers of the AD600 are

used in cascade. However, the 6 dB attenuator and low-pass

filter found in Figure 1 are replaced by a unity gain buffer

amplifier U3A, whose 4 MHz bandwidth eliminates the risk of

instability at the highest gains. The buffer also allows the use of

a high impedance coupling network (C1/R3) that introduces a

high-pass corner at about 12 Hz. An input attenuator of 10 dB

(X0.316) is now provided by R1 + R2 operating in conjunction

with the AD600’s input resistance of 100 Ω. The adjustment

provides exact calibration of the logarithmic intercept V

critical applications, but R1 and R2 may be replaced by a fixed

resistor of 215 Ω if very close calibration is not needed, since the

is forced

G

in

REF

(4)

REV. D

–13–

Page 14

AD600/AD602

INPUT

1V RMS

MAX

(SINE WAVE)

R1

115⍀

U3A

1/2

AD712

15.625mV/dB

Figure 19. The Output of This Three-IC Circuit Is Proportional to the Decibel Value of the RMS Input

CAL

0dB

R2 200⍀

R3

133k⍀

V

G

C1LO

A1HI

A1LO

GAT1

GAT2

A2LO

A2HI

C2LO

R4

3.01k⍀

1

2

3

4

5

6

7

8

0.1F

+

–

–

+

U1 AD600

R5

16.2k⍀

V

RMS

C2

2F

–6V

DEC

AF/RF

OUTPUT

NC

NC

NC

C4

4.7F

1

2

3

4

5

6

7

NC = NO CONNECT

VINP

VNEG

CAVG

VLOG

BFOP

BFIN

U2

AD636

COMM

VPOS

LDLO

V

RMS

14

13

12

11

10

9

8

1/2

AD712

NC

NC

NC

R7

56.2k⍀

R6

3.16k⍀

+316.2mV

U3B

C3

1F

+100mV/dB

0V = 0dB(AT 10mV RMS)

+6V DEC

DEC

DEC

V

+6V

–6V

+6V

FB

0.1F

0.1F

FB

–6V

POWER SUPPLY

DECOUPLING

NETWORK

OUT

C1

C1HI

16

A1CM

15

A1

REF

A2

A1OP

14

VPOS

VNEG

A2OP

A2CM

C2HI

+6V

DEC

–6V

DEC

13

12

11

10

9

input resistance of the AD600 (and all other key parameters of it

and the AD636) are already laser trimmed for accurate operation.

This attenuator allows inputs as large as ±4 V to be accepted,

that is, signals with an rms value of 1 V combined with a crest

factor of up to 4.

The output of A2 is ac coupled via another 12 Hz high-pass filter

formed by C2 and the 6.7 kΩ input resistance of the AD636.

The averaging time constant for the rms-dc converter is determined by C4. The unbuffered output of the AD636 (at Pin 8) is

compared with a fixed voltage of 316 mV set by the positive

supply voltage of 6 V and resistors R6 and R7. V

is propor-

REF

tional to this voltage, and systems requiring greater calibration

accuracy should replace the supply dependent reference with a

more stable source.

Any difference in these voltages is integrated by the op amp U3B,

with a time constant of 3 ms formed by the parallel sum of R6/R7

and C3. Now, if the output of the AD600 is too high, V rms will

be greater than the setpoint of 316 mV, causing the output of

U3B—that is, V

noninverting). A fraction of V

—to ramp up (note that the integrator is

OUT

is connected to the inverting

OUT

gain-control inputs of the AD600, so causing the gain to be

reduced, as required, until V rms is exactly equal to 316 mV, at

which time the ac voltage at the output of A2 is forced to be

exactly 316 mV rms. This fraction is set by R4 and R5 such

that a 15.625 mV change in the control voltages of A1 and

A2—which would change the gain of the cascaded amplifiers by

1 dB—requires a change of 100 mV at V

. Notice here that

OUT

since A2 is forced to operate at an output level well below its

capacity, waveforms of high crest factor can be tolerated throughout the amplifier.

To check the operation, assume an input of 10 mV rms is

applied to the input, which results in a voltage of 3.16 mV rms

at the input to A1, due to the 10 dB loss in the attenuator. If

the system operates as claimed, V

(and hence VG) should

OUT

be zero. This being the case, the gain of both A1 and A2 is

20 dB and the output of the AD600 is therefore 100 times

(40 dB) greater than its input, which evaluates to 316 mV rms,

the input required at the AD636 to balance the loop. Finally,

note that unlike most AGC circuits that need strong temperature

compensation for the internal kT/q scaling, these voltages,

and thus the output of this measurement system, are temperature stable, arising directly from the fundamental and exact

exponential attenuation of the ladder networks in the AD600.

Typical results are presented for a sine wave input at 100 kHz.

Figure 20 shows that the output is held very close to the setpoint of 316 mV rms over an input range in excess of 80 dB.

450

425

400

375

350

325

– mV

300

OUT

275

V

250

225

200

175

150

10 100 101100m10m1m

INPUT SIGNAL – V RMS

Figure 20. The RMS Output of A2 Is Held Close to the

Setpoint 316 mV for an Input Range of Over 80 dB

This system can, of course, be used as an AGC amplifier in

which the rms value of the input is leveled. Figure 21 shows

the decibel output voltage. More revealing is Figure 22, which

shows that the deviation from the ideal output predicted by

Equation 1 over the input range 80 µV to 500 mV rms is within

±0.5 dB, and within ±1 dB for the 80 dB range from 80 µV to

800 mV. By suitable choice of the input attenuator R1 + R2,

this could be centered to cover any range from 25 mV – 250 mV

to, say, 1 mV – 10 V, with appropriate correction to the value of

. Note that V

V

REF

is not affected by the changes in the

SCALE

range. The gain ripple of ±0.2 dB seen in this curve is the result of

–14–

REV. D

Page 15

AD600/AD602

the finite interpolation error of the X-AMP. Note that it occurs

with a periodicity of 12 dB—twice the separation between the

tap points (because of the two cascaded stages).

5

4

3

2

1

– V

0

OUT

V

–1

–2

–3

–4

–5

10 100 101100m10m1m

INPUT SIGNAL – V RMS

Figure 21. The dB Output of Figure 19’s Circuit Is Linear

over an 80 dB Range

2.5

2.0

1.5

1.0

0.5

0

–0.5

–1.0

OUTPUT ERROR – dB

–1.5

–2.0

–2.5

10 100 101100m10m1m

INPUT SIGNAL – V RMS

Figure 22. Data from Figure 20 Presented as the Deviation

from the Ideal Output Given in Equation 4

This ripple can be canceled whenever the X-AMP stages are

cascaded by introducing a 3 dB offset between the two pairs

of control voltages. A simple means to achieve this is shown

in Figure 23: the voltages at C1HI and C2HI are split by

±46.875 mV, or ±1.5 dB. Alternatively, either one of these pins

can be individually offset by 3 dB and a 1.5 dB gain adjustment

made at the input attenuator (R1 + R2).

C1HI

U1

AD600

NC = NO CONNECT

16

15

14

13

12

11

10

9

–6V

DEC

A1CM

A1OP

VPOS

VNEG

A2OP

A2CM

C2HI

10k⍀

+6V DEC

–6V DEC

–46.875mV

78.7⍀ 78.7⍀

–6V DEC

C2

2F

+46.875mV

+6V

DEC

10k⍀

3dB OFFSET

MODIFICATION

NC

NC

NC

1

2

3

4

5

6

7

VINP

VNEG

CAVG

VLOG

BFOP

BFIN

U2

AD636

Figure 23. Reducing the Gain Error Ripple

The error curve shown in Figure 24 demonstrates that over the

central portion of the range the output voltage can be maintained

very close to the ideal value. The penalty for this modification is

the higher errors at the extremities of the range. The next two

applications show how three amplifier sections can be cascaded

to extend the nominal conversion range to 120 dB, with the

inclusion of simple LP filters of the type shown in Figure 15.

Very low errors can then be maintained over a 100 dB range.

2.5

2.0

1.5

1.0

0.5

0

–0.5

–1.0

OUTPUT ERROR – dB

–1.5

–2.0

–2.5

10 100 101100m10m1m

INPUT SIGNAL – V RMS

Figure 24. Using the 3 dB Offset Network, the Ripple

Is Reduced

100 dB to 120 dB RMS Responding Constant Bandwidth AGC Systems with High Accuracy dB Outputs

The next two applications double as both AGC amplifiers and

measurement systems. In both, precise gain offsets are used to

achieve either (1) a very high gain linearity of ±0.1 dB over

the full 100 dB range or (2) the optimal signal-to-noise ratio

at any gain.

REV. D

–15–

Page 16

AD600/AD602

INPUT

1V RMS

MAX

(SINE WAVE)

R13

3.01k⍀

C1LO

A1HI

A1LO

GAT1

GAT2

A2LO

A2HI

C2LO

1

2

+

3

–

4

5

–

6

7

+

8

U1 AD600

+5V

FB

+5V

DEC

–5V

DEC

FB

–5V

POWER SUPPLY

DECOUPLING

NETWORK

Q1

2N3906

11.3k⍀

A1

A2

0.1F

0.1F

R14

301k⍀

R12

REF

16

15

14

13

12

11

10

9

+5V DEC

C1HI

A1CM

A1OP

VPOS

VNEG

A2OP

A2CM

C2HI

–5V

10k⍀

R15

19.6k⍀

R16

6.65k⍀

+5V

DEC

–5V

DEC

R6

C1

0.1F

R1

133k⍀

C2

0.1F

R4

133k⍀

–2dB

–62.5mV

R7

127⍀

U3A

1/4

AD713

R5

1.58k⍀

C3

220pF

0dB

R8

127⍀R910k⍀

R2

487⍀

U3B

+2dB

+62.5mV

NC

–5V

DEC

NC

NC

R3

200⍀

1/4

AD713

+5V

1

2

3

4

5

6

7

VINP

VNEG

CAVG

VLOG

BFOP

BFIN

C5

22F

U4

AD636

COMM

C1LO

A1HI

A1LO

GAT1

GAT2

A2LO

A2HI

C2LO

VPOS

LDLO

V

RMS

1

2

+

3

–

4

5

–

6

7

+

8

14

NC

13

12

NC

11

NC

10

9

8

A1

REF

A2

U2 AD600

R10

3.16k⍀

+316.2mV

NC = NO CONNECT

16

15

14

13

12

11

10

9

R11

46.4k⍀

C6

4.7F

U3C

AD713

C1HI

A1CM

A1OP

VPOS

VNEG

A2OP

A2CM

C2HI

+5V DEC

1/4

C4

2F

+5V

DEC

–5V

DEC

V

OUT

V

LOG

Figure 25. RMS Responding AGC Circuit with 100 dB Dynamic Range

A 100 dB RMS/AGC System with Minimal Gain Error (Parallel Gain with Offset)

Figure 25 shows an rms-responding AGC circuit that can be

used equally well as an accurate measurement system. It

accepts inputs of 10 µV to 1 V rms (–100 dBV to 0 dBV) with

generous overrange. Figure 26 shows the logarithmic output, V

LOG

,

which is accurately scaled 1 V per decade, that is 50 mV/dB, with

an intercept (V

= 0) at 3.16 mV rms (–50 dBV). Gain offsets

LOG

of ±2 dB have been introduced between the amplifiers, provided

by the ±62.5 mV introduced by R6–R9. These offsets cancel a

small gain ripple that arises in the X-AMP from its finite interpolation error, which has a period of 18 dB in the individual VCA

sections. The gain ripple of all three amplifier sections without

this offset (in which case the gain errors simply add) is shown in

Figure 27; it is still a remarkably low ±0.25 dB over the 108 dB

range from 6 µV to 1.5 V rms. However, with the gain offsets

connected, the gain linearity remains under ±0.1 dB over the

specified 100 dB range (Figure 28).

5

4

3

2

1

0

–1

–2

LOGARITHMIC OUTPUT – V

–3

–4

–5

1 10 101100m10m1m100

INPUT SIGNAL – V RMS

Figure 26. V

Plotted vs. VIN for Figure 25‘s Circuit

LOG

Showing 120 dB AGC Range

–16–

REV. D

Page 17

AD600/AD602

2.0

1.5

1.0

0.5

0.1

0

–0.1

–0.5

GAIN ERROR – dB

–1.0

–1.5

–2.0

1 10 101100m10m1m100

INPUT SIGNAL – V RMS

Figure 27. Gain Error for Figure 19 without the 2 dB

Offset Modification

2.0

1.5

1.0

0.5

0.1

0

–0.1

–0.5

GAIN ERROR – dB

–1.0

–1.5

–2.0

1 10 101100m10m1m100

INPUT SIGNAL – V RMS

Figure 28. Adding the 2 dB Offsets Improves the

Linearization

The maximum gain of this circuit is 120 dB. If no filtering were

used, the noise spectral density of the AD600 (1.4 nV/√Hz)

would amount to an input noise of 8.28 µV rms in the full band-

width (35 MHz). At a gain of one million, the output noise

would dominate. Consequently, some reduction of bandwidth is

mandatory, and in the circuit of Figure 25 it is due mostly to

a single-pole low-pass filter R5/C3, which provides a –3 dB

frequency of 458 kHz, which reduces the worst-case output noise

(at V

) to about 100 mV rms at a gain of 100 dB. Of course,

AGC

the bandwidth (and therefore the output noise) could be further

reduced, for example, in audio applications, merely by increasing C3. The value chosen for this application is optimal in

minimizing the error in the V

output for small input signals.

LOG

The AD600 is dc-coupled, but even miniscule offset voltages at

the input would overload the output at high gains; thus high-pass

filtering is also needed. To provide operation at low frequencies,

two simple zeros at about 12 Hz are provided by R1/C1 and

R4/C2; op amp sections U3A and U3B (AD713) are used to

provide impedance buffering, since the input resistance of the

AD600 is only 100 Ω. A further zero at 12 Hz is provided by C4

and the 6.7 kΩ input resistance of the AD636 rms converter.

The rms value of V

is generated at Pin 8 of the AD636; the

LOG

averaging time for this process is determined by C5, and the

value shown results in less than 1% rms error at 20 Hz. The

slowly varying V rms is compared with a fixed reference of

316 mV, derived from the positive supply by R10/R11. Any

difference between these two voltages is integrated in C6, in

conjunction with op amp U3C, the output of which is V

LOG

. A

fraction of this voltage, determined by R12 and R13, is returned

to the gain control inputs of all AD600 sections. An increase in

lowers the gain because this voltage is connected to the

V

LOG

inverting polarity control inputs.

In this case, the gains of all three VCA sections are being varied

simultaneously, so the scaling is not 32 dB/V but 96 dB/V, or

10.42 mV/dB. The fraction of V

required to set its scaling to

LOG

50 mV/dB is therefore 10.42/50, or 0.208. The resulting fullscale range of V

is nominally ±2.5 V. This scaling allows the

LOG

circuit to operate from ±5 V supplies. Optionally, the scaling

can be altered to 100 mV/dB, which would be more easily

interpreted when V

is displayed on a DVM by increasing

LOG

R12 to 25.5 kΩ. The full-scale output of ±5 V then requires the

use of supply voltages of at least ±7.5 V.

A simple attenuator of 16.6 ±1.25 dB is formed by R2/R3 and

the 100 Ω input resistance of the AD600. This allows the reference level of the decibel output to be precisely set to zero for an

input of 3.16 mV rms, and thus center the 100 dB range between

10 µV and 1 V. In many applications R2/R3 may be replaced

by a fixed resistor of 590 Ω. For example, in AGC applications, neither the slope nor the intercept of the logarithmic output

is important.

A few additional components (R14–R16 and Q1) improve the

accuracy of V

at the top end of the signal range (that is, for

LOG

small gains). The gain starts rolling off when the input to the

first amplifier, U1A, reaches 0 dB. To compensate for this nonlinearity, Q1 turns on at V

~ 1.5 V and increases the feedback

LOG

to the control inputs of the AD600s, thereby needing a smaller

voltage at V

to maintain the input to the AD636 to the set-

LOG

point of 316 mV rms.

A 120 dB RMS/AGC System with Optimal S/N Ratio (Sequential Gain)

In the last case, all gains were adjusted simultaneously, resulting

in an output signal-to-noise ratio (S/N ratio) that is always less

than optimal. The use of sequential gain control results in a

major improvement in S/N ratio, with only a slight penalty in

the accuracy of V

of V

. The idea is to increase the gain of the earlier stages

AGC

, and no penalty in the stabilization accuracy

LOG

first (as the signal level decreases) and maintain the highest S/N

ratio throughout the amplifier chain. This can be easily

achieved with the AD600 because its gain is accurate even when

the control input is overdriven. That is, each gain control

window of 1.25 V is used fully before moving to the next

amplifier to the right.