Page 1

120 mA, Current Sinking,

V

www.BDTIC.com/ADI

FEATURES

120 mA current sink

Available in 3 × 3 array WLCSP package

2-wire (I

10-bit resolution

Integrated current sense resistor

2.7 V to 5.5 V power supply

Guaranteed monotonic over all codes

Power-down to 0.5 μA typical

Internal reference

Ultralow noise preamplifier

Power-down function

Power-on reset

CONSUMER APPLICATIONS

Lens autofocus

Image stabilization

Optical zoom

Shutters

Iris/exposure

Neutral density (ND) filters

Lens covers

Camera phones

Digital still cameras

Camera modules

Digital video cameras/camcorders

Camera-enabled devices

Security cameras

Web/PC cameras

2

C-compatible) 1.8 V serial interface

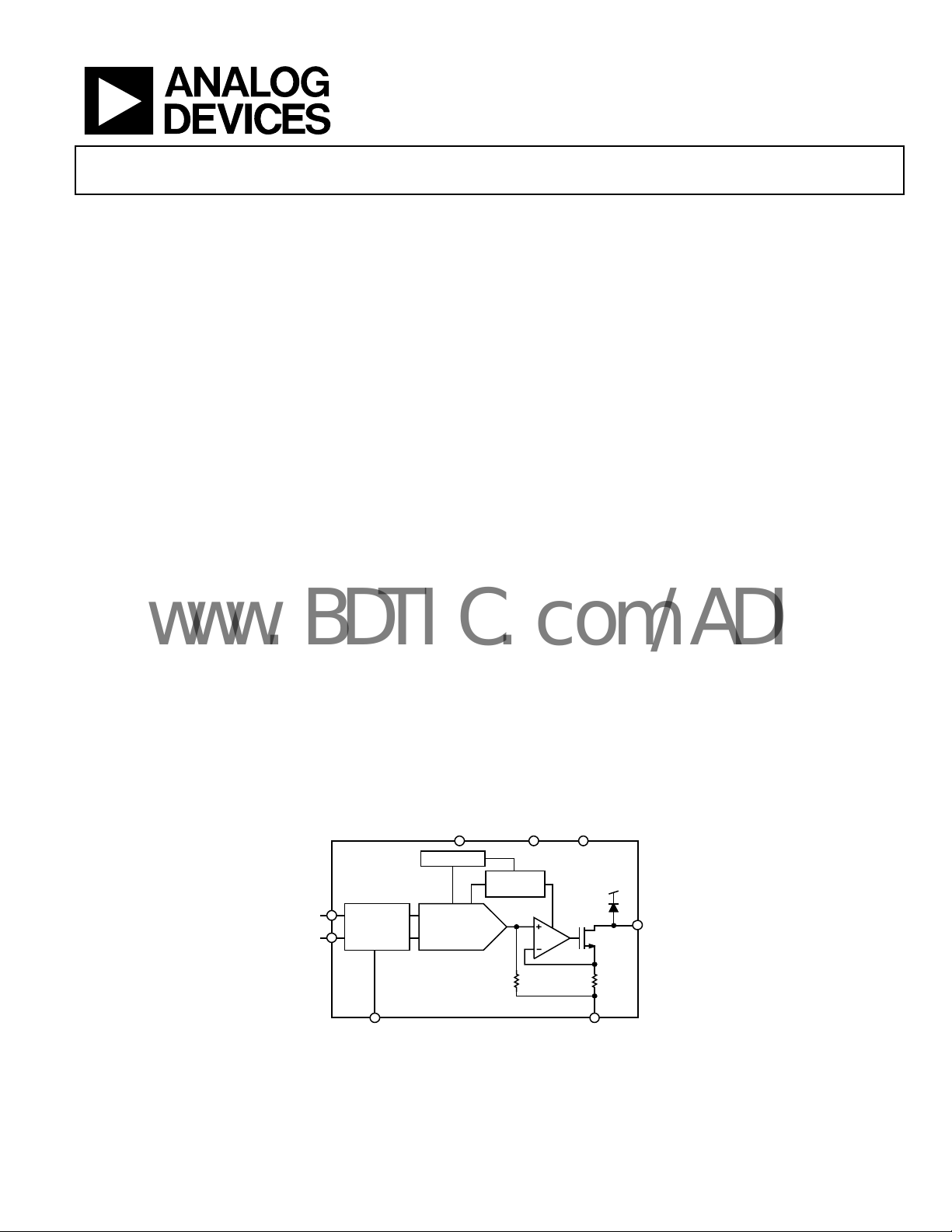

FUNCTIONAL BLOCK DIAGRAM

XSHUTDOWN

10-Bit, I2C® DAC

AD5821

INDUSTRIAL APPLICATIONS

Heater controls

Fan controls

Cooler (Peltier) controls

Solenoid controls

Valve controls

Linear actuator controls

Light controls

Current loop controls

GENERAL DESCRIPTION

The AD5821 is a single 10-bit digital-to-analog converter with

120 mA output current sink capability. It features an internal

reference and operates from a single 2.7 V to 5.5 V supply.

The DAC is controlled via a 2-wire (I

interface that operates at clock rates up to 400 kHz.

The AD5821 incorporates a power-on reset circuit that ensures

th

at the DAC output powers up to 0 V and remains there until

a valid write takes place. It has a power-down feature that reduces

the current consumption of the device to 1 µA maximum.

The AD5821 is designed for autofocus, image stabilization, and

o

ptical zoom applications in camera phones, digital still cameras,

and camcorders.

The AD5821 also has many industrial applications, such as

ntrolling temperature, light, and movement, over the range of

co

−40°C to +85°C without derating.

2

C address for the AD5821 is 0x18.

The I

DGND

DD

2

C-compatible) serial

REFERENCE

POWER-ON

RESET

SDA

SCL

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

I2C SERIAL

INTERFACE

DGND

10-BIT

CURRENT

OUTPUT DAC

AD5821

R

Figure 1.

R

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

SENSE

3.3Ω

D1

AGND

V

DD

I

SINK

05950-001

Page 2

AD5821

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Consumer Applications ................................................................... 1

Industrial Applications .................................................................... 1

General Description......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

AC Specifications.......................................................................... 4

Timing Specifications .................................................................. 4

Absolute Maximum Ratings............................................................ 5

Pin Configuration and Function Descriptions............................. 6

REVISION HISTORY

1/07—Revision 0: Initial Version

Typical Perf or m an c e Charac t e r istics ..............................................7

Te r mi n ol o g y .................................................................................... 10

Theory of Operation ...................................................................... 11

Serial Interface............................................................................ 11

2

I

C Bus Operation ...................................................................... 11

Data Format ................................................................................ 11

Power Supply Bypassing and Grounding................................ 12

Applications Information.............................................................. 14

Outline Dimensions ....................................................................... 15

Ordering Guide .......................................................................... 15

Rev. 0 | Page 2 of 16

Page 3

AD5821

www.BDTIC.com/ADI

SPECIFICATIONS

VDD = 2.7 V to 5.5 V, AGND = DGND = 0 V, load resistance RL = 25 Ω connected to VDD; all specifications T

unless otherwise noted.

MIN

to T

MAX

,

Table 1.

B Version

1

Parameter Min Typ Max Unit Test Conditions/Comments

DC PERFORMANCE

= 3.6 V to 4.5 V; device operates over 2.7 V to 5.5 V

V

DD

with reduced performance

Resolution 10 Bits 117 μA/LSB

Relative Accuracy

Differential Nonlinearity

Zero-Code Error

Offset Error @ Code 16

Gain Error

Offset Error Drift

Gain Error Drift

2

2, 3

2, 4

2

2

4, 5

2, 5

±1.5 ±4 LSB

±1 LSB Guaranteed monotonic over all codes

0 1 5 mA All 0s loaded to DAC

0.5 mA

±0.6 % of FSR @ 25°C

10 μA/°C

±0.2 ±0.5 LSB/°C

OUTPUT CHARACTERISTICS

Minimum Sink Current

4

3 mA

Maximum Sink Current 120 mA

Output Current During XSHUTDOWN 80 nA XSHUTDOWN = 0

Output Compliance

Output Compliance

5

5

0.6 V

0.48 V

DD

DD

V

V

Output voltage range over which maximum 120 mA

rent is available

sink cur

Output voltage range over which 90 mA sink current

vailable

is a

Power-Up Time 20 μs To 10% of FS, coming out of power-down mode; VDD = 5 V

LOGIC INPUTS (XSHUTDOWN)

5

Input Current ±1 μA

Input Low Voltage, V

Input High Voltage, V

INL

INH

0.54 V VDD = 2.7 V to 5.5 V

1.3 V VDD = 2.7 V to 5.5 V

Pin Capacitance 3 pF

LOGIC INPUTS (SCL, SDA)

Input Low Voltage, V

Input High Voltage, V

Input Low Voltage, V

Input High Voltage, V

Input Leakage Current, I

Input Hysteresis, V

Digital Input Capacitance, C

Glitch Rejection

5

INL

INH

INL

INH

IN

HYST

IN

6

−0.3 +0.54 V VDD = 2.7 V to 3.6 V

1.26 VDD + 0.3 V VDD = 2.7 V to 3.6 V

−0.3 +0.54 V VDD = 3.6 V to 5.5 V

1.4 VDD + 0.3 V VDD = 3.6 V to 5.5 V

±1 μA VIN = 0 V to V

DD

0.05 VDD V

6 pF

50 ns Pulse width of spike suppressed

POWER REQUIREMENTS

V

DD

2.7 5.5 V

IDD (Normal Mode) IDD specification is valid for all DAC codes

VDD = 2.7 V to 3.6 V 2.5 4 mA V

IDD (Power-Down Mode)

1

Temperature range is as follows: B Version = −30°C to +85°C.

2

See the section. Terminology

3

Linearity is tested using a reduced code range: Code 32 to Code 1023.

4

To achieve near zero output current, use the power-down feature.

5

Guaranteed by design and characterization; not production tested. XSHUTDOWN is active low. SDA and SCL pull-up resistors are tied to 1.8 V.

6

Input filtering on both the SCL and the SDA inputs suppresses noise spikes that are less than 50 ns.

7

XSHUTDOWN is active low.

7

0.5 μA V

= 1.8 V, V

INH

= 1.8 V, V

INH

= GND, VDD = 3.6 V

INL

= GND

INL

Rev. 0 | Page 3 of 16

Page 4

AD5821

S

www.BDTIC.com/ADI

AC SPECIFICATIONS

VDD = 2.7 V to 5.5 V, AGND = DGND = 0 V, load resistance RL = 25 Ω connected to VDD, unless otherwise noted.

Table 2.

B Version

1, 2

Parameter Min Typ Max Unit Test Conditions/Comments

Output Current Settling Time 250 μs VDD = 3.6 V, RL = 25 Ω, LL = 680 μH, ¼ scale to ¾ scale change (0x100 to 0x300)

Slew Rate 0.3 mA/μs

Major Code Change Glitch Impulse 0.15 nA-s 1 LSB change around major carry

Digital Feedthrough

1

Temperature range is as follows: B Version = −40°C to +85°C.

2

Guaranteed by design and characterization; not production tested.

3

See the section. Terminology

3

0.06 nA-s

TIMING SPECIFICATIONS

VDD = 2.7 V to 3.6 V. All specifications T

Table 3.

B Version

Parameter

f

SCL

t

1

t

2

t

3

t

4

t

5

2

t

6

1

Limit at T

MIN

, T

MAX

400 kHz max SCL clock frequency

2.5 μs min SCL cycle time

0.6 μs min t

1.3 μs min t

0.6 μs min t

100 ns min t

0.9 μs max t

0 μs min

t

7

t

8

t

9

t

10

0.6 μs min t

0.6 μs min t

1.3 μs min t

300 ns max tR, rise time of both SCL and SDA when receiving

0 ns min May be CMOS driven

t

11

250 ns max tF, fall time of SDA when receiving

300 ns max tF, fall time of both SCL and SDA when transmitting

20 + 0.1 C

C

B

1

Guaranteed by design and characterization; not production tested.

2

A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the VINH MIN of the SCL signal) to bridge the undefined region of the SCL falling edge.

3

C

is the total capacitance of one bus line in pF. t

B

400 pF max Capacitive load for each bus line

3

B

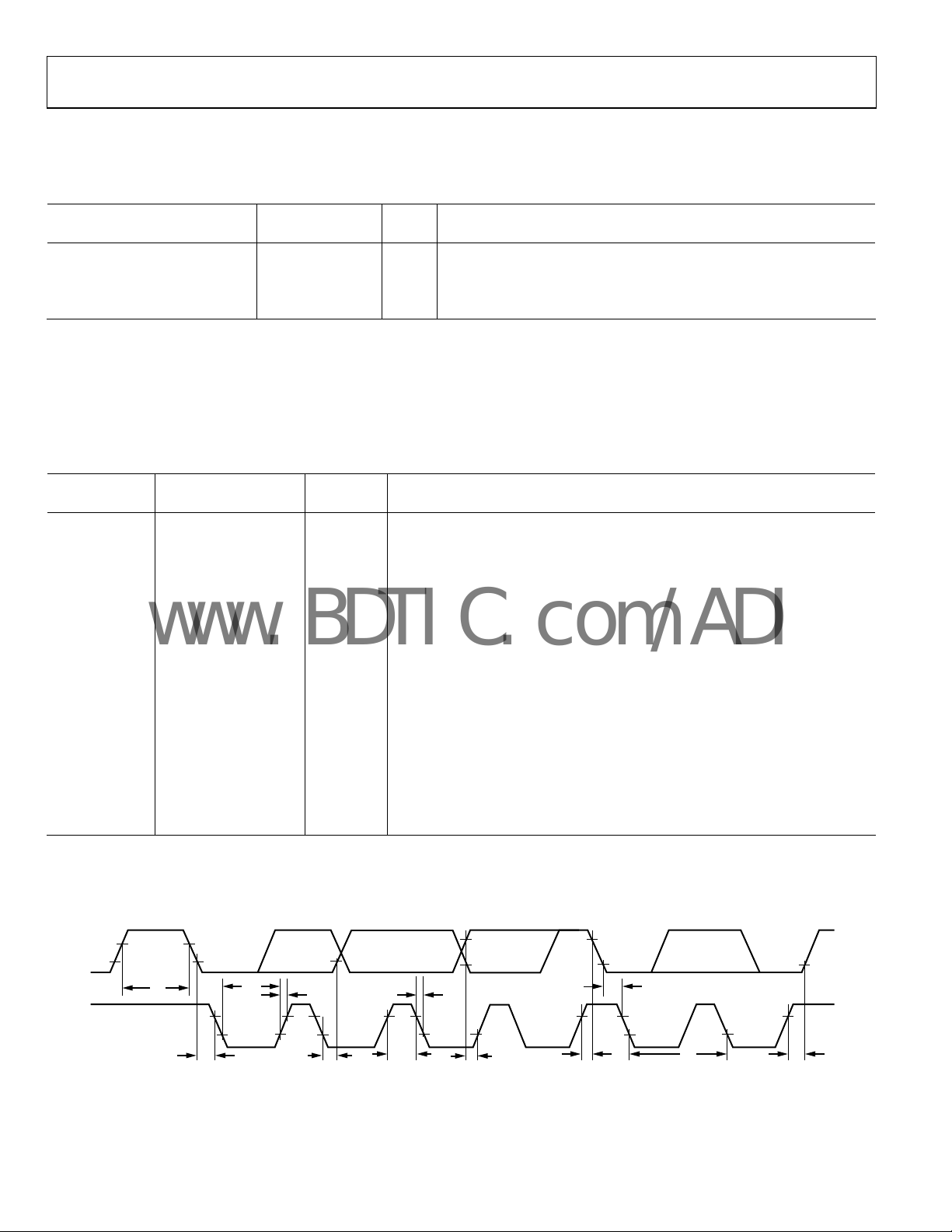

Timing Diagram

MIN

to T

, unless otherwise noted.

MAX

Unit Description

, SCL high time

HIGH

, SCL low time

LOW

, start/repeated start condition hold time

HD, STA

, data setup time

SU, DAT

, data hold time

HD, DAT

, setup time for repeated start

SU, STA

, stop condition setup time

SU, STO

, bus free time between a stop condition and a start condition

BUF

ns min

and tF are measured between 0.3 VDD and 0.7 VDD.

R

DA

SCL

t

9

t

4

START

CONDITIO N

t

3

t

10

t

6

t

t

11

2

t

5

REPEATED

CONDITION

t

7

START

t

4

Figure 2. 2-Wire Serial Interface Timing Diagram

Rev. 0 | Page 4 of 16

t

1

t

8

STOP

CONDITIO N

05950-002

Page 5

AD5821

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 4.

Parameter Rating

VDD to AGND –0.3 V to +5.5 V

VDD to DGND –0.3 V to VDD + 0.3 V

AGND to DGND –0.3 V to +0.3 V

SCL, SDA to DGND –0.3 V to VDD + 0.3 V

XSHUTDOWN to DGND –0.3 V to VDD + 0.3 V

I

to AGND –0.3 V to VDD + 0.3 V

SINK

Operating Temperature Range

Industrial (B Version) −30°C to +85°C

Storage Temperature Range −65°C to +150°C

Junction Temperature (TJ

WLFCSP Power Dissipation (TJ

θJA Thermal Impedance

Mounted on 4-Layer Board 95°C/W

Lead Temperature, Soldering

Maximum Peak Reflow Temperature2260°C (±5°C)

1

To achieve the optimum θJA, it is recommended that the AD5821

be soldered on a 4-layer board.

2

As per JEDEC J-STD-020C.

) 150°C

MAX

1

− TA)/θ

MAX

JA

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 5 of 16

Page 6

AD5821

m

www.BDTIC.com/ADI

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

3

12

A

B

C

VIEW FROM BALL SIDE

Figure 3. 9-Ball WLCSP Pin Configuration

05950-021

Table 5. 9-Ball WLCSP Pin Function Description

Ball Number Mnemonic Description

A1 I

Output Current Sink.

SINK

A2 NC No Connection.

A3 XSHUTDOWN Power-Down. Asynchronous power-down signal, active low.

B1 AGND Analog Ground Pin.

B2 DGND Digital Ground Pin.

B3 SDA I2C Interface Signal.

C1 DGND Digital Ground Pin.

C2 VDD Digital Supply Voltage.

C3 SCL I2C Interface Signal.

1515µm

NC

XSHUTDOWN

DGND

1

2

I

SINK

8

AGND

7

1690µ

SDA

3

SCL

4

Figure 4. Metallization Photo

Dimensions shown in microns (μm)

V

DD

6

DGND

5

Rev. 0 | Page 6 of 16

05950-030

Page 7

AD5821

www.BDTIC.com/ADI

TYPICAL PERFORMANCE CHARACTERISTICS

INL (LSB)

2.0

1.5

1.0

0.5

INL V

= 3.8V

DD

TEMP = 25°C

0

VERT = 50μs/DIV

3

–0.5

0

56

112

168

224

280

336

Figure 5. Typical IN

0.6

0.5

0.4

0.3

0.2

0.1

DNL (LSB)

0

–0.1

–0.2

–0.3

0

56

112

168

224

280

336

Figure 6. Typical DNL vs. Code Plot

92.0

91.5

91.0

90.5

90.0

89.5

OUTPUT CURRENT (mA)

89.0

88.5

88.0

53.5

–6

100.0

–6

150.0

Figure 7. ¼ to ¾ Scale Settling Time (V

448

392

CODE

448

392

CODE

–6

200.0

TIME

672

616

560

504

L vs. Code Plot

672

616

560

504

–6

250.0

DD

896

840

784

728

DNL VDD = 3.8V

TEMP = 25°C

896

840

784

728

–6

300.0

= 3.6 V)

952

1008

1023

05034-004

CH3 M50.0μs

Figure 8. Settling Time for a 4-LSB Step (V

HORIZ = 468μA/DIV

= 3.6 V)

DD

05034-007

952

1008

1023

05034-005

VERT = 2μA/DIV

1

CH1 M2.0s

Figure 9. 0.1 Hz to 10 Hz Noise Plot (V

4.8μA p-p

HORIZ = 2s/DIV

= 3.6 V)

DD

05034-008

0.14

I

@ +25°C

616

I

OUT

@ –40°C

728

672

OUT

I

784

OUT

@ +85°C

896

840

= 3.6 V)

DD

952

1008

1023

05034-009

0.12

0.10

0.08

(A)

OUT

0.06

I

0.04

0.02

05034-006

–6

–6

333.1

0

0

56

112

168

224

280

336

392

448

CODE

504

560

Figure 10. Sink Current vs. Code vs. Temperature (V

Rev. 0 | Page 7 of 16

Page 8

AD5821

www.BDTIC.com/ADI

2000

1800

1600

1400

1200

1000

μA/V

800

600

400

200

0

10 100 1k 100k10k

FREQUENCY

Figure 11. AC Power Supply Rejection (V

3.5

3.0

2.5

2.0

1.5

1.0

INL (LSB)

0.5

NEGATIVE INL (VDD = 3.6V)

0

–0.5

–1.0

Figure 12. INL vs. Temperat

NEGATIVE INL (V

NEGATIVE INL (V

TEMPERATURE (°C)

DD

ure vs. Supply Voltage

1.0

0.8

0.6

0.4

POSITIVE DNL (V

0.2

0

NEGATIVE DNL (V

DNL (LSB)

–0.2

–0.4

–0.6

NEGATIVE DNL (V

–0.8

–1.0

Figure 13. DNL vs. Temperat

DD

DD

NEGATIVE DNL (V

POSITIVE DNL (VDD = 3.6V)

= 4.5V)

= 3.8V)

= 3.6V)

DD

TEMPERATURE (°C)

POSITIVE DNL (V

DD

ure vs. Supply Voltage

= 3.6 V)

DD

POSITIVE INL (V

POSITIVE INL (VDD = 3.6V)

= 3.8V)

= 4.5V)

DD

= 4.5V)

DD

= 3.8V)

DD

= 4.5V)POSITIVE INL (VDD = 3.8V)

05034-010

05034-011

85–40–30–20–100 15253545556575

05034-012

85–40–30–20–100 15253545556575

0.45

0.40

0.35

0.30

V

DD

0.25

0.20

0.15

ZERO-CODE ERROR (mA)

0.10

0.05

0

= 4.5V

VDD = 3.6V

= 3.8V

V

DD

TEMPERATURE (°C)

Figure 14. Zero-Code Error vs. Supply Voltage vs. Temperature

1.5

= 4.5V

V

1.0

0.5

= 3.8V

V

DD

0

–0.5

–1.0

FULL-SCAL E ERROR (mA)

–1.5

–2.0

DD

VDD = 3.6V

TEMPERATURE (°C)

Figure 15. Full-Scale Error vs. Temperature vs. Supply Voltage

1.4

VDD = 5.5V

1.3

= 4.5V

V

DD

1.2

VDD = 3.6V

1.1

VDD = 2.7V

1.0

0.9

0.8

VO LTAG E (V )

0.7

0.6

0.5

0.4

–50 –30 9070503010–10

Figure 16. SCL and SDA Logic High Level (V

TEMPERATURE (°C)

) vs.

INH

Supply Voltage and Temperature

05950-013

85–40 –30 –20 –10 0 15 25 35 45 55 65 75

05950-014

85–40 –30 –20 –10 0 15 25 35 45 55 65 75

05950-024

Rev. 0 | Page 8 of 16

Page 9

AD5821

www.BDTIC.com/ADI

1.4

1.3

1.2

1.1

1.0

0.9

0.8

VO LTAG E (V )

0.7

0.6

0.5

0.4

–50 –30 9070503010–10

Figure 17. SCL and SDA Logic Low Level (V

VDD = 3.6V

VDD = 5.5V

VDD = 2.7V

TEMPERATURE (°C)

V

DD

= 4.5V

) vs.

INL

05950-026

Supply Voltage and Temperature

1.4

VDD = 5.5V

1.3

= 4.5V

V

DD

1.2

VDD = 3.6V

1.1

VDD = 2.7V

1.0

0.9

0.8

VO LTAG E (V )

0.7

0.6

0.5

0.4

–50 –30 9070503010–10

TEMPERATURE (°C)

Figure 18. XSHUTDOWN Logic High Level (V

INH

) vs.

05950-025

Supply Voltage and Temperature

1.4

1.3

1.2

1.1

1.0

0.9

0.8

VO LTAG E (V )

0.7

0.6

0.5

0.4

–50 –30 9070503010–10

Figure 19. DNL vs. XSHUTDOWN Logic Low Level (V

VDD = 5.5V

VDD = 3.6V

TEMPERATURE (°C)

= 4.5V

V

DD

VDD = 2.7V

05950-027

) vs.

INL

Supply Voltage and Temperature

Rev. 0 | Page 9 of 16

Page 10

AD5821

www.BDTIC.com/ADI

TERMINOLOGY

Relative Accuracy

For the DAC, relative accuracy or integral nonlinearity is a

m

easurement of the maximum deviation, in LSB, from a

straight line passing through the endpoints of the DAC transfer

function. A typical INL vs. code plot is shown in

Differential Nonlinearity (DNL)

Differential nonlinearity is the difference between the measured

cha

nge and the ideal 1 LSB change between any two adjacent

codes. A specified differential nonlinearity of ±1 LSB maximum

ensures monotonicity. This DAC is guaranteed monotonic by

design. A typical DNL vs. code plot is shown in

Zero-Code Error

Zero-code error is a measurement of the output error when zero

co

de (0x0000) is loaded to the DAC register. Ideally, the output

is 0 mA. The zero-code error is always positive in the AD5821

because the output of the DAC cannot go below 0 mA. This is

due to a combination of the offset errors in the DAC and output

amplifier. Zero-code error is expressed in milliamperes (mA).

Gain Error

Gain error is a measurement of the span error of the DAC. It is

t

he deviation in slope of the DAC transfer characteristic from

the ideal, expressed as a percent of the full-scale range.

Gain Error Drift

Gain error drift is a measurement of the change in gain error

wi

th changes in temperature. It is expressed in LSB/°C.

Figure 5.

Figure 6.

Digital-to-Analog Glitch Impulse

This is the impulse injected into the analog output when the

in

put code in the DAC register changes state. It is normally

specified as the area of the glitch in nanoamperes per second

(nA-s) and is measured when the digital input code is changed

by 1 LSB at the major carry transition.

Digital Feedthrough

Digital feedthrough is a measurement of the impulse injected

i

nto the analog output of the DAC from the digital inputs of the

DAC, but it is measured when the DAC output is not updated.

It is specified in nanoamperes per second (nA-s) and measured

with a full-scale code change on the data bus, that is, from all 0s

to all 1s and vice versa.

Offset Error

Offset error is a measurement of the difference between I

(actual) and I

function, expressed in milliamperes (mA). Offset error is

measured on the AD5821 with Code 16 loaded into the DAC

register.

Offset Error Drift

Offset error drift is a measurement of the change in offset error

th a change in temperature. It is expressed in microvolts per

wi

degree Celsius (µV/°C).

(ideal) in the linear region of the transfer

OUT

SINK

Rev. 0 | Page 10 of 16

Page 11

AD5821

V

www.BDTIC.com/ADI

THEORY OF OPERATION

The AD5821 is a fully integrated, 10-bit digital-to-analog

converter (DAC) with 120 mA output current sink capability.

It is intended for driving voice coil actuators in applications

such as lens autofocus, image stabilization, and optical zoom.

The circuit diagram is shown in

output

DAC coupled with Resistor R generates the voltage that

Figure 20. A 10-bit current

drives the noninverting input of the operational amplifier. This

voltage also appears across the R

resistor and generates the

SENSE

sink current required to drive the voice coil.

Resistor R and Resistor R

are interleaved and matched.

SENSE

Therefore, the temperature coefficient and any nonlinearities

over temperature are matched, and the output drift over temperature is minimized. Diode D1 is an output protection diode.

XSHUTDOWN

REFERENCE

POWER-ON

RESET

SDA

SCL

I2C SERIAL

INTERFACE

DGND

Figure 20. Block Diagram Showing Connection to Voice Coil

10-BIT

CURRENT

OUTPUT DAC

AD5821

R

DGND

DD

V

DD

D1

I

SINK

R

SENSE

3.3Ω

AGND

SERIAL INTERFACE

The AD5821 is controlled using the industry-standard I2C

2-wire serial protocol. Data can be written to or read from the

DAC at data rates of up to 400 kHz. After a read operation, the

contents of the input register are reset to all 0s.

I2C BUS OPERATION

An I2C bus operates with one or more master devices that

generate the serial clock (SCL) and read and write data on the

serial data line (SDA) to and from slave devices such as the

AD5821. All devices on an I

to the SDA line and their SCL pin connected to the SCL line of

the master device. I

2

pulling high is achieved by pull-up resistors, R

depends on the data rate, bus capacitance, and the maximum load

current that the I

1.8V

R

PRP

2

C device can sink (3 mA for a standard device).

SDA

SCL

2

C bus have their SDA pin connected

C devices can only pull the bus lines low;

. The value of RP

P

05950-001

When the bus is idle, SCL and SDA are both high. The master

device initiates a serial bus operation by generating a start

condition, which is defined as a high-to-low transition on the

SDA low while SCL is high. The slave device connected to the

bus responds to the start condition and shifts in the next eight

data bits under control of the serial clock. These eight data bits

consist of a 7-bit address, plus a read/write (R/

W

) bit that is 0 if

data is to be written to a device, and 1 if data is to be read from a

device. Each slave device on an I

2

C bus must have a unique address.

The address of the AD5821 is 0001100; however, 0001101,

0001110, and 0001111 address the part because the last two bits

are unused/don’t cares (see

ess plus the R/

addr

W

Figure 22 and Figure 23). Because the

bit always equals eight bits of data, the write

address of the AD5821 is 00011000 (0x18) and the read address

is 00011001 (0x19) (see Figure 22 and Figure 23).

At the end of the address data, after the R/

W

bit, the slave

device that recognizes its own address responds by generating

an acknowledge (ACK) condition. This is defined as the slave

device pulling SDA low while SCL is low before the ninth clock

pulse and keeping it low during the ninth clock pulse. Upon

receiving ACK, the master device can clock data into the AD5821

in a write operation, or it can clock it out in a read operation.

Data must change either during the low period of the clock

(because SDA transitions during the high period define a start

condition, as described previously), or during a stop condition,

as described in the

2

I

C data is divided into blocks of eight bits, and the slave generates

Data Format section.

an ACK at the end of each block. Because the AD5821 requires

10 bits of data, two data-words must be written to it when a

write operation occurs, or read from it when a read operation

occurs. At the end of a read or write operation, the AD5821

acknowledges the second data byte. The master generates a stop

condition, defined as a low-to-high transition on SDA while SCL

is high, to end the transaction.

DATA FORMAT

Data is written to the AD5821 high byte first, MSB first, and is

shifted into the 16-bit input register. After all data is shifted in,

data from the input register is transferred to the DAC register.

Because the DAC requires only 10 bits of data, not all bits of the

in

put register data are used. The MSB is reserved for an activehigh, software-controlled, power-down function. Bit 14 is unused;

Bit 13 to Bit 4 correspond to the DAC data bits, Bit 9 to Bit 0.

Bit 3 to Bit 0 are unused.

During a read operation, data is read in the same bit order.

I2C MASTER

DEVICE

I2C SLAVE

DEVICE

Figure 21. Typical I

AD5821

2

C Bus

I2C SLAVE

DEVICE

5950-016

Rev. 0 | Page 11 of 16

Page 12

AD5821

V

X

www.BDTIC.com/ADI

SCL

SDA

1191

START BY

MASTER

00

01 11 1R/W

FRAME 1

SERIAL BUS

ADDRESS BYTE

PD X D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 X X X X

ACK BY

AD5821

FRAME 2

MOST SIGNIFICANT

DATA BYTE

ACK BY

AD5821

FRAME 3

LEAST SIG NIFICANT

DATA BYTE

9

ACK BY

AD5821

STOP BY

MASTER

05950-017

Figure 22. Write Operation

SCL

SDA

1191

START BY

MASTER

00

01 11 1R/W

FRAME 1

SERIAL BUS

ADDRESS BYTE

PD X D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 X X X X

ACK BY

AD5821

FRAME 2

MOST SIGNIFICANT

DATA BYTE

ACK BY

AD5821

FRAME 3

LEAST SIG NIFICANT

DATA BYTE

Figure 23. Read Operation

9

ACK BY

AD5821

STOP BY

MASTER

05950-018

Table 6. Data Format

1

Serial Data-Words High Byte Low Byte

Serial Data Bits SD7 SD6 SD5 SD4 SD3 SD2 SD1 SD0 SD7 SD6 SD5 SD4 SD3 SD2 SD1 SD0

Input Register R15 R14 R13 R12 R11 R10 R9 R8 R7 R6 R5 R4 R3 R2 R1 R0

Function XSHUTDOWN X D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 X X X X

1

XSHUTDOWN = soft power-down; X = unused/don’t care; and D9 to D0 = DAC data.

BATTERY

POWER SUPPLY BYPASSING AND GROUNDING

When accuracy is important in an application, it is beneficial to

consider power supply and ground return layout on the PCB.

The PCB for the AD5821 should have separate analog and digital

power supply sections. Where shared AGND and DGND is

necessary, the connection of grounds should be made at only

one point, as close as possible to the AD5821.

Special attention should be paid to the layout of the AGND return

p

ath and, and it should be tracked between the voice coil motor

and I

output current sink of the AD5821 and illustrates the importance

of reducing the effective series impedance of AGND and the track

resistance between the motor and I

as Inductor L

is effectively a dc current that results in a voltage drop, V

the AD5821 is sinking current. The effect of any series inductance

is minimal.

to minimize any series resistance. Figure 24 shows the

SINK

. The voice coil is modeled

SINK

and Resistor RC. The current through the voice coil

C

, when

C

VOICE

COIL

V

DD

DGND

SDA

SCL

SHUTDOWN

DGND

AD5821

R

R

SENSE

Q1

AGND

R

G

GROUND

RETURN

L

G

Figure 24. Effect of PCB Trace Resistance and Inductance

L

R

R

I

SINK

C

C

T

V

DROP

V

COIL

TRACE

RESISTANCE

05950-019

Rev. 0 | Page 12 of 16

Page 13

AD5821

×+×+

−

+

−

www.BDTIC.com/ADI

When sinking the maximum current of 120 mA, the maximum

voltage drop allowed across R

is 400 mV, and the minimum

SENSE

drain to source voltage of Q1 is 200 mV. This means that the

AD5821 output has a compliance voltage of 600 mV. If V

DROP

falls below 600 mV, the output transistor, Q1, can no longer

operate properly and I

may not be maintained as a constant.

SINK

When sinking 90 mA, the maximum voltage drop allowed

oss R

acr

is 300 mV, and the minimum drain to source

SENSE

voltage of Q1 is 180 mV. This means that the AD5821 output

has a compliance voltage of 480 mV. If V

falls below 480 mV,

DROP

the output transistor, Q1, can no longer operate properly and

I

may not be maintained as a constant. As I

SINK

decreases, the

SINK

voltage required across the transistor, Q1, also decreases and,

therefore, lower supplies can be used with the voice coil motor.

As the current increases to 120 mA through the voice coil,

V

increases. V

C

decreases and eventually approaches the

DROP

minimum specified compliance voltage of 600 mV (or 480 mV,

if I

= 90 mA). The ground return path is modeled by the

SINK

components R

coil and the AD5821 is modeled as R

L

influence R

G

and LG. The track resistance between the voice

G

. The inductive effects of

T

and RC equally, and because the current is

SENSE

maintained as a constant, it is not as critical as the purely resistive

component of the ground return path. When the maximum sink

current is flowing through the motor, the resistive elements, R

, may have an impact on the voltage headroom of Q1 and

R

G

could, in turn, limit the maximum value of R

because of

C

and

T

voltage compliance.

For example, if

V

R

R

I

V

Then the largest value of resistance of the voice coil, R

= 3.6 V

BATTERY

= 0.5 Ω

G

= 0.5 Ω

T

= 120 mA

SINK

= 600 mV (the compliance voltage)

DROP

BAT

R

=

C

SINKDROP

I

SINK

mA120

, is

C

RIRIVV

)]()([

×+×+−

T

××+−

GSINK

=

)]0.5mA(1202mV[600V3.6

24

=

Using another example, if

V

= 3.6 V

BATTERY

R

= 0.5 Ω

G

R

= 0.5 Ω

T

I

= 90 mA

SINK

V

= 480 mV (the compliance voltage specification at 90 mA)

DROP

Then the largest value of resistance of the voice coil, R

SINKDROP

I

SINK

T

)]0.5mA(902mV[480V3.6

××

=

BAT

R

=

C

mA90

, is

C

RIRIVV

)]()([

GSINK

=

33.66

For this reason, it is important to minimize any series impedance

on both the ground return path and interconnect between the

AD5821 and the motor. It is also important to note that for

lower values of I

, the compliance voltage of the output stage

SINK

also decreases. This decrease allows the user to either use voice

coil motors with high resistance values or decrease the power

supply voltage on the voice coil motor. The compliance voltage

decreases as the I

current decreases.

SINK

The power supply of the AD5821, or the regulator used to supply

e AD5821, should be decoupled. Best practice power supply

th

decoupling recommends that the power supply be decoupled

with a 10 µF capacitor. Ideally, this 10 µF capacitor should be of

a tantalum bead type. However, if the power supply or regulator

supply is well regulated and clean, such decoupling may not be

required. The AD5821 should be decoupled locally with a 0.1 µF

ceramic capacitor, and this 0.1 F capacitor should be located as

close as possible to the V

pin. The 0.1 µF capacitor should be

DD

ceramic with a low effective series resistance and effective series

inductance. The 0.1 µF capacitor provides a low impedance path

to ground for high transient currents.

The power supply line should have as large a trace as possible to

p

rovide a low impedance path and reduce glitch effects on the

supply line. Clocks and other fast switching digital signals should

be shielded from other parts of the board by digital ground.

Avoid crossover of digital and analog signals, if possible. When

traces cross on opposite sides of the board, they should run at

right angles to each other to reduce feedthrough effects through

the board. The best technique is to use a multilayer board with

ground and power planes, where the component side of the

board is dedicated to the ground plane only and the signal

traces are placed on the solder side. However, this is not always

possible with a 2-layer board.

Rev. 0 | Page 13 of 16

Page 14

AD5821

V

V

www.BDTIC.com/ADI

APPLICATIONS INFORMATION

The AD5821 is designed to drive both spring-preloaded and

nonspring linear motors used in applications such as lens autofocus, image stabilization, or optical zoom. The operation principle

of the spring-preloaded motor is that the lens position is controlled

by the balancing of a voice coil and spring.

tra

nsfer curve of a typical spring-preloaded linear motor for

Figure 25 shows the

autofocus. The key points of this transfer function are displacement or stroke, which is the actual distance the lens moves in

millimeters (mm) and the current through the motor, measured

in milliamps (mA).

A start current is associated with spring-preloaded linear

motors, which is a threshold current that must be exceeded for

any displacement in the lens to occur. The start current is usually

20 mA or greater; the rated stroke or displacement is usually

0.25 mm to 0.4 mm; and the slope of the transfer curve is

approximately 10 µm/mA or less.

The AD5821 is designed to sink up to 120 mA, which is more

t

han adequate for available commercial linear motors or voice

coils. Another factor that makes the AD5821 the ideal solution

for these applications is the monotonicity of the device, ensuring

that lens positioning is repeatable for the application of a given

digital word.

Figure 26 shows a typical application circuit for the AD5821.

DD

R

R

P

P

SDA

SCL

XSHUTDOWN

1

3

4

I2C SERIAL

INTERFACE

0.5

0.4

0.3

0.2

STROKE (mm)

0.1

REFERENCE

10-BIT

CURRENT

OUTPUT DAC

START

CURRENT

10 50 60 8070 90 100403020 110 120

SINK CURRENT (mA)

Figure 25. Spring-Preloaded Voice Coil Stroke vs. Sink Current

0.1µF

DD

6

POWER-ON

RESET

2

D1

V

CC

VOICE

COIL

I

8

SINK

05950-029

I2C MASTER

DEVICE

I2C SLAVE

DEVICE

R

R

SENSE

AD5821

5

V

DD

V

CC

+

10µF

0.1µF 10µF

Figure 26. Typical Application Circuit

Rev. 0 | Page 14 of 16

7

+

05950-028

Page 15

AD5821

www.BDTIC.com/ADI

OUTLINE DIMENSIONS

0.65

1.575

1.515

1.455

0.59

0.53

SEATING

PLANE

123

A

B

C

110405-0

BALL 1

IDENTIFIER

TOP VIEW

(BALL SI DE DOWN)

0.36

1.750

1.690

1.630

0.28

0.24

0.20

Figure 27. 9-Ball Wafer Level Chip Scale Package [WLCSP]

Dim

(CB-9-1)

ensions shown in millimeters

0.32

0.28

0.50 BSC

BALL PIT CH

BOTTOM VIEW

(BALL SI DE UP)

ORDERING GUIDE

Model Temperature Range Package Description Package Option Branding

AD5821BCBZ-REEL71−40°C to +85°C 9-Ball Wafer Level Chip Scale Package (WLCSP) CB-9-1 D82

AD5821BCBZ-REEL

AD5821-WAFER −40°C to +85°C Bare Die Wafer

AD5821D-WAFER −40°C to +85°C Bare Die Wafer on Film

EVAL-AD5821EBZ

1

Z = Pb-free part.

1

−40°C to +85°C 9-Ball Wafer Level Chip Scale Package (WLCSP) CB-9-1 D82

1

Evaluation Board

Rev. 0 | Page 15 of 16

Page 16

AD5821

www.BDTIC.com/ADI

NOTES

Purchase of licensed I2C components of Analog Devices or one of its sublicensed Associated Companies conveys a license for the purchaser under the Philips I2C Patent

Rights to use these components in an I

2

C system, provided that the system conforms to the I2C Standard Specification as defined by Philips.

©2007 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D05950-0-1/07(0)

T

Rev. 0 | Page 16 of 16

TTT

Loading...

Loading...