Page 1

PRELIMINARY TECHNICAL DATA

QUAD, Parallel-Input, Voltage Output,

a

12-/10-Bit Digital-to-Analog Converter

AD5582/AD5583

FEATURES

12-Bit Linearity and Monotonic –40

o

C to +125oC

Single +5V to +12V or dual ±5V supply

Unipolar or Bipolar Operation

Double Buffered Registers Enable Simultaneous Multi-

Channels Update

4 Separate Rail-to Rail Reference Inputs

Parallel Interface

Data Readback Capability

5µs Settling Time

APPLICATIONS

Process Control Equipment

Closed Loop Servo Control

Data Acquisition Systems

Digitally Controlled Calibration

Motor Control

Optical Network Control Loops

GENERAL DESCRIPTION

The AD5582/AD5583 family of quad, 12-/10-bit, voltage-output

digital-to-analog converter is designed to operate from a single +5

to +15 volt or a dual ±5V supply. Built using a CBCMOS process,

this monolithic DAC offers the user low cost, and ease-of-use in

single or dual-supply systems.

The applied external reference V

output voltage. Valid V

values include VSS<V

REF

determines the full-scale

REF

REF<VDD

resulting

in a wide selection of full scale outputs. For multiplying

applications AC inputs can be as large as |V

|. Two on-board

DD-VSS

precision trimmed resistors are available for 4-Quadrant

configurations.

A doubled-buffered parallel interface offers 25Mbps data load rates.

A common level-sensitive load-DAC strobe (LDAC) input allows

simultaneous update of all DAC outputs from previously loaded

Input Registers. An external asynchronous reset (RS) forces all

registers to the zero code state when MSB='0' or to midscale when

MSB='1'.

Both parts are offered in the same pin-out to allow users to select

the amount of resolution appropriate for their application without

circuit card redesign.

The AD5582/AD5583 are specified over the extended industrial

(-40°C to +125°C) temperature range. Packages available include

thin 1.1 mm TSSOP-48 package.

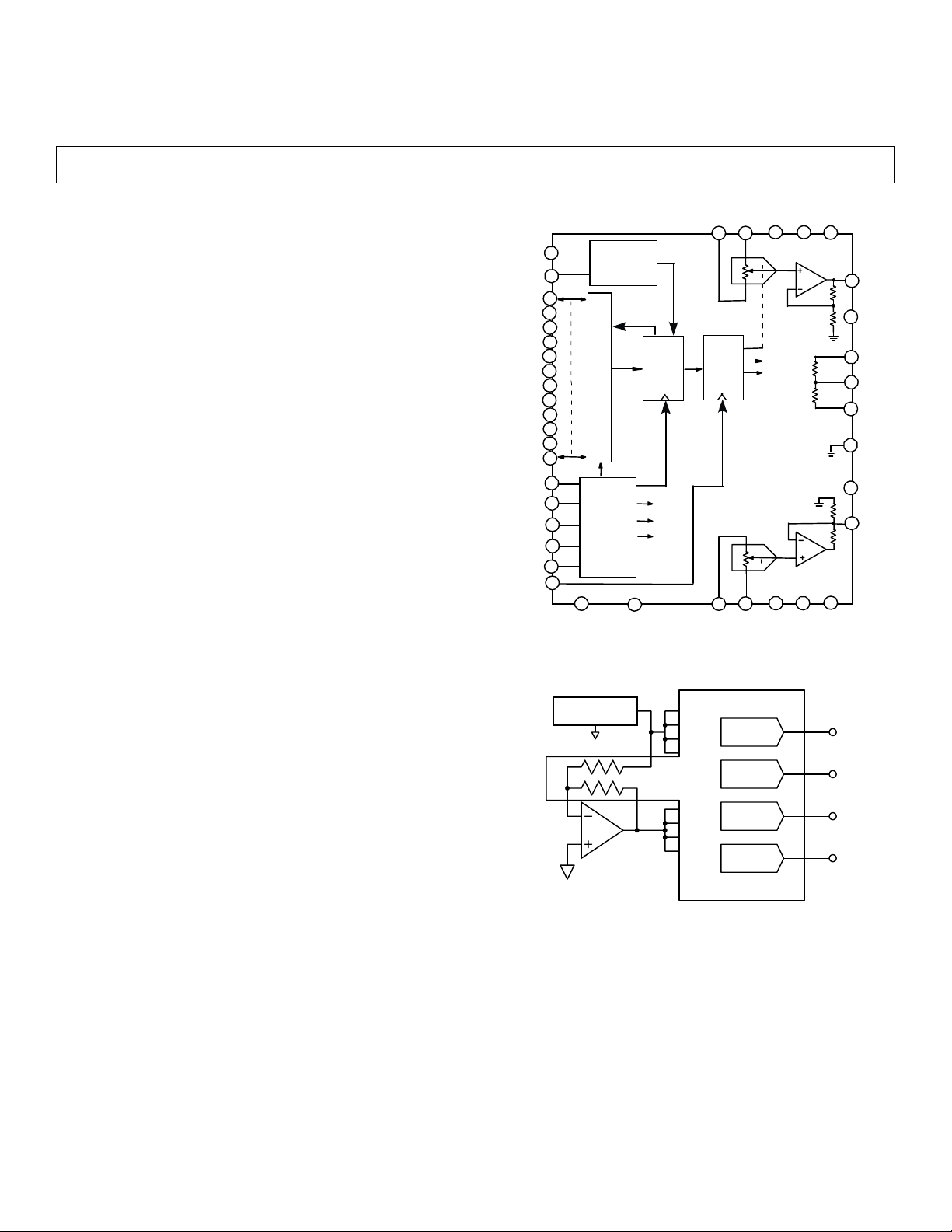

FUNCTIONAL DIAGRAM

A1

V

LOGIC

A0

DB11

DB10

DB9

DB8

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

CS

W/

MSB

RS

LDAC

37

36

24

25

26

27

28

29

30

31

32

33

34

35

23

22

R

19

17

18

21

CONTROL

16

DVDD

ADDR

DECODE

I

N

T

E

R

F

A

C

E

OE

LOGIC

DGND

V

RLAVRHAVRLBVRHB

1

Do

DAC

IN

Di

REG

REG

3

2

20k

20k

4 5

Ω

Ω

V

DD

6

7

38

39

40

AD5582

8

9

10

11

12

20

V

15

RHD

13

14

V

RLD

V

RHC

V

RLCVSS

+2.5V

V

AD5582

ADR421

R

B

DIGITAL CIRCUITRY OMITTED FOR CLARITY

R

-2.5V

Figure 1 Using Onboard Offset resistors to generate a negative

voltage REF

REFH

A

B

DAC A

C

D

R

A

C

DAC B

V

REFL

A

DAC C

B

C

D

±2.5V

±2.5V

±2.5V

±2.5V

DAC D

V

V

RA

RB

RC

AGND

V

V

OA

OB

OC

OD

REV PrC, 23 APR '01

Information furnished b y Analog Devices is believed to be accurate and reliable. However,

no responsibility is assumed by Analog Devices for its use; nor for any infringements of

patents or other rights of third parties which may result from its use. No license is granted

by implication or otherwise under any patent or patent rights of A nalog Devices.

One Technology Way, P.O. Box 9106,

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax:781/326-8703 ©Analog Devices, Inc., 2000

Norwood, MA 02062-9106 U.S.A.

Page 2

PRELIMINARY TECHNICAL DATA

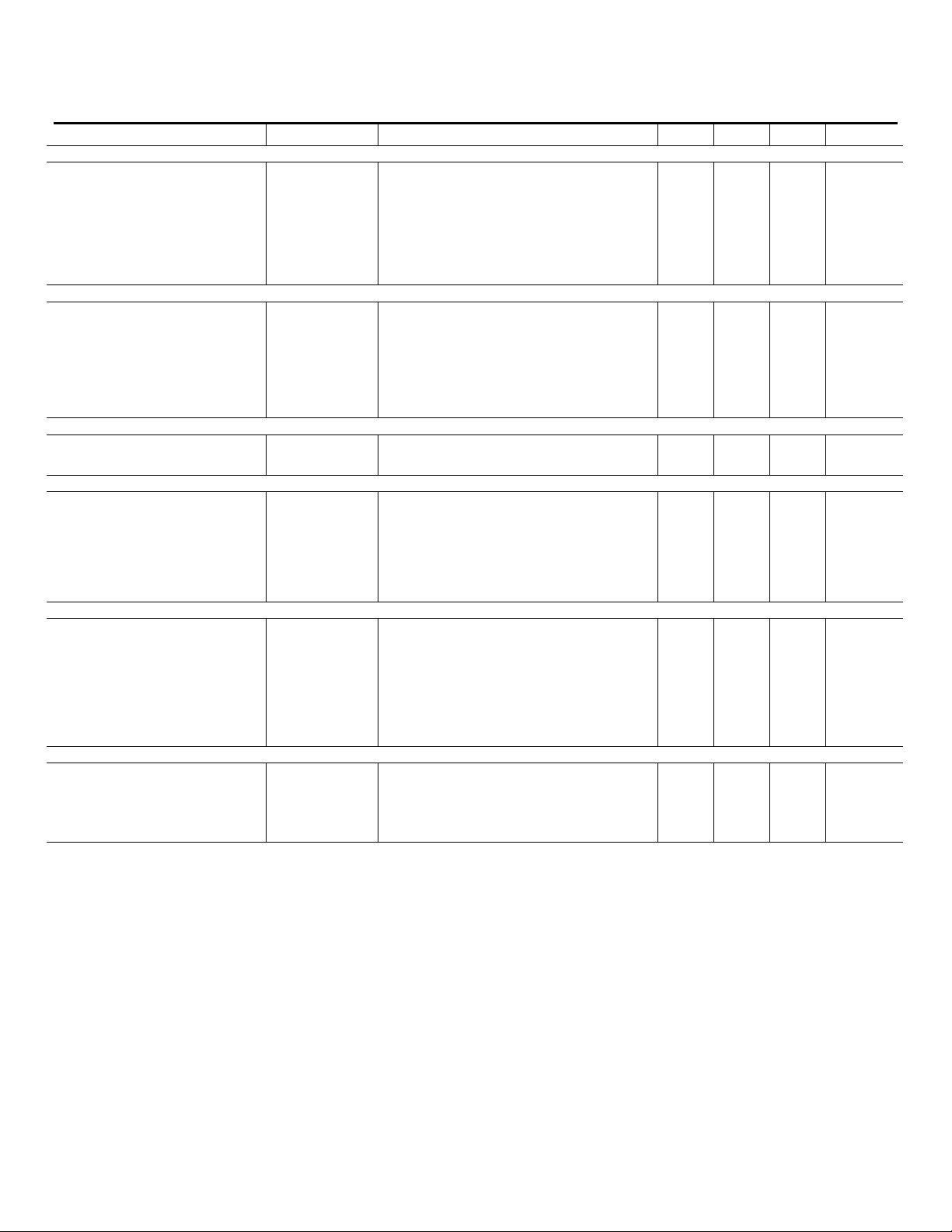

ELECTRICAL CHARACTERISTICS

at VDD =+5V, V

= -5V, VL = +5V±10%, V

SS

AD5582/AD5583

REFH

= +2.5V, V

= -2.5V, -40°C < TA < +125°C, unless otherwise noted.

REFL

PARAMETER SYMBOL CONDITION MIN TYP MAX UNITS

STATIC PERFORMANCE

Resolution1 N AD5582 12 Bits

Resolution1 N AD5583 10 Bits

Relative Accuracy2 INL -1 +1 LSB

Differential Nonlinearity2 DNL Monotonic -1 LSB

V

Zero-Scale Error

Full-Scale Voltage Error

Full-Scale Tempco3

Data = 000H

ZSE

V

Data = FFFH

FSE

TCVFS

2 LSB

2 LSB

10 ppm/oC

REFERENCE INPUT

V

Input Range4 V

REFH

V

Input Range4 V

REFL

Input Resistance8

Input Capacitance3

REF Input Current

REF Multiplying Bandwidth

BW

REFH

REFL

R

REF

C

REF

I

REF

REF

V

V

Data = 555H 10

80 pF

500

Hz

SS

SS

V

DD

V

DD

V

V

KΩ

5

µA

ANALOG OUTPUT

I

Output Current

Capacitive Load3

OUT

CL

Data = 800H, ∆V

OUT

= 4LSB

±2 mA

No Oscillation 500 pF

LOGIC INPUTS Logic Input Low Voltage

Logic Input High Voltage

Input Leakage Current

Input Capacitance3

Output Voltage High VOH I

Output Voltage Low VOL I

VIL

VIH

IIL

CIL

VL = 5V ± 10% 0.8 V

VL = 5V ± 10% 2.4 V

µA

pF

= -0.8mA 2.4 V

OH

= 1.6mA 0.4 V

OL

AC CHARACTERISTICS Output Slew Rate SR

Settling Time7

Shutdown Recovery t

tS

SDR

Data = 000H to FFFH to 000H

2

To ±0.1% of Full Scale 5

V/µs

µs

µs

DAC Glitch Q Code 7FFH to 800H to 7FFH 100 nVs

Digital Feed Through

Analog Crosstalk

V

OUT

V

OUT/VREF

Output Noise eN 40

/t

CS

Data=800

V

REF

, CS toggles at f=16MHz

H

= 1.5VDC +1V

, Data = 000H, f=100KHz

P-P

5 nVs

-80 dB

nV√Hz

SUPPLY CHARACTERISTICS

Positive Supply Current

Negative Supply Current

Power Dissipation

IDD V

ISS V

P

VIL = 0V, No Load

DISS

Power Supply Sensitivity PSS

NOTES:

1. DAC Output Equation: V

DAC resolution AD5582 = 12, AD5583 = 10 bits. One LSB = VREF/4096V for the 12-bit AD5582.

2. The first two codes (000H, 001H) are excluded from the linearity error measurement in single supply operation.

3. These parameters are guaranteed by design and not subject to production testing.

4. When V

minus the offset voltage of the output buffer, which is the same as the V

sheet.

5. Typical specifications represent average readings measured at 25°C.

6. The settling time specification does not apply for negative going transitions within the last 3 LSBs of ground in single supply operation.

is connected to either the VDD or the VSS power supply the corresponding V

REF

OUT

= V

REFL

+ [(V

REFH-VREFL

= 0V, No Load

IL

= 0V, No Load

IL

3 mA

3 mA

30 mW

∆VDD = ±5%

)*Code/2^N], where Code = data loaded in corresponding DAC register A, B, C, D and N equals the

voltage will program between ground and the supply voltage

error specification. See additional discussion in the operation section of the data

ZSE

OUT

30 ppm/V

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future

manufacture unless otherwise agreed to in writing.

REV PrC, 23 APR '01 2

Page 3

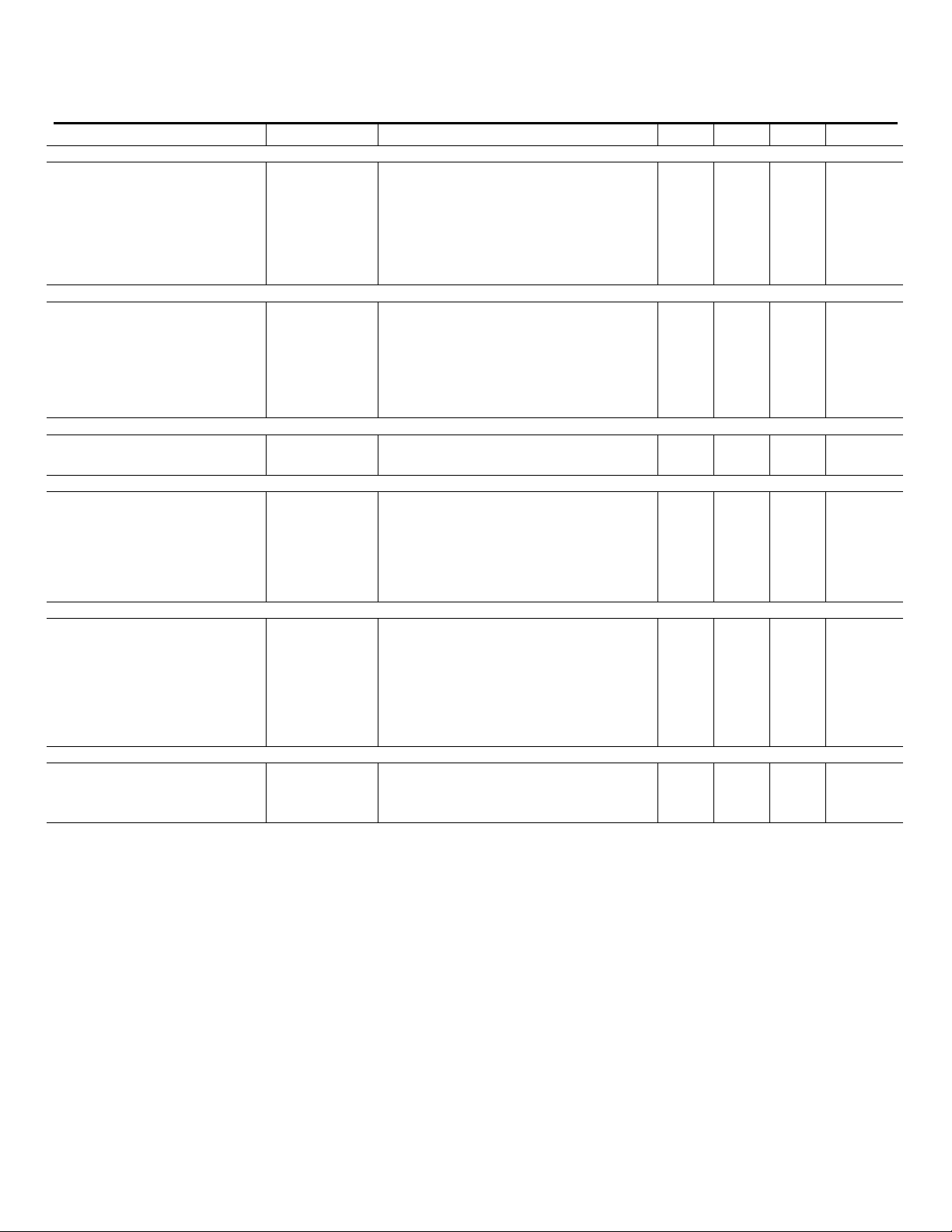

PRELIMINARY TECHNICAL DATA

ELECTRICAL CHARACTERISTICS

at VDD =+15V, V

= 0V, VL =+5V±10%, V

SS

AD5582/AD5583

REFH

= +10V, V

= 0V, -40°C < TA < +125°C, unless otherwise noted.

REFL

PARAMETER SYMBOL CONDITION MIN TYP MAX UNITS

STATIC PERFORMANCE

Resolution1 N AD5582 12 Bits

Resolution1 N AD5583 10 Bits

Relative Accuracy2 INL -1 +1 LSB

Differential Nonlinearity2 DNL Monotonic -1 LSB

V

Zero-Scale Error

Full-Scale Voltage Error

Full-Scale Tempco3

Data = 000H

ZSE

V

Data = FFFH

FSE

TCVFS

2 LSB

2 LSB

10 ppm/oC

REFERENCE INPUT V

V

Input Resistance8

Input Capacitance3

REF Input Current

REF Multiplying Bandwidth

Input Range4 V

REFH

Input Range4 V

REFL

R

C

I

BW

REFH

REFL

REF

REF

REF

REF

V

0 V

Data = 555H 10

VDD V

SS

V

DD

KΩ

5

80 pF

500

Hz

µA

ANALOG OUTPUT

I

Output Current

Capacitive Load3

OUT

CL

Data = 800H, ∆V

OUT

= 4LSB

+5 mA

No Oscillation 500 pF

LOGIC INPUTS/OUTPUTS Logic Input Low Voltage

Logic Input High Voltage

Input Leakage Current

Input Capacitance3

Output Voltage High VOH I

Output Voltage Low VOL I

VIL

VIH

IIL

CIL

0.8 V

2.4 V

µA

pF

= -0.8mA 2.4 V

OH

= 1.6mA 0.4 V

OL

AC CHARACTERISTICS Output Slew Rate SR

Settling Time7

Shutdown Recovery t

tS

SDR

Data = 000H to FFFH to 000H

2

To ±0.1% of Full Scale 5

V/µs

µs

µs

DAC Glitch Q Code 7FFH to 800H to 7FFH 100 nVs

Digital Feed Through

Analog Crosstalk

V

OUT

V

OUT/VREF

Output Noise eN 40

/t

CS

Data=800

V

REFH

, CS toggles at f=16MHz

H

= 2.5VDC +1V

, Data = 000H, f=100KHz

P-P

5 nVs

-80 dB

nV√Hz

SUPPLY CHARACTERISTICS

Positive Supply Current

Power Dissipation

IDD V

P

VIL = 0V, No Load

DISS

Power Supply Sensitivity PSS

NOTES:

1. DAC Output Equation: V

DAC resolution AD5582 = 12, AD5583 = 10 bits. One LSB = VREF/4096V for the 12-bit AD5582.

2. The first two codes (000H, 001H) are excluded from the linearity error measurement in single supply operation.

3. These parameters are guaranteed by design and not subject to production testing.

4. When V

minus the offset voltage of the output buffer, which is the same as the V

sheet.

5. Typical specifications represent average readings measured at 25°C.

6. The settling time specification does not apply for negative going transitions within the last 3 LSBs of ground in single supply operation.

is connected to either the VDD or the VSS power supply the corresponding V

REF

OUT

= V

REFL

+ [(V

REFH-VREFL

= 0V, No Load

IL

3 mA

45 mW

∆VDD = ±5%

)*Code/2^N], where Code = data loaded in corresponding DAC register A, B, C, D and N equals the

voltage will program between ground and the supply voltage

error specification. See additional discussion in the operation section of the data

ZSE

OUT

30 ppm/V

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future

manufacture unless otherwise agreed to in writing.

REV PrC, 23 APR '01 3

Page 4

PRELIMINARY TECHNICAL DATA

ELECTRICAL CHARACTERISTICS

at VDD =+15V, V

= 0V, VL =+5V±10%, V

SS

AD5582/AD5583

REFH

= +10V, V

= 0V, -40°C < TA < +125°C, unless otherwise noted.

REFL

PARAMETER SYMBOL CONDITION MIN TYP MAX UNITS

1,2

INTERFACE TIMING

Clock Frequency f

Chip Select Write Pulsewidth t

Write Setup tWS t

Write Hold tWH t

25 MHz

CLK

30 ns

WCS

= 50 ns 0 ns

WCS

= 50 ns 0 ns

WCS

Address Setup tAS 0 ns

Address Hold tAH 0 ns

Load Setup tLS 70 ns

Load Hold tLH 30 ns

Write Data Setup t

Write Data Hold t

Load Data Pulsewidth t

Reset Pulsewidth t

Chip Select Read Pulsewidth t

Read Data Hold t

Read Data Setup t

Data to Hi Z tDZ C

Chip Select to Data t

Chip Select Repetitive Pulsewidth t

Load Setup in Double Buffer Mode t

t

WDS

t

WDH

50 ns

LDW

50 ns

RESET

130 ns

RCS

t

RDH

t

RDS

C

CSD

10 ns

CSP

20 ns

LDS

= 50 ns 0 ns

WCS

= 50 ns 0 ns

WCS

= 130 ns 0 ns

RCS

= 130 ns 0 ns

RCS

= 10pF 100 ns

L

= 100pF 100 ns

L

NOTES:

1. All input control signals are specified with tR = tF = 2ns (10% to 90% of +3V) and timed from a voltage level of 1.5V.

2. Typicals represent average readings measured at 25°C.

ABSOLUTE MAXIMUM RATINGS

VDD to VSS....................................................... -0.3V to +16.5V

VDD to GND..........................................................-0.3V to 5.5V

VSS to GND......................................................... +0.3V to -5.5V

VDD to V

V

to VSS............................................... -0.3V to (VDD-VSS)

REF-

V

to V

REFH

Logic Inputs to GND............................ V

V

to GND....................................... V

OUT

Short Circuit to GND...........................................................

I

OUT

Thermal Resistance θ

TSSOP-48 Lead (RU-48) ........................................ xxx°C/W

............................................. -0.3V to (V

REF+

........................................ -0.3V to (V

REFL

JA

DD-VSS

DD-VSS

– 0.3V, VDD + 0.3V

SS

– 0.3V, VDD + 0.3V

SS

Maximum Junction Temperature (TJ

Package Power Dissipation = (TJ MAX – TA)/θ

) ........................ 150°C

MAX

JA

Operating Temperature Range ..........................–40°C to +125°C

)

)

Storage Temperature Range ..............................–65°C to +150°C

Lead Temperature:

RU-48 (Vapor Phase, 60 secs)...................................... xxx°C

RU-44 (Infrared, 15 secs)............................................. xxx°C

Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to

the device. This is a stress rating only and functional operation of the device at these or any other

conditions above those indicated in the oper ational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

ORDERING GUIDE:

Resolution TEMP Package Package Container

MODEL (Bits) RANGE Description Option Qty

AD5582YRU-REEL7 12 -40/+125°C TSSOP-48 RU-48

AD5583YRU-REEL7 10 -40/+125°C TSSOP-48 RU-48

The AD5582 contains xxx transistors. The die size measures 108 mil X 144 mil.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future

manufacture unless otherwise agreed to in writing.

REV PrC, 23 APR '01 4

Page 5

PRELIMINARY TECHNICAL DATA

PIN CONFIGURATION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

NOTE: Pin Out not finalized!

Please contact Analog Devices Inc. for final version

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

AD5582/AD5583

Pin# Name Description

. VRLA Voltage Reference Low Input Terminal DAC A

VRHA Voltage Reference High Input Terminal DAC A

VRLB Voltage Reference Low Input Terminal DAC B

VRHB Voltage Reference High Input Terminal DAC B

VDD Positive Power Supply

VOA DAC A Output

VOB DAC B output

RA End Tap Offset Resistor

RB Center Tap Offset Resistor

RC End Tap Offset Resistor

AGND Analog Ground

VOC Voltage Out DAC C

VOD DAC D Output

VSS Negative Power Supply

VRLC Voltage Reference Low Input Terminal DAC C

VRHC Voltage Reference High Input Terminal DAC C

VRLD Voltage Reference Low Input Terminal DAC D

VRHD Voltage Reference High Input Terminal DAC D

DGND Digital Ground

DVDD

LDAC DAC Register Load, active low level sensitive

RS Reset strobe

MSB Reset Mode: MSB=0 Code = 000

800

H

VL Logic Supply Voltage

W/R Write Read Mode select

CS Chip Select, active low

DB0 Data Bit 0

DB1 Data Bit 1

DB2 Data Bit 2

DB3 Data Bit 3

DB4 Data Bit 4

DB5 Data Bit 5

DB6 Data Bit 6

DB7 Data Bit 7

DB8 Data Bit 8

DB9 Data Bit 9

DB10 Data Bit 10

DB11 Data Bit 11

A0 Address Input 0

A1 Address Input 1

, MSB=1 Code

H

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future

manufacture unless otherwise agreed to in writing.

REV PrC, 23 APR '01 5

Page 6

PRELIMINARY TECHNICAL DATA

)

AD5582/AD5583

t

= 130ns

RCS

CS

t

R/W

A0/A1

=0

RDS

tAS=TBD

t

= 100ns max

CSD

HI-Z

DATA OUTPUT(READ TIMING

DATA VALIDDATA OUT

t

=TBD

RDH

tAH=0

tDZ= 100ns max

HI-Z

t

=TBD

WCS

CS

R/W

A0/A1

LDAC

DATA IN

RESET

t

RESET

tWS=TBD

tAS=0

tLS= 70ns

t

=0ns

WDS

= 50ns

tWH=0

tAH=0

tLH= 30ns

t

=0

WDH

t

LDW

= 50ns

DATA WRITE(INPUT AND OUTPUT REGISTERS)TIMING

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future

manufacture unless otherwise agreed to in writing.

REV PrC, 23 APR '01 6

Page 7

(

)

PRELIMINARY TECHNICAL DATA

AD5582/AD5583

t

ADDRESS

ONE

DATA1

VALID

CSP = 10nS

ADDRESS

TWO

DATA2

VALID

ADDRESS

THREE

DATA3

VALID

ADDRESS

FOUR

DATA4

VALID

tWH=0

tLH= 30ns

t

=0

WDH

CS

R/W

ADDRESS

LDAC

DATA IN

t

WCS = 30nS

tWS=0

tAS=0

tLS= 70ns

t

WDS

=0ns

CS

R/W

ADDRESS

LDAC

SING LE BUFFER MO DE

(OUTPUT UPDATED INDIVIDUALLY)

t

ONE

CSP = 10nS

ADDRESS

TWO

ADDRESS

THREE

t

WCS = 30nS

tWS=0

tAS=0

ADDRESS

t

= 0ns t

WDS

ADDRESS

FOUR

t

= 20ns

LDS

t

LDW

tWH=0

t

LDH

= 50ns

WDH

=30ns

=0

DATA IN

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future

manufacture unless otherwise agreed to in writing.

REV PrC, 23 APR '01 7

DATA1

VALID

OUTPUT UPDATED SIMULTANEOUSLY

DATA2

VALID

DOUBLE BUFFER MODE

DATA3

VALID

DATA4

VALID

Page 8

PRELIMINARY TECHNICAL DATA

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm)

AD5582/AD5583

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future

manufacture unless otherwise agreed to in writing.

REV PrC, 23 APR '01 8

Loading...

Loading...