Page 1

Current Output, Parallel Input, 16-/14-Bit

Multiplying DACs with 4-Quadrant Resistors

FEATURES

16-bit resolution

14-bit resolution

2- or 4-quadrant multiplying DAC

±1 LSB DNL

±1 LSB INL or ±2 LSB INL

Operating supply voltage: 2.7 V to 5.5 V

Low noise: 12 nV/√Hz

Low power: I

0.5 µs settling time

Built-in RFB facilitates current-to-voltage conversion

Built-in 4-quadrant resistors allow 0 V to –10 V, 0 V to +10 V,

or ±10 V outputs

2 mA full-scale current ±20%, with V

Automotive operating temperature: –40°C to +125°C

Compact TSSOP-28 package

APPLICATIONS

Automatic test equipment

Instrumentation

Digitally controlled calibration

Digital waveform generation

= 10 µA

DD

= 10 V

REF

AD5546/AD5556

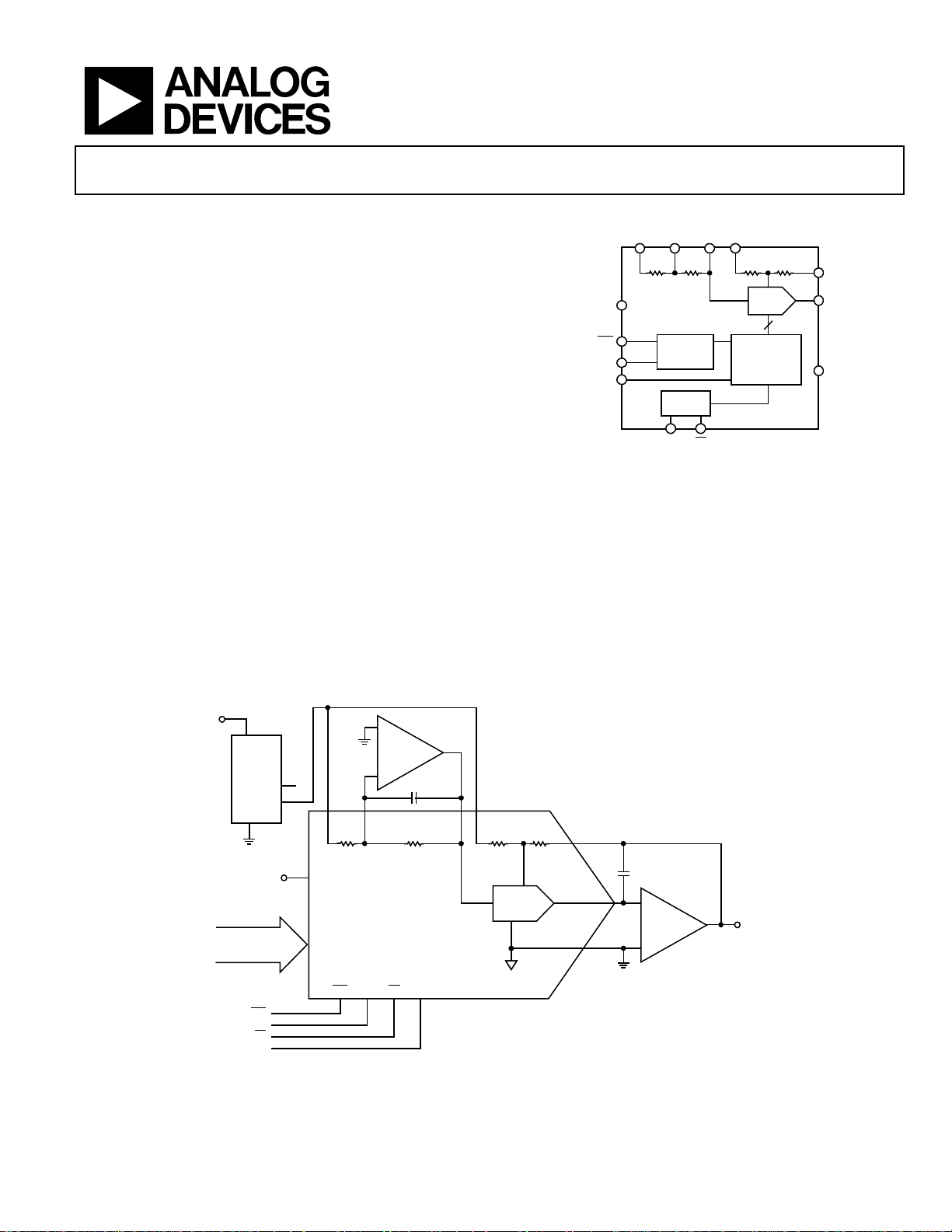

FUNCTIONAL BLOCK DIAGRAM

R1R

R1R

WR

AD5546/

DD

AD5556

V

LDAC

DB0–DB15

Figure 1. AD5546/AD5556 Simplified Block Diagram

GENERAL DESCRIPTION

The AD5546/AD5556 are precision 16-/14-bit, multiplying, low

power, current output, parallel input D/A converters. They

operate from a single 2.7 V to 5.5 V supply with ±10 V multiplying references for 4-quadrant outputs. Built-in 4-quadrant

resistors facilitate the resistance matching and temperature

tracking that minimize the number of components needed for

multiquadrant applications. The feedback resistor (R

fies the I-V conversion with an external buffer. The AD5546/

AD5556 are packaged in compact TSSOP-28 packages with

operating temperatures from –40°C to +125°C.

COM

2

CONTROL

LOGIC

POR

MSB RS

REF R

OFS

R

OFSRFB

16/14

REGISTER

DAC

DAC

R

FB

I

OUT

GND

03810-0-001

) simpli-

FB

5V

2

VIN

U3

ADR03

TRIM

VOUT

GND

4

5V VDD

16/14 DATA

LDAC

MSB

5

6

AD5546/AD5556

WRWRLDAC

+

U2A

OP2177

–

C1

–VREF +VREF

RCOMR1

R

1

U1

RSRSMSB

REF

R2

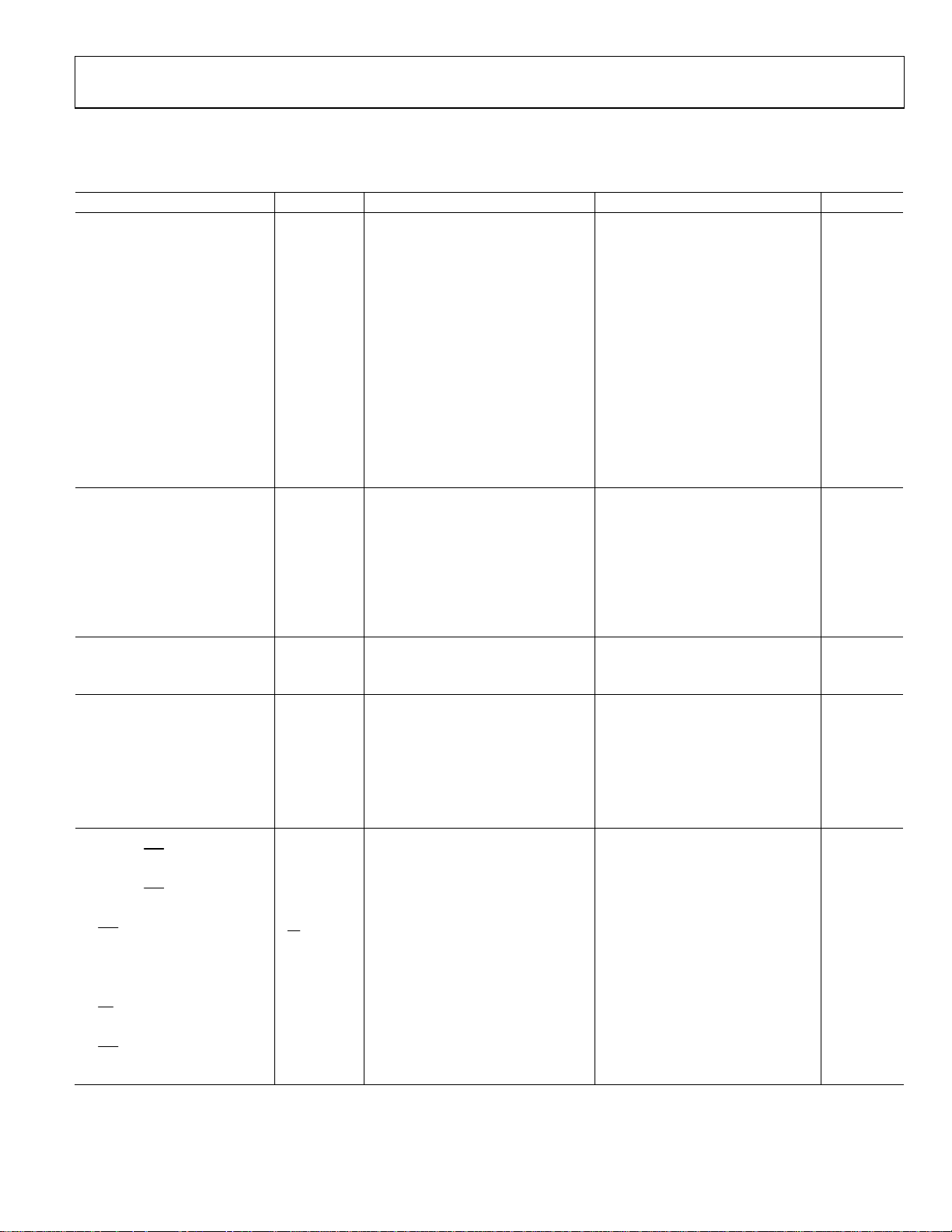

Figure 2. 16-/14-Bit, 4-Quadrant Multiplying DAC with a Minimum of External Components

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

ROF

RFB

ROFS

RFB

C2

16/14-BIT

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

IOUT

GND

–

U2B

OP2177

+

–VREF TO +VREF

VOUT

03810-0-002

www.analog.com

Page 2

AD5546/AD5556

TABLE OF CONTENTS

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 5

Pin Configurations and Functional Descriptions ........................ 6

Typical Performance Characteristics ............................................. 8

Circuit Operation ...........................................................................11

D/A Converter Section .............................................................. 11

Digital Section............................................................................. 12

ESD Protection Circuits............................................................. 12

Amplifier Selection..................................................................... 12

REVISION HISTORY

Revision 0: Initial Version

Reference Selection .................................................................... 12

Applications..................................................................................... 13

Unipolar Mode ........................................................................... 13

Bipolar Mode .............................................................................. 14

AC Reference Signal Attenuator ............................................... 15

System Calibration ..................................................................... 15

Outline Dimensions....................................................................... 16

Ordering Guide .......................................................................... 16

Rev. 0 | Page 2 of 16

Page 3

AD5546/AD5556

SPECIFICATIONS

Table 1. Electrical Characteristics. VDD = 2.7 V to 5.5 V, I

temperature range, unless otherwise noted.

Parameter Symbol Conditions Min Typ Max Unit

STATIC PERFORMANCE

Resolution N

Resolution N

1

AD5546, 1 LSB = V

V

= 10 V

REF

AD5556, 1 LSB = V

= 10 V

V

REF

Relative Accuracy INL Grade: AD5556C ±1 LSB

Relative Accuracy INL Grade: AD5546B ±2 LSB

Differential Nonlinearity DNL Monotonic ±1 LSB

Output Leakage Current I

Output Leakage Current I

Full-Scale Gain Error G

Bipolar Mode Gain Error G

Bipolar Mode Zero-Scale

OUT

OUT

FSE

E

G

ZSE

Data = zero scale, TA = 25°C 10 nA

Data = zero scale, TA = TA maximum 20 nA

Data = full scale ±1 ±4 mV

Data = full scale ±1 ±4 mV

Data = full scale ±1 ±2.5 mV

Error

Full-Scale Tempco2 TCV

FS

1 ppm/°C

REFERENCE INPUT

V

Range V

REF

REF

–18 +18 V

REF Input Resistance REF 4 5 6 kΩ

R1 and R2 Resistance R1 and R2 4 5 6 kΩ

R1-to-R2 Mismatch ∆(R1 to R2) ±0.5 ±1.5 Ω

R

Feedback and Offset

Resistance

Input Capacitance

2

, R

FB

OFS

C

REF

5 pF

ANALOG OUTPUT

Output Current I

Output Capacitance2 C

OUT

OUT

Data = full scale 2 mA

Code dependent 200 pF

LOGIC INPUT AND OUTPUT

Logic Input Low Voltage V

Logic Input Low Voltage V

Logic Input High Voltage V

Logic Input High Voltage V

Input Leakage Current I

IL

IL

IH

IH

IL

VDD = 5 V 0.8 V

VDD = 3 V 0.4 V

VDD = 5 V 2.4 V

VDD = 3 V 2.1 V

10 µA

Input Capacitance2 CIL 10 pF

, 3

INTERFACE TIMING

Data to WR Setup Time

V

Data to WR Hold Time

V

WR Pulse Width

V

LDAC Pulse Width t

V

RS Pulse Width

V

WR to LDAC Delay Time

V

2

t

t

t

t

t

DS

DH

WR

LDAC

RS

LWD

VDD = 5 V 20 ns

= 3 V 35 ns

DD

VDD = 5 V 0 ns

= 3 V 0 ns

DD

VDD = 5 V 20 ns

= 3 V 35 ns

DD

VDD = 5 V 20 ns

= 3 V 35 ns

DD

VDD = 5 V 20 ns

= 3 V 35 ns

DD

VDD = 5 V 0 ns

= 3 V 0 ns

DD

= virtual GND, GND = 0 V, V

OUT

/216 = 153 µV at

REF

/214 = 610 µV at

REF

= –10 V to 10 V, TA = full operating

REF

16 Bits

14 Bits

8 10 12 kΩ

Rev. 0 | Page 3 of 16

Page 4

AD5546/AD5556

Parameter Symbol Condition Min Typ Max Unit

SUPPLY CHARACTERISTICS

Power Supply Range V

Positive Supply Current I

Power Dissipation P

Power Supply Sensitivity P

AC CHARACTERISTICS

4

Output Voltage Settling

DD RANGE

DD

DISS

SS

t

S

Time

Reference Multiplying BW BW V

DAC Glitch Impulse Q V

Multiplying Feedthrough

V

OUT/VREFVREF

Error

Digital Feedthrough Q

D

Total Harmonic Distortion THD V

Output Noise Density e

N

1

All static performance tests (except I

tied to the amplifier output. The op amp +IN is grounded and the DAC I

2

These parameters are guaranteed by design and not subject to production testing.

3

All input control signals are specified with tR = tF = 2.5 ns (10% to 90% of 3 V), and timed from a voltage level of 1.5 V.

4

All ac characteristic tests are performed in a closed-loop system using an AD841 I-V converter amplifier.

) are performed in a closed-loop system, using an external precision OP97 I-V converter amplifier. The AD554x RFB terminal is

OUT

2.7 5.5 V

Logic inputs = 0 V 10 µA

Logic inputs = 0 V 0.055 mW

∆VDD = ±5% 0.003 %/%

To ±0.1% of full scale, data cycles from zero scale to full scale

0.5 µs

to zero scale

= 5 V p-p, data = full scale 4 MHz

REF

= 0 V, midscale to midscale minus 1 7 nV-s

REF

= 100 mV rms, f = 10 kHz –65 dB

WR = 1, LDAC toggles at 1MHz

= 5 V p-p, data = full-scale, f = 1 KHz –85 dB

REF

f = 1 kHz, BW = 1 Hz 12

7 nV-s

nV/rt

Hz

is tied to the op amp –IN. Typical values represent average readings measured at 25°C.

OUT

Rev. 0 | Page 4 of 16

Page 5

AD5546/AD5556

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

VDD to GND –0.3 V, +8 V

RFB, R

, R1, R

OFS

Logic Inputs to GND –0.3 V, +8 V

V(I

) to GND –0.3 V, VDD + 0.3 V

OUT

Input Current to Any Pin except Supplies ±50 mA

Thermal Resistance (θJA) 128°C

Maximum Junction Temperature (TJ

Operating Temperature Range –40°C to +125°C

Storage Temperature Range –65°C to +150°C

Lead Temperature:

Vapor Phase, 60 s 215°C

Infrared, 15 s 220°C

Package Power Dissipation (T

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

, and REF to GND –18 V, 18 V

COM

) 150°C

MAX

J MAX

– TA)/θ

JA

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those listed in the operational sections

of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rev. 0 | Page 5 of 16

Page 6

AD5546/AD5556

PIN CONFIGURATIONS AND FUNCTIONAL DESCRIPTIONS

D5

1

D7

D6

2

D5

3

4

D4

D3

5

D2

6

AD5546

D1

7

TOP VIEW

(Not to Scale)

8

D0

R

9

OFS

R

10

FB

11

R1

R

12

COM

REF

13

14

I

OUT

28

V

DD

D8

27

D9

26

25

D10

D11

24

D12

23

D13

22

21

D14

D15

20

GND

19

18

RS

MSB

17

WR

16

15

LDAC

03810-0-003

Figure 3.AD5546 Pin Configuration

1

2

D4

D3

3

4

D2

D1

5

D0

6

AD5556

7

NC

TOP VIEW

(Not to Scale)

NC

8

9

R

OFS

10

R

FB

R1

11

12

R

COM

REF

13

14

I

OUT

NC = NO CONNECT

Figure 4. AD5556 Pin Configuration

Table 3. AD5546 Functional Descriptions

Pin No. Mnemonic Description

1–8 D7 to D0 Digital Input Data Bits D7 to D0. Signal level must be ≤ V

9 R

OFS

Bipolar Offset Resistor. Accepts up to ±18 V. In 2-quadrant mode ties to RFB. In 4-quadrant mode ties to R1 and

+ 0.3 V.

DD

external reference.

10 R

FB

Internal Matching Feedback Resistor. Connects to the output of an external op amp for I-V conversion.

11 R1 4-Quandrant Resistor R1. In 2-quadrant mode shorts to REF pin. In 4-quadrant mode ties to R

12 R

COM

Center Tap Point of Two 4-Quadrant Resistors, R1 and R2. In 4-quadrant mode, ties to the inverting node of the

reference amplifier. In 2-quadrant mode, shorts to REF pin.

13 REF

DAC Reference Input in 2-Quadrant Mode and R2 Terminal in 4-Quadrant Mode. In 2-quadrant mode, this is the

reference input with constant input resistance versus code. In 4-quadrant mode, this pin is driven by the external

reference amplifier.

14 I

OUT

DAC Current Output. Connects to the inverting node of an external op amp for I-V conversion.

15 LDAC Digital Input Load DAC Control. Signal level must be ≤ VDD + 0.3 V.

16

WR Write Control Digital Input in Active Low. Transfers shift-register data to DAC register on rising edge. Signal level

must be ≤ V

+ 0.3 V.

DD

17 MSB Power-On Reset State. MSB = 0 resets at zero scale, MSB = 1 resets at midscale. Signal level must be ≤ VDD + 0.3 V.

18

RS Reset in Active Low. Resets to zero scale if MSB = 0, and resets to midscale if MSB = 1. Signal level must be

≤ V

+ 0.3 V.

DD

19 GND Analog and Digital Grounds.

20–21 D15 to D14 Digital Input Data Bits D15 to D14. Signal level must be ≤ V

+ 0.3 V.

DD

22–27 D13 to D8 Digital Input Data Bits D13 to D8. Signal level must be ≤ VDD + 0.3 V.

28 V

DD

Positive Power Supply Input. Specified range of operation: 2.7 V to 5.5 V.

Table 4. AD5556 Functional Descriptions

Pin No. Mnemonic Description

1–6 D5 to D0

Digital Input Data Bits D5 to D0. Signal level must be ≤ V

+0.3 V.

DD

7–8 NC No Connection. User should not connect anything other than dummy pads on these terminals.

9 R

OFS

Bipolar Offset Resistor. Accepts up to ±18 V. In 2-quadrant mode ties to RFB. In 4-quadrant mode ties to R1 and

external reference.

10 R

FB

Internal Matching Feedback Resistor. Connects to the output of an external op amp for I-V conversion.

11 R1 4-Quandrant Resistor R1. In 2-quadrant mode shorts to REF pin. In 4-quadrant mode ties to R

12 R

COM

Center Tap Point of Two 4-Quadrant Resistors, R1 and R2. In 4-quadrant mode, ties to the inverting node of the

reference amplifier. In 2-quadrant mode, shorts to REF pin.

13 REF

DAC Reference Input in 2-Quadrant Mode and R2 Terminal in 4-Quadrant Mode. In 2-quadrant mode, this is the

reference input with constant input resistance versus code. In 4-quadrant mode, this pin is driven by the external

reference amplifier.

14 I

OUT

DAC Current Output. Connects to the inverting node of an external op amp for I-V conversion.

28

V

DD

27

D6

D7

26

25

D8

D9

24

D10

23

22

D11

D12

21

20

D13

GND

19

RS

18

17

MSB

WR

16

LDAC

15

03810-0-004

.

OFS

.

OFS

Rev. 0 | Page 6 of 16

Page 7

AD5546/AD5556

Pin No. Mnemonic Description

15 LDAC

16

WR Write Control Digital Input in Active Low. Transfers shift-register data to DAC register on rising edge. Signal level

17 MSB

18

RS Reset in Active Low. Resets to zero-scale if MSB = 0 and resets to midscale if MSB = 1. Signal level must be

19 GND Analog and Digital Grounds.

20–27 D13 to D6

28 V

DD

Table 5. AD5546 Parallel Input Data Format

MSB LSB

Bit Position B15 B14 B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0

Data Word D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Table 6. AD5556 Parallel Input Data Format

MSB LSB

Bit Position B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0

Data Word D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Table 7. Control Inputs

RS WR

LDAC Register Operation

0 X X Reset output to 0, with MSB pin = 0. Midscale with MSB pin = 1.

1 0 0 Load input register with data bits.

1 1 1 Load DAC register with the contents of the input register.

1 0 1 Input and DAC registers are transparent.

1

1 1 0 No register operation.

Digital Input Load DAC Control. Signal level must be ≤ V

must be ≤ V

+ 0.3 V.

DD

+ 0.3 V.

DD

Power On Reset State. MSB = 0 resets at zero-scale, MSB = 1 resets at midscale. Signal level must be ≤ V

≤ VDD + 0.3 V.

Digital Input Data Bits D13 to D6. Signal level must be ≤ V

+ 0.3 V.

DD

Positive power supply input. Specified range of operation: 2.7 V to 5.5 V.

DH

t

LWD

t

LDAC

t

RS

03810-0-005

WR

DATA

LDAC

RS

When LDAC and

t

WR

t

DS

Figure 5. AD5546/AD5556 Timing Diagram

t

WR are tied together and programmed as a pulse, the data bits are loaded into the input register on

the falling edge of the pulse, and then loaded into the DAC register on the rising edge of the pulse.

+ 0.3 V.

DD

Rev. 0 | Page 7 of 16

Page 8

AD5546/AD5556

TYPICAL PERFORMANCE CHARACTERISTICS

1.0

0.8

0.6

0.4

0.2

0

INL (LSB)

–0.2

–0.4

–0.6

–0.8

–1.0

0 8192 16384 24576 32768 40960 49152 57344 65536

CODE (Decimal)

Figure 6. AD5546 Integral Nonlinearity Error

03810-0-006

1.0

0.8

0.6

0.4

0.2

0

DNL (LSB)

–0.2

–0.4

–0.6

–0.8

–1.0

0 0248 4096 6144 8192 10240 12288 14336 16384

CODE (Decimal)

Figure 9. AD5556 Differential Nonlinearity Error

03810-0-009

1.0

0.8

0.6

0.4

0.2

0

DNL (LSB)

–0.2

–0.4

–0.6

–0.8

–1.0

0 8192 16384 24576 32768 40960 49152 57344 65536

CODE (Decimal)

Figure 7. AD5546 Differential Nonlinearity Error

1.0

0.8

0.6

0.4

0.2

0

INL (LSB)

–0.2

–0.4

–0.6

–0.8

–1.0

0 2048 4096 6144 8192 10240 12288 14336 16384

CODE (Decimal)

Figure 8. AD5556 Integral Nonlinearity Error

03810-0-007

03810-0-008

1.5

V

=2.5V

REF

=25°C

T

A

1.0

0.5

INL

0

–0.5

LINEARITY ERROR (LSB)

–1.0

–1.5

24

SUPPLY VOLTAGE VDD (V)

Figure 10. Linearity Error vs. V

5

V

=5V

DD

T

=25° C

A

4

(LSB)

DD

3

2

SUPPLY CURRENT I

1

0

0 0.5 1.0 1.5 2.0 3.0 3.52.5 4.0 4.5 5.0

LOGIC INPUT VOLTAGE VIH (V)

DNL

GE

68

DD

Figure 11. Supply Current vs. Logic Input Voltage

03810-0-010

10

03810-0-011

Rev. 0 | Page 8 of 16

Page 9

AD5546/AD5556

3.0

2.5

LDAC (5V/DIV)

2.0

1.5

0x5555

0x8000

VDD=5V

V

=10V

REF

CODES 0x8000 ↔0x7FFF

1.0

SUPPLY CURRENT (mA)

0.5

0

10k 100k 1M 10M 100M

CLOCK FREQUENCY (Hz)

Figure 12. AD5546 Supply Current vs. Clock Frequency

90

80

70

60

50

40

PSSR (–dB)

30

20

10

0

10 100 1k 10k 100k 1M

FREQUENCY (Hz)

Figure 13. Power Supply Rejection Ratio vs. Frequency

0xFFFF

0x0000

03810-0-012

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

TIME (µ s)

V

OUT

03810-0-015

(50mV/DI V)

Figure 15. AD5546 Midscale Transition and Digital Feedthrough

VDD=5V± 10%

=10V

V

REF

0xFFFF

0x8000

0x4000

0x2000

0x1000

0x0800

0x0400

0x0200

0x0100

0x0080

0x0040

0x0020

0x0010

0x0008

0x0004

0x0002

0x0001

REF LEVEL

0.000dB

0x0000

03810-0-013

10 100 1k 100k10k 1M 10M

START 10.000Hz STOP 50 000 000.000Hz

Figure 16. AD5546 Unipolar Reference Multiplying Bandwidth

/DIV

12.000dB

MARKER 4 41 677.200Hz

MAG (A/R) –2.939db

–12dB

–24dB

–36dB

–48dB

–60dB

–72dB

–84dB

–96dB

–108dB

03810-0-016

1

2

CH1 5.00V CH2 2.00V M 200ns A CH1 2.70V

B CH1 –6.20V

400.00ns

Figure 14. Settling Time from Full Scale to Zero Scale

LDAC

V

OUT

03810-0-014

Rev. 0 | Page 9 of 16

REF LEVEL

0.000dB

0

–12

–24

–36

–48

–60

–72

–84

ALL BITS ON

D15 AND D14 ON

D15 AND D13 ON

D15 AND D12 ON

D15 AND D11 ON

D15 AND D10 ON

D15 AND D9 ON

D15 AND D8 ON

D15 AND D7 ON

D15 AND D6 ON

D15 AND D5 ON

D15 AND D4 ON

D15 AND D3 ON

D15 AND D2 ON

D15 AND D1 ON

/DIV

12.000dB

–96

D15 AND D0 ON

–108

D15 ON

–120

10 100 1k 100k10k 1M 10M

START 10.000Hz STOP 10 000 000.000Hz

Figure 17. AD5546 Bipolar Reference Multiplying Bandwidth

(Codes from Midscale to Full Scale)

03810-0-017

Page 10

AD5546/AD5556

REF LEVEL

0.000dB

0

ALL BITS OFF

D14 ON

–12

D14 AND D13 ON

D14 AND D12 ON

–24

D14 AND D11 ON

D14 AND D10 ON

–36

D14 AND D9 ON

D14 AND D8 ON

–48

D14 AND D7 ON

D14 AND D6 ON

–60

D14 AND D5 ON

D14 AND D4 ON

–72

D14 AND D3 ON

D14 AND D2 ON

–84

D14 AND D1 ON

–96

D14 AND D0 ON

–108

D14 ON

–120

10 100 1k 100k10k 1M 10M

START 10.000Hz STOP 10 000 000.000Hz

/DIV

12.000dB

Figure 18. AD5546 Bipolar Reference Multiplying Bandwidth

(Codes from Midscale to Zero Scale)

03810-0-018

Rev. 0 | Page 10 of 16

Page 11

AD5546/AD5556

CIRCUIT OPERATION

D/A CONVERTER SECTION

The AD5546/AD5556 are 16-/14-bit multiplying, current output, and parallel input DACs. The devices operate from a single

R

40kΩ

80kΩ

, or

REF

40kΩ

2R

80kΩ

2.7 V to 5.5 V supply, and provide both unipolar 0 V to –V

0 V to +V

, and bipolar ±V

REF

output ranges from a –18 V to

REF

+18 V reference. In addition to the precision conversion RFB

commonly found in current output DACs, there are three additional precision resistors for 4-quadrant bipolar applications.

The AD5546/AD5556 consist of two groups of precision R-2R

ladders, which make up the 12/10 LSBs, respectively. Furthermore, the four MSBs are decoded into 15 segments of resistor

value 2R. Figure 19 shows the architecture of the 16-bit

AD5546. Each of the 16 segments in the R-2R ladder carries an

equally weighted current of one-sixteenth of full scale. The

feedback resistor, R

, and 4-quadrant resistor, R

FB

, have values

OFS

of 10 kΩ. Each 4-quadrant resistor, R1 and R2, equals 5 kΩ. In

4-quadrant operation, R1, R2, and an external op amp work

together to invert the reference voltage and apply it to the REF

input. With R

output can swing from –V

and RFB connected as shown in Figure 2, the

OFS

REF

to +V

REF

.

REF

RCOM

R1

5kΩ

5kΩ

R2

R1

2R

80kΩ2R80kΩ2R80kΩ

R

R

40kΩ

40kΩ

2R

2R

80kΩ

80kΩ

R

2R

The reference voltage inputs exhibit a constant input resistance

of 5 kΩ ±20%. The DAC output, I

, impedance is code depen-

OUT

dent. External amplifier choice should take into account the

variation of the AD5546/AD5556 output impedance. The

feedback resistance in parallel with the DAC ladder resistance

dominates output voltage noise. To maintain good analog

performance, it is recommended to bypass the power supply

with a 0.01 µF to 0.1 µF ceramic or chip capacitor in parallel

with a 1 µF tantulum capacitor. Also, to minimize gain error,

PCB metal traces between V

and RFB should match.

REF

Every code change of the DAC corresponds to a step function;

gain peaking at each output step may occur if the op amp has

limited GBP and excessive parasitic capacitance present at the

op amp inverting node. A compensation capacitor, therefore,

may be needed between the I-V op amp inverting and output

nodes to smooth the step transition. Such a compensation

capacitor should be found empirically, but a 20 pF capacitor is

generally adequate for the compensation.

The V

power is used primarily by the internal logic and to

DD

drive the DAC switches. Note that the output precision degrades

if the operating voltage falls below the specified voltage. Users

should also avoid using switching regulators because device

power supply rejection degrades at higher frequencies.

2R

80kΩ

4 MSB

15 SEGMENTS

R

40kΩ

2R

80kΩ

R

40kΩ

80kΩ

2R

R

40kΩ

2R

80kΩ

R

40kΩ

80kΩ

2R

2R

80kΩ

8-BIT R2R

RA

R

R

R

R

2R

2R

2R

2R

80kΩ

2R

80kΩ

4-BIT R2R

RS

RS

10kΩ 10kΩ

RS

LDAC

WR

RB

80kΩ

80kΩ

80kΩ

16 8 4

ADDRESS DECODER

LDAC

WR

D15 D14 D0

DAC REGISTER

INPUT REGISTER

Figure 19. 16-Bit AD5546 Equivalent R-2R DAC Circuit with Digital Section

ROFS

RFB

IOUT

GND

03810-0-019

Rev. 0 | Page 11 of 16

Page 12

AD5546/AD5556

V

DIGITAL SECTION

The AD5546/AD5556 have 16-/14-bit parallel inputs. The

devices are double-buffered with 16-/14-bit registers. The

double-buffered feature allows the update of several AD5546/

AD5556 simultaneously. For AD5546, the input register is

loaded directly from a 16-bit controller bus when the

brought low. The DAC register is updated with data from the

input register when LDAC is brought high. Updating the DAC

register updates the DAC output with the new data (see

Figure 19). To make both registers transparent, tie

LDAC high. The asynchronous

pin resets the part to zero

RS

scale if MSB pin = 0, and midscale if MSB pin = 1.

ESD PROTECTION CIRCUITS

All logic input pins contain back-biased ESD protection Zeners

connected to ground (GND) and V

a result, the voltage level of the logic input should not be greater

than the supply voltage.

DD

DIGITAL

INPUTS

5kΩ

Figure 20. Equivalent ESD Protection Circuits

, as shown in Figure 20. As

DD

DGND

03810-0-020

WR

WR

pin is

low and

AMPLIFIER SELECTION

In addition to offset voltage, the bias current is important in op

amp selection for precision current output DACs. An input bias

current of 30 nA in the op amp contributes to 1 LSB in the

AD5546’s full-scale error. Op amps OP1177 and AD8628 are

good candidates for the I-V conversion.

REFERENCE SELECTION

The initial accuracy and the rated output of the voltage reference determine the full span adjustment. The initial accuracy is

usually a secondary concern in precision, as it can be trimmed.

Figure 25 shows an example of a trimming circuit. The zero

scale error can also be minimized by standard op amp nulling

techniques.

The voltage reference temperature coefficient and long-term

drift are primary considerations. For example, a 5 V reference

with a TC of 5 ppm/

per degree Celsius. As a result, the reference that operates at

o

C contributes an additional 750 µV full-scale error.

55

Similarly, the same 5 V reference with a ±50 ppm long-term

drift means that the output may change by ±250 µV over time.

Therefore, it is practical to calibrate a system periodically to

maintain its optimum precision.

o

C means that the output changes by 25 µV

Rev. 0 | Page 12 of 16

Page 13

AD5546/AD5556

APPLICATIONS

UNIPOLAR MODE

2-Quadrant Multiplying Mode, V

The AD5546/AD5556 DAC architecture uses a current-steering

R-2R ladder design that requires an external reference and op

amp to convert the unipolar mode of output voltage to

= –V

V

OUT

V

= –V

OUT

× D/65,536 (AD5546) (1)

REF

× D/16,384 (AD5556) (2)

REF

where D is the decimal equivalent of the input code.

The output voltage polarity is opposite to the V

this case (see Figure 21). Table 8 shows the negative output

versus code for the AD5546.

Table 8. AD5546 Unipolar Mode Negative Output vs. Code

D in Binary V

OUT

1111 1111 1111 1111 –V

1000 0000 0000 0000 –V

0000 0000 0000 0001 –V

0000 0000 0000 0000 0

+5V

0.1µF

C2

0.1µF

16/14 DATA

C1

1µF

= 0 V to –V

OUT

(V)

(65,535/65,536)

REF

/2

REF

(1/65,536)

REF

2

VIN

U3

ADR03

5

TRIM

VOUT

GND

4

C3

REF

polarity in

REF

RCOMR1

R

1

VDD

U1

AD5546/AD5556

R2

REF

2-Quadrant Multiplying Mode, V

The AD5546/AD5556 are designed to operate with either

positive or negative reference voltages. As a result, positive

output can be achieved with an additional op amp, (see

Figure 22), and the output becomes

V

= +V

OUT

= +V

V

OUT

× D/65,536 (AD5546) (3)

REF

× D/16,384 (AD5556) (4)

REF

Table 9 shows the positive output versus code for the AD5546.

Table 9. AD5546 Unipolar Mode Positive Output vs. Code

D in Binary V

1111 1111 1111 1111 +V

1000 0000 0000 0000 +V

0000 0000 0000 0001 +V

OUT

REF

REF

REF

0000 0000 0000 0000 0

ROFS

ROFS

16/14-BIT

RFB

RFB

GND

IOUT

C6

2.2pF

–

AD8628

+

V+

U2

V–

0.1µF

= 0 V to +V

OUT

(V)

(65,535/65,536)

/2

(1/65,536)

VOUT

–2.5V TO 0V

C4

REF

WRWRLDAC

LDAC

MSB

Figure 21. Unipolar 2-Quadrant Multiplying Mode, V

RSRSMSB

= 0 to –V

OUT

C5

1µF

–5V

03810-0-021

REF

Rev. 0 | Page 13 of 16

Page 14

AD5546/AD5556

+5V

C1

1µF

0.1µF

C2

2

VIN

U3

ADR03

TRIM

VOUT

GND

4

C3

0.1µF

16/14 DATA

5

+2.5V

6

R

1

VDD

AD5546/AD5556

+

AD8628

–

RCOMAR1A

U1

V+

V–

–5V

U2A

0.1µF

C7

R2

C8

C9

1µF

REFA

–2.5V

ROFSA

ROFS

16/14-BIT

RFBA

RFB

GND

IOUT

C6

–

AD8628

+

+5V

V+

V–

U2B

C4

1µF

C5

0.1µF

VOUT

0V TO +2.5V

WRWRLDAC

LDAC

MSB

RSRSMSB

Figure 22. Unipolar 2-Quadrant Multiplying Mode, V

+15V

1µF

C2

C1

0.1µF

+5V

C3

0.1µF

2

VIN

U3

ADR01

TRIM

VOUT

GND

4

+

U2A

AD8512

5

6

VDD

–

RCOMR1

R

1

U1

AD5546/AD5556

16/14 DATA

WRWRLDAC

LDAC

MSB

RSRSMSB

Figure 23. 4-Quadrant Multiplying Mode, V

BIPOLAR MODE

4-Quadrant Multiplying Mode, V

The AD5546/AD5556 contain on-chip all the 4-quadrant

resistors necessary for the precision bipolar multiplying

operation. Such a feature minimizes the number of exponent

components to only a voltage reference, dual op amp, and

compensation capacitor (see Figure 23). For example, with a

OUT

= –V

REF

to +V

REF

03810-0-022

= 0 to +V

OUT

REF

REF

+10V–10V

ROF

ROFS

16/14-BIT

OUT

RFB

RFB

= –V

GND

REF

IOUT

to +V

REF

C9

–

AD8512

+

+15V

V+

U2B

V–

–15V

C4

1µF

C5

0.1µF

C6

0.1µF

C7

1µF

VOUT

–10V TO +10V

03810-0-023

C8

R2

10 V reference, the circuit yields a precision, bipolar –10 V to

+10 V output.

V

= (D/32768 − 1) × V

OUT

= (D/16384 − 1) × V

V

OUT

(AD5546) (5)

REF

(AD5556) (6)

REF

Rev. 0 | Page 14 of 16

Page 15

AD5546/AD5556

Table 10 shows some of the results for the 16-bit AD5546.

Table 10. AD5546 Output vs. Code

D in Binary V

1111 1111 1111 1111 +V

1000 0000 0000 0001 +V

OUT

(32,767/32,768)

REF

(1/32,768)

REF

1000 0000 0000 0000 0

0111 1111 1111 1111 –V

0000 0000 0000 0000 –V

(1/32,768)

REF

REF

AC REFERENCE SIGNAL ATTENUATOR

Besides handling digital waveforms decoded from parallel input

data, the AD5546/AD5556 handle equally well low frequency

+

U2A

OP2177

–

C7

RCOMAR1A

VREFA

R2R1

U1

RSRSMSB

Figure 24. Signal Attenuator with AC Reference

+

U4

AD5170

10kΩ

B

R7

1kΩ

+2.5V

VDD

AD5546/AD5556

AD8628

–

RCOMAR1A

U1

V+

U2A

V–

–5V

+5V

1µF

+10V

–10V

+5V

1µF

C1

0.1µF

VDD

C2

AD5546/AD5556

16/14 DATA

WRWRLDAC

LDAC

MSB

2

VIN

C1

C2

0.1µF

U3

ADR03

TRIM

VOUT

GND

4

R3

470kΩ

5

6

C3

0.1µF

16/14 DATA

0.1µF

R2R1

C8

C9

1µF

C7

ac reference signals for signal attenuation, channel equalization,

and waveform generation applications. The maximum signal

range can be up to ±18 V (see Figure 24).

SYSTEM CALIBRATION

The initial accuracy of the system can be adjusted by trimming

the voltage reference ADR0x with a digital potentiometer (see

Figure 25). The AD5170 provides an OTP (one time programmable), 8-bit adjustment that is ideal and reliable for such calibration. ADI’s OTP digital potentiometer comes with programmable software that simplifies the factory calibration process.

ROFSA

ROFS

VREFA

RFBA

16/14-BIT

–2.5V

ROFSA

RFB

ROFS

16/14-BIT

IOUT

GND

RFBA

RFB

GND

IOUT

+15V

C6

–

OP2177

+

–15V

V+

U2B

V–

C4

1µF

C5

0.1µF

C8

1µF

C9

0.1µF

C6

+5V

–

V+

U2B

AD8628

V–

+

C4

1µF

C5

0.1µF

VOUT

03810-0-024

0V TO +2.5V

VOUT

LDAC

MSB

WRWRLDAC

RSRSMSB

Figure 25. Full Span Calibration

Rev. 0 | Page 15 of 16

03810-0-025

Page 16

AD5546/AD5556

OUTLINE DIMENSIONS

9.80

9.70

9.60

28

PIN 1

0.65

0.15

0.05

COPLANARITY

0.10

BSC

0.30

0.19

COMPLIANT TO JEDEC STANDARDS MO-153AE

Figure 26. 28-Lead Thin Shrink Small Outline Package [TSSOP]

1.20 MAX

SEATING

PLANE

15

4.50

4.40

4.30

0.20

0.09

6.40 BSC

8°

0°

0.75

0.60

0.45

141

RU-28

Dimensions shown in millimeters

ORDERING GUIDE

Temperature

Model RES (Bit) DNL (LSB) INL (LSB)

Range (°C)

AD5546BRU 16 ±1 ±2 –40 to +125 50 TSSOP-28 RU-28

AD5546BRU-REEL7 16 ±1 ±2 –40 to +125 1000 TSSOP-28 RU-28

AD5556CRU 14 ±1 ±1 –40 to +125 50 TSSOP-28 RU-28

AD5556CRU-REEL7 14 ±1 ±1 –40 to +125 1000 TSSOP-28 RU-28

Ordering

Quantity

Package

Description

Package

Option

© 2004 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D03810-0-1/04(0)

Rev. 0 | Page 16 of 16

Loading...

Loading...