Page 1

High-Performance Driver/Comparator

a

FEATURES

250 MHz Operation

Driver/Comparator and Active Load Included

On-Chip Schottky Diode Bridge

52-Lead LQFP Package with Built-In Heat Sink

APPLICATIONS

Automatic Test Equipment

Semiconductor Test Systems

Board Test Systems

Instrumentation and Characterization Equipment

PRODUCT DESCRIPTION

The AD53509 is a single chip that performs the pin electronics

functions of driver, comparator and active load in ATE VLSI

and memory testers. In addition, a Schottky diode bridge for the

active load and a VCOM buffer are included internally.

The driver is a proprietary design that features three active

states: Data High Mode, Data Low Mode and Term Mode as

well as an Inhibit State. This facilitates the implementation of

high speed active termination. The output voltage range is –2 V

to +7 V to accommodate a wide variety of test devices. The

output leakage is typically less than 250 nA over the entire signal range.

The dual comparator, with an input range equal to the driver

output range, features built-in latches and ECL-compatible

outputs. The outputs are capable of driving 50 Ω signal lines

terminated to –2 V. Signal tracking capability is upwards of

5 V/ns.

The active load can be set for up to 40 mA load current with

less than a 10 µA linearity error through the entire set range.

I

, IOL and the buffered VCOM are independently adjustable.

OH

On-board Schottky diodes provide high speed switching and low

capacitance.

Also included on the chip is an on-board temperature sensor

whose purpose is to give an indication of the surface temperature of the DCL. This information can be used to measure θ

and θJA or flag an alarm if proper cooling is lost. Output from

the sensor is a current sink that is proportional to absolute temperature. The gain is trimmed to a nominal value of 1.0 µA/K.

As an example, the output current can be sensed by using a

10 kΩ resistor connected from 10 V to the THERM (IOUT) pin.

A voltage drop across the resistor will be developed that equals:

10K × 1 µA/K = 10 mV/K = 2.98 V at room temperature.

JC

Active Load on a Single Chip

AD53509

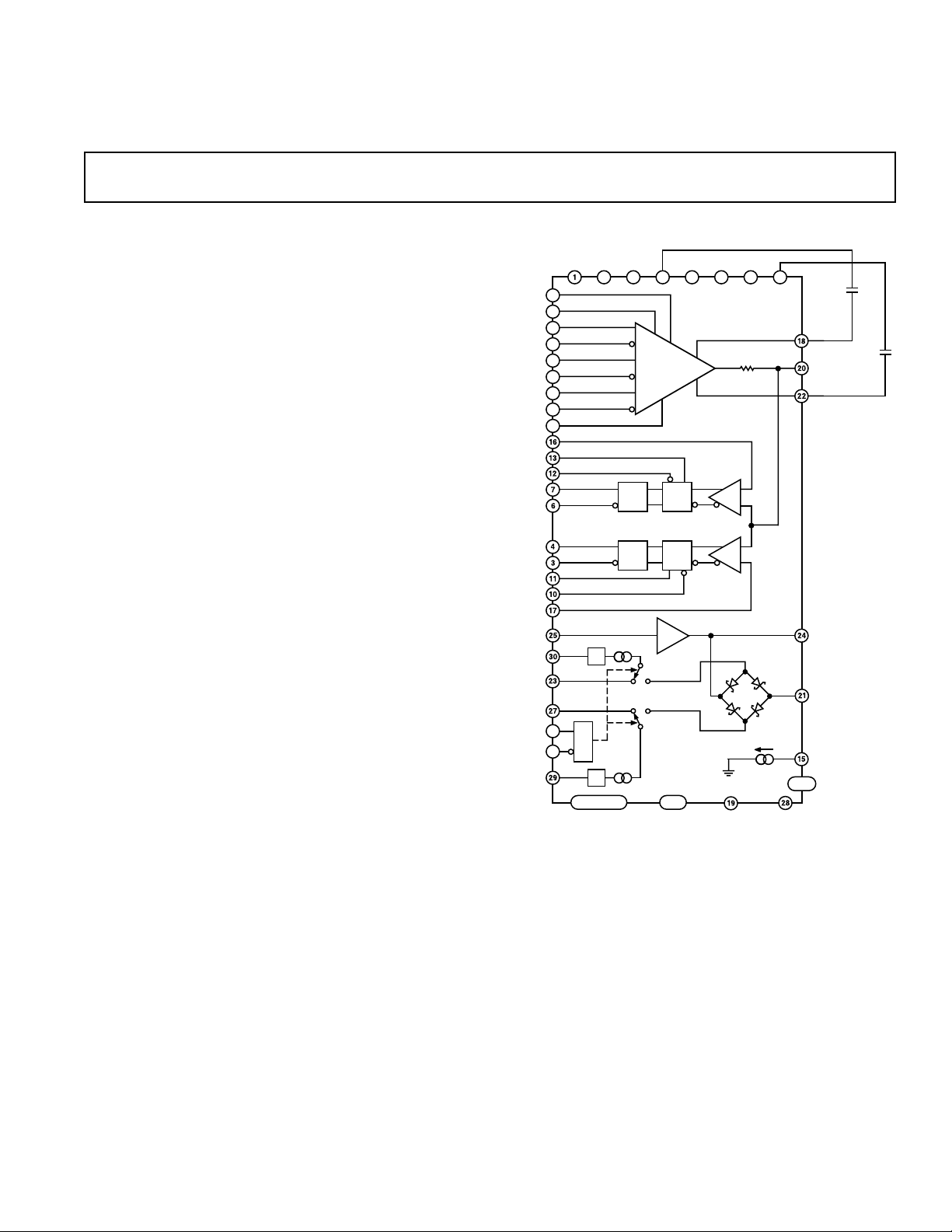

FUNCTIONAL BLOCK DIAGRAM

V

VEEVEEVEEV

CC

CC

51 52 39 40 41 32

34

EE

AD53509

DRIVER

COMPARATOR

ACTIVE LOAD

+1

2,5,89,33,44,46,48

VCCO

NC = NO CONNECT

46

1.0A/K

HQGND2 HQGND

14, 26

CHDCPL

VHDCPL

V

OUT

VLDCPL

VCOMS

OUT_L

THERM

VH

VTERM

DATA

DATA

IOD

IOD

RLD

RLD

HCOMP

LEH

LEH

QH

QH

QL

QL

LEL

LEL

LCOMP

VCOMI

IOLC

IOLRTN

IOHRTN

INHL

INHL

IOHC

V

L

VCCVCCV

47

45

37

38

43

42

49

50

31

V/I

36

35

V/I

PWRGND

39nF

NC

39nF

CLDCPL

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

Page 2

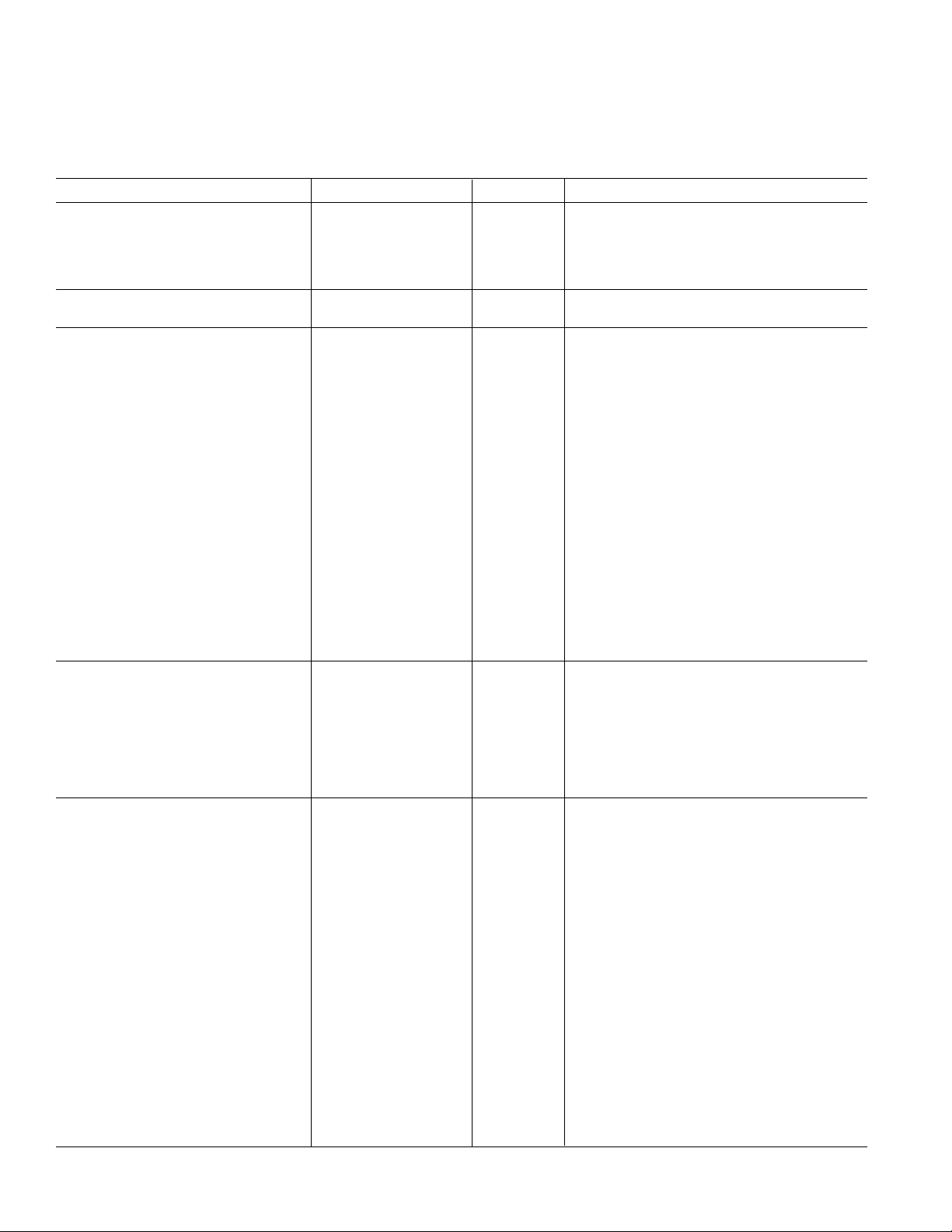

AD53509–SPECIFICATIONS

DRIVER SPECIFICATIONS

(All specifications are at TJ = 85C 5C, VS = 11 V 3%, –VS = –6 V = 3% unless otherwise noted. All temperature coefficients are

measured at TJ = 75C to 95C.)

Parameter Min Typ Max Unit Test Conditions

DIFFERENTIAL INPUT CHARACTERISTICS

(DATA to DATA, IOD to IOD, RLD to RLD)

Input Voltage –2 +3 V

Differential Input Range 2 V All Digital Inputs Within a 2 V Range

Bias Current –250 +250 µAV

REFERENCE INPUTS

Bias Currents –50 +50 µAV

OUTPUT CHARACTERISTICS

Logic High Range –2 +7 V DATA = H, VH = –2 V to +7 V, VL = –2 V, VT = 0 V

Logic Low Range –2 +6 V DATA = L, VL = –2 V to +6 V, VH = 7 V, VT = 0 V

Amplitude (V

and VL) 0.1 9 V VL = 0.0 V, VH = 0.1 V, VT = 0 V

H

Absolute Accuracy V

VH Offset –50 +50 mV DATA = H, VH = 0 V, VL = –2 V, VT = –1 V

VH Gain + Linearity Error 0.3 – 5 +0.3 + 5 % of VH + mV DATA = H, VH = –1 V to +7 V, VL = –2 V, VT = –2 V

VL Offset –50 +50 mV DATA = L, VL = 0 V, VH = 5 V, VT = 3 V

VL Gain + Linearity Error –0.3 – 5 +0.3 + 5 % of VL + mV DATA = L, VL = –2 V to +6 V, VH = 7 V, VT = 7 V

Offset TC 0.5 mV/°CV

Output Resistance

VH = –2 V 44 46 48 Ω VL = –2 V, VT = 0 V, I

VH = +7 V 44 46 48 Ω VL = –1 V, VT = 0 V, I

VL = –2 V 44 46 48 Ω VH = 6 V, VT = 0 V, I

VL = +6 V 44 46 48 Ω VH = 7 V, VT = 0 V, I

VH = +3 V 46 Ω VL = 0 V, VT = 0 V, I

Dynamic Current Limit >100 mA C

Static Current Limit –85 +85 mA Output to –2 V, VH = 7 V, VL = –1 V, VT = 0 V

V

ERM

T

Voltage Range –2 +7 V TERM MODE, VT = –2 V to +7 V, VL = 0 V, VH = 3 V

V

Offset –50 +50 mV TERM MODE, VT = 0 V, VL = 0 V, VH = 3 V

ERM

T

V

Gain + Linearity Error –0.3 +10 +0.3 +10 % of V

ERM

T

+ mV TERM MODE, VT = –2 V to +7 V, VL = 0 V, VH = 3 V

SET

Offset TC 0.5 mV/°CV

Output Resistance 44 46 49 Ω I

DYNAMIC PERFORMANCE, (VH AND VL)

Propagation Delay Time 1.5 ns Measured at 50%, VH = +400 mV, VL = –400 mV,

Propagation Delay TC 2 ps/°C Measured at 50%, VH = +400 mV, VL = –400 mV,

Delay Matching, Edge to Edge <100 ps Measured at 50%, VH = +400 mV, VL = –400 mV,

Rise and Fall Times

1 V Swing 0.42 ns Measured 20%–80%, VL = 0 V, VH = 1 V, VT = 0 V

3 V Swing 0.75 ns Measured 20%–80%, VL = 0 V, VH = 3 V, VT = 0 V

5 V Swing 1.65 ns Measured 10%–90%, VL = 0 V, VH = 5 V, VT = 0 V

9 V Swing 3.0 ns Measured 10%–90%, VL = –2 V, VH = 7 V, VT = 0 V

Rise and Fall Time Temperature Coefficient

1 V Swing ±1 ps/°C Measured 20%–80%, VL = 0 V, VH = 1 V

3 V Swing ±2 ps/°C Measured 20%–80%, VL = 0 V, VH = 3 V

5 V Swing ±4 ps/°C Measured 10%–90%, VL = 0 V, VH = 5 V

Overshoot and Preshoot <3 + 50 % of Step + mV VL, VH = –0.1 V, 0.1 V, VL, VH = 0.0 V, 1.0 V

Settling Time

to 15 mV <50 ns VL = 0 V, VH = 0.5 V, VT = –2 V

to 4 mV <10 µsV

= –2 V, +3 V

IN

, VH, VT = 5 V

L

= –2 V, VH = +7 V, VT = 0 V

L

= –2 V, VH = 0 V, VT = –1 V (VH Offset)

L

VL = 0 V, VH = 5 V, VT = 3 V (VL Offset)

= 0, +1, +30 mA

OUT

= 0, –1, –30 mA

OUT

= 0, 1, 30 mA

OUT

= 0, –1, –30 mA

OUT

= –30 mA (Trim Point)

= 39 nF, VH = 6 V, VL = –2 V, VT = 0 V

BYP

OUT

DATA = H and Output to 7 V, VH = 6 V,

VL = –2 V, VT = 0 V, DATA = L

= 0 V, VL = 0 V, VH = 3 V

T

= +30 mA, +1.0 mA, VT = –2.0 V, VH = 3 V, VL = 0 V

OUT

I

= –30 mA, –1.0 mA, VT = +7.0 V, VH = 3 V, VL = 0 V

OUT

I

= ±30 mA, ±1.0 mA, VT = 0 V, VH = 3 V, VL = 0 V

OUT

VT = 0 V

VT = 0 V

VT = 0 V

VL, VH = 0.0 V, 3.0 V, VL, VH = 0.0 V, 5.0 V

VL, VH = –2.0 V, 7.0 V

= 0 V, VH = 0.5 V, VT = –2 V

L

–2–

REV. A

Page 3

AD53509

Parameter Min Typ Max Unit Test Conditions

Delay Change vs. Pulsewidth 50 ps V

= 0 V, VH = 2 V, Pulsewidth = 2.5 ns/7.5 ns, 30 ns/90 ns

L

Minimum Pulsewidth

3 V Swing 1.4 ns V

5 V Swing 2.0 ns V

= 0 V, VH = 3 V, 90% (2.7 V) Reached, Measure @ 50%

L

= 0 V, VH = 5 V, 90% (4.5 V) Reached, Measure @ 50%

L

Toggle Rate 250 MHz VL = 0 V, VH = 5 V, VDUT > 3.0 V p-p

DYNAMIC PERFORMANCE, INHIBIT

Delay Time, Active to Inhibit 3.3 ns Measured at 50%, VH = +2 V, VL = –2 V, VT = 0 V

Delay Time, Inhibit to Active 2.9 ns Measured at 50%, V

= +2 V, VL = –2 V, VT = 0 V

H

Delay Time Matching (Z) <2 ns Z = Delay Time Active to Inhibit Test (Above)—

Delay Time Inhibit to Active Test (Above)

(Of Worst Two Edges)

I/O Spike 150 mV, p-p VH = 0 V, VL = 0 V, VT = 0 V

Rise, Fall Time, Active to Inhibit 1.6 ns V

= +2 V, VL = –2 V (Measured 20%/80% of 1 V Output)

H

Rise, Fall Time, Inhibit to Active 1.4 ns VH = +2 V, VL = –2 V (Measured 20%/80% of 1 V Output)

DYNAMIC PERFORMANCE , V

Delay Time, VH to V

Delay Time, V

to VH and V

TERM

TERM

Overshoot and Preshoot <3.0 + 75 % of Step + mV VH/VL, V

, VL to V

TERM

TERM

TERM

to V

2.5 ns Measured at 50%, VL = –1 V, VH = +1 V, V

L

2.5 ns Measured at 50%, VL = VH = +0.4 V, V

= (0 V, –1 V), (0 V, –2.0 V),

TERM

TERM

= 0 V

TERM

= –0.4 V

(0 V, 6.0 V)

V

Mode Rise Time 2.2 ns VL = –2 V, VH = +2 V, V

TERM

V

Mode Fall Time 2.2 ns VL = –2 V, VH = +2 V, V

TERM

= 0 V, 20%–80%

TERM

= 0 V, 20%–80%

TERM

PSRR, DRIVE or TERM Mode 35 dB VS = VS ± 3%

Specifications subject to change without notice.

COMPARATOR SPECIFICATIONS

(All specifications are at TJ = 85C 5C. [Outputs terminated in 150 to GND, +VS = 11 V 3% –VS = 6 V 3%, VCCO = 3.3 V unless

otherwise specified.] All temperatures coefficients are measured at TJ = 75C to 95C.)

Parameter Min Typ Max Unit Test Conditions

DC INPUT CHARACTERISTICS

Offset Voltage (VOS) –25 +25 mV CMV = 0 V

Offset Voltage (Drift) 50 µV/°C CMV = 0 V

HCOMP, LCOMP Bias Current –50 +50 µAV

= 0 V

IN

Voltage Range (VCM) –2 +7.0 V

Differential Voltage (V

) 9.0 V

DIFF

Gain and Linearity –0.05 +0.05 % FSR VIN = –2 V to +7 V (9 V FSR)

LATCH ENABLE INPUTS

Logic “1” Current (IIH) 250 µA LEA, LEA, LEB, LEB = +3 V

Logic “0” Current (IIL) –250 µA LEA, LEA, LEB, LEB = –2 V

Logic Input Range –2 +3 V

DIGITAL OUTPUTS

Logic “1” Voltage (VOH) VCCO – 0.98 V Q or Q, 16.7 mA Load

Logic “0” Voltage (VOL) VCCO – 1.5 V Q or Q, 10 mA Load

Slew Rate 1 V/ns

VCCO Range 0 8 V

SWITCHING PERFORMANCE

Propagation Delay

Input to Output 1.8 ns VIN = 2 V p-p,

Latch Enable to Output 2 ns HCOMP = 1 V, LCOMP = 1 V

Propagation Delay Temperature Coefficient 2 ps/°C

Propagation Delay Change with Respect to

Slew Rate: 0.5 V, 1.0 V, 3.0 V/ns <± 100 ps VIN = 0 V to 5 V

Slew Rate: 5.0 V/ns <±350 ps VIN = 0 V to 5 V

Amplitude: 1.0 V, 3.0 V, 5.0 V <± 200 ps VIN = 1.0 V/ns

Equivalent Input Rise Time 450 ps VIN = 0 V to 3 V, 3 V/ns

Pulsewidth Linearity <±200 ps VIN = 0 V to 3 V, 3 V/ns, PW = 3 ns–8 ns

Settling Time 25 ns Settling to ±8 mV, VIN = 1 V to 0 V

Latch Timing

Input Pulsewidth 1.68 ns

Setup Time 1.0 ns

Hold Time 1.1 ns

Hysteresis 6 mV Latch Inputs Programmed for Hysteresis

Specifications subject to change without notice.

–3–REV. A

Page 4

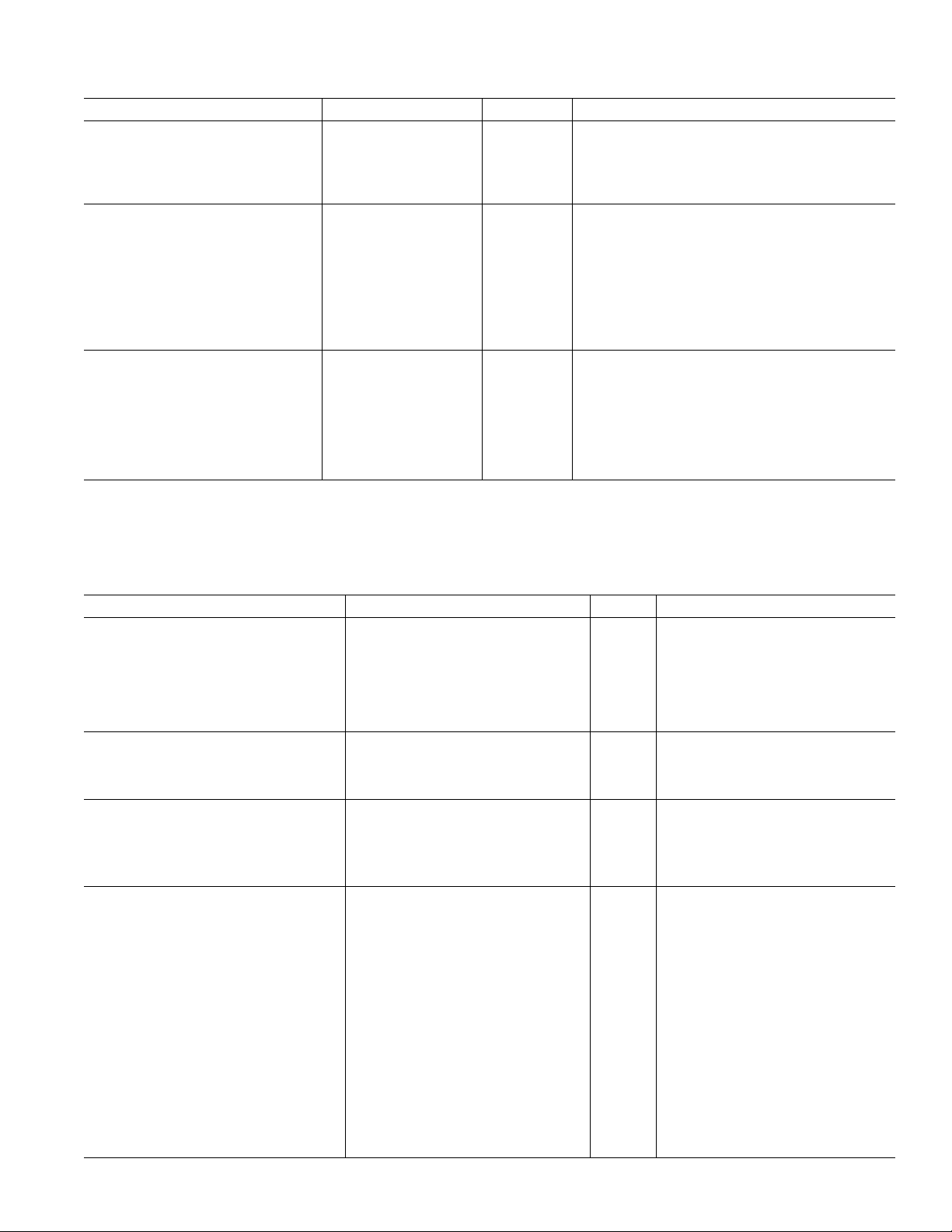

AD53509–SPECIFICATIONS

ACTIVE LOAD SPECIFICATIONS

(All specifications are at TJ = 85C 5C, +VS = 11 V 3%, –VS = –6 V = 3% unless otherwise noted. All temperature coefficients are

measured at TJ = 75C to 95C.)

Parameter Min Typ Max Unit Test Conditions

INPUT CHARACTERISTICS

INHL, INHL

Input Voltage –2 +3 V IOHC = 1 V, IOLC = 1 V, VCOM = 2 V, OUT_L = 0 V

Bias Current –250 250 µA INHL, INHL = –2 V, +3 V

IOHC Current Program Range

IOH = 0 mA to –40 mA 0 4 V OUT_L = –0.7 V, +7 V

IOLC Current Program Range

IOL = 0 mA to +40 mA 0 4 V OUT_L = – 2 V, +5.7 V

IOHC, IOLC Input Bias Current –300 +300 µA IOLC = 0 V, 4.0 V and IOHC = 0 V, 4.0 V

IOLRTN, IOHRTN Range –2 +7 V IOL = +40 mA, IOH = –40 mA, OUT_L = –2 V, +7 V

VDUT Range –2 +7 V IOL = +40 mA, IOH = –40 mA, IOUT_L–VCOMI >1.3 V

VDUT Range, IOH = 0 mA to –40 mA –0.7 +7 V OUT_L –VCOM > 1.3 V

VDUT Range, IOL = 0 mA to +40 mA –2 +5.7 V VCOM–VDUT > 1.3 V

VCOMI Input Range –2 +7 V IOL = +40 mA, IOH = –40 mA

OUTPUT CHARACTERISTICS

Accuracy

Absolute Accuracy Error, Load Current –0.3 – 100 +0.3 + 100 % I

VCOM Buffer

Offset Error –50 +50 mV IOL, IOH = 40 mA, VCOMI = 0 V, OUT_L = VCOM

Bias Current –10 +1 +10 µA VCOMI = 0 V, OUT_L = VCOM

Gain Error –0.2 +0.2 % IOL, IOH = 40 mA, VCOMI = –1 V to +6 V,

Linearity Error –10 +10 mV IOL, IOH = 40 mA, VCOMI = –1 V to +6 V,

Output Current TC <± 2 µA/°C Measured at IOH, IOL = 200 µA

DYNAMIC PERFORMANCE

Propagation Delay

± I

to Inhibit 1.9 ns VCOM = ± 2 V, IOL = +20 mA, IOH = –20 mA

OUT

Inhibit to ± I

Propagation Delay Matching <1.8 ns

I/O Spike 240 mV VCOM = 0 V, IOL = +20 mA, IOH = –20 mA

Settling Time to 15 mV <50 ns IOL = +20 mA, IOH = –20 mA, 50 Ω Load, to ⫾15 mV

Settling Time to 4 mV <10 µs IOL = +20 mA, IOH = –20 mA, 50 Ω Load, to ⫾4 mV

Specifications subject to change without notice.

OUT

2.8 ns VCOM = ± 2 V, IOL = +20 mA, IOH = 20 mA

+ µA IOL, IOH = 25 µA–40 mA, VCOM = 0 V, OUT_L = ± 2 V and

SET

IOL = 25 µA–40 mA, VCOM = +7 V, OUT_L = +5.7 V and

IOH = 25 µA–40 mA, VCOM = –2 V, OUT_L = –0.7 V

VOUT = VCOM

VOUT = VCOM

–4–

REV. A

Page 5

AD53509

TOTAL FUNCTION SPECIFICATIONS

(All specifications are at TJ = 85C 5C, VS = 11 V 3%, –VS = –6 V = 3% unless otherwise noted. All temperature coefficients are

measured at TJ = 75C to 95C.)

Parameter Min Typ Max Unit Test Conditions

OUTPUT CHARACTERISTICS

Output Leakage Current, V

Output Leakage Current, V

Output Capacitance 8 pF Driver and Load INHIBITED

POWER SUPPLIES

Total Supply Range 17 V

Positive Supply 11 V

Negative Supply –6 V

Positive Supply Current 280 mA Driver = INH, I

Negative Supply Current 290 mA Driver = INH, I

VCCO Current 65 mA VCCO = 3.3 V, Comparator Output 150 ⍀ to GND

Total Power Dissipation 4.8 W Driver = INH, I

Temperature Sensor Gain Factor 1 µA/K R

NOTES

Connecting or shorting the decoupling pins to ground will result in the destruction of the device.

Specifications subject to change without notice.

= –1 V to +5 V –250 +250 nA

OUT

= –2 V to +7 V –500 +500 µA

OUT

Table I. Driver Truth Table

= 10 kΩ, V

LOAD

Program = 40 mA, Load = Active

LOAD

Program = 40 mA, Load = Active

LOAD

Program = 40 mA, Load = Active

LOAD

SOURCE

= 11 V

DATA DATA IOD IOD RLD RLD OUTPUT STATE

0110XXV

1010XXV

L

H

XX0101INH

XX0110V

TERM

Table II. Comparator Truth Table

OUTPUT STATES

VOUT LEH LEH LEL LEL QH QH QL QL

>HCOMP >LCOMP 1 0 1 0 1 0 1 0

>HCOMP <LCOMP 1 0 1 0 1 0 0 1

<HCOMP >LCOMP 1 0 1 0 0 1 1 0

<HCOMP <LCOMP 1 0 1 0 0 1 0 1

X X 0 1 0 1 QH (t – 1) QH (t – 1) QL (t – 1) QL (t – 1)

Table III. Active Load Truth Table

OUTPUT STATES (Including Diode Bridge)

OUT_L INHL INHL IOH IOL I(OUT_L)

<VCOM 0 1 V(IOHC) × 10 mA V(IOLC) × 10 mA IOL

>VCOM 0 1 V(IOHC) × 10 mA V(IOLC) × 10 mA IOH

X100 0 0

–5–REV. A

Page 6

AD53509

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

1

Power Supply Voltage

VCC to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 V

VEE to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –8 V

VCC to VEE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 V

VCCO to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 V

PWR GND HQ GND . . . . . . . . . . . . . . . . . . . . . . . ± 0.4 V

Inputs

DATA, DATA, IOD, IOD, RLD, RLD . . . . . . +5 V, –2 V

DATA to DATA, IOD to IOD, RLD to RLD . . . . . . . ± 3 V

LEL, LEL, LEH, LEH . . . . . . . . . . . . . . . . . . . +5 V, –2 V

LEL to LEL, LEH to LEH . . . . . . . . . . . . . . . . . . . . . ± 3 V

INHL, INHL . . . . . . . . . . . . . . . . . . . . . . . . . . . +5 V, –2 V

INHL to INHL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 3 V

VH, VL, VTERM, VCOM_I to GND . . . . . . . . +8 V, –3 V

VH to VL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10 V

(VH–VTERM) and (VTERM – VL) . . . . . . . . . . . . . ±10 V

IOHC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±6 V

IOLC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±6 V

HCOMP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +8 V, –3 V

LCOMP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +8 V, –3 V

HCOMP, LCOMP to V

. . . . . . . . . . . . . . . . . . . ±10 V

OUT

Outputs

V

Short Circuit Duration . . . . . . . . . . . . . . . . Indefinite

OUT

V

Inhibit Mode . . . . . . . . . . . . . . . . . . . . . . . +8 V, –3 V

OUT

VHDCPL . . . . . . . . Do Not Connect Except for Cap to V

VLDCPL . . . . . . . . Do Not Connect Except for Cap to V

QH, QH, QL, QL Maximum I

OUT

Continuous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 mA

Surge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100 mA

THERM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 V, 0 V

IOHRTN, IOLRTN . . . . . . . . . . . . . . . . . . +8.5 V, –3.5 V

VCOM_S Short Circuit Duration . . . . . . . . . . . . . . . 3 sec

2

CC

EE

2

Environmental

Operating Temperature (Junction) . . . . . . . . . . . . . . . 175°C

Storage Temperature . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 sec)

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Absolute maximum limits apply

individually, not in combination. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2

Output short circuit protection is guaranteed as long as proper heat sinking is

employed to ensure compliance with the operating temperature limits.

3

To ensure lead coplanarity (± 0.002 inches) and solderability, handling with bare

hands should be avoided and the device should be stored in environments at 24 °C

± 5°C (75°F ± 10°F) with relative humidity not to exceed 65%.

3

. . . . . . . . . . . 260°C

Table IV. Package Thermal Characteristics

Air Flow, FM JA, C/W

0 33

200 25

400 22

ORDERING GUIDE

Shipment Method

Package Quantity per Package

Model Description Shipping Container Option

AD53509JSQ 52-Lead LQFP-EDQUAD 90 SQ-52

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD53509 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–6–

REV. A

Page 7

PIN CONFIGURATION

AD53509

V

VCCO

QL

QL

VCCO

QH

QH

VCCO

PWRGND

LEL

LEL

LEH

LEH

CC

CC

V

V

52 51 50 49 48 43 42 41 4047 46 45 44

1

CC

PIN 1

IDENTIFIER

2

3

4

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20 21 22 23 24 25 26

PWRGND

RLD

RLD

AD53509

HEAT SINK UP

(Not to Scale)

VH

NC

THERM

LCOMP

HCOMP

VHDCPL

HQGND2

NC = NO CONNECT

VTERM

PWRGND

OUT

V

OUT_L

IOD

PWRGND

IOLRTN

VLDCPL

EE

V

IOD

VCOMI

VCOMS

NC

V

EE

39

V

38

DATA

37

DATA

36

INHL

35

INHL

34

V

PWRGND

33

32

V

31

V

30

IOLC

29

IOHC

28

HQGND

27

IOHRTN

EE

CC

EE

L

–7–REV. A

Page 8

AD53509

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

52-Lead LQFP–EDQUAD with Integral Heat Slug

(SQ-52)

0.030 (0.75)

0.024 (0.60)

0.018 (0.45)

SEATING

PLANE

STANDOFF

0.004 (0.10)

MAX

0.063 (1.60)

MAX

52 40

1

13

14

0.006 (0.15)

0.002 (0.05)

0.008 (0.20)

0.004 (0.09)

CENTER FIGURES ARE TYPICAL UNLESS OTHERWISE NOTED

0.630 (16.00) SQ

0.551 (14.00) SQ

TOP VIEW

(PINS DOWN)

0.039 (1.00)

BSC

0.020 (0.50)

0.017 (0.42)

0.014 (0.35)

39

27

26

0.057 (1.45)

0.055 (1.40)

0.053 (1.35)

0.270

(6.86)

DIA

7

3.5

0

C01539–0–12/00 (rev. A)

–8–

PRINTED IN U.S.A.

REV. A

Loading...

Loading...