Page 1

CLK

256-Position, Ultralow Power

1.8 V Logic-Level Digital Potentiometer

FEATURES

Ultralow standby power IDD = 50 nA typical

256-position

End-to-end resistance 100 kΩ

Logic high voltage 1.8 V

Power supply 2.7 V to 5.5 V

Low temperature coefficient 35 ppm/°C

Compact thin 8-lead TSOT-8 (2.9 mm × 2.8 mm) package

Simple 3-wire digital interface

Wide operating temperature −40°C

Pin-to-pin compatible to AD5160 with CS inverted

APPLICATIONS

Battery-operated electronics adjustment

Remote utilities meter adjustment

Mechanical potentiometer replacement

Transducer circuit adjustment

Automotive electronics adjustment

Gain control and offset adjustment

System calibration

VCXO adjustment

GENERAL OVERVIEW

The AD5165 provides a compact 2.9 mm × 2.8 mm packaged

solution for 256-position adjustment applications. These devices

perform the same electronic adjustment function as mechanical

potentiometers or variable resistors, with enhanced resolution,

solid-state reliability, and superior low temperature coefficient

performance. The AD5165’s supply voltage requirement is 2.7 V

to 5.5 V, but its logic voltage requirement is 1.8 V to V

AD5165 consumes very low quiescent power during standby

mode and is ideal for battery-operated applications.

Wiper settings are controlled through a simple 3-wire interface.

The interface is similar to the SPI® digital interface except for the

inverted chip-select function that minimizes logic power consumption in the idling state. The resistance between the wiper

and either endpoint of the fixed resistor varies linearly with

respect to the digital code transferred into the wiper register.

Operating from a 2.7 V to 5.5 V power supply and consuming

less than 50 nA typical standby power allows use in batteryoperated portable or remote utility device applications.

to +125°C

DD

. The

AD5165

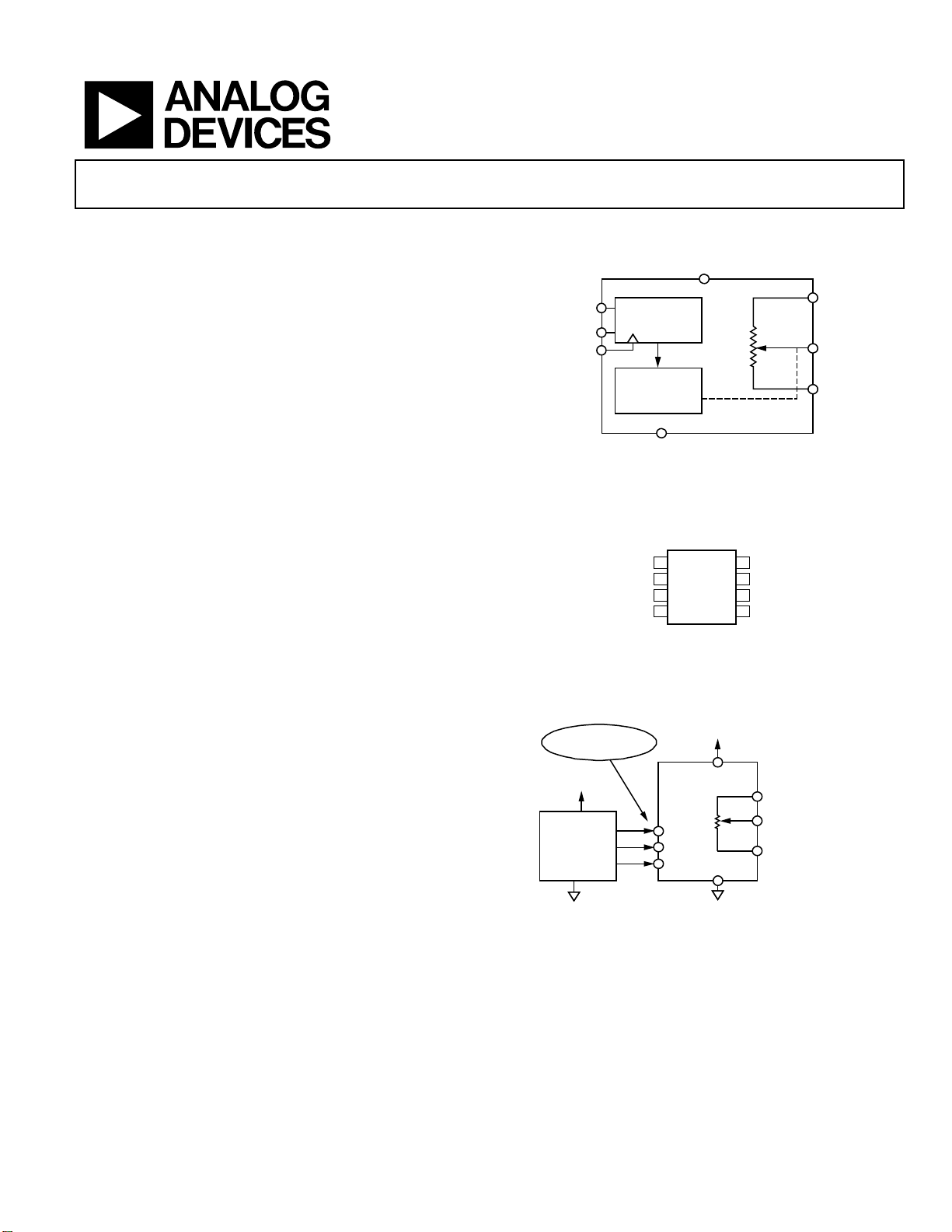

FUNCTIONAL BLOCK DIAGRAM

V

DD

04749-0-002

A,VB,VW

A

W

B

04749-0-001

< 5V

CS

SDI

3-WIRE

INTERFACE

WIPER

REGISTER

GND

Figure 1.

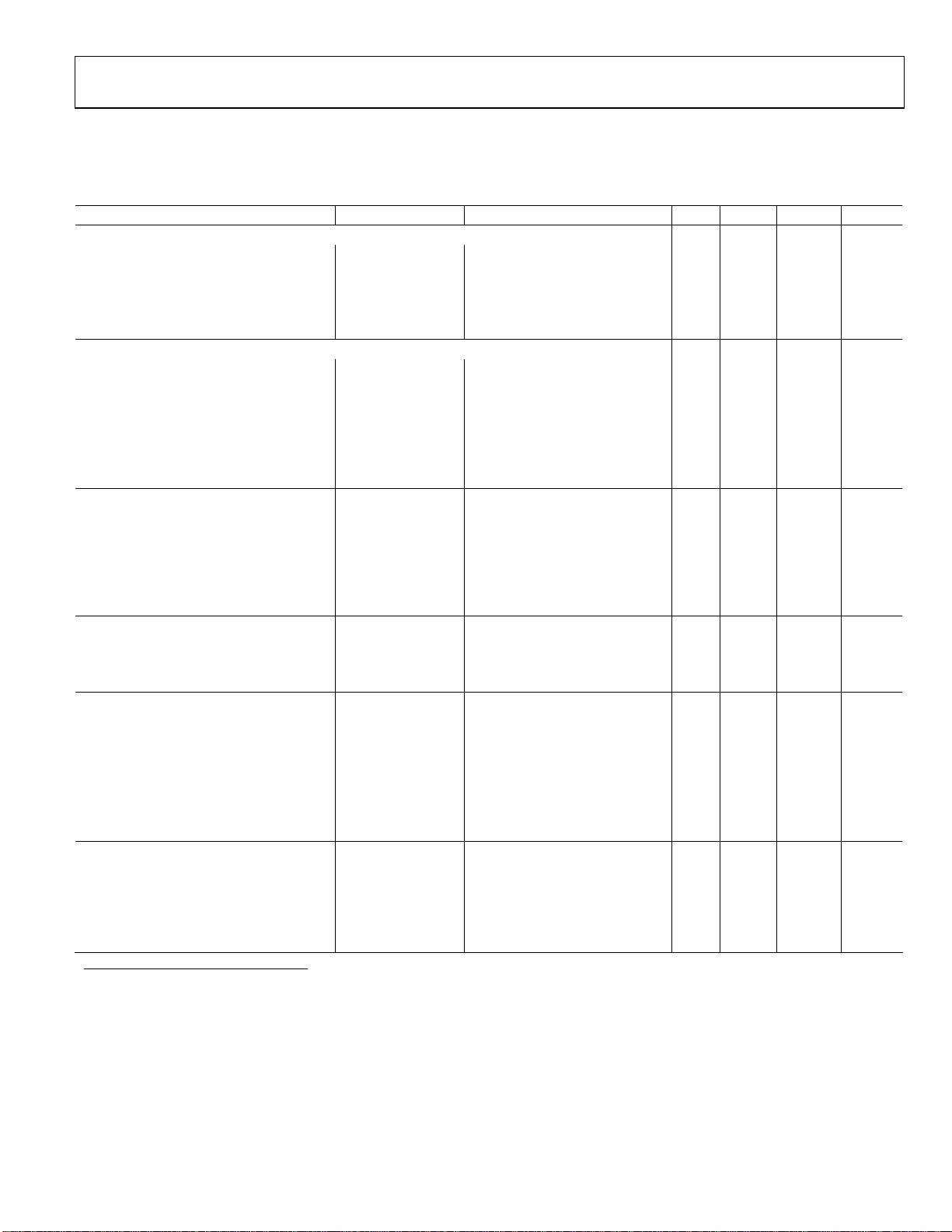

PIN CONFIGURATION

1

W

2

AD5165

V

DD

TOP VIEW

3

GND

(Not to Scale)

4

CLK

Figure 2.

A

8

B

7

CS

6

5

SDI

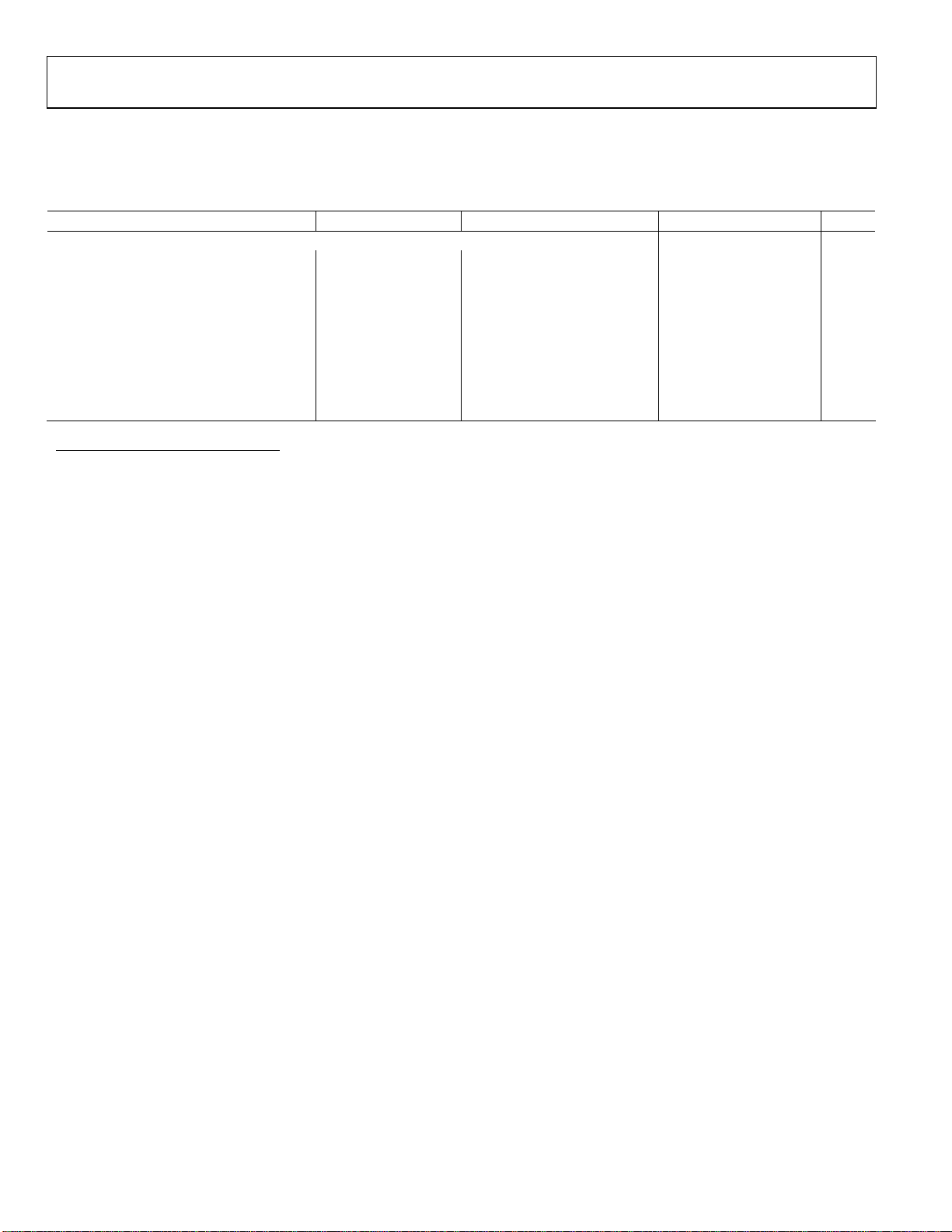

TYPICAL APPLICATION

AD5165

CS

CLK

SDI

Figure 3.

5V

V

DD

GND

V

A

WIDE TERMINAL

V

W

VOLTAGE RANGE:

V

B

0V < V

VOH= 1.8V MIN

3.3V

DIGITAL

CONTROL

LOGIC OR

MICRO

Note:

The terms digital potentiometer, RDAC, and VR are used interchangeably.

04749-0-003

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Anal og Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

Page 2

AD5165

TABLE OF CONTENTS

Electrical Characteristics—100 kΩ Vers io n .................................. 3

Absolute Maximum Ratings............................................................ 5

Pin Configuration and Functional Descriptions.......................... 6

Typical Performance Characteristics............................................. 7

Tes t Ci r cu it s ..................................................................................... 11

3-Wire Digital Interface................................................................. 12

Theory of Operation ...................................................................... 13

Programming the Variable Resistor .........................................13

Programming the Potentiometer Divider............................... 14

3-Wire Serial Bus Digital Interface.......................................... 14

ESD Protection ........................................................................... 14

Terminal Voltage Operating Range.......................................... 14

Power-Up Sequence ................................................................... 14

Layout and Power Supply Bypassing ....................................... 15

Evaluation Board ........................................................................ 15

Outline Dimensions....................................................................... 16

Ordering Guide .......................................................................... 16

REVISION HISTORY

4/04—Revision 0: Initial Version

Rev. 0 | Page 2 of 16

Page 3

AD5165

ELECTRICAL CHARACTERISTICS—100 kΩ VERSION

VDD = 5 V ± 10%, or 3 V ± 10%; VA = VDD; VB = 0 V; –40°C < TA < +125°C; unless otherwise noted.

Table 1.

Parameter Symbol Conditions Min Typ

DC CHARACTERISTICS—RHEOSTAT MODE

Resistor Differential Nonlinearity

2

R-DNL RWB, V

Resistor Integral Nonlinearity2 R-INL RWB, V

Nominal Resistor Tolerance

Resistance Temperature Coefficient (∆RAB/RAB)/∆Tx10

Wiper Resistance R

3

∆RAB/R

W

AB

TA = 25°C −20 +20 %

6

V

= V

AB

VDD = 2.7 V/5.5 V 85/50 150/120 Ω

= no connect

A

= no connect

A

, wiper = no connect 35 ppm/°C

DD

−1 ±0.1 +1 LSB

−2 ±0.25 +2 LSB

DC CHARACTERISTICS—POTENTIOMETER DIVIDER MODE

Resolution N 8 Bits

Differential Nonlinearity

4

DNL −1 ±0.1 +1 LSB

Integral Nonlinearity4 INL −1 ±0.3 +1 LSB

Voltage Divider Temperature

(∆V

W/VW

)/∆Tx10

6

Code = 0x80 15 ppm/°C

Coefficient

Full-Scale Error V

Zero-Scale Error V

WFSE

WZSE

Code = 0xFF −0.5 −0.3 0 LSB

Code = 0x00 0 0.1 0.5 LSB

RESISTOR TERMINALS

Voltage Range

Capacitance6 A, B C

5

V

A,B,W

A,B

GND V

f = 1 MHz, measured to GND,

90 pF

Code = 0x80

Capacitance6 W C

W

f = 1 MHz, measured to GND,

95 pF

Code = 0x80

Common-Mode Leakage I

CM

VA = VB = VDD/2 1 nA

DIGITAL INPUTS AND OUTPUTS

Input Logic High V

Input Logic Low V

Input Capacitance

6

IH

IL

C

IL

VDD = 2.7 V to 5.5 V 1.8 V

VDD = 2.7 V to 5.5 V 0.6 V

5 pF

POWER SUPPLIES

Power Supply Range V

Supply Current I

DD RANGE

DD

2.7 5.5 V

Digital inputs = 0 V or V

DD

0.05 1 µA

VDD = 2.7 V, digital inputs = 1.8 V 10 µA

VDD = 5 V, digital inputs = 1.8 V 500 µA

Power Dissipation

Power Supply Sensitivity PSS

7

P

DISS

Digital inputs = 0 V or V

= +5 V ± 10%,

V

DD

DD

5.5 µW

±0.001 ±0.005 %/%

Code = Midscale

DYNAMIC CHARACTERISTICS

6, 8

Bandwidth −3 dB BW Code = 0x80 55 kHz

Total Harmonic Distortion THD

VW Settling Time t

S

W

VA =1 V rms, VB = 0 V, f = 1 kHz, 0.05 %

VA = 5 V, VB = 0 V,

2 µs

±1 LSB error band

Resistor Noise Voltage Density e

N_WB

RWB = 50 kΩ 28 nV/√Hz

1

Typical specifications represent average readings at +25°C and VDD = 5 V.

2

Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper

positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic.

3

VAB = VDD, wiper (VW) = no connect.

4

INL and DNL are measured at VW with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. VA = VDD and VB = 0 V.

5

Resistor terminals A, B, and W have no limitations on polarity with respect to each other.

6

Guaranteed by design and not subject to production test.

7

P

is calculated from (IDD × VDD). CMOS logic level inputs result in minimum power dissipation.

DISS

8

All dynamic characteristics use VDD = 5 V.

1

Max Unit

DD

V

Rev. 0 | Page 3 of 16

Page 4

AD5165

TIMING CHARACTERISTICS—100 kΩ VERSION

VDD = +5 V ± 10%, or +3 V ± 10%; VA = VDD; VB = 0 V; −40°C < TA < +125°C; unless otherwise noted.

Table 2.

Parameter Symbol Conditions Min Typ

3-WIRE INTERFACE TIMING CHARACTERISTICS

Clock Frequency f

Input Clock Pulse Width tCH, t

Data Setup Time t

Data Hold Time t

CS Setup Time t

CS Low Pulse Width t

CLK Fall to CS Rise Hold Time t

CLK Fall to CS Fall Hold Time t

CS Fall to Clock Rise Setup t

1

Typical specifications represent average readings at +25°C and VDD = 5 V.

2

Guaranteed by design and not subject to production test.

3

All dynamic characteristics use VDD = 5 V.

4

See and for location of measured values. All input control voltages are specified with tFigure 34 Figure 35

level of 1.5 V.

2, , 3 4

(specifications apply to all parts)

= 1/( tCH+ tCL)

CLK

CL

DS

DH

CSS

CSW

CSH0

CSH1

CS1

Clock level high or low 20 ns

5 ns

5 ns

15 ns

40 ns

0 ns

0 ns

10 ns

= tF = 2 ns (10% to 90% of 3 V) and timed from a voltage

R

1

Max Unit

25 MHz

Rev. 0 | Page 4 of 16

Page 5

AD5165

ABSOLUTE MAXIMUM RATINGS

JMAX

− TA)/θJA.

1, 2

DD

±20 mA

2

±5 mA

±5 mA

) 150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

TA = +25°C, unless otherwise noted.

Table 3.

Parameter Value

VDD to GND –0.3 V to +7 V

VA, VB, VW to GND V

Maximum Current

I

, IWA Pulsed

WB

Continuous (RWB ≤ 1 kΩ, A open)

I

WB

IWA Continuous (R

≤ 1 kΩ, B open)2

WA

Digital Inputs and Output Voltage to GND 0 V to +7 V

Operating Temperature Range –40°C to +125°C

Maximum Junction Temperature (T

Storage Temperature –65°C to +150°C

Lead Temperature (Soldering, 10 – 30 sec) 245°C

Thermal Resistance2 θJA: TSOT-8 200°C/W

1

Maximum terminal current is bounded by the maximum current handling

of the switches, maximum power dissipation of the package, and maximum

applied voltage across any two of the A, B, and W terminals at a given

resistance.

2

Package power dissipation = (T

JMAX

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. 0 | Page 5 of 16

Page 6

AD5165

PIN CONFIGURATION AND FUNCTIONAL DESCRIPTIONS

V

GND

CLK

W

DD

1

2

AD5165

TOP VIEW

3

(Not to Scale)

4

8

A

7

B

6

CS

5

SDI

04749-0-002

Figure 4.

Table 4.

Pin Name Description

1 W Wiper terminal. GND ≤ VA ≤ V

2 V

DD

Positive Power Supply.

DD.

3 GND Digital Ground.

4 CLK Serial Clock Input. Positive-edge triggered.

5 SDI Serial Data Input (data loads MSB first).

6 CS Chip Select Input, active high. When CS returns low, data is loaded into the wiper register.

7 B B terminal. GND ≤ VA ≤ VDD.

8 A A terminal. GND ≤ VA ≤ VDD.

Rev. 0 | Page 6 of 16

Page 7

AD5165

TYPICAL PERFORMANCE CHARACTERISTICS

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

RHEOSTAT MODE INL (LSB)

–0.3

–0.4

–0.5

Figure 5. R-INL vs. Code vs. Supply Voltages

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

REHOSTAT MODE DNL (LSB)

–0.3

–0.4

–0.5

Figure 6. R-DNL vs. Code vs. Supply Voltages

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

–0.3

POTENTIOMETER MODE INL (LSB)

–0.4

–0.5

Figure 7. INL vs. Code vs. Temperature , V

5.5V

2.7V

1289632 640 160 192 224 256

CODE (Decimal)

1289632 640 160 192 224 256

CODE (Decimal)

1289632 640 160 192 224 256

CODE (Decimal)

–40°C

+25°C

+85°C

+125°C

= 5 V

DD

5.5V

2.7V

04749-0-011

04749-0-013

04749-0-006

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

–0.3

POTENTIOMETER MODE DNL (LSB)

–0.4

–0.5

1289632 640 160 192 224 256

CODE (Decimal)

Figure 8. DNL vs. Code vs. Temperature, V

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

–0.3

POTENTIOMETER MODE INL (LSB)

–0.4

–0.5

1289632 640 160 192 224 256

CODE (Decimal)

–40°C

+25°C

+85°C

+125°C

DD

= 5 V

5.5V

2.7V

04749-0-008

04749-0-007

Figure 9. INL vs. Code vs. Supply Voltages

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

–0.3

POTENTIOMETER MODE DNL (LSB)

–0.4

–0.5

1289632 640 160 192 224 256

CODE (Decimal)

5.5V

2.7V

04749-0-009

Figure 10. DNL vs. Code vs. Supply Voltages

Rev. 0 | Page 7 of 16

Page 8

AD5165

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

RHEOSTAT MODE INL (LSB)

–0.3

–0.4

–0.5

Figure 11. R-INL vs. Code vs. Temperature, V

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

RHEOSTAT MODE DNL (LSB)

–0.3

–0.4

–0.5

Figure 12. R-DNL vs. Code vs. Temperature, V

0.5

0.4

0.3

0.2

0.1

0

FSE (LSB)

–0.1

–0.2

–0.3

–0.4

–0.5

1289632 640 160 192 224 256

CODE (Decimal)

1289632 640 160 192 224 256

CODE (Decimal)

FSE @ VDD = 5.5V

FSE @ VDD = 2.7V

4020–20 0–40 60 80 100 120

TEMPERATURE (°C)

–40°C

+25°C

+85°C

+125°C

= 5 V

DD

DD

–40°C

+25°C

+85°C

+125°C

= 5 V

04749-0-010

04749-0-012

04749-0-023

0.5

0.4

0.3

0.2

0.1

0

ZSE (LSB)

–0.1

–0.2

–0.3

–0.4

–0.5

TEMPERATURE (°C)

ZSE @ VDD = 5.5V

ZSE @ VDD = 2.7V

4020–20 0–40 60 80 100 120

Figure 14. Zero-Scale Error vs. Temperature

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

SUPPLY CURRENT (µA)

–0.3

–0.4

–0.5

4020–20 0–40 60 80 100 120

TEMPERATURE (°C)

IDD@ VDD = 5.5V

IDD@ VDD = 2.7V

Figure 15. Supply Current vs. Temperature

10000

1000

100

A)

µ

(

10

DD

I

1

0.1

0.01

012345

VDD = VA = 2.7V

V

(0) (V)

IH

VDD = VA = 5V

04749-0-022

04749-0-020

04749-0-025

Figure 13. Full-Scale Error vs. Temperature

Figure 16. Supply Current vs. Digital Input Voltage

Rev. 0 | Page 8 of 16

Page 9

AD5165

1000

100

V

= VA = 2.7V

10

A)

µ

(

DD

I

1

0.1

0.01

012345

DD

V

(1MHz) (V)

IH

VDD = VA = 5V

Figure 17. Supply Current vs. Digital Input Voltage

20

15

10

5

0

–5

–10

RHEOSTAT MODE TEMCO (ppm/°C)

–15

–20

Figure 18. Rheostat Mode Tempco ∆R

1289632 640 160 192 224 256

CODE (Decimal)

/∆T vs. Code

WB

04749-0-026

04749-0-015

REF LEVEL

0.000dB

0

–6

–12

–18

–24

–30

–36

–42

–48

–54

–60

1k 10k 100k 1M

START 1 000.000Hz STOP 1 000 000.000Hz

Figure 20. Gain vs. Frequency vs. Code, R

REF LEVEL

–5.000dB

–5.5

–6.0

–6.5

–7.0

–7.5

–8.0

–8.5

–9.0

–9.5

–10.0

–10.5

10k

START 1 000.000Hz STOP 1 000 000.000Hz

/DIV

6.000dB

/DIV

0.500dB

0x80

0x40

0x20

0x10

0x08

0x04

0x02

0x01

MARKER 54 089.173Hz

MAG (A/R) –9.052dB

= 100 kΩ

AB

100kΩ – 54kHz

R = 100kΩ

Figure 21. –3 dB Bandwidth @ Code = 0x80

04749-0-048

10M

04749-0-047

8

6

4

2

0

–2

–4

–6

POTENTIOMETER MODE TEMPCO (ppm/°C)

–8

CODE (Decimal)

Figure 19. Potentiometer Mode Tempco ∆V

1289632 640 160 192 224 256

/∆T vs. Code

WB

04749-0-014

Rev. 0 | Page 9 of 16

80

CODE = 80H, VA = VDD, VB = 0V

60

40

PSRR (–dB)

20

PSRR @ VDD = 5V DC ± 10% p-p AC

PSRR @ V

0

1k100 10k 100k 1M

= 3V DC ± 10% p-p AC

DD

FREQUENCY (Hz)

04749-0-019

Figure 22. PSRR v s. Frequency

Page 10

AD5165

800

700

600

VDD = 5V

VA = 5V

V

= 0V

B

500

A)

µ

(

400

DD

I

300

200

100

0

10k 1M100k 10M

FREQUENCY (Hz)

1

2

Ch 1 200mV

Figure 23. I

B

Ch 2 5.00 V

W

DD

CODE 55

CODE FF

H

vs. Frequency

B

M 100ns A CH2 3.00 V

W

H

VW

CS

04749-0-018

04749-0-030

1

2

Ch 1 100mV

B

Ch 2 5.00 V

W

B

M 200ns A CH1 152mV

W

Figure 26. Midscale Glitch, Code 0x80–0x7F

VW

CS

04749-0-028

Figure 24. Large Signal Settling Time, Code 0xFF–0x00

1

2

B

Ch 1 200mV

Ch 2 5.00 V

W

B

M 100ns A CH2 3.00 V

W

Figure 25. Digital Feedthrough

VW

CLK

04749-0-030

Rev. 0 | Page 10 of 16

Page 11

AD5165

V

TEST CIRCUITS

Figure 27 to Figure 33 illustrate the test circuits that define the test conditions used in the product specification tables.

V+ = V

DUT

A

V+

W

B

DD

1LSB = V+/2

V

MS

N

04749-0-031

OFFSET

GND

V

IN

2.5V

DUT

A

W

B

+15V

AD8610

–15V

V

OUT

04749-0-035

Figure 27. Test Circuit for Potentiometer Divider Nonlinearity Error

(INL, DNL)

NO CONNECT

DUT

A

W

B

I

W

V

MS

04749-0-032

Figure 28. Test Circuit for Resistor Position Nonlinearity Error

(Rheostat Operation; R-INL, R-DNL)

MS2

DUT

A

W

B

V

W

IW = VDD/R

V

MS1

RW = [V

NOMINAL

MS1

– V

MS2

]/I

W

04749-0-033

Figure 29. Test Circuit for Wiper Resistance

V

A

V

DD

A

V+

W

B

V

MS

10%

V+ = V

DD

PSRR (dB) = 20 LOG

∆V

PSS (%/%) =

MS

∆

V

DD

∆

( )

∆

%

%

V

MS

V

DD

04749-0-034

Figure 30. Test Circuit for Power Supply Sensitivity (PSS, PSSR)

Figure 31. Test Circuit for Gain vs. Frequency

0.1V

RSW=

I

DUT

B

W

I

SW

GND TO V

SW

CODE = 0x00

DD

0.1V

04749-0-036

Figure 32. Test Circuit for Incremental ON Resistance

NC

DUT

GND

A

B

NC

V

DD

I

W

CM

NC = NO CONNECT

V

CM

04749-0-037

Figure 33. Test Circuit for Common-Mode Leakage Current

Rev. 0 | Page 11 of 16

Page 12

AD5165

V

3-WIRE DIGITAL INTERFACE

Note that in the AD5165 data is loaded MSB first.

Table 5. AD5165 Serial Data-Word Format

B7 B6 B5 B4 B3 B2 B1 B0

D7 D6 D5 D4 D3 D2 D1 D0

MSB LSB

7

2

2

1

SDI

0

1

CLK

0

1

CS

0

1

OUT

0

Figure 34. 3-Wire Digital Interface Timing Diagram

D6 D5 D4 D3 D2 D1 D0

D7

RDAC REGISTER LOAD

= 5 V, VB = 0 V, VW = V

(V

A

OUT

04749-0-004

)

0

1

SDI

(DATA IN)

CLK

VOUT

CS

0

1

0

t

1

0

V

DD

0

Figure 35. 3-Wire Digital Interface Detailed Timing Diagram (V

Dx Dx

CSHO

t

CSS

t

t

CH

DS

t

CL

t

DH

t

CS1

t

CSH1

t

CSW

t

S

= 5 V, VB = 0 V, VW = V

A

±1LSB

OUT

04749-0-005

)

Rev. 0 | Page 12 of 16

Page 13

AD5165

−

THEORY OF OPERATION

The AD5165 is a 256-position digitally controlled variable

resistor (VR) device.

PROGRAMMING THE VARIABLE RESISTOR

Rheostat Operation

The nominal resistance of the RDAC between terminals A and

B is available in 100 kΩ. The nominal resistance (R

has 256 contact points accessed by the wiper terminal, plus the

B terminal contact. The 8-bit data in the RDAC latch is decoded

to select one of the 256 possible settings.

A

W

B

Figure 36. Rheostat Mode Configuration

A

W

B

A

B

) of the VR

AB

W

04749-0-038

where:

D is the decimal equivalent of the binary code loaded in the

8-bit RDAC register.

is the end-to-end resistance.

R

AB

R

is the wiper resistance contributed by the on resistance of

W

the internal switch.

In summary, if R

circuited, the following output resistance R

= 100 kΩ and the A terminal is open

AB

is set for the

WB

indicated RDAC latch codes.

Table 6. Codes and Corresponding R

Resistance

WB

D (Dec.) RWB (Ω) Output State

255 99,710 Full scale (RAB – 1 LSB + RW)

128 50,100 Midscale

1 490 1 LSB

0 100 Zero scale (wiper contact resistance)

Assuming that a 100 kΩ part is used, the wiper’s first connection starts at the B terminal for data 0x00. Because there is a

50 Ω wiper contact resistance, such a connection yields a minimum of 100 Ω (2 × 50 Ω) resistance between terminals W and

B. The second connection is the first tap point, which corresponds to 490 Ω (R

= RAB/256 + 2 × RW = 390 Ω + 2 × 50 Ω)

WB

for data 0x01. The third connection is the next tap point,

representing 880 Ω (2 × 390 Ω + 2 × 50 Ω) for data 0x02, and

so on. Each LSB data value increase moves the wiper up the

resistor ladder until the last tap point is reached at 100,100 Ω

+ 2 × RW).

(R

AB

A

R

S

D7

D6

D5

D4

D3

D2

D1

D0

RDAC

LATCH

AND

DECODER

R

S

R

S

W

R

S

B

Note that, in the zero-scale condition, a finite wiper resistance

of 100 Ω is present. Care should be taken to limit the current

flow between W and B in this state to a maximum pulse current

of no more than 20 mA. Otherwise, degradation or possible

destruction of the internal switch contact can occur.

Similar to the mechanical potentiometer, the resistance of the

RDAC between the wiper W and terminal A also produces a

digitally controlled complementary resistance, R

. When these

WA

terminals are used, the B terminal can be opened. Setting the

resistance value for R

starts at a maximum value of resistance

WA

and decreases as the data loaded in the latch increases in value.

The general equation for this operation is

256

256

D

ABWA

WA

)(

DR ×+×

= 2

For R

= 100 kΩ with the B terminal open circuited, the

AB

following output resistance R

(2)

RR

W

is set for the indicated RDAC

latch codes.

Table 7. Codes and Corresponding R

Resistance

WA

D (Dec.) RWA (Ω) Output State

255 490 Full scale

128 50,100 Midscale

1 99, 710 1 LSB

0 100,100 Zero scale

04749-0-039

Figure 37. AD5165 Equivalent RDAC Circuit

The general equation determining the digitally programmed

Typical device-to-device matching is process-lot dependent

and may vary by up to ±20%. Because the resistance element

is processed in thin film technology, the change in R

AB

with

temperature has a very low 35 ppm/°C temperature coefficient.

output resistance between W and B is

WB

256

D

DR ×+×= 2

)(

AB

(1)

RR

W

Rev. 0 | Page 13 of 16

Page 14

AD5165

Ω

PROGRAMMING THE POTENTIOMETER DIVIDER

Voltage Output Operation

The digital potentiometer easily generates a voltage divider at

wiper-to-B and wiper-to-A proportional to the input voltage at

A to B. Unlike the polarity of V

positive, voltage across A to B, W to A, and W to B can be at

either polarity.

V

I

Figure 38. Potentiometer Mode Configuration

If ignoring the effect of the wiper resistance for approximation,

connecting the A terminal to 5 V and the B terminal to ground

produces an output voltage at the wiper-to-B starting at 0 V

up to 1 LSB less than 5 V. Each LSB of voltage is equal to the

voltage applied across terminals A and B divided by the 256

positions of the potentiometer divider. The general equation

defining the output voltage at V

valid input voltage applied to terminals A and B is

to GND, which must be

DD

A

W

V

O

B

04749-0-040

with respect to ground for any

W

The data setup and data hold times in the specifications table

determine the valid timing requirements. The AD5165 uses an

8-bit serial input data register word that is transferred to the

internal RDAC register when the CS line returns to logic low.

Extra MSB bits are ignored.

ESD PROTECTION

All digital inputs are protected with a series of input resistors

and parallel Zener ESD structures, shown in Figure 39 and

Figure 40. This applies to the digital input pins SDI, CLK,

and CS.

340

LOGIC

GND

Figure 39. ESD Protection of Digital Pins

A, B, W

GND

Figure 40. ESD Protection of Resistor Terminals

04749-0-041

04749-0-042

256

256

D

−

(3)

V

B

D

DV

W

V

)(

256

+=

A

A more accurate calculation, which includes the effect of wiper

resistance, V

, is

W

DR

DR

)(

WB

DV

)(

W

V

+=

A

R

AB

WA

)(

(4)

V

B

R

AB

Operation of the digital potentiometer in the divider mode

results in a more accurate operation over temperature. Unlike

the rheostat mode, the output voltage is dependent mainly on

the ratio of the internal resistors R

and RWB and not the

WA

absolute values. Therefore, the temperature drift reduces to

15 ppm/°C.

3-WIRE SERIAL BUS DIGITAL INTERFACE

The AD5165 contains a 3-wire digital interface (SDI, CS, and

CLK). The 8-bit serial word must be loaded MSB first. The

format of the word is shown in Table 5.

The positive-edge sensitive CLK input requires clean transitions

to avoid clocking incorrect data into the serial input register.

Standard logic families work well. If mechanical switches are

used for product evaluation, they should be debounced by a

flip-flop or other suitable means. When CS is high, the clock

loads data into the serial register on each positive clock edge,

as shown in Figure 34.

TERMINAL VOLTAGE OPERATING RANGE

The AD5165 VDD and GND power supply defines the boundary

conditions for proper 3-terminal digital potentiometer operation. Supply signals present on terminals A, B, and W that

exceed V

or GND are clamped by the internal forward-biased

DD

diodes, as shown in Figure 41.

V

DD

A

W

B

GND

04749-0-043

Figure 41. Maximum Terminal Voltages Set by V

and GND

DD

POWER-UP SEQUENCE

Because the ESD protection diodes limit the voltage compliance

at terminals A, B, and W (see Figure 41), it is important to

power V

and W; otherwise, the diode is forward biased such that V

powered unintentionally and may affect the rest of the user’s

circuit. The ideal power-up sequence is in the following order:

GND, V

order of powering V

important as long as they are powered after V

/GND before applying any voltage to terminals A, B,

DD

, digital inputs, and then VA, VB, and VW. The relative

DD

, VB, VW, and the digital inputs is not

A

/GND.

DD

DD

is

Rev. 0 | Page 14 of 16

Page 15

AD5165

LAYOUT AND POWER SUPPLY BYPASSING

It is good practice to employ compact, minimum lead length

layout design. The leads to the inputs should be as direct as

possible with a minimum conductor length. Ground paths

should have low resistance and low inductance.

Similarly, it is also good practice to bypass the power supplies

with quality capacitors for optimum stability. Supply leads to

the device should be bypassed with disk or chip ceramic

capacitors of 0.01 µF to 0.1 µF. Low ESR 1 µF to 10 µF tantalum

or electrolytic capacitors should also be applied at the supplies

to minimize any transient disturbance and low frequency ripple

(see Figure 42). Note that the digital ground should also be

joined remotely to the analog ground at one point to minimize

the ground bounce.

EVALUATION BOARD

An evaluation board, along with all necessary software, is

available to program the AD5165 from any PC running

Windows® 98/2000/XP. The graphical user interface, as shown

in Figure 43, is straightforward and easy to use. More detailed

information is available in the user manual, which comes with

the board.

V

DD

+

C3

µ

FC10.1µF

10

Figure 42. Power Supply Bypassing

V

DD

AD5165

GND

04749-0-044

04749-0-046

Figure 43. AD5165 Evaluation Board Software

The AD5165 starts at midscale upon power-up. To increment

or decrement the resistance, the user may move the scroll bars

on the left. To write any specific value, the user should use the

bit pattern in the upper screen and click the Run button. The

format of writing data to the device is shown in Figure 32.

Rev. 0 | Page 15 of 16

Page 16

AD5165

R

OUTLINE DIMENSIONS

2.90 BSC

847

1.60 BSC

PIN 1

INDICATO

0.90

0.87

0.84

0.10 MAX

1 3562

1.95

BSC

0.38

0.22

COMPLIANT TO JEDEC STANDARDS MO-193BA

2.80 BSC

0.65 BSC

1.00 MAX 0.20

SEATING

PLANE

0.08

8°

4°

0°

Figure 44. 8-Lead Thin Small Outline Transistor Package [Thin SOT-23]

(UJ-8)

Dimensions shown in millimeters

0.60

0.45

0.30

ORDERING GUIDE

Model RAB (Ω) Temperature Package Description Package Option Quantity on Reel Branding

AD5165BUJZ100-R21 100 k –40°C to +125°C Thin SOT-23 UJ-8 250 D3N

AD5165BUJZ100-R71 100 k –40°C to +125°C Thin SOT-23 UJ-8 3,000 D3N

AD5165EVAL Evaluation Board

1

Z = Pb-free part.

© 2004 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D04749–0–4/04(0)

Rev. 0 | Page 16 of 16

Loading...

Loading...