Datasheet ACT-5260PC-150F17T, ACT-5260PC-150F17M, ACT-5260PC-150F17I, ACT-5260PC-150F17C, ACT-5260PC-133F17T Datasheet (ACT)

...Page 1

eroflex Circuit

– RISC TurboEngines For The Future © SCD5260 REV A 3/29/99

Integer Control

Floating point Control

ACT5260

64-Bit Superscaler Microprocessor

Features

■ Full militarized QED RM5260 microprocessor

■ Dual Issue superscalar QED RISCMark - can issue one

integer and one floating-point instruction per cycle

microprocessor - can issue one integer and one

floating-point instruction per cycle

● 100, 133 and 150MHz frequency (200MHz future option)

Consult Factory for latest speeds

● 260 Dhrystone2.1 MIPS

● SPECInt95 4.8. SPECfp95 5.1

■ High performance system interface compatible with R4600,

R4700 and R5000

● 64-bit multiplexed system address/data bus for optimum

price/performance up to 100 MHz operating frequency

● High performance write protocols maximize uncached

write bandwidth

● Operates at input system clock multipliers of 2 through 8

● 5V tolerant I/O's

● IEEE 1149.1 JTAG boundary scan

■ Integrated on-chip caches - up to 3.2GBps internal data rate

● 16KB instruction - 2 way set associative

● 16KB data - 2 way set associative

● Virtually indexed, physically tagged

● Write-back and write-through on per page basis

● Pipeline restart on first double for data cache misses

■ Integrated memory management unit

● Fully associative joint TLB (shared by I and D translations)

● 48 dual entries map 96 pages

● Variable page size (4KB to 16MB in 4x increments)

■ Embedded supply de-coupling capacitors and Pll filter

components

■ High-performance floating point unit - up to 400 MFLOPS

● Single cycle repeat rate for common single precision

operations and some double precision operations

● Two cycle repeat rate for double precision multiply and

double precision combined multiply-add operations

● Single cycle repeat rate for single precision combined

multiply-add operation

■ MIPS IV instruction set

● Floating point multiply-add instruction increases

performance in signal processing and graphics

applications

● Conditional moves to reduce branch frequency

● Index address modes (register + register)

■ Embedded application enhancements

● Specialized DSP integer Multiply-Accumulate instruction

and 3 operand multiply instruction

● I and D cache locking by set

● Optional dedicated exception vector for interrupts

■ Fully static CMOS design with power down logic

● Standby reduced power mode with WAIT instruction

● 5 Watts typical at 3.3V, less than 175 mwatts in Standby

■ 208-lead CQFP, cavity-up package (F17)

■ 208-lead CQFP, inverted footprint (F24), Intended to duplicate

the commercial QED footprint (Consult Factory)

■ 179-pin PGA package (Future Product) (P10)

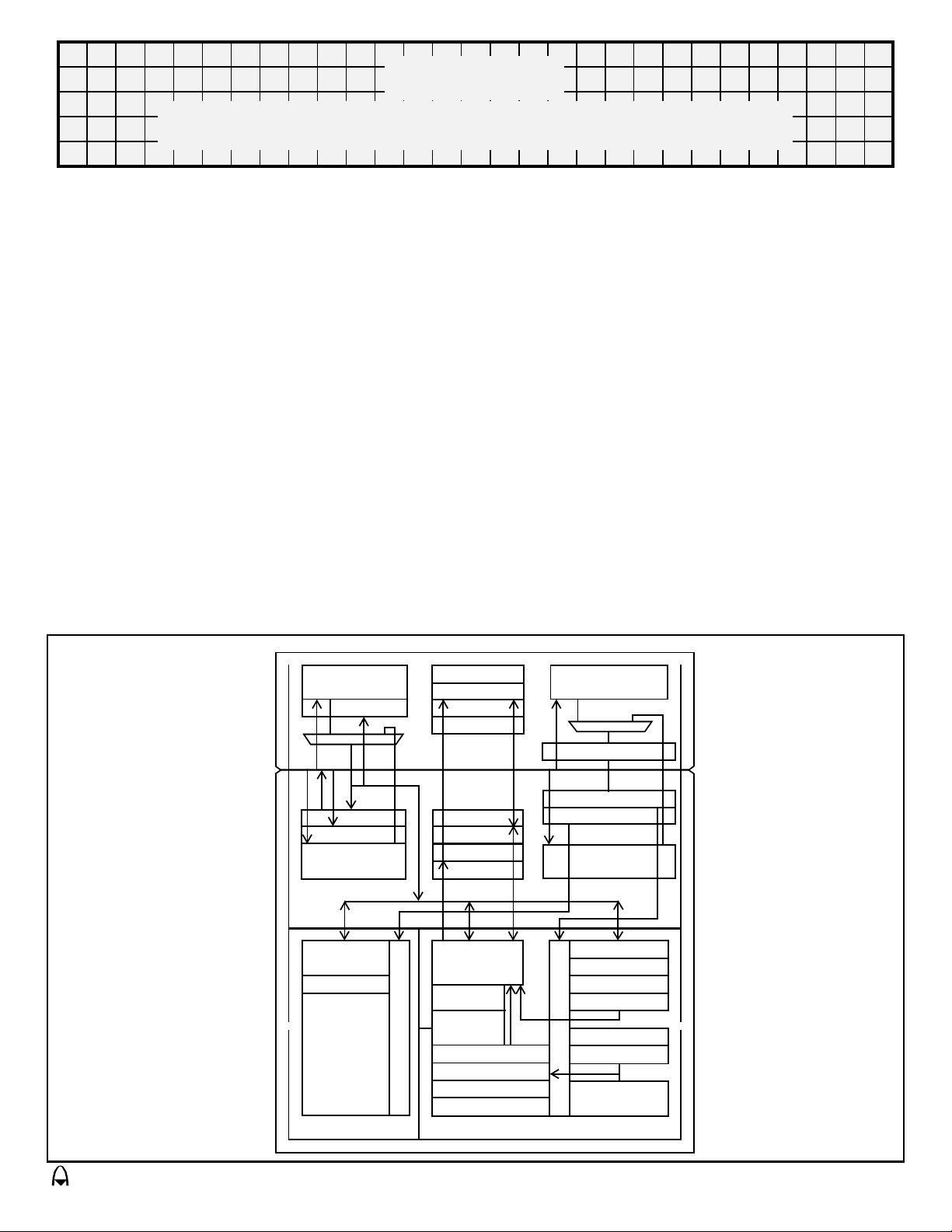

BLOCK DIAGRAM

Data Set A

Store Buffer

Write Buffer

Read Buffer

Data Set B

Control

Floating-point

Register File

Unpacker/Packer

Floating-point

MAdd, Add, Sub,Cvt

Div, SqRt

DBus

Sys AD

FPIBus

Phase Lock Loop

Data Tag A

DTLB Physical

Data Tag B

Address Buffer

Instruction Tag A

ITLB Physical

Instruction Tag B

Tag Aux Tag

Joint TLB

Coprocessor 0

System/Memory

Control

PC Incrementer

Branch Adder

Instruction TLB Virtual

Program Counter

Instruction Set A

Instruction Select

Integer Instruction Register

FP Instruction Register

Instruction Set B

Integer/Address Adder

DVA

IVA

Integer Multiply, Divide

IntIBus

Load Aligner

Integer Register File

Data TLB Virtual

Shifter/Store Aligner

Logic Unit

ABus

Technology

Page 2

DESCRIPTION:

The ACT5260 is a highly integrated superscalar

microprocessor that implements a superset of the

MIPS IV Instruction Set Architecture(ISA). It has a

high performance 64-bit integer unit, a high

throughput, fully pipelined 64-bit floating point unit,

an operating system friendly memory management

unit with a 48-entry fully associative TLB, a 16 KByte

2-way set associative instruction cache, a 16 KByte

2-way set associative data cache, and a

high-performance 64-bit system interface. The

ACT5260 can issue both an integer and a floating

point instruction in the same cycle.

The ACT5260 is ideally suited for high-end

embedded control applications such as

internetworking, high performance image

manipulation, high speed printing, and 3-D

visualization.

Integer Unit

Like the R5000, the ACT5260 implements the

MIPS IV Instruction Set Architecture, and is therefore

fully upward compatible with applications that run on

processors implementing the earlier generation

MIPS I-III instruction sets. Additionally, the ACT5260

includes two implementation specific instructions not

found in the baseline MIPS IV ISA but that are useful

in the embedded market place. Described in detail in

the QED RM5260 datasheet, these instructions are

integer multiply-accumulate and 3-operand integer

multiply.

The ACT5260 integer unit includes thirty-two

general purpose 64-bit registers, a load/store

architecture with single cycle ALU operations (add,

sub, logical, shift) and an autonomous multiply/divide

unit. Additional register resources include: the HI/LO

result registers for the two-operand integer multiply/

divide operations, and the program counter(PC).

HARDWARE OVERVIEW

The ACT5260 offers a high-level of integration

targeted at high-performance embedded

applications. Some of the key elements of the

ACT5260 are briefly described below.

Superscalar Dispatch

The ACT5260 has an efficient asymmetric

superscalar dispatch unit which allows it to issue an

integer instruction and a floating-point computation

instruction simultaneously. With respect to

superscalar issue, integer instructions include alu,

branch, load/store, and floating-point load/store,

while floating-point computation instructions include

floating-point add, subtract, combined multiply-add,

converts, etc. In combination with its high throughput

fully pipelined floating-point execution unit, the

superscalar capability of the ACT5260 provides

unparalleled price/performance in computationally

intensive embedded applications.

CPU Registers

Like all MIPS ISA processors, the ACT5260 CPU

has a simple, clean user visible state consisting of 32

general purpose registers, two special purpose

registers for integer multiplication and division, a

program counter, and no condition code bits.

Register File

The ACT5260 has thirty-two general purpose

registers with register location 0 hard wired to zero.

These registers are used for scalar integer

operations and address calculation. The register file

has two read ports and one write port and is fully

bypassed to minimize operation latency in the

pipeline.

ALU

The ACT5260 ALU consists of the integer adder/

subtractor, the logic unit, and the shifter. The adder

performs address calculations in addition to

arithmetic operations, the logic unit performs all

logical and zero shift data moves, and the shifter

performs shifts and store alignment operations. Each

of these units is optimized to perform all operations in

a single processor cycle

For additional Detail Information regarding the

operation of the Quantum Effect Design (QED)

RISCMark

Microprocessor see the latest QED datasheet

(Revision 1.1 July 1998).

RM5260, 64-Bit Superscalar

Pipeline

For integer operations, loads, stores, and other

non-floating-point operations, the ACT5260 uses the

simple 5-stage pipeline also found in the circuits

R4600, R4700, and R5000. In addition to this

standard pipeline, the ACT5260 uses an extended

seven stage pipeline for floating-point operations.

Like the R5000, the ACT5260 does virtual to physical

translation in parallel with cache access.

Aeroflex Circuit Technology SCD5260 REV A 3/29/99 Plainview NY (516) 694-6700

2

Page 3

Absolute Maximum Ratings

1

Symbol Rating Range Units

2

to 4.6 V

V

TERM

Tc

T

BIAS

T

STG

I

IN

I

OUT

Notes:

1. Stresses above those listed under "AbsoluteMaximums Rating" may cause permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2. V

IN minimum = -2.0V for pulse width less than 15nS. VIN maximum should not exceed +5.5 Volts.

3. When V

4. No more than one output should be shorted at one time. Duration of the short should not exceed more than 30 second.

IN < 0V or VIN > Vcc.

Terminal Voltage with respect to GND

Operating Temperature

Case Temperature under Bias

Storage Temperature

DC Input Current

DC Output Current

-0.5

-55 to +125 °C

-55 to +125 °C

-55 to +125 °C

20

3

mA

50 mA

Recommended Operating Conditions

Symbol Parameter Minimum Maximum Units

V

CC

V

IH

V

IL

T

C

Power Supply Voltage

Input High Voltage

Input Low Voltage

Operating Temperature Case

For 133MHz Parts only

+3.135 +3.465 V

0.7V

CC

-0.5 0.2V

V

+ 0.5 V

CC

CC

-55 +125 °C

-40 +125 °C

V

(VCC = 3.3V ±5%; 133MHz parts: Tc =-40°C to +125°C, All other parts Tc =-55°C to +125°C)

DC Characteristics

Parameter Sym Conditions

Output Low Voltage

Output High Voltage

Output Low Voltage

Output High Voltage

Input High Voltage

Input Low Voltage

Input Current

Input Current

Input Current

Input Capacitance

Output Capacitance

Aeroflex Circuit Technology SCD5260 REV A 3/29/99 Plainview NY (516) 694-6700

V

V

V

V

C

OL1

OH1

OL2

OH2

V

V

I

IN1

I

IN2

I

IN3

C

OUT

IH

IL

IN

IOL = 20 µA

IOL = 20 µA

IOL = 4 mA

IOL = 4 mA

V

= 0V

IN

V

= V

IN

V

IN

CC

= 5.5V

3

100 / 133 / 150MHz

Min Max

- 0.1 V

Vcc - 0.1 - V

- 0.4 V

2.4 - V

0.7V

-0.5 0.2V

CC

V

+ 0.5 V

CC

CC

-20 +20 µA

-20 +20 µA

-250 +250 µA

- 10 pF

- 10 pF

Units

V

Page 4

Power Consumption

Parameter Symbol Conditions

Active Operating

Supply Current

Standby Current

Notes:

5. Typical integer instruction mix and cache miss rates.

I

CC1

I

CC2

I

CC3

I

SB1

I

SB1

CL = 0pF,

No SysAD activity

CL = 50pF, R4000 write

protocol without FPU operation

CL = 50pF, write re-issue or

pipelined writes

CL = 0pF

CL = 50pF

AC Characteristics

(VCC = 3.3V ±5%; 133MHz parts: Tc =-40°C to +125°C, All other parts Tc =-55°C to +125°C)

Capacitive Load Deration

Symbol Parameter

100MHz, 3.3V 133MHz, 3.3V 150MHz, 3.3V

5

Max Typ5 Max Typ5 Max

Typ

Units

800 1550 800 1550 1000 1750 mA

1000 1750 1000 1750 1150 1950 mA

1100 2000 1100 2000 1250 2250 mA

75 150 75 150 100 175 mA

75 150 75 150 100 175 mA

100 / 133 / 150MHz

Units

Minimum Maximum

LD

C

Load Derate

Clock Parameters

Parameter Symbol Test Conditions

SysClock High

SysClock Low

SysClock Frequency

6

SysClock Period

Clock Jitter for SysClock

SysClock Rise Time

SysClock Fall Time

ModeClock Period

t

SCHigh

t

SCLow

t

SCP

t

JitterIn

t

SCRise

t

SCFall

t

ModeCKP

Transition < 5ns

Transition < 5ns

- 2 ns/25pF

100/133/150MHz

Units

Min Max

4 - ns

4 - ns

33 75 MHz

- 30 ns

- ±250 ps

- 5 ns

- 5 ns

- 256*t

SCP

ns

JTAG Clock Period

Notes:

6. Operation of the ACT5260 is only guaranteed with the Phase Loop enabled.

Aeroflex Circuit Technology SCD5260 REV A 3/29/99 Plainview NY (516) 694-6700

t

JTAGCKP

4

- 4*t

SCP

ns

Page 5

System Interface Parameters

7

Parameter Symbol Test Conditions

100MHz 133MHz 150MHz

Min Max Min Max Min Max

Data Output

Data Setup

Data Hold

Notes: -

7. Timmings are are measured from from 1.5V of the clock to 1.5V of the signal.

8. Capacitive load for all output timing is 50pF.

8

t

DO

t

DS

t

DH

mode14...13 = 10 (fastest)

14...13 = 11

mode

14...13 = 00

mode

14...13 = 01 (slowest)

mode

t

= 5ns

RISE

t

= 5ns

FALL

1.0 7.0 1.0 7.0 1.0 7.0 ns

1.0 7.5 1.0 7.5 1.0 7.5 ns

1.0 8.0 1.0 8.0 1.0 8.0 ns

1.0 8.5 1.0 8.5 1.0 8.5 ns

5.0 - 5.0 - 5.0 - ns

2.0 - 2.0 - 2.0 - ns

Boot Time Interface Parameters

Parameter Symbol Test Conditions

Units

100/133/150MHz

Units

Min Max

Mode Data Setup

Mode Data Hold

t

t

DS

DH

4 - SysClock cycles

0 - SysClock cycles

Aeroflex Circuit Technology SCD5260 REV A 3/29/99 Plainview NY (516) 694-6700

5

Page 6

.0236 (.51)

.0158 (.49)

.005 (.127)

.008 (.258)

Package Information – "F17" – CQFP 208 Leads

1.131 (28.727) SQ

1.109 (28.169) SQ

10453

52

105

1.009 (25.63)

.9998 (25.37)

51 Spaces at .0197

(51 Spaces at .50)

Pin 1 Chamfer

Detail "A"

.010R MIN

.015 (.381)

.010R MIN

.009 (.229)

.130 (3.302)

MAX

0°±5°

.100 (2.540)

.080 (2.032)

.009 (.253)

.007 (.178)

.035 (.889)

.025 (.635)

Detail "A"

1

208

.960 (24.384) SQ

REF

1.331 (33.807)

1.269 (32.233)

Note: Pin rotation is opposite of QEDs PQUAD due to cavity-up construction.

156

157

.055 (1.397)

REF

.055 (1.397)

.045 (1.143)

.115 (2.921)

MAX

Units: Inches (Millimeters)

Future Package – "P10" – PGA 179 Pins (Advanced)

Bottom View Side View

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

V

U

T

R

P

N

M

L

1.840

K

J

H

G

F

E

D

C

B

A

1.700

BSC

1.880

1.700

BSC

1.840

1.880

Aeroflex Circuit Technology SCD5260 REV A 3/29/99 Plainview NY (516) 694-6700

6

.100

BSC

.018

.050

.221

MAX

Page 7

ACT5260 Microprocessor CQFP Pinouts – "F17"

Pin # Function Pin # Function Pin # Function Pin # Function

1 Vcc (3.3V) 53 NC 105 Vcc (3.3V) 157 NC

2 NC 54 NC 106 NMI* 158 NC

3 NC 55 NC 107 ExtRqst* 159 NC

4 Vcc (3.3V) 56 Vcc (3.3V) 108 Reset* 160 NC

5 Vss 57 Vss 109 ColdReset* 161 Vcc (3.3V)

6 SysAD4 58 ModeIn 110 VccOK 162 Vss

7 SysAD36 59 RdRdy* 111 BigEndian 163 SysAD28

8 SysAD5 60 WrRdy* 112 Vcc (3.3V) 164 SysAD60

9 SysAD37 61 ValidIn* 113 Vss 165 SysAD29

10 Vcc (3.3V) 62 ValidOut* 114 SysAD16 166 SysAD61

11 Vss 63 Release* 115 SysAD48 167 Vcc (3.3V)

12 SysAD6 64 VccP 116 Vcc (3.3V) 168 Vss

13 SysAD38 65 VssP 117 Vss 169 SysAD30

14 Vcc (3.3V) 66 SysClock 118 SysAD17 170 SysAD62

15 Vss 67 Vcc (3.3V) 119 SysAD49 171 Vcc (3.3V)

16 SysAD7 68 Vss 120 SysAD18 172 Vss

17 SysAD39 69 Vcc (3.3V) 121 SysAD50 173 SysAD31

18 SysAD8 70 Vss 122 Vcc (3.3V) 174 SysAD63

19 SysAD40 71 Vcc (3.3V) 123 Vss 175 SysADC2

20 Vcc (3.3V) 72 Vss 124 SysAD19 176 SysADC6

21 Vss 73 SysCmd0 125 SysAD51 177 Vcc (3.3V)

22 SysAD9 74 SysCmd1 126 Vcc (3.3V) 178 Vss

23 SysAD41 75 SysCmd2 127 Vss 179 SysADC3

24 Vcc (3.3V) 76 SysCmd3 128 SysAD20 180 SysADC7

25 Vss 77 Vcc (3.3V) 129 SysAD52 181 Vcc (3.3V)

26 SysAD10 78 Vss 130 SysAD21 182 Vss

27 SysAD42 79 SysCmd4 131 SysAD53 183 SysADC0

28 SysAD11 80 SysCmd5 132 Vcc (3.3V) 184 SysADC4

29 SysAD43 81 Vcc (3.3V) 133 Vss 185 Vcc (3.3V)

30 Vcc (3.3V) 82 Vss 134 SysAD22 186 Vss

31 Vss 83 SysCmd6 135 SysAD54 187 SysADC1

32 SysAD12 84 SysCmd7 136 Vcc (3.3V) 188 SysADC5

33 SysAD44 85 SysCmd8 137 Vss 189 SysAD0

34 Vcc (3.3V) 86 SysCmdP 138 SysAD23 190 SysAD32

35 Vss 87 Vcc (3.3V) 139 SysAD55 191 Vcc (3.3V)

36 SysAD13 88 Vss 140 SysAD24 192 Vss

37 SysAD45 89 Vcc (3.3V) 141 SysAD56 193 SysAD1

38 SysAD14 90 Vss 142 Vcc (3.3V) 194 SysAD33

39 SysAD46 91 Vcc (3.3V) 143 Vss 195 Vcc (3.3V)

40 Vcc (3.3V) 92 Vss 144 SysAD25 196 Vss

41 Vss 93 Int0* 145 SysAD57 197 SysAD2

42 SysAD15 94 Int1* 146 Vcc (3.3V) 198 SysAD34

43 SysAD47 95 Int2* 147 Vss 199 SysAD3

44 Vcc (3.3V) 96 Int3* 148 SysAD26 200 SysAD35

45 Vss 97 Int4* 149 SysAD58 201 Vcc (3.3V)

46 ModeClock 98 Int5* 150 SysAD27 202 Vss

47 JTDO 99 Vcc (3.3V) 151 SysAD59 203 NC

48 JTDI 100 Vss 152 Vcc (3.3V) 204 NC

49 JTCK 101 NC 153 Vss 205 NC

50 JTMS 102 NC 154 NC 206 NC

51 Vcc (3.3V) 103 NC 155 NC 207 Vcc (3.3V)

52 Vss 104 NC 156 Vss 208 Vss

Aeroflex Circuit Technology SCD5260 REV A 3/29/99 Plainview NY (516) 694-6700

7

Page 8

CIRCUIT TECHNOLOGY

Ordering Information

Part Number Screening

Speed

(MHz)

Package

ACT-5260PC-100F17C Commercial Temperature (0°C to +70°C) 100 208 Lead CQFP

ACT-5260PC-133F17C Commercial Temperature (0°C to +70°C) 133 208 Lead CQFP

ACT-5260PC-150F17C Commercial Temperature (0°C to +70°C) 150 208 Lead CQFP

ACT-5260PC-100F17I Industrial Temperature (-40°C to +85°C) 100 208 Lead CQFP

ACT-5260PC-133F17I Industrial Temperature (-40°C to +85°C) 133 208 Lead CQFP

ACT-5260PC-150F17I Industrial Temperature (-40°C to +85°C) 150 208 Lead CQFP

ACT-5260PC-100F17T Military Temperature (-55°C to +125°C) 100 208 Lead CQFP

ACT-5260PC-133F17T Reduced Military Temperature (-40°C to +125°C) 133 208 Lead CQFP

ACT-5260PC-150F17T Military Temperature (-55°C to +125°C) 150 208 Lead CQFP

ACT-5260PC-100F17M Military Temperature, Screened* (-55°C to +125°C) 100 208 Lead CQFP

ACT-5260PC-133F17M Reduced Military Temperature, Screened* (-40°C to +125°C) 133 208 Lead CQFP

ACT-5260PC-150F17M Military Temperature, Screened* (-55°C to +125°C) 150 208 Lead CQFP

Part Number Breakdown

ACT– 5260 PC – 100 F17 M

Aeroflex Circuit

Technology

Base Processor Type

Cache Style

PC = Primary Cache

Maximum Pipeline Freq.

100 = 100MHz

133 = 133MHz (Screening: T & M -40°C to +125°C only)

150 = 150MHz

200 = 200MHZ (Future option)

* Screened to the individual test methods of MIL-STD-883

Specifications subject to change without notice.

Aeroflex Circuit Technology

35 South Service Road

Plainview New York 11803

C = Commercial Temp, 0°C to +70°C

I = Industrial Temp, -40°C to +85°C

T = Military Temp, -55°C to +125°C

M = Military Temp, -55°C to +125°C, Screened

Q = MIL-PRF-38534 Compliant/SMD if applicable

F17 = 1.120" SQ 208 Lead CQFP

F24 = 1.120" SQ Inverted 208 Lead CQFP

(Consult Factory)

P10 = 1.86"SQ PGA 179 pins with shoulder

Future Product

Telephone: (516) 694-6700

FAX: (516) 694-6715

Toll Free Inquiries: (800) 843-1553

www.aeroflex.com/act1.htm E-Mail: sales-act@aeroflex.com

Aeroflex Circuit Technology SCD5260 REV A 3/29/99 Plainview NY (516) 694-6700

8

Screening

*

Package Type & Size

Surface Mount Package

Thru-Hole Package

Loading...

Loading...