Page 1

M

e

m

ory

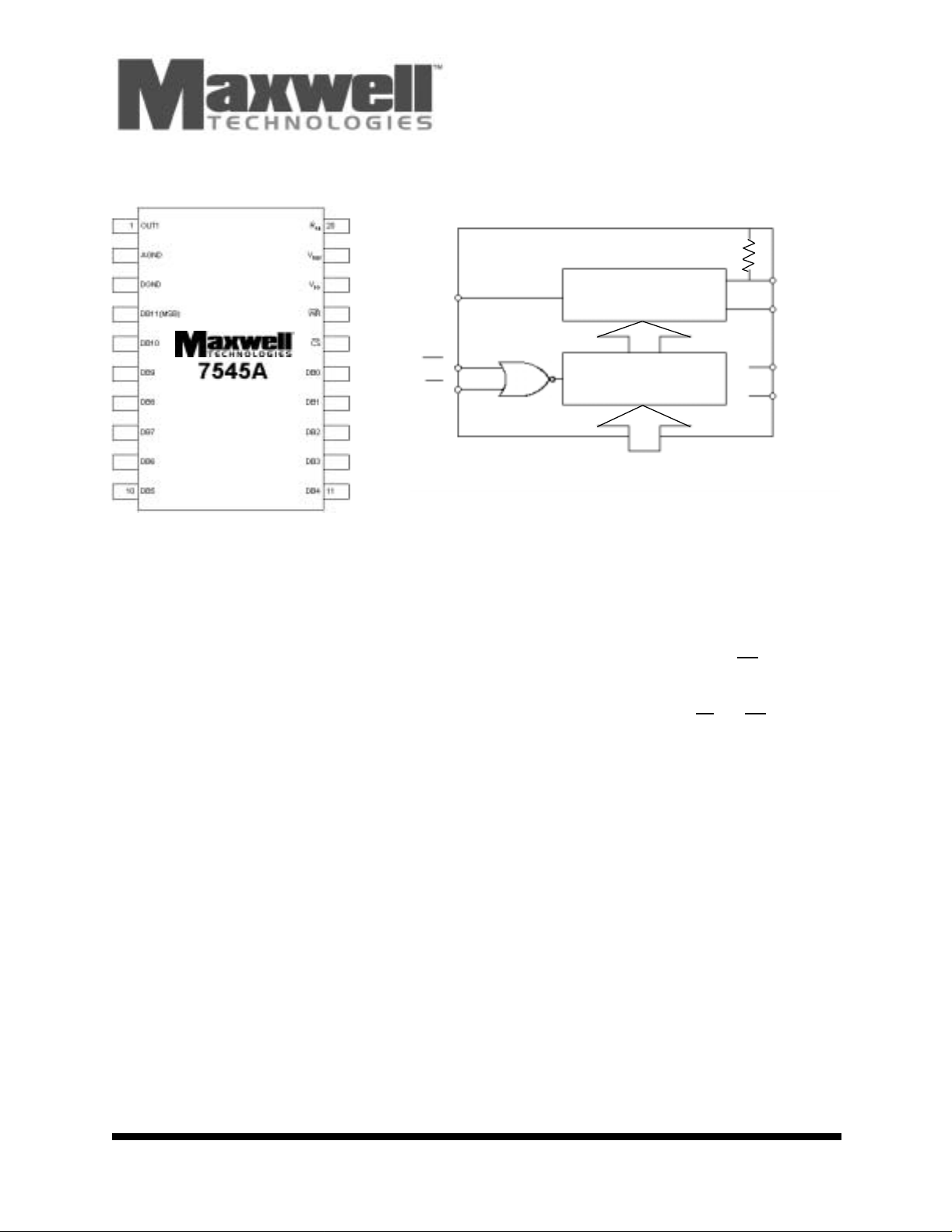

7545A

12-Bit Buffered Multiplying

Digital to Analog Converter

R

FB

R

V

REF

12-BIT MULTIPYING

DAC

12

OUT1

AGND

WR

CS

FEATURES:

•RAD-PAK® patented shielding against natural space radia-

tion

• Total dose hardness:

- > 100 krad (Si), depending upon space mission

• Excellent single event effects

- SEL

: > 120 MeV/mg/cm

TH

- SEUTH: > 120 MeV/mg/cm2 using all 1’s

• Package:

- 20 pin R

- 20 pin R

• Low gain temperature coefficient:

- 5 ppm/

• Fast interface timing

• Single +5 V to +15 V supply

AD-PAK® Flat Pack

AD-PAK® DIP

°

C typ.

2

V

INPUT D A TA LATCH E S

12

DB11-DBO

DD

DGND

DESCRIPTION:

Maxwell Technologies’ 7545A is a 12-bit CMOS-buffered multiplying DAC with internal data latches, which features a

greater than 100 krad (Si) total dose tolerance, depending

upon space mission. The 7545A features a WR

100 ns which allows interfacing to a much wider range of fast

8-bit and 16-bit microprocessors. It is loaded by a single 12-bit

wide word under the control of the CS

these control inputs low makes the input latches transparent

allowing unbuffered operation of the DAC. The 7545A is particularly suitable for single supply operations and applications

with wide temperature variations.

Maxwell Technologies' patented R

ogy incorporates radiation shielding in the microcircuit package. It eliminates the need for box shielding while providing

the required radiation shielding for a lifetime in orbit or space

mission. In a GEO orbit, R

krad (Si) radiation dose tolerance. This product is available

with screening up to Class S.

AD-PAK® packaging technol-

AD-PAK provides greater than 100

pulse width of

and WR inputs; tying

(858) 503-3300- Fax: (858) 503-3301- www.maxwell.com

02.05.02 REV 4

All data sheets are subject to change without notice

©2001 Maxwell Technologies

All rights reserved.

1

Page 2

M

e

m

ory

12-Bit Buffered Multiplying

Digital to Ana log Converter

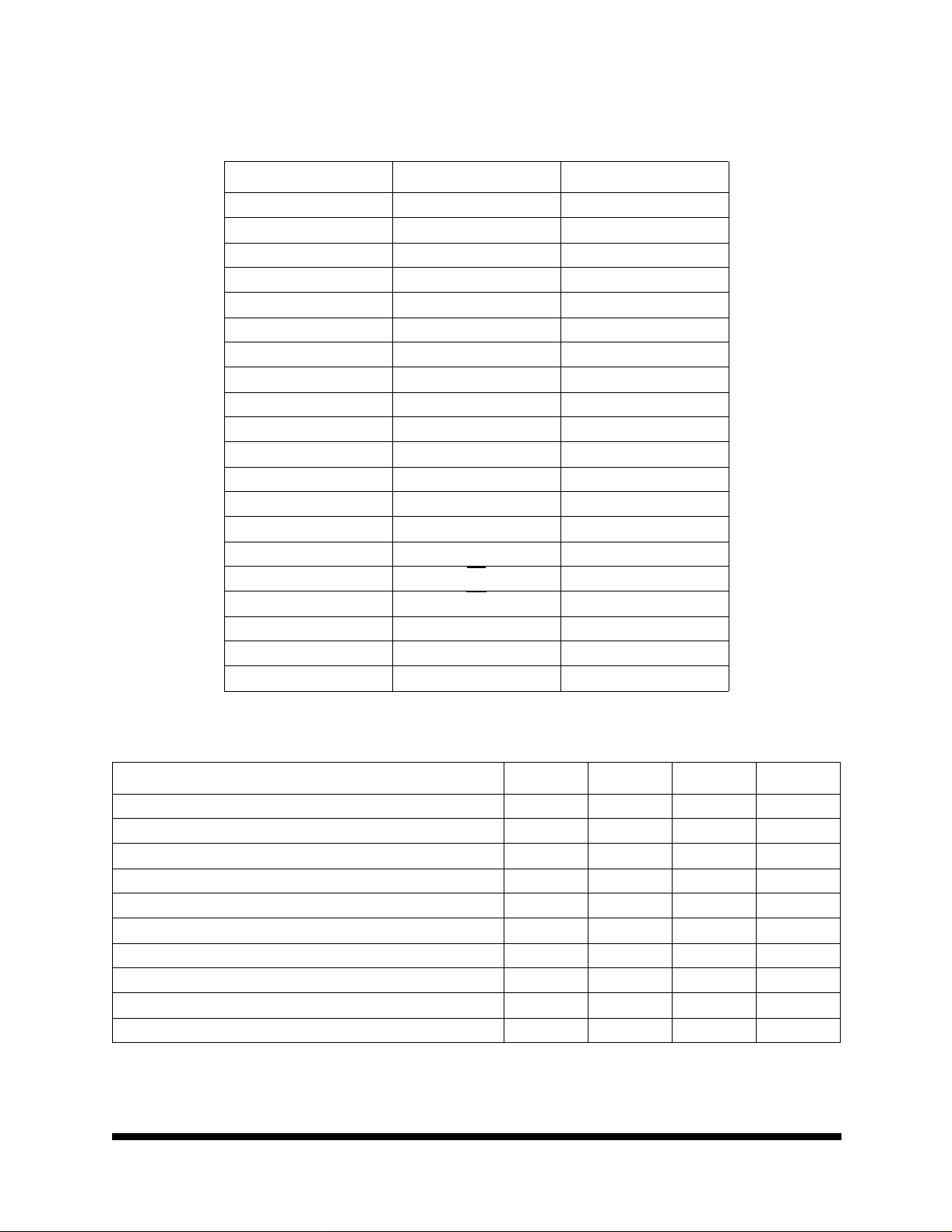

TABLE 1. 7545A PINOUT DESCRIPTION

PIN SYMBOL DESCRIPTION

1 OUT 1 Output Current

2 AGND Analog Ground

3 DGND Digital Ground

4 DB 11 Data Bit 11 (MSB)

5 DB 10 Data Bit 10

6 DB 9 Data Bit 9

7 DB 8 Data Bit 8

8 DB 7 Data Bit 7

9 DB 6 Data Bit 6

10 DB 5 Data Bit 5

11 DB 4 Data Bit 4

12 DB 3 Data Bit 3

13 DB 2 Data Bit 2

14 DB 1 Data Bit 1

15 DB 0 Data Bit 0 (LSB)

16 CS

17 WR

18 V

19 V

20 RFB Feedback Resistance

DD

REF

7545A

Chip Select (Active Low)

Write (Active Low)

Digital Supply Voltage

Reference Input

TABLE 2. 7545A ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL MIN MAX UNIT

VDD to DGND -- -0.3 17 V

Digital Input Voltage to DGND -- -0.3 V

, V

V

RFB

V

PIN1

AGND to DGND -- -0.3 V

Power Dissipation to 75

Thermal Impedance — Flat Package

Thermal Impedance — DIP Package

Operating Temperature -- -55 125

Storage Temperature Range T

to DGND -- -- 25 V

REF

to DGND -- -0.3 VDD + 0.3 V

°

CP

02.05.02 REV 4

Θ

Θ

D

JC

JC

S

-- 450 mW

-- 6.08 °C/W

-- 6.04 °C/W

-65 150

+ 0.3 V

DD

+ 0.3 V

DD

°

C

°

C

©2001 Maxwell Technologies

All rights reserved.

2All data sheets are subject to change without notice

Page 3

M

e

m

ory

12-Bit Buffered Multiplying

Digital to Analog Converter

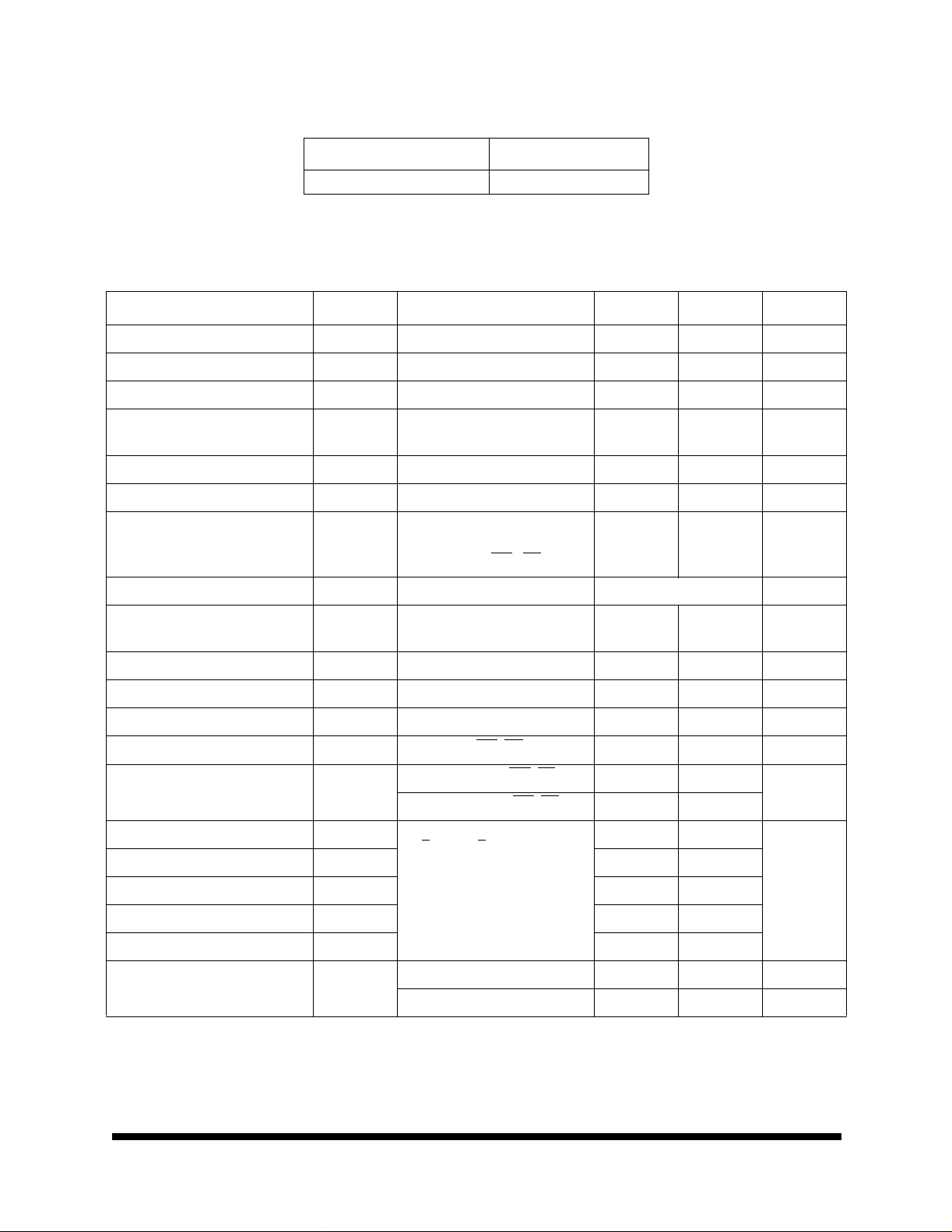

TABLE 3. DELTA LIMITS

PARAMETER VARIATION

7545A

I

DD

± 10%

TABLE 4. 754 5A SP ECIFICA TIO NS

(VDD = +5 V, TA = -55 TO 125 °C UNLESS OTHERWISE NOTED)

EST SYMBOL TEST CONDITION MIN MAX UNIT

T

Resolution RES 12 -- Bits

Relative Accuracy RA -1/ 2 1/2 LSB

Differential Nonlinearity DNL 12-Bit Monotonic T

Gain Error

1

A

DAC Register Loaded with

E

MIN

to T

MAX

1111 1111 11 11

Gain Temperature Coefficient

2

Power Supply Rejection PSRR ∆V

Output Current Settling Time

2

TC

AE

DD = +/- 5% -0.004 0.004 %/%

t

SL

To 1/2LSB; OUT1 Load = 100Ω,

DAC Output Measured from

Falling Edge of WR

. CS = 0V

Feed through Error FT 5 (typical) mV p-p

Reference Input Resistance

(Pin 19 to Ground)

2

R

IN

-1 1 LSB

-4 4 LSB

-5 5 ppm/°C

-- 1 µs

10 20 KΩ

Digital Input High Voltage V

Digital Input Low Voltage V

Digital Input Leakage Current I

Digital Input Capacitance

Output Capacitance

Chip Select to Write Setup Time

Chip Select to Write Hold Time

Write Pulse Width

Data Setup Time

Data Hold Time

3

Supply Current from V

2

2

3

3

3

3

DD

1. Measured using feedback resistor.

2. Guaranteed by design.

C

IN

C

OUT1

t

CS

t

CH

t

WR

t

DS

t

DH

I

DD

IH

IL

VIN = 0 V or V

DB0 - DB11; WR, CS -- 15 pF

IN

DD

2.4 -- V

-- 0.8 V

-10 10 µA

DB0 - DB11 = 0 V, WR, CS = 0V -- 70 pF

DB0 - DB11 = V

, WR, CS = 0V -- 150

DD

tCS > tWR, tCH > 0 170 -- nS

0-170 -150 --

5--

All Digital Inputs VIL or V

All Digital Inputs 0 or V

DD

IH

2

-- 2 mA

-- 100 µA

02.05.02 REV 4

3All data sheets are subject to change without notice

©2001 Maxwell Technologies

All rights reserved.

Page 4

M

e

m

ory

12-Bit Buffered Multiplying

7545A

Digital to Analog Converter

TABLE 5. 7545A SPECIFICATIONS

VDD = +15 TA = -55 TO 125 °C UNLESS OTHERWISE NOTED)

RESOLUTION RES 12 BITS

RELATIVE ACCURACY RA -1/2 1/2 LSB

D

IFFERENTIAL NONLINEARITY DNL 12-BIT MONOTONIC TMIN TO TMAX -1 1 LSB

T

EST SYMBOL TEST CONDITION MIN MAX UNIT

Differential Nonlinearity DNL 12-Bit Monotonic T

Gain Error

1

A

DAC Register Loaded with

E

MIN

to T

MAX

-1 1 LSB

-4 4 LSB

1111 1111 11 11

Gain Temperature Coefficient

2

Power Supply Rejection PSRR ∆V

Output Current Settling Time

2

TC

AE

=+/- 5% -0.004 0.004 %/%

DD

t

SL

To 1/2LSB; OUT1 Load = 100Ω,

-5 5 ppm/°C

-- 1 µs

DAC Output Measured from

Falling Edge of WR

. CS = 0V

Feed through Error FT 5 (typical) mV p-p

Reference Input Resistance

(Pin 19 to Ground)

2

Digital Input High Voltage V

Digital Input Low Voltage V

Digital Input Leakage Current I

Digital Input Capacitance

Output Capacitance

Chip Select toWrite Setup TIme

Chip Select to Write Hold Time

Write Pulse Width

Data Setup Time

Data Hold Time

3

Supply Current from V

2

2

3

3

3

3

DD

C

R

IN

IH

IL

IN

C

IN

OUT1

t

CS

t

CH

t

WR

t

DS

t

DH

I

DD

VIN = 0 V or V

DD

DB0 - DB11; WR, CS -- 15 pF

DB0 - DB11 = 0 V, WR, CS = 0V -- 70 pF

DB0 - DB11 = V

, WR, CS = 0V -- 150

DD

tCS > tWR, tCH > 095--nS

All Digital Inputs VIL or V

All Digital Inputs 0 or V

IH

DD2

10 20 KΩ

13.5 -- V

-- 1.5 V

-10 10 µA

0-95 -80 --

5--

-- 2 mA

-- 100 µA

1. Measured using feedback resistor.

2. Guaranteed by design.

02.05.02 REV 4

4All data sheets are subject to change without notice

©2001 Maxwell Technologies

All rights reserved.

Page 5

M

e

m

ory

12-Bit Buffered Multiplying

Digital to Analog Converter

FIGURE 1. WRITE CYCLE TIMING DIAGRAM

FIGURE 2. MODE SELECTION TABLE

MODE SELECTIO N

7545A

WRITE MODE:

and WR low, DAC responds to data

CS

bus (DB0 - DB11) inputs

HOLD MODE:

Either CS or WR high, data bus (DB0 DB11) is locked out ; DAC holds last data

present when WR

state.

or CS assumed high

02.05.02 REV 4

5All data sheets are subject to change without notice

©2001 Maxwell Technologies

All rights reserved.

Page 6

M

e

m

ory

12-Bit Buffered Multiplying

Digital to Analog Converter

7545A

20 PIN RAD-PAK® DUAL IN LINE PACKAGE

SYMBOL

MIN NOM MAX

A -- 0.202 0.230

b 0.014 0.018 0.026

b2 0.045 0.050 0.065

c 0.008 0.010 0.018

D -- 1.000 1.060

E 0.220 0.290 0.310

eA 0.300 BSC

eA/2 0.150 BSC

e 0.100 BSC

L 0.125 0.145 0.155

Q 0.015 0.045 0.070

S1 0.005 0.025 -S2 0.005 -- --

N20

DIMENSION

D20-01

Note: All dimensions in inches

02.05.02 REV 4

6All data sheets are subject to change without notice

©2001 Maxwell Technologies

All rights reserved.

Page 7

M

e

m

ory

12-Bit Buffered Multiplying

Digital to Analog Converter

7545A

20 PIN RAD-PAK® FLAT PACKAGE

SYMBOL

MIN NOM MAX

A 0.128 0.141 0.154

b 0.015 0.017 0.022

c 0.003 0.005 0.009

D 0.470 0.480 0.490

E 0.287 0.295 0.303

E1 -- -- 0.333

E2 0.155 0.160 -E3 0.030 0.068 --

e 0.050 BSC

L 0.350 0.380 0.390

Q 0.026 0.034 0.045

S1 0.005 0.007 --

N20

F20-01

Note: All dimensions in inches

DIMENSION

02.05.02 REV 4

7All data sheets are subject to change without notice

©2001 Maxwell Technologies

All rights reserved.

Page 8

M

e

m

ory

12-Bit Buffered Multiplying

7545A

Digital to Analog Converter

Important Notice:

These data sheets are created using the chip m anufacturers publ ished specifications. Maxwell Technologies verifies

functional ity by testing key parameters eit her by 100% testing, sample testing or char acterization.

The specifications presented within these data sheets represent the latest and most accurate informati on available to

date. However, these specifications are subject to change without notice and Maxwell Technologies assumes no

responsibility for the use of this information.

Maxwell Technologies’ products are not authorized for use as critical components in life support devices or systems

without express written approval from Maxwell Technologies.

Any claim against Maxwell Technologies must be made within 90 days f rom the date of shipment from Maxwell Technologies. Maxwell Technologies’ liability shall be limited to replacement of defective parts.

02.05.02 REV 4

8All data sheets are subject to change without notice

©2001 Maxwell Technologies

All rights reserved.

Page 9

M

e

m

ory

12-Bit Buffered Multiplying

C)

l

Digital to Analog Converter

Product Ordering Options

Model Number

7545A

7545A

RP

F X

Feature

Screening Flow

Package

Option De tails

S = Maxwell Class S

B = Maxwell Class B

E = Engineering (testing @ +25°

I = Industrial (testing @ -55°C,

+25°C, +125°C)

D = Dual In-line Package (DIP)

F = Flat Pack

Radiation Feature

Base Product

Nomenclature

02.05.02 REV 4

AD-PAK® package

RP = R

12-Bit Buffered Multiplying Digita

to Analog Converter

©2001 Maxwell Technologies

All rights reserved.

9All data sheets are subject to change without notice

Loading...

Loading...