Datasheet 74LVX08SJX, 74LVX08SJ, 74LVX08MX, 74LVX08MTCX, 74LVX08MTC Datasheet (Fairchild Semiconductor)

...Page 1

May 1993

Revised March 1999

74LVX08 Low Voltage Quad 2-Input AND Gate

© 1999 Fairchild Semiconductor Corporation DS011602.prf www.fairchildsemi.com

74LVX08

Low Voltage Quad 2-Input AND Gate

General Description

The LVX08 contains four 2-input AND gates. The inputs tolerate voltages up to 7V allowing the interface of 5V systems to 3V systems.

Features

■ Input voltage level translation from 5V to 3V

■ Ideal for low power/low noise 3.3V applications

■ Guaranteed simultaneous switching noise level and

dynamic threshold performance

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending su ffix let te r “X” to the ordering code .

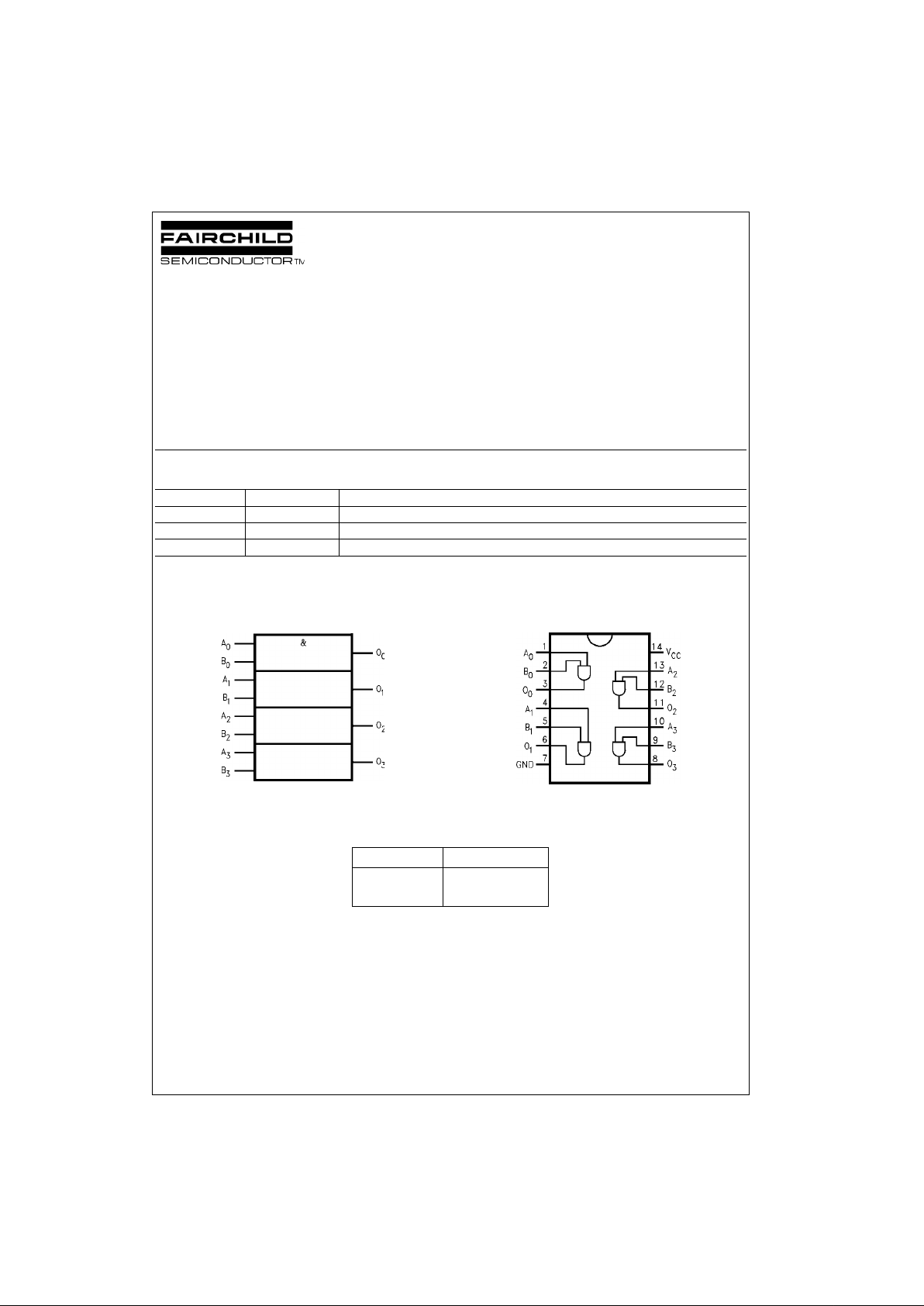

Logic Symbol

IEEE/IEC

Connection Diagram

Pin Descriptions

Order Number Package Number Package Description

74LVX08M M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow

74LVX08SJ M14D 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74LVX08MTC MTC14 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Pin Names Description

A

n

, B

n

Inputs

O

n

Outputs

Page 2

www.fairchildsemi.com 2

74LVX08

Absolute Maximum Ratings(Note 1) Recommended Operating

Conditions

(Note 2)

Note 1: The “Absolute Maximum Ratin gs” are those v alues beyon d which

the safety of the dev ice cannot be guaranteed. T he device sh ould not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The “Recommend ed O peratin g Cond itions” t able w ill defin e the co ndition s

for actual device operation.

Note 2: Unused inputs must be held HIGH or LOW. They may not float.

DC Electrical Characteristics

Noise Characteristics

(Note 3)

Note 3: Input tr = tf = 3 ns

Supply Voltage (VCC) −0.5V to +7.0V

DC Input Diode Current (I

IK

)

V

I

= −0.5V −20 mA

DC Input Voltage (V

I

) −0.5V to 7V

DC Output Diode Current (I

OK

)

V

O

= −0.5V −20 mA

V

O

= VCC + 0.5V +20 mA

DC Output Voltage (V

O

) −0.5V to VCC + 0.5V

DC Output Source

or Sink Current (I

O

) ±25 mA

DC V

CC

or Ground Current

(I

CC

or I

GND

) ±50 mA

Storage Temperature (T

STG

) −65°C to +150°C

Power Dissipation 180 mW

Lead Temperature (T

L

)

(Soldering, 10 seconds) 240°C

Supply Voltage (V

CC

) 2.0V to 3.6V

Input Voltage (V

I

)0V to 5.5V

Output Voltage (V

O

) 0V to V

CC

Operating Temperature (TA) −40°C to +85°C

Input Rise and Fall Time (∆t/∆V) 0 ns/V to 100 ns/V

Symbol Parameter

V

CC

TA = +25°C TA = −40°C to +85°C

Units Conditions

Min Typ Max Min Max

V

IH

HIGH Level Input Voltage 2.0 1 1.5

3.0 2.0 2.0 V

3.6 2.4 2.4

V

IL

LOW Level Input Voltage 2.0 0.5 0.5

3.0 0.8 0.8 V

3.6 0.8 0.8

V

OH

HIGH Level Output Voltage 2.0 1.9 2.0 1.9 VIN = VIL or VIHIOH = −50 µA

3.0 2.9 3.0 2.9 V IOH = −50 µA

3.0 2.58 2.48 IOH = −4 mA

V

OL

LOW Level Output Voltage 2.0 0.0 0.1 0.1 VIN = V

IL

or VIHIOL = 50 µA

3.0 0.0 0.1 0.1 V IOL = 50 µA

3.0 0.36 0.44 IOL = 4 mA

I

IN

Input Leakage Current 3.6 ±0.1 ±1.0 µAVIN = 5.5V or GND

I

CC

Quiescent Supply Current 3.6 2.0 20.0 µAVIN = VCC or GND

Symbol Parameter

V

CC

(V)

TA = 25°C

Units

CL (pF)

Typ Limit

V

OLP

Quiet Output Maximum Dynamic V

OL

3.3 0.3 0.5 V 50

V

OLV

Quiet Output Minimum Dynamic V

OL

3.3 −0.3 −0.5 V 50

V

IHD

Minimum HIGH Level Dynamic Input Voltage 3.3 2.0 V 50

V

ILD

Maximum LOW Level Dynamic Input Voltage 3.3 0.8 V 50

Page 3

3 www.fairchildsemi.com

74LVX08

AC Electrical Characteristics

Note 4: Parameter gu aranteed by design. t

OSLH

= |t

PLHm

− t

PLHn

|, t

OSHL

= |t

PHLm

− t

PHLn

|

Capacitance

Note 5: CPD is defined as the value of the internal equivalent capacitance whic h is calculated from th e operating current cons umption without load.

Symbol Parameter

V

CC

(V)

TA = +25°C TA =−40°C to +85°C

Units

CL (pF)

Min Typ Max Min Max

t

PLH

Propagation Delay Time 2.7 6.3 11.4 1.0 13.5

ns

15

t

PHL

8.8 14.9 1.0 17.0 50

3.3 ± 0.3 4.8 7.1 1 .0 8.5 15

7.3 10.6 1.0 12.0 50

t

OSLH

Output to Output Skew 2.7 1.5 1.5

ns

50

t

OSHL

(Note 4) 3.3 1.5 1.5

Symbol Parameter

TA = +25°C TA = −40°C to +85°C

Units

Min Typ Max Min Max

C

IN

Input Capacitance 4 10 10 pF

C

PD

Power Dissipation 18 pF

Capacitance (Note 5)

Page 4

www.fairchildsemi.com 4

74LVX08

Physical Dimensions inches (millimeters) unless otherwise noted

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow

Package Number M14A

14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

Package Number M14D

Page 5

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

74LVX08 Low Voltage Quad 2-Input AND Gate

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are dev ic es or syste ms

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided i n the labe li ng, can be re asonably expected to result in a significant injury to the

user.

2. A critical componen t in any com ponent o f a l ife supp ort

device or system whose failu re to perform can b e reasonably expected to c ause th e fa i lure of the li fe s upp or t

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Package Number MTC14

Loading...

Loading...