Page 1

DATA SH EET

Product specification

File under Integrated Circuits, IC06

December 1990

INTEGRATED CIRCUITS

74HC/HCT390

Dual decade ripple counter

For a complete data sheet, please also download:

•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

Page 2

December 1990 2

Philips Semiconductors Product specification

Dual decade ripple counter 74HC/HCT390

FEATURES

• Two BCD decade or bi-quinary counters

• One package can be configured to divide-by-2, 4, 5, 10,

20, 25, 50 or 100

• Two master reset inputs to clear each decade counter

individually

• Output capability: standard

• ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT390 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT390 are dual 4-bit decade ripple counters

divided into four separately clocked sections. The counters

have two divide-by-2 sections and two divide-by-5

sections. These sections are normally used in a BCD

decade or bi-quinary configuration, since they share a

common master reset input (nMR). If the two master reset

inputs (1MR and 2MR) are used to simultaneously clear all

8 bits of the counter, a number of counting configurations

are possible within one package. The separate clocks

(n

CP0and nCP1) of each section allow ripple counter or

frequency division applications of divide-by-2, 4, 5, 10, 20,

25, 50 or 100.

Each section is triggered by the HIGH-to-LOW transition of

the clock inputs (nCP0and nCP1). For BCD decade

operation, the nQ0output is connected to the nCP1 input

of, the divide-by-5 section. For bi-quinary decade

operation, the nQ3 output is connected to the nCP0input

and nQ0becomes the decade output.

The master reset inputs (1MR and 2MR) are active HIGH

asynchronous inputs to each decade counter which

operates on the portion of the counter identified by the “1”

and “2” prefixes in the pin configuration. A HIGH level on

the nMR input overrides the clocks and sets the four

outputs LOW.

QUICK REFERENCE DATA

GND = 0 V; T

amb

=25°C; tr=tf= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (PD in µW):

PD=CPD× V

CC

2

× fi+∑ (CL× V

CC

2

× fo) where:

fi= input frequency in MHz

fo= output frequency in MHz

∑ (CL× V

CC

2

× fo) = sum of outputs

CL= output load capacitance in pF

VCC= supply voltage in V

2. For HC the condition is VI= GND to V

CC

For HCT the condition is VI= GND to VCC−1.5 V

SYMBOL PARAMETER CONDITIONS

TYPICAL

UNIT

HC HCT

t

PHL

/ t

PLH

propagation delay CL= 15 pF; VCC=5V

n

CP0 to nQ

0

14 18 ns

n

CP1 to nQ

1

15 19 ns

n

CP1to nQ

2

23 26 ns

n

CP1to nQ

3

15 19 ns

nMR to Q

n

16 18 ns

f

max

maximum clock frequency nCP0,nCP

1

66 61 MHz

C

I

input capacitance 3.5 3.5 pF

C

PD

power dissipation capacitance per counter notes 1 and 2 20 21 pF

Page 3

December 1990 3

Philips Semiconductors Product specification

Dual decade ripple counter 74HC/HCT390

ORDERING INFORMATION

See

“74HC/HCT/HCU/HCMOS Logic Package Information”

.

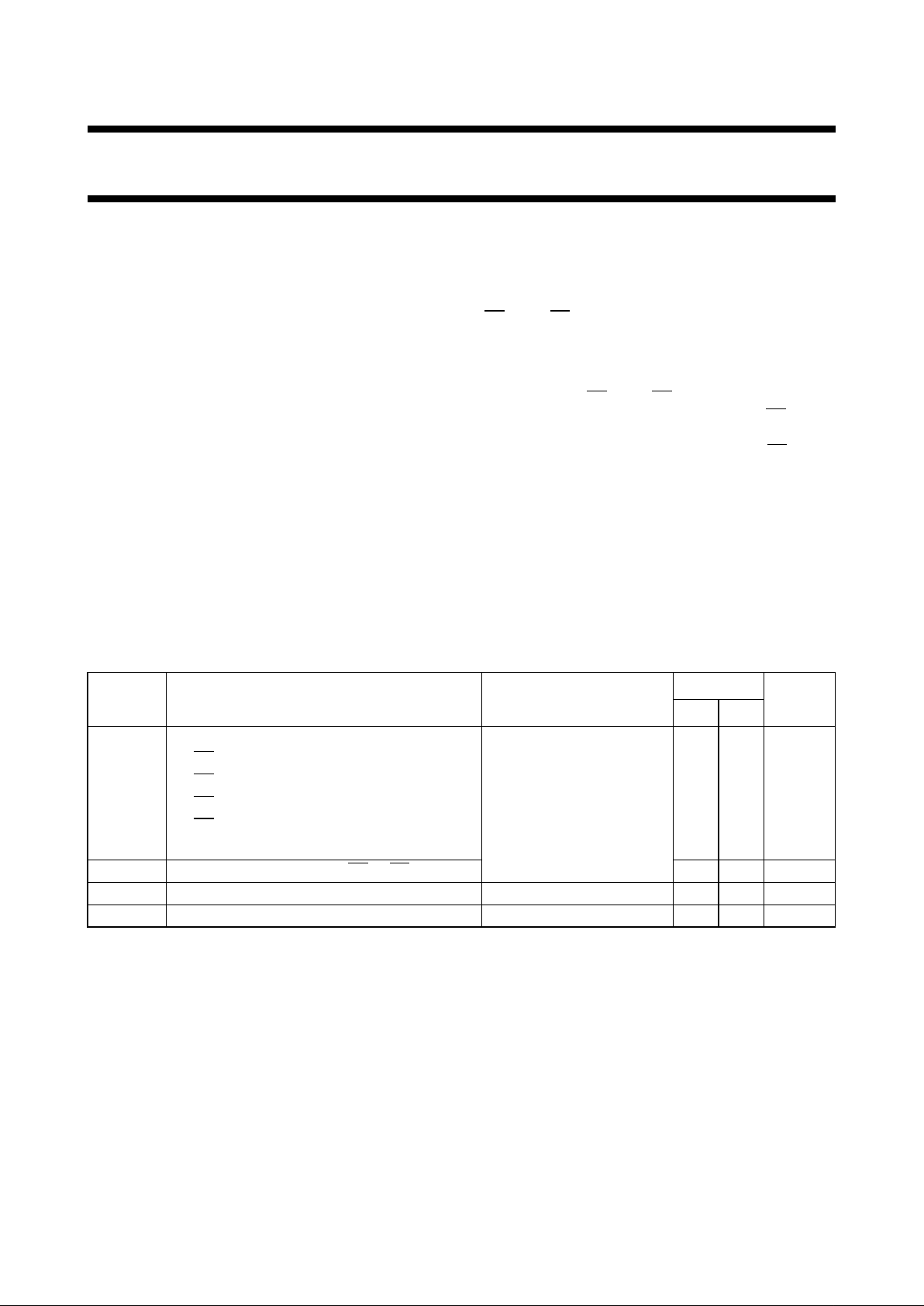

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1, 15 1

CP0, 2CP

0

clock input divide-by-2 section (HIGH-to-LOW, edge-triggered)

2, 14 1MR, 2MR asynchronous master reset inputs (active HIGH)

3, 5, 6, 7 1Q

0

to 1Q

3

flip-flop outputs

4, 12 1

CP1, 2CP

1

clock input divide-by-5 section (HIGH-to-LOW, edge triggered)

8 GND ground (0 V)

13, 11, 10, 9 2Q

0

to 2Q

3

flip-flop outputs

16 V

CC

positive supply voltage

Fig.1 Pin configuration. Fig.2 Logic symbol. Fig.3 IEC logic symbol.

Page 4

December 1990 4

Philips Semiconductors Product specification

Dual decade ripple counter 74HC/HCT390

Fig.4 Functional diagram.

BCD COUNT SEQUENCE

FOR 1/2 THE “390”

Notes

1. Output Q

0

connected to nCP

1

with counter input on nCP0.

H = HIGH voltage level

L = LOW voltage level

COUNT

OUTPUTS

Q0Q1Q

2

Q

3

0 LLLL

1 HLLL

2LHLL

3 HHLL

4 LLHL

5HLHL

6 LHHL

7 HHHL

8 LLLH

9 HLLH

BI-QUINARY COUNT SEQUENCE

FOR 1/2 THE “390”

Note

1. Output Q

3

connected to nCP

0

with counter input on nCP1.

COUNT

OUTPUTS

Q0Q1Q

2

Q

3

0 LLLL

1LHLL

2 LLHL

3 LHHL

4 LLLH

5 HLLL

6 HHLL

7HLHL

8 HHHL

9 HLLH

Fig.5 Logic diagram (one counter).

Page 5

December 1990 5

Philips Semiconductors Product specification

Dual decade ripple counter 74HC/HCT390

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see

“74HC/HCT/HCU/HCMOS Logic Family Specifications”

.

Output capability: standard

ICC category: MSI

AC CHARACTERISTICS FOR 74HC

GND = 0 V; t

r=tf

= 6 ns; CL=50pF

SYMBOL PARAMETER

T

amb

(°C)

UNIT

TEST CONDITIONS

74HC

V

CC

(V)

WAVEFORMS

+25 −40 to +85 −40 to +125

min. typ. max. min. max. min. max.

t

PHL

/ t

PLH

propagation delay

nCP0 to nQ

0

47

17

14

145

29

25

180

36

31

220

44

38

ns 2.0

4.5

6.0

Fig.6

t

PHL

/ t

PLH

propagation delay

nCP1 to nQ

1

50

18

14

155

31

26

195

39

33

235

47

40

ns 2.0

4.5

6.0

Fig.6

t

PHL

/ t

PLH

propagation delay

nCP1 to nQ

2

74

27

22

210

42

36

265

53

45

315

63

54

ns 2.0

4.5

6.0

Fig.6

t

PHL

/ t

PLH

propagation delay

nCP1 to nQ

3

50

18

14

155

31

26

195

39

33

235

47

40

ns 2.0

4.5

6.0

Fig.6

t

PHL

propagation delay

nMR to nQ

n

52

19

15

165

33

28

205

41

35

250

50

43

ns 2.0

4.5

6.0

Fig.7

t

THL

/ t

TLH

output transition time 19

7

6

75

15

13

95

19

16

110

22

19

ns 2.0

4.5

6.0

Fig.6

t

W

clock pulse width

nCP0, nCP

1

80

16

14

19

7

6

100

20

17

120

24

20

ns 2.0

4.5

6.0

Fig.6

t

W

master reset pulse width

HIGH

80

17

14

28

10

8

105

21

18

130

26

22

ns 2.0

4.5

6.0

Fig.7

t

rem

removal time

nMR to nCP

n

75

15

13

22

8

6

95

19

16

110

22

19

ns 2.0

4.5

6.0

Fig.7

f

max

maximum clock pulse

frequency

nCP0, nCP

1

6.0

30

35

20

60

71

4.8

24

28

4.0

20

24

MHz 2.0

4.5

6.0

Fig.6

Page 6

December 1990 6

Philips Semiconductors Product specification

Dual decade ripple counter 74HC/HCT390

DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see

“74HC/HCT/HCU/HCMOS Logic Family Specifications”

.

Output capability: standard

ICC category: MSI

Note to HCT types

The value of additional quiescent supply current (∆I

CC

) for a unit load of 1 is given in the family specifications.

To determine ∆ICC per input, multiply this value by the unit load coefficient shown in the table below.

AC CHARACTERISTICS FOR 74HCT

GND = 0 V; t

r=tf

= 6 ns; CL=50pF

INPUT UNIT LOAD COEFFICIENT

nCP

0

nCP1, nMR

0.45

0.60

SYMBOL PARAMETER

T

amb

(°C)

UNIT

TEST CONDITIONS

74HCT

V

CC

(V)

WAVEFORMS

+25 −40 to +85 −40 to +125

min. typ. max. min. max. min. max.

t

PHL

/ t

PLH

propagation delay

nCP0 to nQ

0

21 34 43 51 ns 4.5 Fig.6

t

PHL

/ t

PLH

propagation delay

nCP1 to nQ

1

22 38 48 57 ns 4.5 Fig.6

t

PHL

/ t

PLH

propagation delay

nCP1 to nQ

2

30 51 64 77 ns 4.5 Fig.6

t

PHL

/ t

PLH

propagation delay

nCP1 to nQ

3

22 38 48 57 ns 4.5 Fig.6

t

PHL

propagation delay

nMR to nQ

n

21 36 45 54 ns 4.5 Fig.7

t

THL

/ t

TLH

output transition time 7 15 19 22 ns 4.5 Fig.6

t

W

clock pulse width

nCP0, nCP

1

18 8 23 27 ns 4.5 Fig.6

t

W

master reset pulse width

HIGH

17 10 21 26 ns 4.5 Fig.7

t

rem

removal time

nMR to nCP

n

15 8 19 22 ns 4.5 Fig.7

f

max

maximum clock pulse

frequency

nCP0, nCP

1

27 55 22 18 MHz 4.5 Fig.6

Page 7

December 1990 7

Philips Semiconductors Product specification

Dual decade ripple counter 74HC/HCT390

AC WAVEFORMS

PACKAGE OUTLINES

See

“74HC/HCT/HCU/HCMOS Logic Package Outlines”

.

Fig.6 Waveforms showing the clock (nCPn) to output (nQn) propagation delays, the clock pulse width, the output

transition times and the maximum clock frequency.

(1) HC : VM= 50%; VI= GND to VCC.

HCT : V

M

= 1.3 V; VI= GND to 3 V.

Fig.7 Waveforms showing the master reset (nMR) pulse width, the master reset to output (nQn) propagation

delays and the master reset to clock (nCPn) removal time.

(1) HC : VM= 50%; VI= GND to VCC.

HCT : V

M

= 1.3 V; VI= GND to 3 V.

Loading...

Loading...