Page 1

Philips Semiconductors Product specification

74ABT651Octal transceiver/register, inverting (3-State)

FEA TURES

•Independent registers for A and B buses

•The 74ABT651 is the inverting version of the 74ABT652

•Multiplexed real-time and stored data

•3-State outputs

•Live insertion/extraction permitted.

•Power-up 3-State

•Power-up reset

•Output capability: +64mA/–32mA

•Latch-up protection exceeds 500mA per Jedec Std 17

•ESD protection exceeds 2000 V per MIL STD 883 Method 3015

and 200 V per Machine Model

QUICK REFERENCE DATA

SYMBOL PARAMETER

t

PLH

t

PHL

C

C

I

CCZ

IN

I/O

Propagation delay

CPBA to An or CPAB to Bn

Input capacitance VI = 0V or V

I/O capacitance Outputs disabled; VO = 0V or V

Total supply current Outputs disabled; VCC =5.5V 110 µA

DESCRIPTION

The 74ABT651 high-performance BiCMOS device combines low

static and dynamic power dissipation with high speed and high

output drive.

The 74ABT651 transceiver/register consists of bus transceiver

circuits with 3-State outputs, D-type flip-flops, and control circuitry

arranged for multiplexed transmission of data directly from the input

bus or the internal registers. Data on the A or B bus will be clocked

into the registers as the appropriate clock pin goes High. Output

Enable (OEAB, OEBA

bus management.

The following examples demonstrate the four fundamental

bus-management functions that can be performed with the

74ABT651.

The select pins determine whether data is stored or transferred

through the device in real time.

The output enable pins determine the direction of the data flow.

CONDITIONS

= 25°C; GND = 0V

T

amb

CL = 50pF; VCC = 5V

CC

) and Select (SAB, SBA) pins are provided for

TYPICAL UNIT

3.8

4.4

4 pF

CC

7 pF

ns

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA DWG NUMBER

24-Pin Plastic DIP –40°C to +85°C 74ABT651 N 74ABT651 N SOT222-1

24-Pin plastic SO –40°C to +85°C 74ABT651 D 74ABT651 D SOT137-1

24-Pin Plastic SSOP Type II –40°C to +85°C 74ABT651 DB 74ABT651 DB SOT340-1

24-Pin Plastic TSSOP Type I –40°C to +85°C 74ABT651 PW 74ABT651PW DH SOT355-1

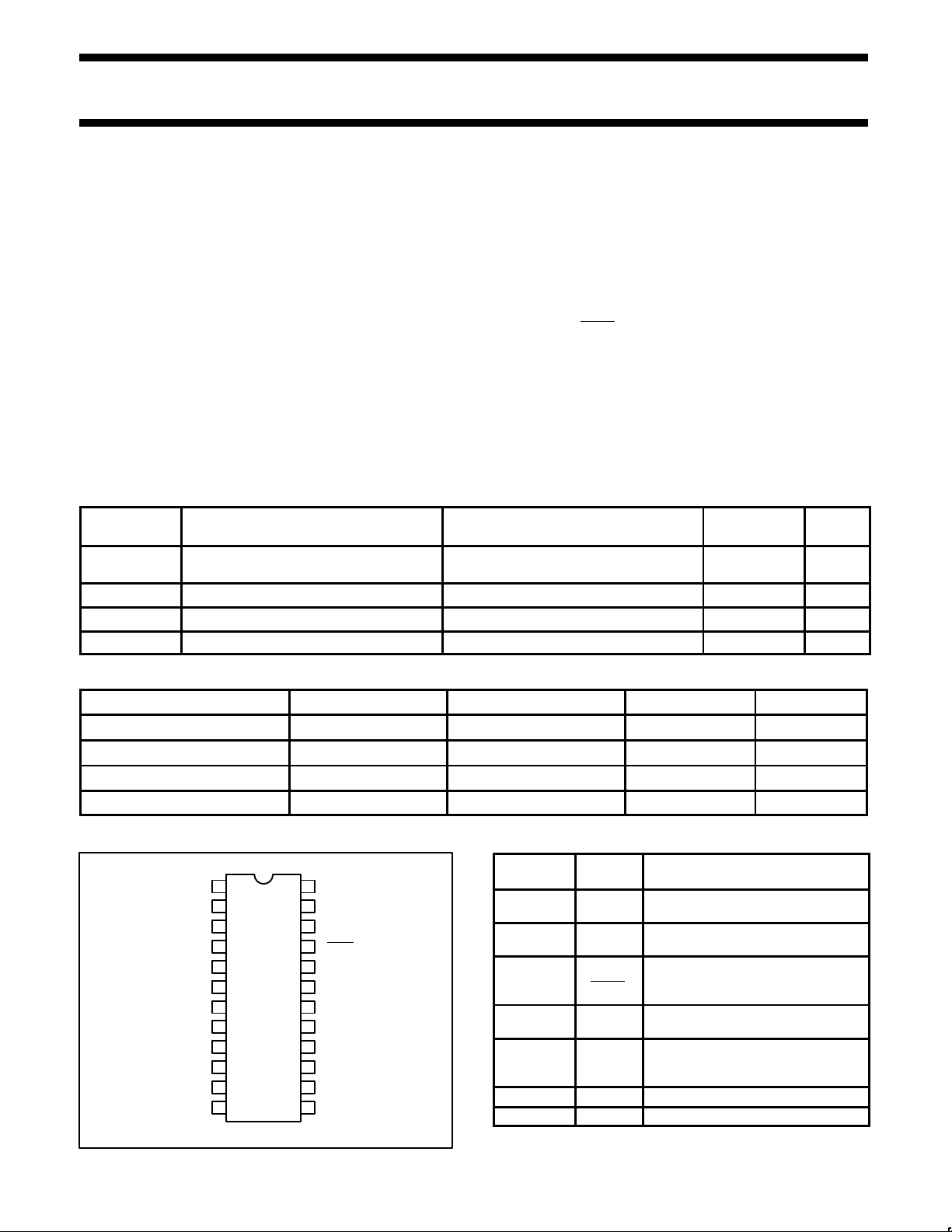

PIN CONFIGURA TION

1

CPAB

2

SAB

3

OEAB

4

A0

5

A1

6

A2

7

A3

8

A4

9

A5

10

A6

11

A7

12

GND

V

24

CC

CPBA

23

SBA

22

OEBA

21

B0

20

B1

19

B2

18

B3

17

B4

16

B5

15

B6

14

B713

SA00094

PIN DESCRIPTION

PIN

NUMBER

1, 23

2, 22

3, 21

4, 5, 6, 7, 8,

9, 10, 11

20, 19, 18,

17, 16, 15,

14, 13

12 GND Ground (0V)

24 V

SYMBOL FUNCTION

CPAB /

CPBA

SAB /

SBA

OEAB /

OEBA

A0 – A7 Data inputs/outputs (A side)

B0 – B7 Data inputs/outputs (B side)

CC

A to B clock input / B to A clock input

A to B select input / B to A select input

A to B Output Enable input /

B to A Output Enable input

(active–Low)

Positive supply voltage

1995 Sep 06 853-1783 15703

1

Page 2

Philips Semiconductors Product specification

74ABT651Octal transceiver/register, inverting (3-State)

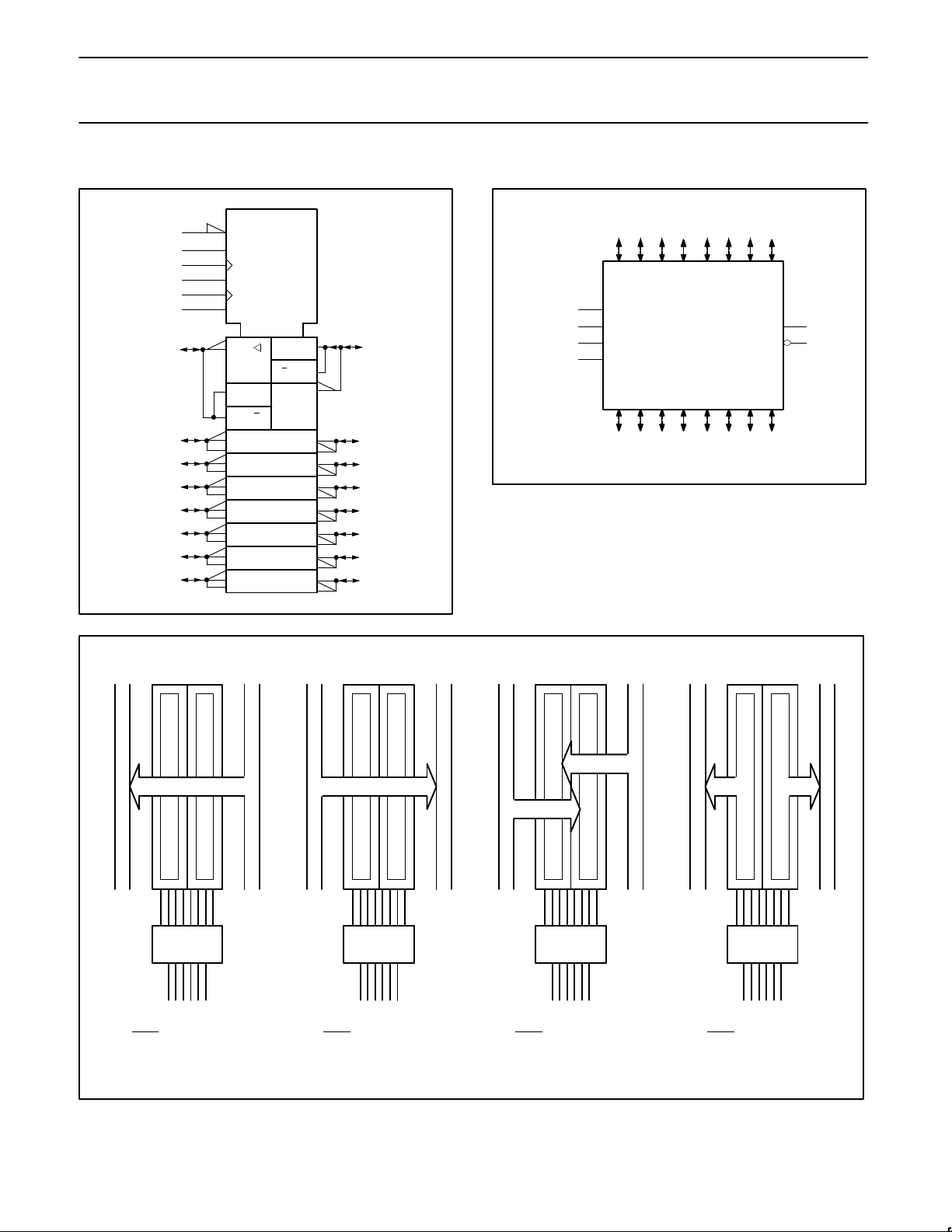

LOGIC SYMBOL (IEEE/IEC)

21

3

23

22

1

2

4

5

6

7

8

9

10

11

EN1 [BA]

EN2 [AB]

C4

G5

C6

G7

1

1

6D 7

17

54D

5

1

1

2

LOGIC SYMBOL

4567 891011

A0 A1 A2 A3 A4 A5 A6 A7

23 CPBA

22 SBA

20

19

18

17

16

15

14

13

SA00125

SAB2

CPAB1

B0 B1 B2 B3 B4 B5 B6 B7

20 19 18 17 16 15 14 13

3OEAB

21OEBA

SA00095

REAL TIME BUS TRANSFER

BUS B TO BUS A

REAL TIME BUS TRANSFER

BUS A TO BUS B

STORAGE FROM

A, B, OR A AND B

TRANSFER STORED DATA

TO A OR B

ABABABAB

}

OEABOEBA

CPABCPBA SAB SBA

LLXXXL

OEABOEBA

HHXXLX

}

CPABCPBA SAB SBA

}

OEABOEBA

CPABCPBA SAB SBA

XH↑XXX

LXX↑XX

LH↑↑XX

}

OEABOEBA

CPABCPBA SAB SBA

H L H | L H | L H H

SA00097

1995 Sep 06

2

Page 3

Philips Semiconductors Product specification

OPERATING MODE

74ABT651Octal transceiver/register, inverting (3-State)

FUNCTION TABLE

INPUTS DATA I/O

OEAB OEBA CPAB CPBA SAB SBA An Bn

L

L

X

H

L

L

L

L

H

H

H L H or L H or L H H Output Output

H = High voltage level

L = Low voltage level

X = Don’t care

↑ = Low-to-High clock transition

* The data output function may be enabled or disabled by various signals at the OEBA

enabled, i.e., data at the bus pins will be stored on every Low-to-High transition of the clock.

** If both Select controls (SAB and SBA) are Low, then clocks can occur simultaneously. If either Select control is High, the clocks must be

staggered in order to load both registers.

H

H

H

H

X

L

L

L

H

H

H or L

↑

↑

↑

H or L

↑

X

X

X

H or L

H or L

↑

H or L

↑

↑

↑

X

H or L

X

X

X

X

X

**

X

X

X

X

L

H

X

X

X

X

Input Input

Input

X**Unspecified

output*

L

H

X

X

Output Input

Input Output

Unspecified

output*

Input

Isolation

Store A and B data

Store A, Hold B

Store A in both registers

Hold A, Store B

Store B in both registers

Real time B data to A bus

Stored B

data to A bus

Real time A data to B bus

data to B bus

Store A

Stored A data to B bus

Stored B

data to A bus

and OEAB inputs. Data input functions are always

LOGIC DIAGRAM

OEBA

OEAB

CPBA

SBA

CPAB

SAB

A0

A1

A2

A3

A4

A5

A6

A7

21

3

23

22

1

2

1of 8 Channels

4

1D

C1

Q

5

6

7

8

9

10

11

DETAIL A X 7

1D

C1

Q

20

B0

19

B1

18

B2

17

B3

16

B4

15

B5

14

B6

13

B7

1995 Sep 06

SA00098

3

Page 4

Philips Semiconductors Product specification

SYMBOL

PARAMETER

UNIT

74ABT651Octal transceiver/register, inverting (3-State)

ABSOLUTE MAXIMUM RATINGS

SYMBOL

V

CC

I

IK

V

I

I

OK

V

OUT

I

OUT

T

stg

DC supply voltage –0.5 to +7.0 V

DC input diode current VI < 0 –18 mA

DC input voltage

DC output diode current VO < 0 –50 mA

DC output voltage

DC output current output in Low state 128 mA

Storage temperature range –65 to 150 °C

PARAMETER CONDITIONS RATING UNIT

3

3

1, 2

–1.2 to +7.0 V

output in Off or High state –0.5 to +5.5 V

NOTES:

1. 1Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the

device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to

absolute-maximum-rated conditions for extended periods may affect device reliability .

2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction

temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

3. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

RECOMMENDED OPERATING CONDITIONS

LIMITS

Min Max

V

CC

V

V

V

I

OH

I

OL

∆t/∆v Input transition rise or fall rate 0 10 ns/V

T

amb

DC supply voltage 4.5 5.5 V

Input voltage 0 V

I

High-level input voltage 2.0 V

IH

Low-level Input voltage 0.8 V

IL

High-level output current –32 mA

Low-level output current 64 mA

Operating free-air temperature range –40 +85 °C

CC

V

1995 Sep 06

4

Page 5

Philips Semiconductors Product specification

I

Input leakage

74ABT651Octal transceiver/register, inverting (3-State)

DC ELECTRICAL CHARACTERISTICS

LIMITS

T

= –40°C

SYMBOL PARAMETER TEST CONDITIONS T

amb

= +25°C

Min Typ Max Min Max

V

V

V

V

RST

I

OFF

IPU/I

IIH + I

IIL + I

I

CEX

I

CCH

I

CCL

I

CCZ

∆I

I

Input clamp voltage VCC = 4.5V; IIK = –18mA –0.9 –1.2 –1.2 V

IK

VCC = 4.5V; IOH = –3mA; VI = VIL or V

High–level output voltage VCC = 5.0V; IOH = –3mA; VI = VIL or V

OH

VCC = 4.5V; IOH = –32mA; VI = VIL or V

Low–level output voltage VCC = 4.5V; IOL = 64mA; VI = VIL or V

OL

3

Power-up output low voltage VCC = 5.5V; IO = 1mA; VI = GND or V

I

Input leakage

current

Control pins VCC = 5.5V; VI = GND or 5.5V ±0.01 ±1.0 ±1.0 µA

Data pins VCC = 5.5V; VI = GND or 5.5V ±5 ±100 ±100 µA

IH

IH

IH

IH

CC

2.5 3.2 2.5 V

3.0 3.7 3.0 V

2.0 2.30 2.0 V

0.42 0.55 0.55 V

0.13 0.55 0.55 V

Power-off leakage current VCC = 0.0V; VO or VI ≤ 4.5V ±5.0 ±100 ±100 µA

Power-up/down 3-State

PD

output current

3–State output High current VCC = 5.5V; VO = 2.7V; VI = VIL or V

OZH

3–State output Low current VCC = 5.5V; VO = 0.5V; VI = VIL or V

OZL

4

Output High leakage current VCC = 5.5V; VO = 5.5V; VI = GND or V

O

Output current

1

Quiescent supply current

Additional supply current per

CC

input pin

2

VCC = 2.1V; VO = 0.5V; VOE = Don’t Care;

= GND or V

V

I

CC

IH

IH

CC

±5.0 ±50 ±50 µA

5.0 50 50 µA

–5.0 –50 –50 µA

5.0 50 50 µA

VCC = 5.5V; VO = 2.5V –40 –65 –180 –40 –180 mA

VCC = 5.5V; Outputs High, VI = GND or V

VCC = 5.5V; Outputs Low, VI = GND or V

VCC = 5.5V; Outputs 3–State;

= GND or V

V

I

CC

VCC = 5.5V; one input at 3.4V,

other inputs at V

or GND; VCC = 5.5V

CC

CC

CC

110 250 250 µA

20 30 30 mA

110 250 250 µA

0.3 1.5 1.5 mA

NOTES:

1. Not more than one output should be tested at a time, and the duration of the test should not exceed one second.

2. This is the increase in supply current for each input at 3.4V.

3. For valid test results, data must not be loaded into the flip-flops (or latches) after applying the power .

4. This parameter is valid for any V

transition time of up to 100µsec is permitted.

between 0V and 2.1V, with a transition time of up to 10msec. From VCC = 2.1V to VCC = 5V ± 10%, a

CC

amb

to +85°C

UNIT

AC CHARACTERISTICS

GND = 0V, tR = tF = 2.5ns, CL = 50pF, RL = 500Ω

SYMBOL PARAMETER WA VEFORM

f

MAX

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PZH

t

PZL

t

PHZ

t

PLZ

t

PZH

t

PZL

t

PHZ

t

PLZ

1995 Sep 06

Maximum clock frequency 1 125 300 125 MHz

Propagation delay

CPAB to Bn or CPBA to An

Propagation delay

An to Bn or Bn to An

Propagation delay

SAB to Bn or SBA to An

Output enable time

to An

OEBA

Output disable time

to An

OEBA

Output enable time

OEAB to Bn

Output disable time

OEAB to Bn

1

2

3

5

6

5

6

5

6

5

6

LIMITS

T

T

amb

V

= +25oC

= +5.0V

CC

amb

= +5.0V ±0.5V

V

CC

Min Typ Max Min Max

2.2

1.7

1.5

1.5

1.5

1.5

1.3

2.5

1.5

1.5

1.8

2.9

1.5

1.5

3.8

4.4

3.2

3.7

3.8

4.4

3.7

4.7

4.0

3.2

3.4

4.5

3.8

3.1

5.1

5.1

5.1

4.6

5.1

4.9

4.6

6.8

4.5

3.8

6.1

6.5

4.5

4.4

2.2

1.7

1.5

1.5

1.5

1.5

1.3

2.5

1.5

1.5

1.8

2.9

1.5

1.5

5

= -40 to

o

+85

C

5.6

5.6

6.2

5.4

6.5

5.9

5.8

8.5

5.0

4.1

6.5

7.4

5.5

5.1

UNIT

ns

ns

ns

ns

ns

ns

ns

Page 6

Philips Semiconductors Product specification

74ABT651Octal transceiver/register, inverting (3-State)

AC SETUP REQUIREMENTS

GND = 0V, tR = tF = 2.5ns, CL = 50pF, RL = 500Ω

LIMITS

T

SYMBOL PARAMETER WAVEFORM

ts(H)

(L)

t

s

th(H)

(L)

t

h

tw(H)

(L)

t

w

Setup time

An to CPAB, Bn to CPBA

Hold time

An to CPAB, Bn to CPBA

Pulse width, High or Low

CPAB or CPBA

4

4

1

AC WAVEFORMS

VM = 1.5V, VIN = GND to 3.0V

1/f

MAX

CPBA or

CPAB

An or Bn

Waveform 1. Propagation Delay, Clock Input to Output, Clock

Pulse Width, and Maximum Clock Frequency

V

M

tw(H) tw(L)

t

PHL

V

M

V

M

V

t

M

PLH

V

M

SA00087

= +25oC

amb

= +5.0V

V

CC

Min Typ Min

3.0

3.0

0.0

0.0

4.0

4.0

An or Bn

CPBA or

CPAB

NOTE: The shaded areas indicate when the input is permitted

1.2

0.8

–0.8

–0.9

1.2

1.1

V

(H)

t

s

to change for predictable output performance.

Waveform 4. Data Setup and Hold Times

T

= -40 to +85oC

amb

= +5.0V ±0.5V

V

CC

3.0

3.0

0.0

0.0

4.0

4.0

V

M

M

t

(H)

h

V

M

V

MVM

(L)

t

s

(L)

t

W

V

M

UNIT

ns

ns

ns

t

(L)

h

SA00090

An or Bn

Bn or An

V

M

t

PLH

V

M

V

M

t

PHL

V

M

SA00016

Waveform 2. Propagation Delay, An to Bn or Bn to An

SBA or SAB

An or Bn

V

M

t

PHL

V

M

t

PLH

V

M

V

M

SA00089

Waveform 3. Propagation Delay, SBA to An or SAB to Bn

OEBA

OEAB

An or Bn

V

M

t

PZH

V

M

t

PHZ

V

–0.3V

V

M

OH

0V

SA00100

Waveform 5. 3–State Output Enable Time to High Level and

Output Disable Time from High Level

OEBA

OEAB

An or Bn

V

M

t

PZL

V

M

t

PLZ

V

M

VOL +0.3V

0V

SA00101

Waveform 6. 3–State Output Enable Time to Low Level and

Output Disable Time from Low Level

1995 Sep 06

6

Page 7

Philips Semiconductors Product specification

74ABT651Octal transceiver/register, inverting (3-State)

TEST CIRCUIT AND WAVEFORM

V

CC

R

PULSE

GENERATOR

V

IN

R

D.U.T.

T

V

OUT

C

L

L

R

L

Test Circuit for 3-State Outputs

SWITCH POSITION

TEST SWITCH

t

PLZ

t

PZL

closed

closed

All other open

DEFINITIONS

RL = Load resistor; see AC CHARACTERISTICS for value.

= Load capacitance includes jig and probe capacitance;

C

L

see AC CHARACTERISTICS for value.

= Termination resistance should be equal to Z

R

T

pulse generators.

OUT

of

t

W

(tF)

(tR)t

t

W

90%

V

M

V

M

10%

7.0V

90%

NEGATIVE

PULSE

POSITIVE

PULSE

10%

V

M

10% 10%

t

THL

t

TLH

90% 90%

V

M

VM = 1.5V

Input Pulse Definition

INPUT PULSE REQUIREMENTS

FAMILY

Amplitude Rep. Rate t

t

W

R

74ABT 3.0V 1MHz 500ns 2.5ns 2.5ns

t

TLH

THL

AMP (V)

0V

(tR)

(tF)

AMP (V)

0V

t

F

SA00012

1995 Sep 06

7

Loading...

Loading...