Datasheet 3D7303Z-500, 3D7303Z-50, 3D7303Z-400, 3D7303Z-40, 3D7303Z-300 Datasheet (DADD)

...Page 1

3D7303

MONOLITHIC TRIPLE

data

3

1

8

I1

VDD

FIXED DELAY LINE

(SERIES 3D7303)

FEATURES

• All-silicon, low-power CMOS technology

• TTL/CMOS compatible inputs and outputs

• Vapor phase, IR and wave solderable

• Auto-insertable (DIP pkg.)

• Low ground bounce noise

• Leading- and trailing-edge accuracy

• Delay range: 10 through 500ns

• Delay tolerance: 2% or 1.0ns

• Temperature stability: ±3% typical (0C-70C)

• Vdd stability: ±1% typical (4.75V-5.25V)

• Minimum input pulse width: 20% of total

delay

• 14-pin DIP available as drop-in replacement for

hybrid delay lines

FUNCTIONAL DESCRIPTION

The 3D7303 Triple Delay Line product family consists of fixed-delay

CMOS integrated circuits. Each package contains three matched,

independent delay lines. Delay values can range from 10ns through

500ns. The input is reproduced at the output without inversion,

shifted in time as per the user-specified dash number. The 3D7303

is TTL- and CMOS-compatible, capable of driving ten 74LS-type

loads, and features both rising- and falling-edge accuracy.

I1

1

I2

2

I3

3

GND

4

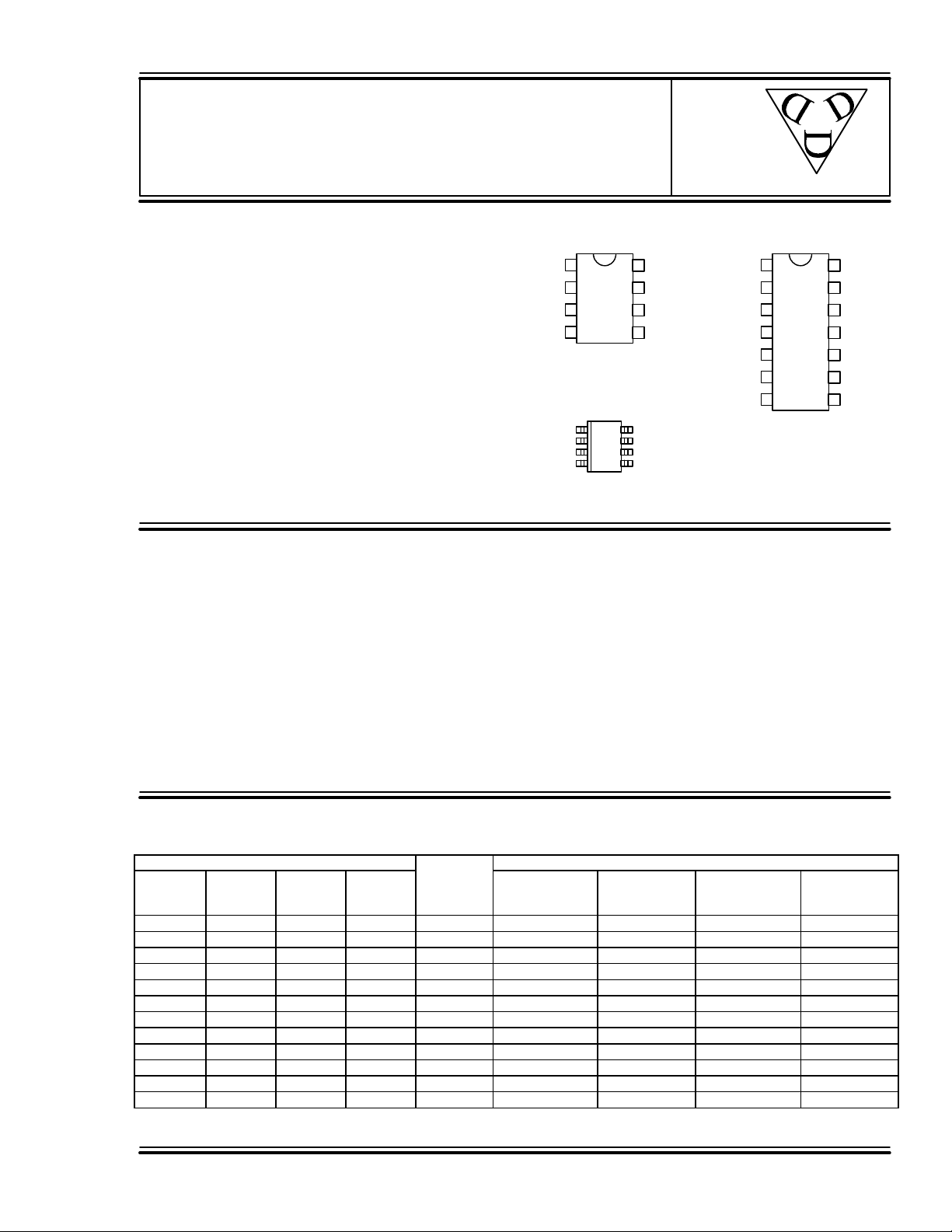

3D7303M DIP

3D7303H Gull-Wing

(300 Mil)

2

I2

3

I3

GND

4

3D7303Z SOIC

(150 Mil)

8

7

6

5

7

6

5

delay

devices, inc.

PACKAGES

O1

O2

O3

VDD

O1

O2

O3

I1

N/C

I2

N/C

I3

N/C

GND

3D7303 DIP

3D7303G Gull-Wing

3D7303K Unused pins

PIN DESCRIPTIONS

I1 Delay Line 1 Input

I2 Delay Line 2 Input

I3 Delay Line 3 Input

O1 Delay Line 1 Output

O2 Delay Line 2 Output

O3 Delay Line 3 Output

VCC +5 Volts

1

2

3

4

5

6

7

(300 Mil)

GND Ground

The all-CMOS 3D7303 integrated circuit has been designed as a

N/C No Connection

reliable, economic alternative to hybrid TTL fixed delay lines. It is

offered in a standard 8-pin auto-insertable DIP and a space saving surface mount 8-pin SOIC.

14

13

12

11

10

9

8

removed

VDD

N/C

O1

N/C

O2

N/C

O3

TABLE 1: PART NUMBER SPECIFICATIONS

PART NUMBER DELAY INPUT RESTRICTIONS

DIP-8

3D7303M

3D7303H

-10 -10 -10 -10

-15 -15 -15 -15

-20 -20 -20 -20

-25 -25 -25 -25

-30 -30 -30 -30

-40 -40 -40 -40

-50 -50 -50 -50

-100 -100 -100 -100

-200 -200 -200 -200

-300 -300 -300 -300

-400 -400 -400 -400

-500 -500 -500 -500

NOTE: Any delay between 10 and 500 ns not shown is also available. 1996 Data Delay Devices

SOIC-8

3D7303Z

DIP-14

3D7303

3D7303G

DIP-14

3D7303K

PER LINE

(ns)

10 ± 1.0

15 ± 1.0

20 ± 1.0

25 ± 1.0

30 ± 1.0

40 ± 1.0

50 ± 1.0

100 ± 2.0

200 ± 4.0

300 ± 6.0

400 ± 8.0

500 ± 10.0

Max Operating

Frequency

33.3 MHz 100.0 MHz 15.0 ns 5.0 ns

22.2 MHz 100.0 MHz 22.5 ns 5.0 ns

16.7 MHz 100.0 MHz 30.0 ns 5.0 ns

13.3 MHz 83.3 MHz 37.5 ns 6.0 ns

11.1 MHz 71.4 MHz 45.0 ns 7.0 ns

8.33 MHz 62.5 MHz 60.0 ns 8.0 ns

6.67 MHz 50.0 MHz 75.0 ns 10.0 ns

3.33 MHz 25.0 MHz 150.0 ns 20.0 ns

1.67 MHz 12.5 MHz 300.0 ns 40.0 ns

1.11 MHz 8.33 MHz 450.0 ns 60.0 ns

0.83 MHz 6.25 MHz 600.0 ns 80.0 ns

0.67 MHz 5.00 MHz 750.0 ns 100.0 ns

Absolute Max

Oper. Freq.

Min Operating

Pulse Width

Absolute Min

Oper. P.W.

Doc #96001 DATA DELAY DEVICES, INC. 1

12/2/96 3 Mt. Prospect Ave. Clifton, NJ 07013

Page 2

3D7303

APPLICATION NOTES

OPERATIONAL DESCRIPTION

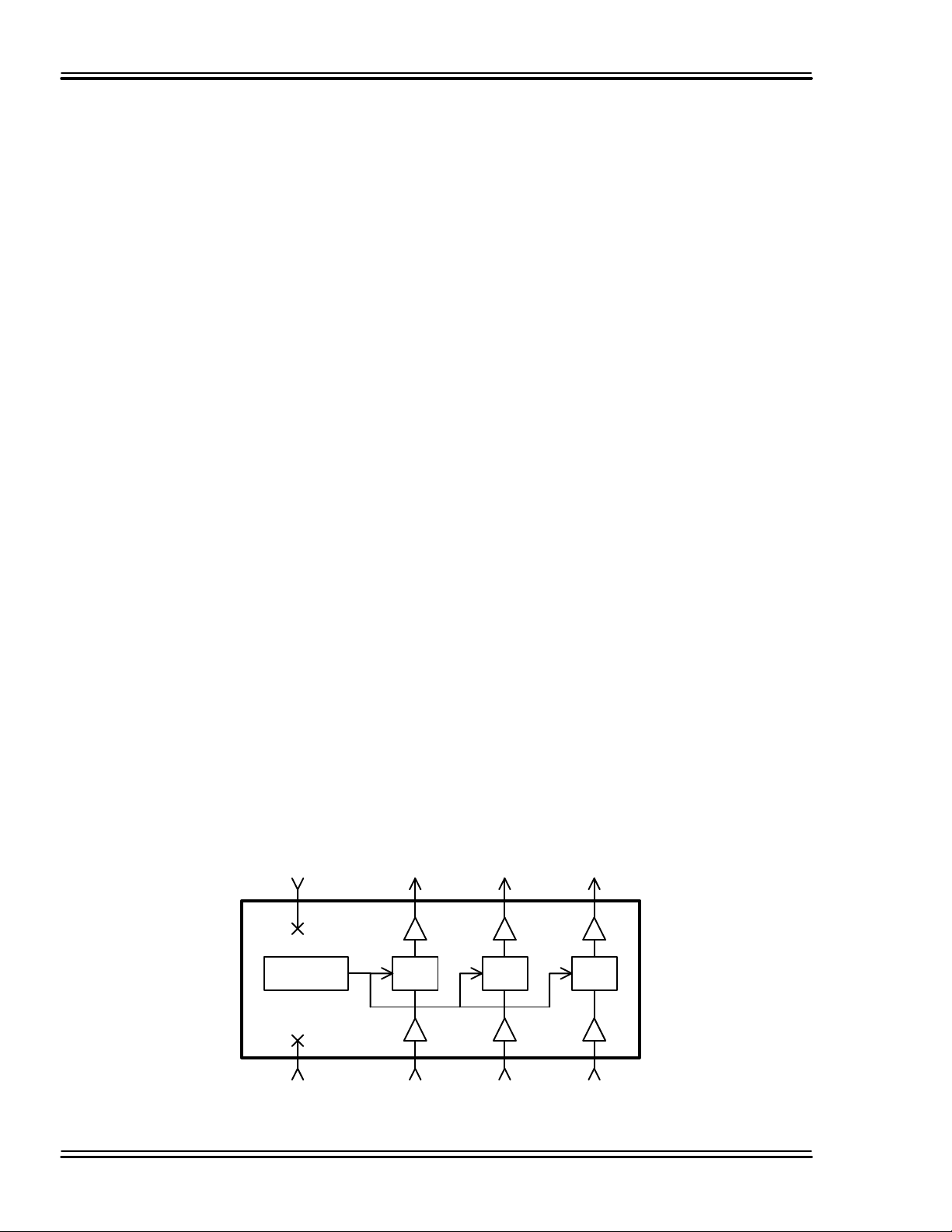

The 3D7303 triple delay line architecture is

shown in Figure 1. The individual delay lines are

composed of a number of delay cells connected

in series. Each delay line produces at its output

a replica of the signal present at its input, shifted

in time. The delay lines are matched and share

the same compensation signals, which

minimizes line-to-line delay deviations over

temperature and supply voltage variations.

INPUT SIGNAL CHARACTERISTICS

The Frequency and/or Pulse Width (high or low)

of operation may adversely impact the specified

delay accuracy of the particular device. The

reasons for the dependency of the output delay

accuracy on the input signal characteristics are

varied and complex. Therefore a Maximum and

an Absolute Maximum operating input

frequency and a Minimum and an Absolute

Minimum operating pulse width have been

specified.

OPERATING FREQUENCY

The Absolute Maximum Operating Frequency

specification, tabulated in Table 1, determines

the highest frequency of the delay line input

signal that can be reproduced, shifted in time at

the device output, with acceptable duty cycle

distortion.

The Maximum Operating Frequency

specification determines the highest frequency of

the delay line input signal for which the output

delay accuracy is guaranteed.

To guarantee the Table 1 delay accuracy for

input frequencies higher than the Maximum

Operating Frequency, the 3D7303 must be

tested at the user operating frequency.

Therefore, to facilitate production and device

identification, the part number will include a

custom reference designator identifying the

intended frequency of operation. The

programmed delay accuracy of the device is

guaranteed, therefore, only at the user specified

input frequency. Small input frequency variation

about the selected frequency will only marginally

impact the programmed delay accuracy, if at all.

Nevertheless, it is strongly recommended

that the engineering staff at DATA DELAY

DEVICES be consulted.

OPERATING PULSE WIDTH

The Absolute Minimum Operating Pulse

Width (high or low) specification, tabulated in

Table 1, determines the smallest Pulse Width of

the delay line input signal that can be

reproduced, shifted in time at the device output,

with acceptable pulse width distortion.

The Minimum Operating Pulse Width (high or

low) specification determines the smallest Pulse

Width of the delay line input signal for which the

output delay accuracy tabulated in Table 1 is

guaranteed.

To guarantee the Table 1 delay accuracy for

input pulse width smaller than the Minimum

Operating Pulse Width, the 3D7303 must be

tested at the user operating pulse width.

Therefore, to facilitate production and device

identification, the part number will include a

VDD

Temp & VDD

Compensation

GND

O1

Delay

Line

I1

O2

Delay

Line

I2

O3

Delay

Line

I3

Figure 1: 3D7303 Functional Diagram

Doc #96001 DATA DELAY DEVICES, INC. 2

12/2/96 Tel: 973-773-2299 Fax: 973-773-9672 http://www.datadelay.com

Page 3

3D7303

APPLICATION NOTES (CONT’D)

custom reference designator identifying the

intended frequency and duty cycle of operation.

The programmed delay accuracy of the device is

guaranteed, therefore, only for the user specified

input characteristics. Small input pulse width

variation about the selected pulse width will only

marginally impact the programmed delay

accuracy, if at all. Nevertheless, it is strongly

recommended that the engineering staff at

DATA DELAY DEVICES be consulted.

POWER SUPPLY AND

TEMPERATURE CONSIDERATIONS

The delay of CMOS integrated circuits is strongly

dependent on power supply and temperature.

The monolithic 3D7303 programmable delay line

utilizes novel and innovative compensation

DEVICE SPECIFICATIONS

circuitry to minimize the delay variations induced

by fluctuations in power supply and/or

temperature.

The thermal coefficient is reduced to 600

PPM/C, which is equivalent to a variation , over

the 0C-70C operating range, of ±±3% from the

room-temperature delay settings and/or 1.0ns,

whichever is greater. The power supply

coefficient is reduced, over the 4.75V-5.25V

operating range, to ±±1% of the delay settings at

the nominal 5.0VDC power supply and/or 2.0ns,

whichever is greater. It is essential that the

power supply pin be adequately bypassed

and filtered. In addition, the power bus

should be of as low an impedance

construction as possible. Power planes are

preferred.

TABLE 2: ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL MIN MAX UNITS NOTES

DC Supply Voltage V

Input Pin Voltage V

Input Pin Current I

Storage Temperature T

Lead Temperature T

DD

IN

IN

STRG

LEAD

-0.3 7.0 V

-0.3 VDD+0.3 V

-1.0 1.0 mA 25C

-55 150 C

300 C 10 sec

TABLE 3: DC ELECTRICAL CHARACTERISTICS

(0C to 70C, 4.75V to 5.25V)

PARAMETER SYMBOL MIN MAX UNITS NOTES

Static Supply Current* I

High Level Input Voltage V

Low Level Input Voltage V

High Level Input Current I

Low Level Input Current I

High Level Output Current I

Low Level Output Current I

DD

IH

IL

IH

IL

OH

OL

Output Rise & Fall Time TR & T

2.0 V

-4.0 mA VDD = 4.75V

4.0 mA VDD = 4.75V

F

30 mA

0.8 V

1

1

µA

µA

2 ns CLD = 5 pf

VIH = V

DD

VIL = 0V

VOH = 2.4V

VOL = 0.4V

*IDD(Dynamic) = 3 * CLD * VDD * F Input Capacitance = 10 pf typical

where: CLD = Average capacitance load/line (pf) Output Load Capacitance (CLD) = 25 pf max

F = Input frequency (GHz)

Doc #96001 DATA DELAY DEVICES, INC. 3

12/2/96 3 Mt. Prospect Ave. Clifton, NJ 07013

Page 4

3D7303

SILICON DELAY LINE AUTOMATED TESTING

Test

OUT1

OUT2

OUT3

OUT

TRIGINREF

TRIG

PRINTER

IN3

IN2

IN1

0.6V

0.6V

1.5V

1.5V

2.4V

2.4V

1.5V

1.5V

TEST CONDITIONS

INPUT: OUTPUT:

Ambient Temperature: 25oC ± 3oC R

Supply Voltage (Vcc): 5.0V ± 0.1V C

Input Pulse: High = 3.0V ± 0.1V Threshold: 1.5V (Rising & Falling)

Low = 0.0V ± 0.1V

Source Impedance: 50Ω Max.

Rise/Fall Time: 3.0 ns Max. (measured

between 0.6V and 2.4V )

Pulse Width: PWIN = 1.25 x Total Delay

Period: PERIN = 2.5 x Total Delay

NOTE: The above conditions are for test only and do not in any way restrict the operation of the device.

: 10KΩ ± 10%

load

: 5pf ± 10%

load

Device

Under

10KΩ

470Ω

Digital

Scope

5pf

PULSE

GENERATOR

INPUT

SIGNAL

COMPUTER

SYSTEM

DEVICE UNDER

TEST (DUT)

Figure 2: Test Setup

PW

IN

t

RISE

V

IH

t

PLH

PER

DIGITAL SCOPE/

TIME INTERVAL COUNTER

IN

t

FALL

V

IL

t

PHL

OUTPUT

SIGNAL

V

OH

V

OL

Figure 3: Timing Diagram

Doc #96001 DATA DELAY DEVICES, INC. 4

12/2/96 Tel: 973-773-2299 Fax: 973-773-9672 http://www.datadelay.com

Loading...

Loading...