PUBLICATION NO. 980479

DIGITAL

r

'"

r

00

'-

MULTIMETER

.J '-___

EPT.

""""

-~-

1

u

"

DANA

LABORATORIES,

2401

CAMPUS

IRVINE,

Copyright @ 1977 by

This book or parts thereof may

CALIFORNIA

Dana

laboratories. Inc. Printed in the United States

INC.

DRIVE

92715

PUBLICATION DATE:

not

be reproduced

in

any

form

MAY

without

TELEPHONE

TELETYPE

TELEX

1977

of

written

(714)

910-595-1136

678-341

America.

permission

833-1234

All

rights

of

the publishers.

reserved.

DIGITALY REMASTERED

OUT OF PRINT- MANUAL SCAN

S

By

ArtekMedia

P.O. BOX 175

Welch, MN 55089-0175

Phone: 651-269-4265

www.artekmedia.com

“High resolution scans of obsolete technical manuals”

If you are looking for a quality scanned technical manual in PDF format please visit our WEB

site at www.artekmedia.com or drop us an email at manuals@artekmedia.com

If you don’t see the manual you need on the list drop us a line anyway we may still be able to

obtain the manual you need or direct you to other sources. If you have an existing manual you

would like scanned please write for details. This can often be done very reasonably in

consideration for adding your manual to our library.

Typically the scans in our manuals are done as follows;

1) Typed text pages are typically scanned in black and white at 300 dpi.

2) Photo pages are typically scanned in gray scale mode at 600 dpi

3) Schematic diagram pages are typically scanned in black and white at 600

dpi unless the original manual had colored high lighting (as is the case for

some 70’s vintage Tektronix manuals).

4) Most manuals are text searchable

5) All manuals are fully bookmarked

All data is guaranteed for life (yours or mine … whichever is shorter). If for ANY REASON your

file becomes corrupted, deleted or lost, ArtekMedia will replace the file for the price of shipping,

or free via FTP download.

Thanks

Dave & Lynn Henderson

ArtekMedia

WARRANTY

ARTEKMEDIA => 2012

...

Within one year

your instrument,

or

workmanship. All parts and labor charges will be paid by Dana

Laboratories. Just call Dana

in California, for assistance.

for your prepaid shipment. Your instrument will be returned

freight prepaid.

of

purchase, Dana Laboratories will repair

at

our option,

if

in any way

Product Service

We

will advise the proper shipping address

it

is

defective

at

(714)833·1234 collect

or

in

material

replace

to

you

OPRIETARY NOTICE

This document and the technical data herein disclosed, are proprietary

to

Dana Laboratories, Inc., and shall

of

permission

solicit quotations from a competitive source or used for manufacture

by anyone other than Dana Laboratories, Inc. The information herein

has been developed at private expense, and may only be used for

operation and maintenance reference purposes or for purposes

engineering evaluation and incorporation into technical specifications

and other documents which specify procurement

Dana Laboratories, Inc.

Dana Laboratories, Inc., be used,

not,

without express written

in

whole or in part to

of

products from

of

FOR

ARTEKMEDIA => 2012

Before undertaking any maintenance procedure, whether it

be

described herein or an exploratory procedure aimed at

determining whether there has been a malfunction, read the

applicable section

WARNING and

The equipment described in this manual contains voltages

hazardous

inflicting personal injury. The cautionary and warning

notes are included in this manual to alert operator and

maintenance personnel to the electrical hazards and thus

prevent personal injury and damage to equipment.

If this instrument

through

ensure that the instrument common connector

nected to the ground (earth) connection

mains.

YOUR

a specific troubleshooting or maintenance procedure

of

this manual and note carefully the

CAUTION notices contained therein.

to

human life a,.u safety and which

is

to be powered from the

an

autotransformer (such

as

a Variac

SAFETY

is

capable

AC

or

equivalent)

of

the power

Mains

is

of

con-

Before operating the unit ensure that the protective con-

is

ductor (green wire)

protective conductor

the protective feature

the power cord by using a two conductor extension cord

a three-prong/two-prong adapter.

Maintenance and calibration procedures contained in this

manual sometimes call for operation

applied and protective covers removed. Read the procedures

carefully and heed Warnings

to ensure your personal safety.

Before operating this instrument.

1.

Ensure that the instrument

operate on the voltage available

source.

2.

Ensure that the proper fuse

instrument for the power source

instrument

3. Ensure that

proximity to this instrument are properly grounded

or connected to the protective third-wire earth

ground.

See Installation section.

connected to the ground (earth)

of

the power outlet.

of

the third protective conductor in

of

to

avoid "live" circuit points

is

to be operated.

all

other devices connected to or in

Do

the unit with power

is

configured to

at

the power

is

in

place in the

on

not

defeat

or

which the

TABLE OF CONTENTS

ARTEKMEDIA => 2012

Section Title

1 GENERAL DESCRIPTION

1.1

1.2

1.3 Electrical Description

1.4 Specifications .

2 INSTALLATION & OPERATION

2.1

2.2 Unpacking and Inspection .

2.3 Bench Operation .

2.4

2.5 Power Requirements

2.6 Storage Requirements 2-2

2.7 Reshipment

2.8

2.9 Operation

2.9.2 Autorange . 2-4

2.9.3 Manual Range .

2.9.4 Overrange

2.9.5 Signal Input

2.9.6 Function Select

2.10 Hold/Read Probe (Option 81)

2.11

2.12

General.

Mechanical Description.

General .

Rack Mounting

Packaging Requirements

Input/Output/Controls .

BCD

Output

Battery

(Option 51)

Pack (Option 70)

Page

1-1

1-1

1-1

1-1

1-1

2-1

2-1

2-1

2-1

2-1

2-2

2-3

2-4

24

24

24

24

24

2-5

2-5

2-5

BCD

3

3.1

3.2 Mechanical Description .

3.3 Electrical Description

3.4 Operation

3.4.3 Function Codes

3.4.4 Range Codes

3.4.5 Serial

3.4.6 Parallel

3.4.7

4

4.1

4.3

4.13 Function Controls

OUTPUT

General.

Output

Output

Hold.

THEORY OF OPERATION

General.

Circuit Description

.

3-1

3-1

3-1

3-1

3-3

3-3

34

34

3-5

3-5

4-1

4-1

4-1

4-3

iii

TABLE

ARTEKMEDIA => 2012

OF

CONTENTS continued

l

1

"""

~ection

5

5.1

5.2 Calibration Checks

5.3

5.3.5 Calibration Procedure 5·6

5.4

5.4.7

5.4.10

6

7

MAINTENANCE.

Introduction

Calibration Adjustments 5·5

Troubleshooting Performance Tests

Unit Performance Tests

Subassembly Performance Tests . 5·20

DRAWINGS

PARTS

LIST

Title

Page

"'""I

5-1

5-1

5-1

5-9

5·9

6-1

7.1

iv

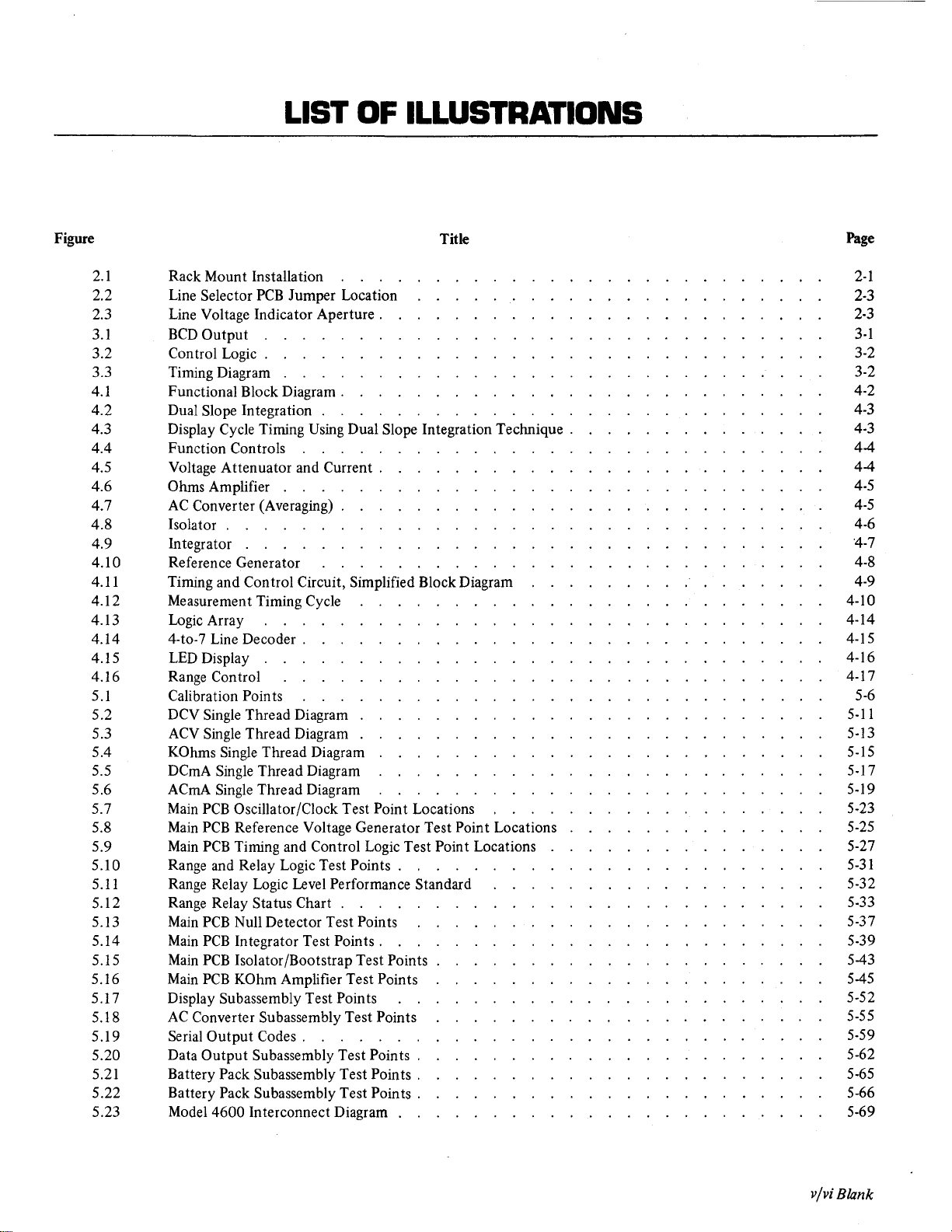

LIST OF ILLUSTRATIONS

ARTEKMEDIA => 2012

Figure

2.1

2.2

2.3

3.1

3.2

3.3

4.1

4.2

4.3

4.4

4.5

4.6

4.7

4.8

4.9

4.10

4.11

4.12

4.13

4.14

4.15

4.16

5.1

5.2

5.3

5.4

5.5

5.6

5.7

5.8

5.9

5.10

5.11

5.12

5.13

5.14

5.15

5.16

5.17

5.18

5.19

5.20

5.21

5.22

5.23

Title

Rack Mount Installation

Line Selector

Line Voltage Indicator

BCD

Output

Control

Timing Diagram . . . .

Functional Block Diagram.

Dual Slope

Display Cycle Timing Using Dual Slope Integration Technique .

Function

Voltage Attenuator and

Ohms Amplifier . . . .

AC

Converter (Averaging)

Isolator.

Integrator . . . . .

Reference Generator

Timing and

Measurement Timing

Logic Array

4-to-7 Line Decoder .

LED

Display . .

Range

Calibration

DCV Single Thread Diagram

ACV

Single Thread Diagram

KOhms Single Thread Diagram

DCmA Single Thread Diagram

ACmA Single Thread Diagram

Main

PCB

Main

PCB

Main

PCB

Range and Relay Logic Test

Range Relay Logic Level Performance Standard

Range Relay Status

Main

PCB

Main

PCB

Main

PCB

PCB

Main

Display Subassembly Test Points

AC

Converter Subassembly Test Points

Serial

Output

Data

Output

Battery Pack Subassembly Test

Battery Pack Subassembly Test

Model

PCB

Jumper Location

Aperture.

.

Logic.

Controls . . . . .

Control

Oscillator/Clock Test Point Locations

Reference Voltage Generator Test Point Locations

Timing and Control Logic Test Point Locations

Null Detector Test Points

Isolator/Bootstrap Test Points

KOhm Amplifier Test Points

4600

. . . .

Integration.

. . . .

Control Circuit, Simplified Block Diagram

Points

Integrator Test

Codes.

Subassembly Test

Interconnect Diagram . .

.

Current.

Cycle

Points.

Chart.

. . .

Points.

. . . . . .

. . . .

.

Points.

Points.

Points.

Page

2·1

2·3

2·3

3·1

3·2

3·2

4·2

4·3

4·3

44

44

4·5

4·5

4·6

4·7

4·8

4·9

4·10

4·14

4·15

4·16

4·17

5·6

5·11

5·13

5·15

5·17

5·19

5·23

5·25

5-27

5-31

5-32

5.33

5-37

5·39

543

5-45

5-52

5-55

5·59

5-62

5·65

5-66

5-69

v/vi Blank

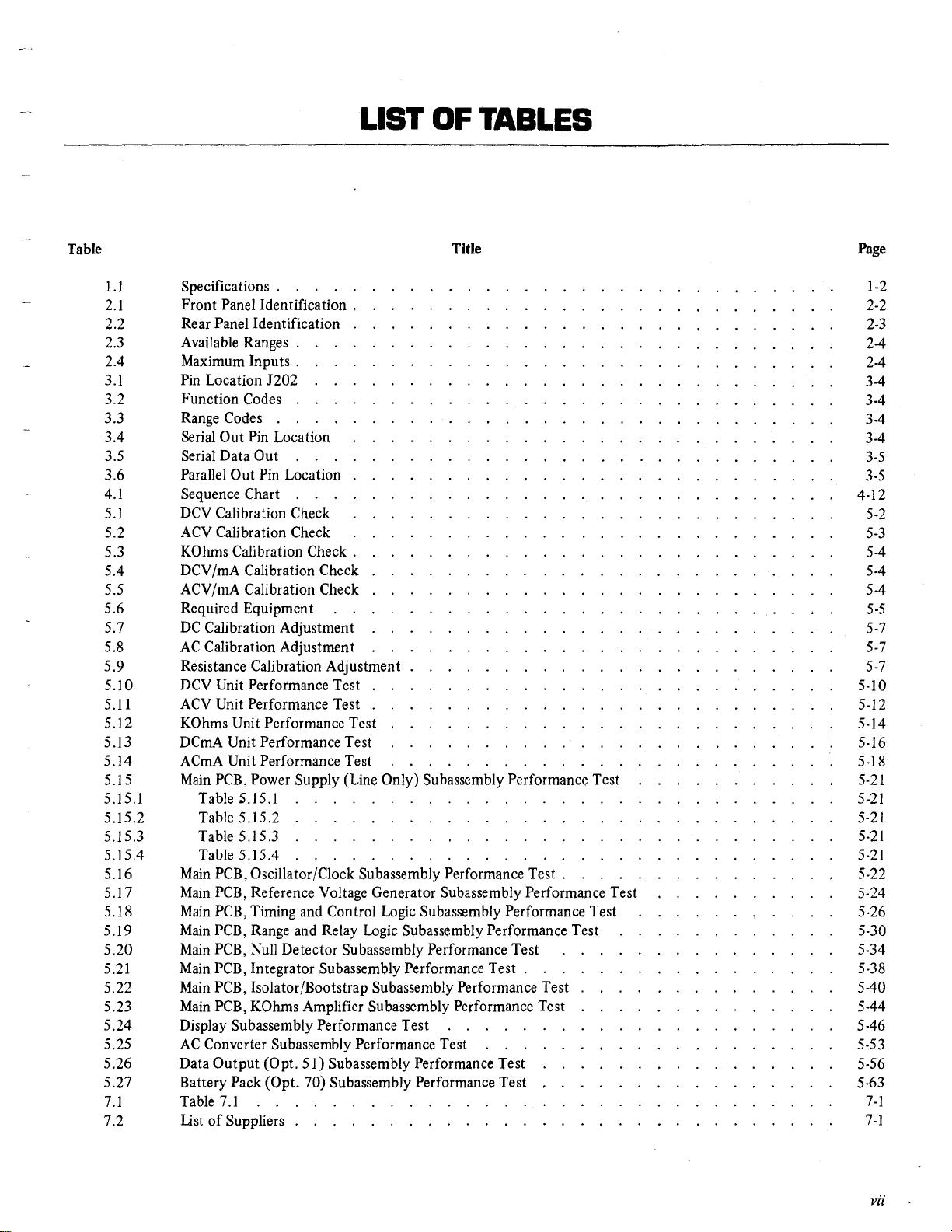

LIST

ARTEKMEDIA => 2012

OF

TABLES

Table

1.1

2.1

2.2

2.3

2.4

3.1

3.2

3.3

3.4

3.5

3.6

4.1

5.1 DCV Calibration Check

5.2 ACV Calibration Check

5.3

5.4 DCV /mA Calibration Check

5.5 ACV/mA Calibration Check

5.6 Required Equipment

5.7

5.8

5.9

5.10

5.11

5.12

5.13 DCmA

5.14

5.15 Main

5.15.1

5.15.2

5.15.3

5.15.4 Table 5.15.4

5.16 Main PCB, Oscillator/Clock Subassembly Performance

5.17

5.18 Main

5.19 Main

5.20

5.21 Main

5.22

5.23 Main PCB, KOhms Amplifier Subassembly Performance Test

5.24

5.25

5.26 Data

5.27

7.1

7.2

Specifications . 1-2

Front

Panel

Identification.

Rear

Panel Identification

Available

Maximum

Pin Location

Function

Range Codes

Serial

Serial

Parallel

Sequence Chart

KOhms Calibration

DC

AC

Resistance Calibration Adjustment

DCV Unit Performance

ACV

KOhms Unit Performance Test

ACmA Unit Performance Test

Main

Main PCB, Null Detector Subassembly Performance Test 5-34

Main

Display Subassembly Performance Test 5-46

AC

Battery Pack

Table 7.1

List

Ranges.

Inputs.

J202

Codes

Out

Pin Location

Data

Out

Out

Pin Location

Check.

Calibration Adjustment

Calibration

Unit Performance Test

Unit Performance Test 5-16

PCB, Power Supply (Line Only) Subassembly Performance Test 5-21

Table

Table 5.15.2 5-21

Table 5.15.3

PCB, Reference Voltage Generator Subassembly Performance Test 5-24

PCB, Timing and Control Logic Subassembly Performance Test

PCB, Range and Relay Logic Subassembly Performance Test 5-30

PCB, Integrator Subassembly Performance Test .

PCB, Isolator/Bootstrap Subassembly Performance Test 5-40

Converter Subassembly Performance Test 5-53

Output

of

Suppliers .

S.15.1

(Opt.

(Opt.

Adjustment

Test

51)

Subassembly Performance Test

70) Subassembly Performance Test

Title

Test.

Page

2-2

2-3

24

2-4

34

3-4

3-4

3-4

3-5

3-5

4-12

5-2

5-3

5-4

5-4

54

5-5

5-7

5-7

5-7

5-10

5-12

5-14

5-18

5-21

5-21

5-21

5-22

5-26

5-38

544

5-56

5-63

7-1

7-1

vii

SECTION 1

ARTEKMEDIA => 2012

GENERAL DESCRIPTION

1.1

GENERAL.

1.1.1 The Dana Model 4600

curate, four digit instrument featuring auto range, auto

polarity, 80

mon mode noise rejection, and 10,000 megohm input

resistance on the

Available options include Battery Pack, Data Output, and

Read, Hold Probe.

1.1.2 The basic instrument has full multimeter capability

measuring full scale inputs from 10

five

DC

voltage ranges, from 10 mOhms to 20 Megohms on

ohms ranges, 10 namps to 2 amps on

ranges, and 10 namps to 2 amps on

1.1.3 High reliability

and solid-state circuitry, including the display. Protection

from possible introduction

through both mechanical and electrical means. The use

separate input terminals, while routing inputs only when

the proper function

nals reaching the wrong circuitry. The current functions are

protected on

function

rms

AC

handle inputs

20 kHz, decreasing to 200 volts at 100 kHz

dB

normal mode noise rejection, 140

DC

functions .2 and 2 volt ranges.

voltage ranges, from 10

is

is

selected, reduces the chance

all

ranges by a 2.5 amp fuse; the

is

designed to handle inputs

on

all

ranges; the

of

1000 volts

AC

is

a compact, highly

IN

J.J,V

to 1000 volts on

five

insured by the

of

fault voltage

of

volts function

DC

or 1000 volts rms

dB

com-

to 1000 volts on

five

five

AC

current

DC

current ranges.

use

of

LSI

MaS

is

provided

of

DC

volts

1000 volts

is

on

DC

designed to

AC

all

ranges.

ac-

AC

six

of

sig-

or

to

Option 84 RF Probe, measures RF voltages to

200

MHz.

Option 88

Option 89

1.2 MECHANICAL DESCRIPTION.

1.2.1 The basic

ment and comes equipped with a bail handle to simplify

carrying. The bail handle rotates 3600 and may be used

a "kickstand" for easy measuring and control access.

1.2.2

the power supply are mounted on two printed circuit

boards and housed

the interior

nance

1.3 ELECTRICAL DESCRIPTION.

1.3.1 The model 4600 utilizes the dual-slope integration

method

minimizes the number

ability and lower cost while having

stability and noise rejection.

All

is

made by removing three screws on the back panel.

of

Deluxe test leads, include assorted tips.

Standard test leads, with replaceable tips.

DMM

is

designed

components

of

the instrument for calibration and mainte-

analog-to-digital conversion. This technique

of

the basic instrument including

in

a high-impact plastic case. Access to

of

components for increased reli-

as

a bench top instru-

inher~nt

advantages

as

of

1.1.4 Also available

(designated 4600-51). The option provides the function,

range, polarity, and numeric readout data in

both serially and in parallel.

1.1.5 Accessories available for 4600 include:

Option

Option 70

Option 80

Option

Option 82

Option

61

81

83

is

the Option

Carrying case.

Battery pack for operation - up to

four hours continuous

where no

Shielded input cable, for use in high

noise environments.

Hold Probe, provides pushbutton control

of

5

measurement to 5

50

measurements to 50

AC

power

Measure/Hold functions.

KV

HV

Probe, extends

KV

HV

Probe, extends

51

Isolated Output

use

is

available.

KV.

KV.

BCD

in areas

DC

voltage

DC

voltage

form

1.3.2 The circuitry consists

section, digital section, and an analog-to-digital converter.

1.3.3 The analog-to-digital (A/D) converter changes a dc

signal fed into it into a representative digital signal. The

method used to perform this task

integration.

1.3.4 The digital section measures the

converter to produce a numeric value on the instrument

display that represents the value

digital section also provides range control and decimal

placement.

1.3.5 The signal conditioning section scales, filters, and,

when required, converts the input signal to a full scale

volts for the A/D converter.

1.4 SPECIFICATIONS.

1.4.1 Specifications are provided in table 1.1.

of

a signal conditioning

is

called dual-slope

output

of

the input signal. The

of

the

AID

±2

1-1

980479

ARTEKMEDIA => 2012

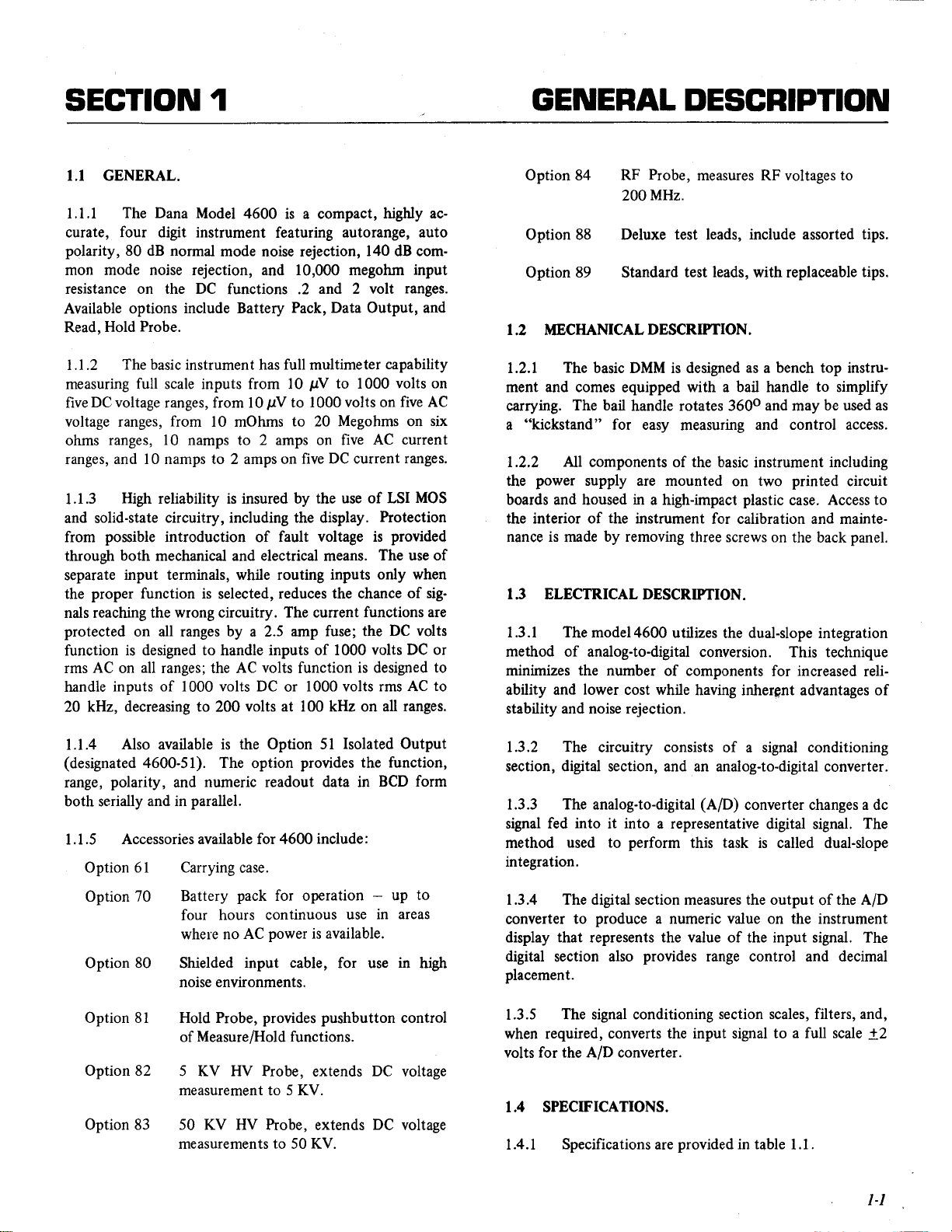

Table

1.1

- Specifications

..

DC

VOLTAGE

Full Range

Display:

Resolution: .005%

Accuracy:

Temperature

Coefficient:

Input

Resistance:

;\formal Mode

Noise Rejection:

I

!

I

Common

. Mode Noise

Rejection:

Settling Time to

0.01%

of

Full

Scale Step Input:

±.19999, ±1.9999, ±19.999,

+199.99,

volt range, .01%

10

6 Months, 230C ± 50C

(after zeroing)

.2V Range

2V,

1000V Range

+1000.0

of

range except 1000

of

J..LV

on .2 volt range

±(0.02%

+ 2 digits)

20V, 200V Ranges

HO.Ol %

+ 1 digit)

±(0.01 %

+ 1 digit)

of

reading

of

reading

of

reading

range

o to 50°C

2V, 20V, 200V, 1000V

Ranges

±(O.OO

1 %

of

reading

.1

digit)/oC

+

.2V Range

±(0.002%

+

.5

.2V Range

1010nminimum

2V

Range

101 On

20V, 200V, 1000V

10

Mn

80

dB

multiples

50

dB

increasing at 12 dB/octave

140

dB

120

dB

(With

10 Kohm Source)

700 milliseconds

2.5 seconds maximum on

1 KV range for 1 KV step

input

of

reading

digit)/oC

minimum

Ranges

± .25%

at 50 and

at 59 Hz, general slope

DC

at 50 and

of

10

60

Hz

±

60

Hz

Hz

and at

0.1

%.

OHMS

Full Range

Display:

Resolution:

Accuracy:

Temperature

Coefficient:

Settling Time

Rated Accuracy: on

Maximum

Input Voltage:

Current through

Unknown and

Voltage across

Unknown:

Open Circuit

Voltage: 7 volts maximum

to

.19999

19.999

1999.9

10

6 Months,

.2

2K,

2000

20,000

o to 50°C

.2

2

Ranges

2000

20,000

Less than 700 msec

2S0V

all

.2

2Kn

20Kn

200Kn

2000

20,000

Kn,

1.9999

Kn,

199.99

Kn,

19.999

milliohms on .2

230C ± 5°C

Kn

Range

±(O.OS%

+ 2 digits)

20K, 200

±(O.OS%

+ 1 digit)

±(

+ 1 digit)

±(0.2%

+ 1 digit)

Kn

±(O.OOS%

+ 1 digit)/oC

Kn,

±(0.002S%

.1

+

±(O.OOS%

.1

+

±(O.OOS%

+

.1

all

ranges

Range

Kn

Kn

Range

0.1 % of

Kn

of

Range

20

Kn,

digit)/oC

Kn

Range

digit)/oC

Kn

digit)/oC

ranges

DC

or peak

Kn

Kn

of

Kn

of

reading

Range

reading

of

of

Range

of

Current

1

1

100pA 2 volts

10

IpA

0.1

reading

reading

200

of

rnA

rnA

Kn,

Kn,

Mn

Kn

Range

reading

Kn

reading

reading

reading

AC

J..lA

pA

range

Voltage

0.2 volts

2 volts

2 volts

2 volts

2 volts

1-2

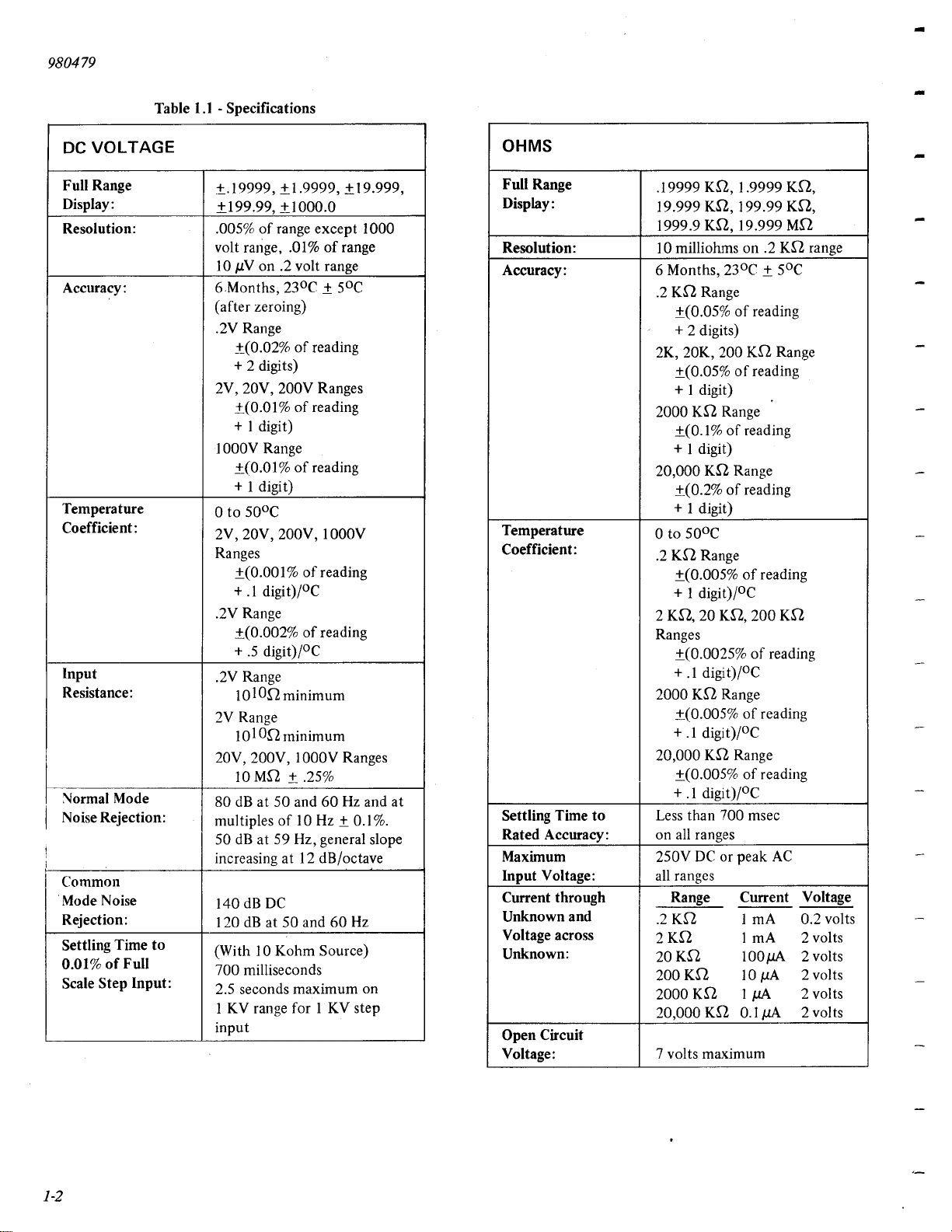

Table

ARTEKMEDIA => 2012

1.1

. Specifications continued

980479

ACVOLTS

Full Range

Display:

Resolution:

Accuracy:

(From

1%

to

range

of

range)

of

100%

.19999, 1.9999, 19.999,

199.99,

10 microvolts on the .2 volt

range

6 Months,

.2

30

2000.0V rms

230C ± 100C

Volt Range

Hz

to 50

±(0.1 %

of

Hz

reading

+ 70 digits)

Hz

to 500

50

±(0.1 %

Hz

of

reading

+ 30 digits)

500

Hz

to 50 kHz

±(0.08%

of

reading

+ 16 digits)

50 kHz to

±(.7%

+

2,200

30

Hz to 50

±(0.25%

100 kHz

of

reading

40

digits)

Volt Ranges

Hz

of

reading

+ 20 digits).

Hz

to 20 kHz

50

of

±(0.1 %

reading

+ 9 digits)

20 kHz to 50 kHz

of

±(0.1 %

reading

+ 10 digits)

50 kHz to

±(.7%

100 kHz

of

reading

+ 14 digits)

20

Volt Range

30

Hz to 50

±(.25%

+

50

Hz

±(.1 %

30

Hz

of

reading

digits)

to 20 kHz

of

reading

+ 12 digits)

20 kHz to 50 kHz

±(.I % of

+

16

50 kHz to 100 kHz

±(.7%

reading

digits)

of

reading

+ 16 digits)

2000 Volt Range

(10V to 500V)

30

Hz

to 50

Hz

±(0.45%

of

reading

+ 10 digits)

50 Hz to 20 kHz

±(0.15%

of

reading

+ 5 digits)

AC VOLTS continued

Accuracy: (con't)

2000 Volt Range

(500V to 1000V)

30

Hz

to 50

±(0.5%

of

+ 10 digits)

50 Hz to 20 kHz

±(0.2%

of

+ 5 digits)

Temperature

Coefficient:

30

Hz

to

±CO.Ol

10

%

of

+ .4 digits)/oC

10 kHz to 100 kHz

±(0.05% or reading

+.1

digit)/oC

Common

Mode Noise

Rejection: in either lead

Input

Impedance:

Zero Offset:

Settling Time

(To 100%

of

range):

Less than 80

60 Hz with I Kohm imbalance

1 Megohm with 100 pF

shunt capacitance with

.221J.F

in series on aRranges

Range

.2V

2V 5 digits max

20V

200V

2000V 5 digits max

of

range to F

1 %

of

to 1 %

Step settles to 0.1 %

value within 1.5 seconds

range

CURRENT AC

Full Range

Display:

Shunt Values: .2

Input Protection:

Accuracy:

(From

1%

of

range

to

100%

of

range)

.19999 rnA, 1.9999 rnA,

19.999 rnA, 199.99 rnA,

1999.9

2mA

20mA

200

2000

2.5 Amp Fast Blow Fuse

6 Months,

50

.2,2,

rnA

rnA

rnA

rnA

Hz

- 10 kHz

20, 200

±(0.2%

23

of

+ 20 digits)

2000

rnA

Range

±(0.3%

of

+ 20 digits)

Temperature

Coefficient: + .6 digits)/oC

±(0.015%

of

Hz

reading

reading

kHz

reading

dB

at

50

40

digits max

30

digits max

5 digits max

.S.

or F

of

IKn

loon

Ion

In

O.ln

0

('

±

SoC

rnA

Range

reading

reading

reading

Hz

.S.

final

and

1-3

980479

ARTEKMEDIA => 2012

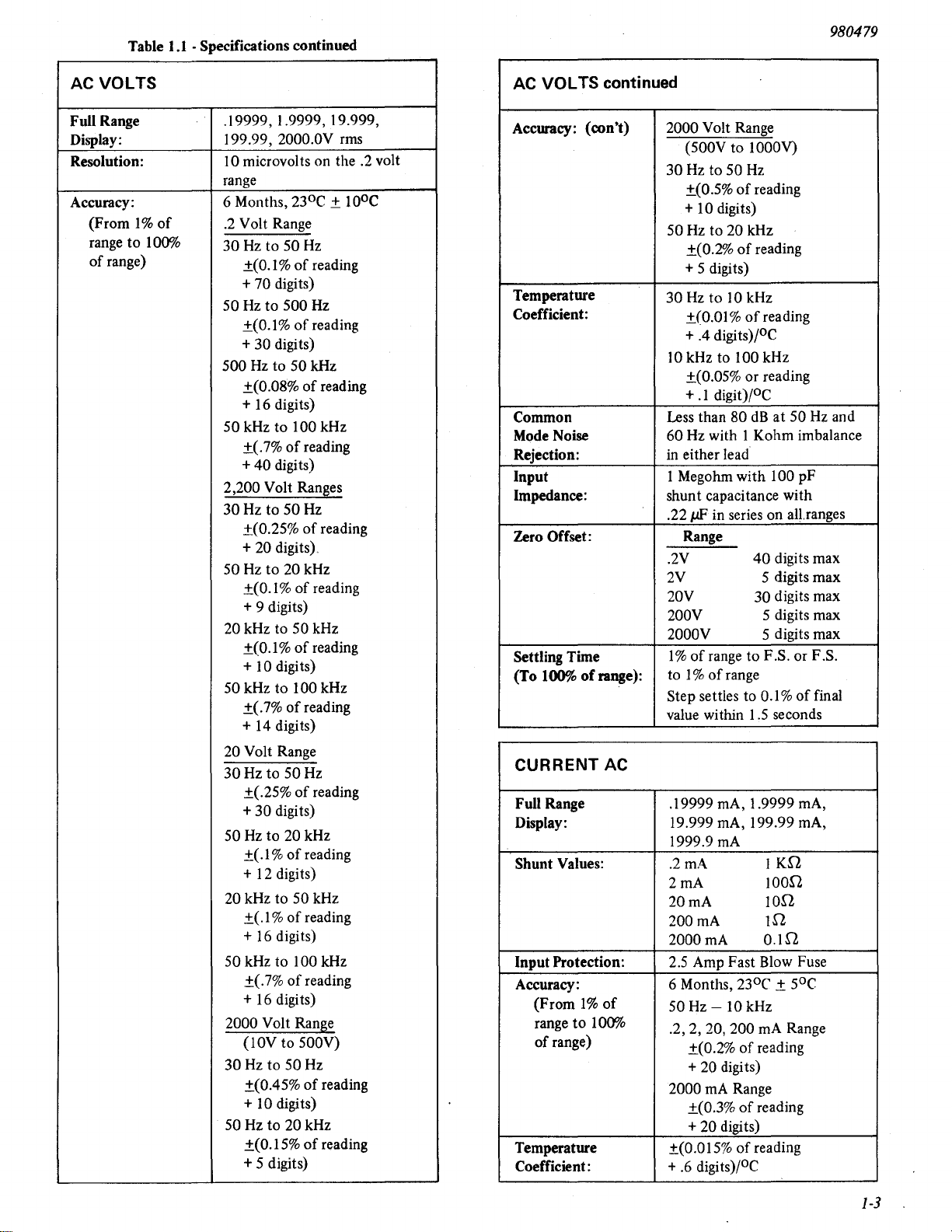

Table

1.1

- Specifications continued

•

-

CURRENT

Full Range

Display:

Shunt

Values: .2

Protection:

Input

Accuracy:

Temperature

Coefficient:

DC

GENERAL

±.19999 rnA, ±1.9999 rnA, Ranging:

±19.999

+1999.9

2mA

20

200 rnA

2000 rnA

2.5 Amp Fast Blow Fuse

6 Months,

.2, 2,

2000

o to

±(0.01 %

+ .2 digits)/oC

rnA, ±199.99 rnA,

rnA

rnA

rnA

230C ±

20, 200

±(0.12%

+ 4 digits)

±(0.3%

+

20 digits)

500C

rnA

of

Range

of

of

reading

IKn

lOOn

IOn

In

o.ln

SoC

rnA

Ranges

reading

reading

Digitizing

Technique: Dual Slope

Signal Integration Time:

Read Rate:

Maximum

Common

Mode Voltage:

Power

Requirements:

Storage

Temperature:

Operating

Temperature:

Warmup: 30 minutes

Weight

(Approx.):

Dimensions:

Automatic or Manual

100 msec ± .25%

400 msec per reading

2-1

/2 reading per second

+.25%

KV

DC

1

to Earth Ground

100, 120, 220, 240

±IO% from nominal.

50 to 400 Hz,

maximum

-200 C to

-200 C to 650 C w/battery opt.

0-

to 6 month accuracy

Std:

With Battery Option:

73mm x

(2.87 x 7.87 x 9.84 inches)

or peak

50°C

Kg

2.3

3.2

(Sibs.)

Kg

(7Ibs.)

200mm x 250mm

10

750 C

AC

volts

watts

input

1-4

SECTION 2

ARTEKMEDIA => 2012

INSTALLATION & OPERATION.

2.1

GENERAL.

2.1.1 This section covers the incoming inspection, instal·

lation, storage and operation

of

the Model 4600

DMM.

2.2 UNPACKING & INSPECTION.

2.2.1 The Model 4600

is

enclosed between two molded,

plastic·foam forms and packaged in a double·walled card·

board carton for shipment. The plastic forms hold the

instrument securely in the carton and absorb any reason·

able external shock normally encountered in transit.

2.2.2 Prior to unpacking, examine the exterior

shipping carton for any

the

DMM

from the carton and inspect the exterior

instrument for any

signs

signs

of

of

damage. Carefully remove

damage.

If

damage

of

is

found,

of

the

the

notify the carrier immediately.

2.3

BENCH

OPERATION.

2.3.1 The instrument comes equipped with a bail handle"

that doubles

elevating the front

as

a carrying handle and

of

the instrument.

as

a "kickstand" for

2.4 RACK MOUNTING.

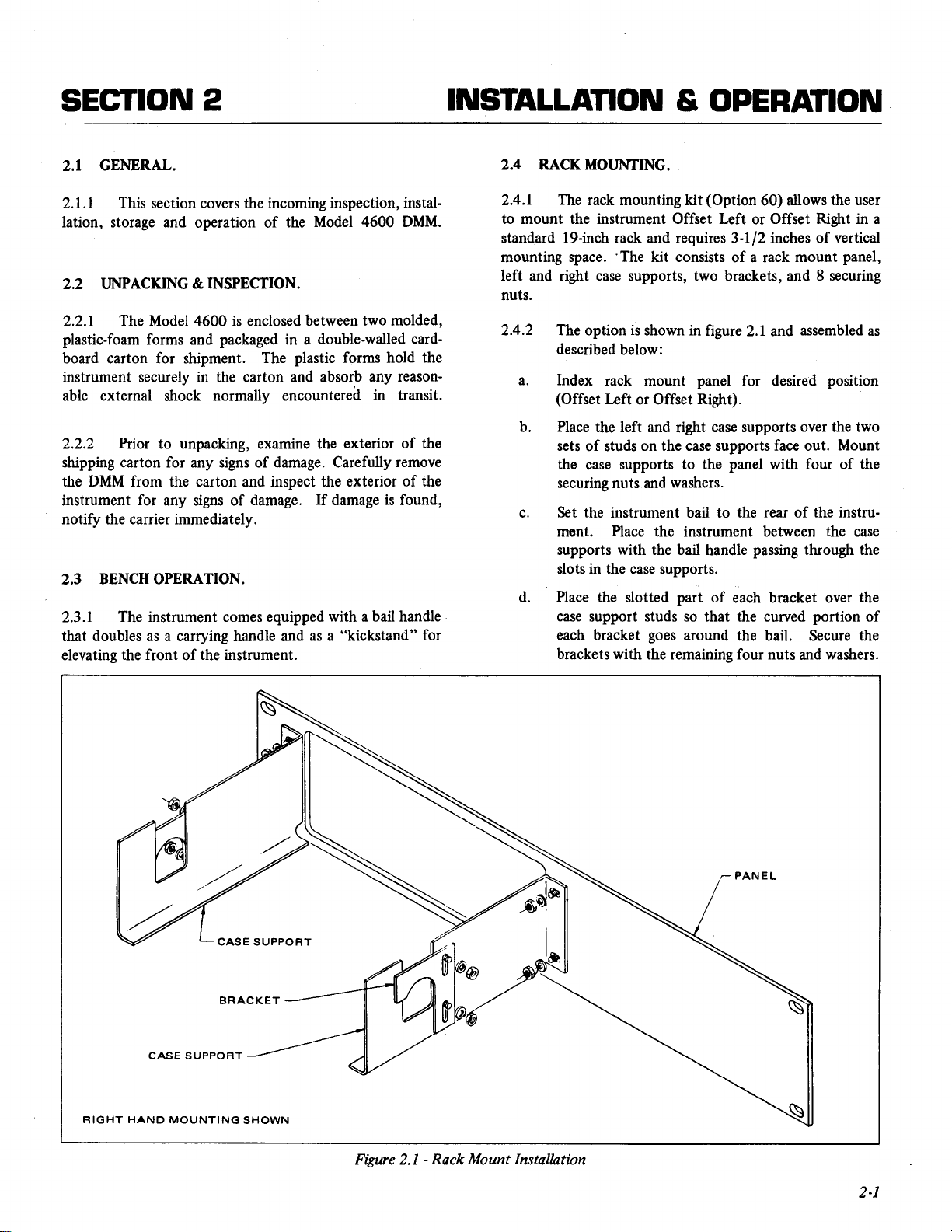

2.4.1 The rack mounting kit (Option 60) allows the user

to mount the instrument Offset Left or Offset Right in a

standard 19-inch rack and requires 3-1/2 inches

mounting space.

left and right

"The

kit consists

case

supports, two brackets, and 8 securing

of

a rack mount panel,

of

vertical

nuts.

2.4.2 The option

is

shown in figure

2.1

and assembled

as

described below:

a.

Index rack mount panel for desired position

(Offset Left or Offset Right).

b. Place the left and right case supports over the two

sets

of

studs on the case supports face out. Mount

the

case

supports to the panel with four

of

the

securing nuts. and washers.

c.

Set the instrument bail to the rear

ment. Place the instrument between the

of

the instru·

case

supports with the bail handle passing through the

slots in the

d.

Place the slotted part

case

case

supports.

support studs

of

each bracket over the

so

that the curved portion

of

each bracket goes around the bail. Secure the

brackets with the remaining four nuts and washers.

RIGHT

CASE

HAND

CASE

SUPPORT

MOUNTING

SUPPORT

BRACKET

SHOWN

Figure 2.1 .

Rack

Mount

Installation

r-

PANEL

2-1

980479

ARTEKMEDIA => 2012

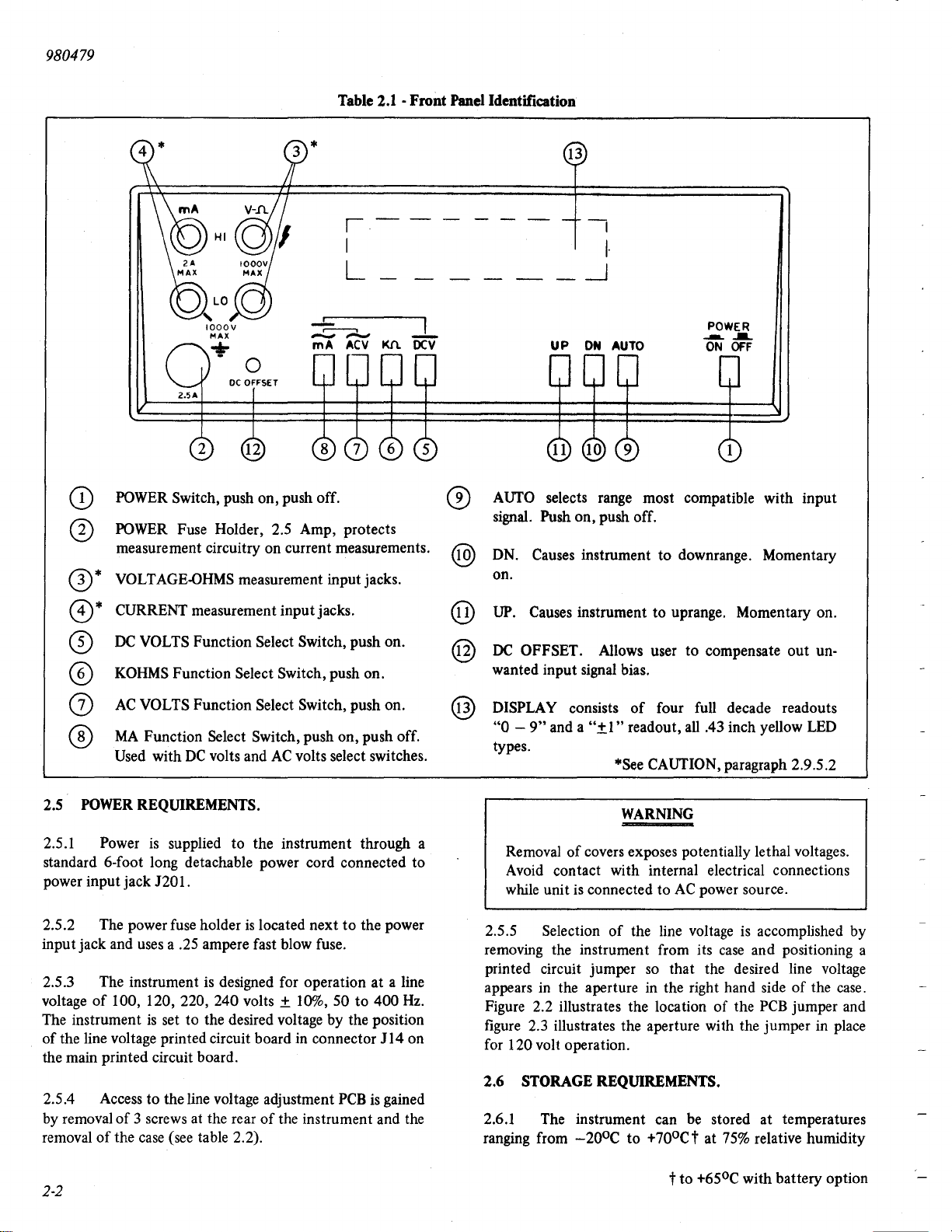

Table

2.1

-Front

Panel

Identification

13

CD

CD

0*

8)*

CD

(0

1-

- - -

I

L

POWER Switch, push on, push off.

POWER Fuse Holder, 2.5 Amp, protects

measurement circuitry on current measurements.

VOLTAGE-OHMS measurement input jacks.

CURRENT measurement

DC

VOLTS Function Select Switch, push on.

KOHMS Function Select Switch, push on.

input

jacks.

--

-I

I·

.-J

UP

ON

AUTO

AUTO selects range most compatible with

®

signal. Push on, push off.

DN.

Causes instrument

on.

UP.

@

@

Causes instrument

DC

OFFSET. Allows user

wanted input signal bias.

to

downrange. Momentary

to

uprange. Momentary on.

to

POWER

--.

......

ON

OFF

compensate

out

input

un-

AC

(j)

®

2.5

POWER REQUIREMENTS.

2.5.1

standard 6-foot long detachable power cord connected

power input

2.5.2 The power fuse holder

input jack and uses a .25 ampere fast blow fuse.

2.5.3 The instrument is designed for operation

voltage

The instrument

of

the main printed circuit board.

2.5.4 Access

by removal

removal

of

the line voltage printed circuit board in connector 114 on

VOLTS Function Select Switch, push on.

MA

Function Select Switch, push on, push off.

Used with

Power

jack

100, 120, 220, 240 volts ± 10%, 50

of

3 screws at the rear

of

the case (see table 2.2).

DC

volts and

is

supplied

1201.

is

set

to

the desired voltage by the position

to

the line voltage adjustment

AC

to

the instrument through a

is

located

of

the instrument and the

volts select switches.

next

to

the power

to

PCB

is

at

a line

400

gained

to

Hz.

DISPLA Y consists

@

"0 -9"

types.

2.5.5

removing the instrument from its case and positioning a

printed circuit jumper

appears in the aperture in the right hand side

Figure 2.2 illustrates the location

figure 2.3 illustrates the aperture with the jumper in place

for

2.6

2.6.1 The instrument can be stored

ranging from

and a

Removal

Avoid contact with internal electrical connections

while unit

120 volt operation.

STORAGE REQUIREMENTS.

of

is

Selection

-200C

of

four full decade readouts

"±1"

readout, all .43 inch yellow LED

*See CAUTION, paragraph 2.9.5.2

WARNING

covers exposes potentially lethal voltages.

connected

of

to

AC

power source.

the line voltage is accomplished by

so

that

the desired line voltage

of

the

PCB

at

temperatures

to

+700Ct

at

75%

relative humidity

of

the case.

jumper and

2-2

t

to

+650C with battery option

CD

ARTEKMEDIA => 2012

POWER

power cable.

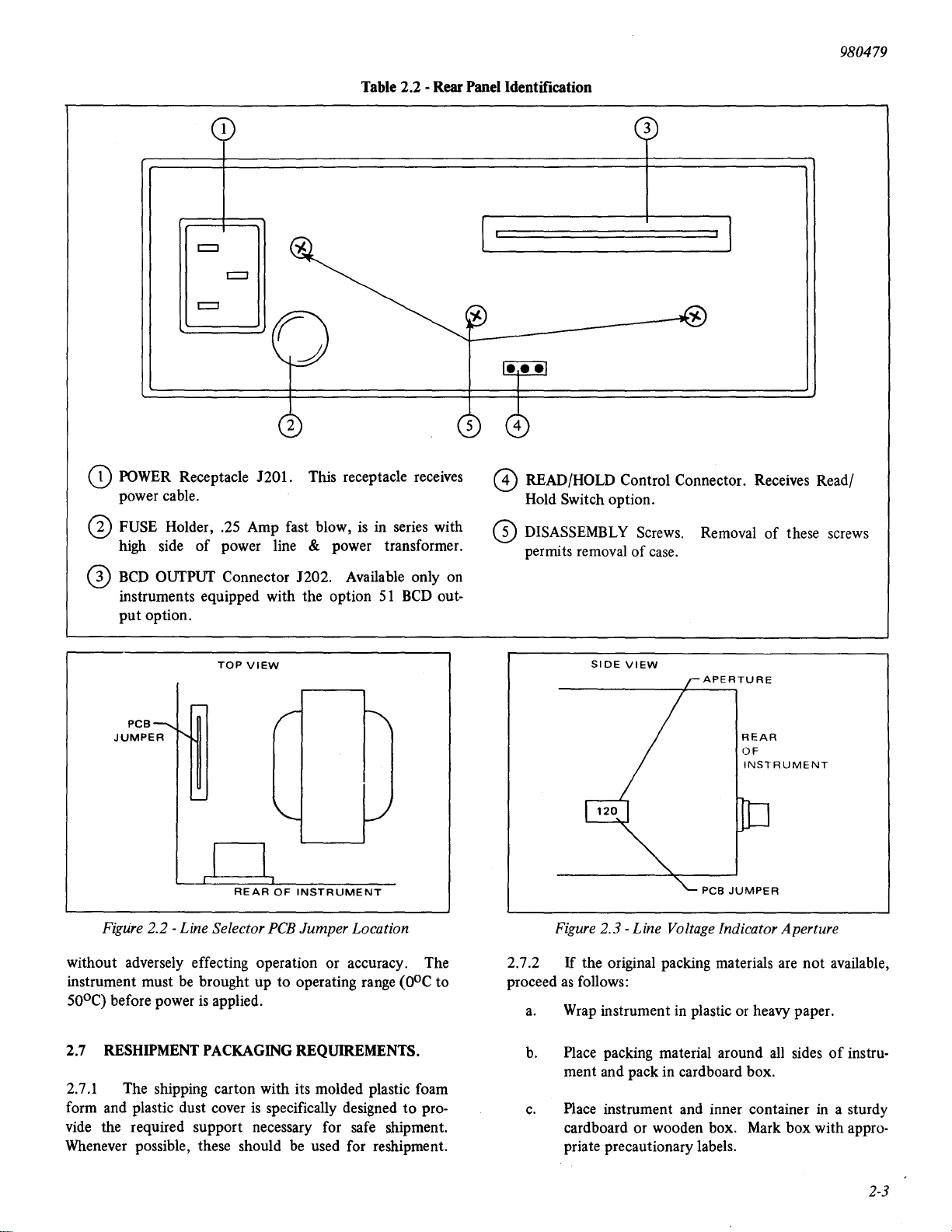

Table

2.2 -

Rear

c::::J

Receptacle 1201. This receptacle receives

Panel

Identification

8)

980479

3

READ/HOLD Control Connector. Receives Read/

Hold

Switch option.

CD

FUSE Holder, .25 Amp fast blow, is in series with

of

high side

CD

BCD

OUTPUT Connector 1202. Available only on

instruments equipped with the option

put

option.

Figure 2.2 - Line Selector PCB Jumper Location

without adversely effecting operation or accuracy. The

instrument must be brought

50°C) before power is applied.

power line & power transformer.

51

BCD

out-

TOP

VIEW

REAR

OF

INSTRUMENT

up

to

operating range

(OOC

to

eD

DISASSEMBLY Screws. Removal

permits removal

Figure 2.3 - Line Voltage Indicator Aperture

If

2.7.2

proceed

a. Wrap instrument in plastic or heavy paper.

the original packing materials are

as

follows:

SIDE

of

VIEW

case.

APERTURE

REAR

OF

INSTRUMENT

PCB

JUMPER

of

these screws

not

available,

2.7

RESHIPMENT

2.7.1 The shipping carton with its molded plastic foam

form and plastic dust cover

vide the required support necessary for safe shipment.

Whenever possible, these should be used for reshipment.

PACKAGING

is

specifically designed

REQUIREMENTS.

to

pro-

b.

Place packing material around all sides

ment

and pack in cardboard box.

c.

Place instrument and inner container in a sturdy

cardboard or wooden box. Mark

priate precautionary labels.

box

of

instru-

with appro-

2-3

980479

ARTEKMEDIA => 2012

INPUT jOUTPUT jCONTROLS.

2.8

2.8.1 In tables

controls and their function. Also described are input and

output connectors.

2.9

OPERA

2.9.1 Operation consists

tion, selecting autorange or manually selecting the desired

range, applying the input signal and reading the results on

the instrument readout.

2.9.2 Autorange.

nON.

2.1

and 2.2 are described the operating

of

selecting the desired func-

2.9.4.2 Overrange

the read rate.

2.9.5 Signal Input.

2.9.5.1 Signal input

front panel. These jacks accept standard probe banana

plugs and are spaced to accept dual banana plugs. Several

probe sets for the

Section 1).

2.9.5.2 The left hand pair

DC

and

AC

current measurements; the jacks on the right are

for voltage and resistance measurements.

is

indicated by the display flashing at

is

through four banana jacks on the

4600 are available from the factory (see

of

input jacks are reserved for

2.9.2.1 In autorange the instrument automatically selects

the range most appropriate for the signal being measured.

2.9.2.2

ranges

downranging occurs at

2.9.3 Manual Range.

2.9.3.1 When autorange

in manual range. Higher or lower ranges are selected by

pressing the

selected at the read rate within the range limits

selected function

pressed.

2.9.3.2 The available ranges for each function are given in

table 2.3.

As

the input signal changes, the instrument changes

as

required. Upranging occurs at 100%

5%

of

range.

is

not selected, the instrument

UP

or

DN

range buttons. A new range

as

long

as

the

UP

or

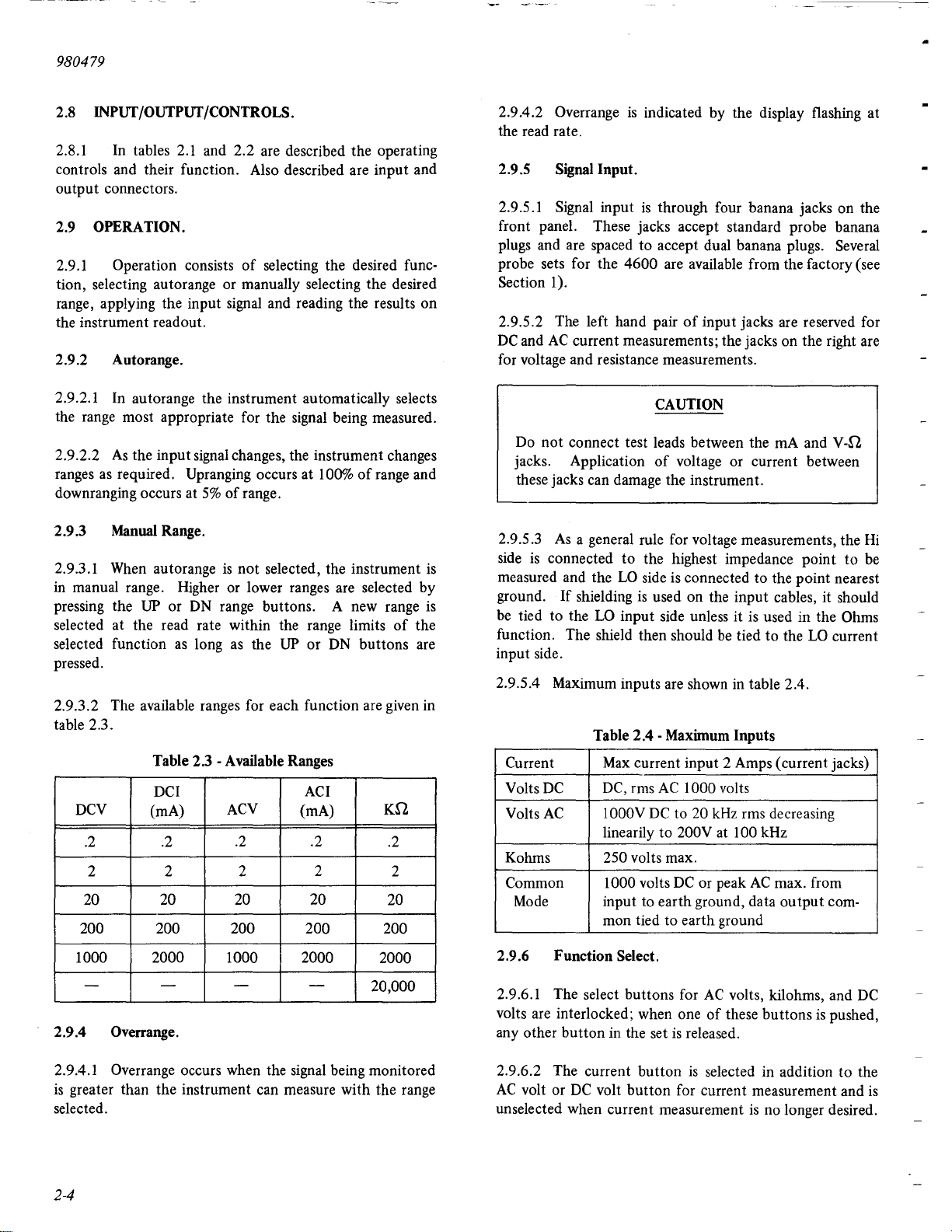

Table 2.3 - Available Ranges

DCI

DCV

.2

2 2 2

20

200 200 200 200

(rnA)

.2

20 20 20

ACV

.2

ACI

(rnA)

.2

DN

2

of

range and

of

the

buttons are

Kn

.2

2

20

200

is

is

CAUTION

Do not connect test leads between the

jacks. Application

these jacks can damage the instrument.

As

2.9.5.3

side

measured and the

ground.

be

tied

function. The shield then should be tied to the

input side.

2.9.5.4 Maximum inputs are shown in table 2.4.

Current

Volts

Volts

Kohms

Common

Mode

a general rule for voltage measurements, the

is

connected

If

shielding

to

the

LO

Table 2.4 -Maximum Inputs

Max

DC

AC

DC,

1000V

linearily to

250 volts max.

1000 volts

input to earth ground, data

mon tied to earth ground

of

voltage or current between

to

the highest impedance point

LO

side

is

connected to the point nearest

is

used on the input cables, it should

input side unless it

current input 2 Amps (current jacks)

rms

AC

1000 volts

DC

to 20

kHz

200V at 100 kHz

DC

or peak

rnA

is

used in the Ohms

rms decreasing

AC

max. from

output

and

LO

Von

to

current

com-

Hi

be

1000 2000 1000 2000

-

2.9.4 Overrange.

2.9.4.1 Overrange occurs when the signal being monitored

is

greater than the instrument can measure with the range

selected.

2-4

- -

2000

- 20,000

2.9.6 Function Select.

2.9.6.1 The select buttons for

volts are interlocked; when one

any other button in the set

2.9.6.2 The current button

AC

volt or

unselected when current measurement

DC

volt button for current measurement and

AC

volts, kilohms, and

of

these buttons

is

released.

is

selected in addition to the

is

pushed,

is

no longer desired.

DC

is

2.10

ARTEKMEDIA => 2012

HOLD/READ PROBE

2.1

0.1

This option consists

switch that connects to

2.10.2

With

the option plug inserted in 1203

position, the instrument takes readings only

switch

is

held down.

2.10.3. With the option plug inserted in

position, the instrument

switch

is

pressed.

2.11 BCD OUTPUT

(Option

(Option

n03

on the rear panel.

81).

of

a probe with a built-in

n03

goes

into the hold mode when the

51).

as

in

the read

long

in

the hold

as

the

2.11.1 This option provides function, range, polarity, and

value

in

BCD

the display

operated device.

quiring serial or parallel output. The option

detail

in

Section 3.

form for printer or other digitally

It

is

designed to interface with units

is

covered

re-

in

980479

to four hours

the instrument

power switch

2.12.2

level, the condition

of

continuous

is

connected to the power

is

set to the OFF position.

When

the battery charge drops below operating

is

use.

indicated

Recharging occurs when

by

a LED lamp on the

line

and the

instrument front panel. To fully recharge the batteries

quires about

Option 70

Option

16

hours.

NOTE

is

not available for units equipped with the

51

BCD Output.

re-

NOTE

Option

51

is

not available for units equipped with the

Option 70 battery pack.

2.12

BATIERVPACK(Option70).

2.1.2.1 With the battery pack option the instrument

becomes completely portable, taking measurements for up

CAUTION

On

units equipped for battery pack operation (Option

70)

the batteries

connected to the

ment

is

turned off. The batteries charge

mately

16

are

hours; it

charging when the instrument

AC

power source and the instru·

in

approxi·

is

recommended that the unit

is

be

unplugged during extended periods of non-use to

avoid

pOSSible

damage to the batteries.

2-5

THIS

ARTEKMEDIA => 2012

PAGE

LEFT

BLANK

SCANS

By

ArtekMedia

SECTION 3

ARTEKMEDIA => 2012

3.1

GENERAL.

Model

3.1.1 The

vides

the function, range, polarity, and numeric readout

data in

single

data

of

characteristics

3.2

3.2.1

printed circuit board that

BCD

connector on the instrument rear panel. The output

is

completely isolated from the measurement portion

the 4600, thereby preserving the common mode noise

MECHANICAL

All

components for the option

4600 Option

form, both serially and in parallel, from a

of

the instrument.

DESCRIPTION.

is

51

Isolated Output pro·

are

on a

mounted above the instrument

single

BCD OUTPUT

main

PC

board by four spacers;

located between the boards, prevents any digital

generated on the option board from affecting the measure·

ment circuitry on the

3.2.2

nector that extends out the back

a slot provided for this purpose. This connector

option output connector and

3.3

3.3.1 The option, shown in simplified block diagram

form in figure 3.1, consists

section, and six optical couplers.

One end

ELECTRICAL DESCRIPTION.

Main

board.

of

the option board forms an edge con·

is

of

a floating section, a grounded

an

aluminum shield,

of

the instrument through

designated J202.

J202

noise

is

the

Kn

RANGE

,

NUMERIC

DATA

TRANSFER

00

CLOCK

-100

AC

T

I

I

P7

I

:

I

I

1

I

I

I

I

I

I

:

1

FUNCTION

ENCODE

CONTROL

LOGIC

h>

:>

:>

MUX

f

r--

.-.-

......-

~

I

I

I

I

'-

OCll

I

I

OCI

I

I

I

OCI

I

I

I

OCI

I

I

I

I

10CIs

SERIAL

SERIAL

SERIAL

SERIALS

1 I

2 I

4 I

"-

I

SERIES

DATA

,

1

I

I

I

SHIFT

REGISTER

2

I

I

I

PARALLEL

OUTPUT

I

3

4

i

TIO

GEN

I

I

I

I

I

PARALLEL

1

OUTPUT

I

INHIBIT

I

SERIAL

STROBE

_I

HOLD~(~I----------------------------------~

FLOATING

SECTION

Figure

3.1·BCD

:

oc,.I"'~------------------------«

Hc5"i:D

I

I

Output

GROUNDED

SECTION

3-]

980479

ARTEKMEDIA => 2012

TRANSFER

00

"

L

COUNTER

U1

i

F/F

U5,U3

DATA

TRANS

DECODE

U5

GATE

U2,

U3

f--

~

PART

MUX

U6,U7

...

-

OF

MUX

SERIAL

DATA

CLOCK

DATA

CLOCK

(1

kHz)

TRANSFER

TRANSFER

(1

STROBE

Figure

~END

OF

.-J

00

_________

kHz)

I I

1

MS

I I

r

3.2 - Control Logic

DIGITIZING

t+--5

=il

--'I

.....

If-----

II

I I I I I I I I

MSEC--+j

n

8

MS

..

______

-----

_

...

~oIL

20

IlS

3-2

PARALLEL

DATA

VALID

Figure

3.3-

UNITS

TENS

HUNDREDS

Timing

THOUSANDS

TEN

THOUSANDS

FUNCTION-----..J

RANGE-------..J

Diagram

980479

ARTEKMEDIA => 2012

3.3.2 The floating section encodes and multiplexes the

binary data from the measurement portion

and transmits the data through optical couplers 1 through

5.

The sixth coupler

The floating section consists of: Function Encode, the

Multiplexer (MUX), and the

3.3.2.1 The multiplexer consists

line data selector/multiplexers,

receives inputs from the function encode circuitry and

trol signals from the control logic, both located on the option

board, and range and numeric data from the display board.

The

multiplexer has a 4-bit byte output which drives the

four optical data couplers; the output byte corresponds to

of

one

control logic.

3.3.2.2 The

consists

counter

generates the operational logic for the multiplexer and the

strobe

provides timing information for the grounded side. The

circuitry operates by following a predetermined series

steps shown in figure 3.3. The operation starts when the

TRANSFER line

as

OD,

Display board,

signal

data transfer signal enables the gate, allowing the 1 kHz

clock

board) to advance counter

is

3.3.2.3 The clock advances the counter through seven

steps. At the

The

strobing action

ment circuitry

UI,

and the readout value being strobed to the display

routed through the multiplexer and optical couplers. The

sixth step the multiplexer selects the encoded Function

byte. The seventh step the multiplexer selects the Range

byte.

is

the generation

reset when TRANSFER

the three possible input bytes, selected by the

Control Logic, shown simplified in figure 3.2,

of

an R/S flip-flop (US, U3), gate circuit (U2, U3),

(UI),

signal

which drives the

soon

as

pulses

a strobe

sets the flip-flop output true (Data Transfer). The

signal

(also from the counter/multiplexer on Display

decoded by

operation

the

five

readout data bytes to the

On

the eighth step, the flip-flop

inhibited, preventing the advancement

is

used for

and decode logic (US). The control logic

goes

true, permitting counter Ul to count

are

received from the gate circuit.

signal

from the counter/multiplexer on the

is

received the negative going

US.

same

time seven strobe pulses are generated.

of

the control logic

of

the counter/multiplexer

so

that during the first

of

additional strobe signals. The counter

HOLD

Control Logic.

U6

five

Ul.

The output

goes

false.

of

and

data optical couplers and

is

of

the instrument

(see paragraph 3.4.7).

two dual 4-line to

U7.

The multiplexer

edge

of

the counter

synchronized with the

of

the measure-

five

steps

of

MUX

are selected

is

reset and the gate

of

the counter

1-

con-

of

When

of

the

counter

is

being

or

is

3.3.3 The grounded portion

data from the optical isolators to provide the output data

in

series and parallel form for a recorder or other digitally

operated device at connector

of

consists

hold circuitry.

3.3.3.1 The shift register consists

serial shift registers, each

four data optical couplers (OCI 1 through 4). The outputs

of

the optical couplers are also used

being binarily weighted (1-24-8). The strobe pulse

received through optical coupler (OCI 5) and applied to the

command inputs

3.3.3.2 One output pair

generate

VALID

the other output pair

microsecond pulse (SERIAL DATA STROBE and its

reciprocal

inverted and used to strobe the shift register.

3.3.3.3 The hold circuit permits the user to electrically

stop the instrument from taking new readings through the

BCD

transistors (one on the grounded portion and the other on

the floating portion) and an optically coupled isolator

(OCI6).

3.4 OPERATION.

3.4.1 Provided with the Option

nectOr

preventing misalignment

and 44 connector pins (Dana PIN 600809). Pin identification

pend on the type

3.4.2

referenced to pin

at pin 1 for printer reference.

put

are defined

Logic

Logic

a shift register, a dual timeout generator and

of

the dual one-shot.

an

eight millisecond pulse (PARALLEL

and its reciprocal, INHIBIT PARALLEL DATA);

is

SERIAL DATA STROBE). Serial Data Strobe

output connector. The circuit consists

(Dana

PIN

600810), a key (Dana PIN 600811) for

of

is

provided in table 3.1. The pins used, however,

of

operation used (serial or parallel).

All

output lines are from TTL logic and are

2.

A reference

as:

Hi:

+2.4 volts minimum

Lo: +0.8 volts maximum (8

of

the option converts the

110. The grounded portion

of

four 8-bit parallel out

of

which

is

driven by one

as

the serial outputs,

of

the one-shot

programmed to generate a 20

the connector, mounting screws,

+5

Output

is

programmed to

51

is

the mating con-

volt output

levels

of

rna

current sink)

of

DATA

of

the 2

is

provided

the data out-

the

de-

is

is

3.3.2.4 The function encoding circuitry converts the

polarity,

use

AC,

T,

and

Kn

by the multiplexer.

inputs into a

BCD

coded output for

+"

3.4.3

3.4.3.1 The function codes are shown

Function Codes.

in

table 3.2.

3-3

980479

ARTEKMEDIA => 2012

Table 3.1 - Pin Location

1202

+5V

Ref

Earth Ground

Output

Serial

Thousands (4)

Function

Range (4)

Hundreds (4)

Tens (4)

Units (4) 14 R

Serial

Output

Thousands (1)

10 Thousands

Function (1) 18 V Function

Range (1) 19 W Range

Tens (1)

Hundreds (1)

Units (1)

I

Function

-DC

+DC

ACV 1 1 0 0 3

-DCI

+DCI

ACI

Kn

3.4.4 Range Codes.

3.4.4.1 The range codes are shown in table

(4)

(4)

(2)

(1)

Table 3.2 -

Fl

0

1

0 0

1

1 1 1 0

1

A

1

B

2

3

C

D

4

E Serial Data Strobe

5

F

6

7 H Hold

J Serial

8

K

9

10 L

11

M

12 N

P Tens (8)

13

15

S

16

T

17

U

20 X

Y Tens (2)

21

22 Z

Function

F2

0

0

0

0

J202

Serial Data Strobe

Parallel

Inhibit

Thousands (8)

+ Polarity

Hundreds (8)

Units

Serial

. Thousands

10 Thousands

Hundreds

Units (2)

Data

Parallel

Output

(8)

Output

(2)

(2)

(2)

(2)

Codes

F4

0 0 0

0 0 1

1

1 0 5

0 1

F8

0

3.3.

Valid

Data

(8)

(2)

(2)

(OL)

Dec

4

7

9

Table

3.3

Range

20,000 1

2,000 0 0

200 1

20

2

.2

3.4.5 Serial

3.4.5.1 The data

lines; strobe data

form.

vided in table 3.4.

Pin identification for lines used in serial

+5V

Ref

Earth Ground 2

Output

Serial

Output

Serial

Rl

0

1

0 0

Output.

output

is

available in logic true and inverted true

Table

3.4

- Serial

(4

lines) 8

(2

lines)

-Range Codes

R2

0

1 0 3

1

0 0

is

available in serial form

Out

1202

1 A

R4 Dec

1 5

1 4

0 2

0 0

Pin Location

B

3 C

4 D

5

6

7

9

10

11

12

13

14

15

16

17

18 V

19

20

21

22

Serial Data Strobe

E

Serial Data Strobe

F

H Hold

Serial

J

Output

K

L

M

N

P

R

Serial

S

T

U

W

X

Output

Y

Z

out

(8

(2

1

on

four

is

pro-

lines)

lines)

3-4

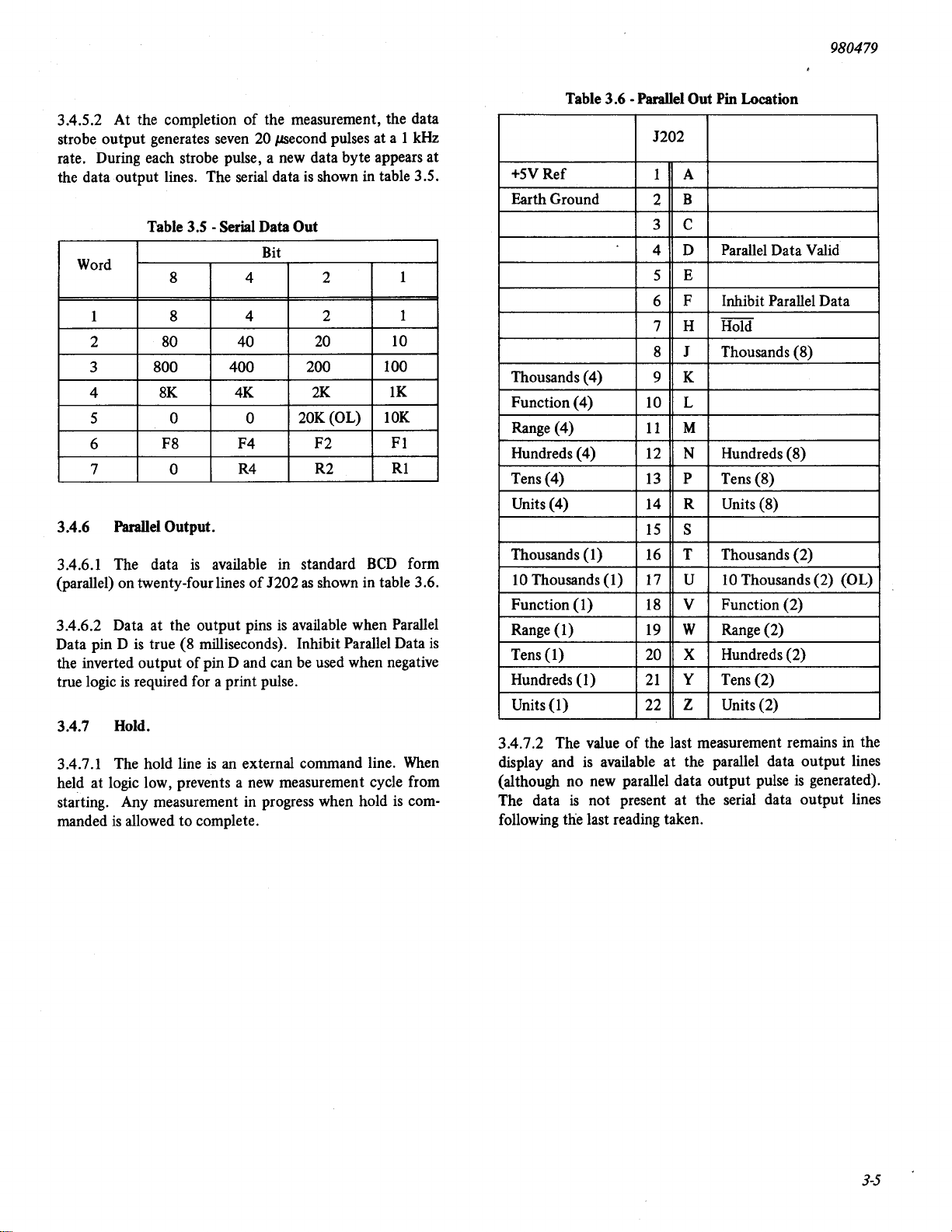

3.4.5.2 At the completion

ARTEKMEDIA => 2012

strobe

output

rate. During each strobe pulse, a new data byte appears

the data

Word

1 8 4 2

2

3

4

5 0 0

6

7 0

3.4.6 Parallel Output.

3.4.6.1 The data

(parallel) on twenty-four lines

3.4.6.2 Data

Data pin D is true

the inverted

true logic

3.4.7 Hold.

3.4.7.1 The hold line

held at logic low, prevents a new measurement cycle from

starting. Any measurement in progress when hold

manded

generates seven 20

output

is

lines. The serial data is shown in table 3.5.

Table 3.5 - Serial Data

8 4 2

80

800

8K 4K 2K

F8

is

at

the

output

(8

output

is

required for a print pulse.

allowed

of

to

complete.

of

the measurement, the data

J1Second

Bit

40

400

F4 F2

R4

available in standard

of

1202

pins is available when Parallel

milliseconds). Inhibit Parallel Data is

pin D and can be used when negative

is

an external command line. When

pulses at a 1 kHz

Out

20

200

20K(OL)

R2

BCD

as

shown in table 3.6.

1

1

10

100

lK

10K

Fl

Rl

is

at

form

com-

Table 3.6 -Parallel Out Pin Location

1202

+5VRef

Earth Ground

Thousands (4)

Function (4)

Range (4)

Hundreds (4)

Tens (4)

Units (4)

Thousands (1)

10 Thousands (1) 17 U

Function (1)

Range

(1)

Tens (1)

Hundreds (1)

Units (1)

3.4.7.2 The value

display and is available

(although no new parallel data

The data

following the last reading taken.

is

not present at the serial data

1 A

B

2

3

C

4 D Parallel Data Valid

E

5

F Inhibit Parallel Data

6

7 H Hold

J Thousands (8)

8

9 K

L

10

M

11

12

N Hundreds (8)

13

P Tens (8)

14 R

15

S

T Thousands (2)

16

18

V

19

W Range (2)

X Hundreds

20

Y Tens (2)

21

Z Units (2)

22

of

the last measurement remains in the

at

the parallel data

Units (8)

10

Thousands (2) (OL)

Function (2)

(2)

output

pulse

is

980479

output

output

lines

generated).

lines

3-5

THIS

ARTEKMEDIA => 2012

PAGE

LEFT

BLANK

SCANS

By

ArtekMedia

SECTION 4

ARTEKMEDIA => 2012

THEORY

OF

OPERATION

4.1 GENERAL.

of

output

the Model

as

well

as

is

pre-

level pro-

ac

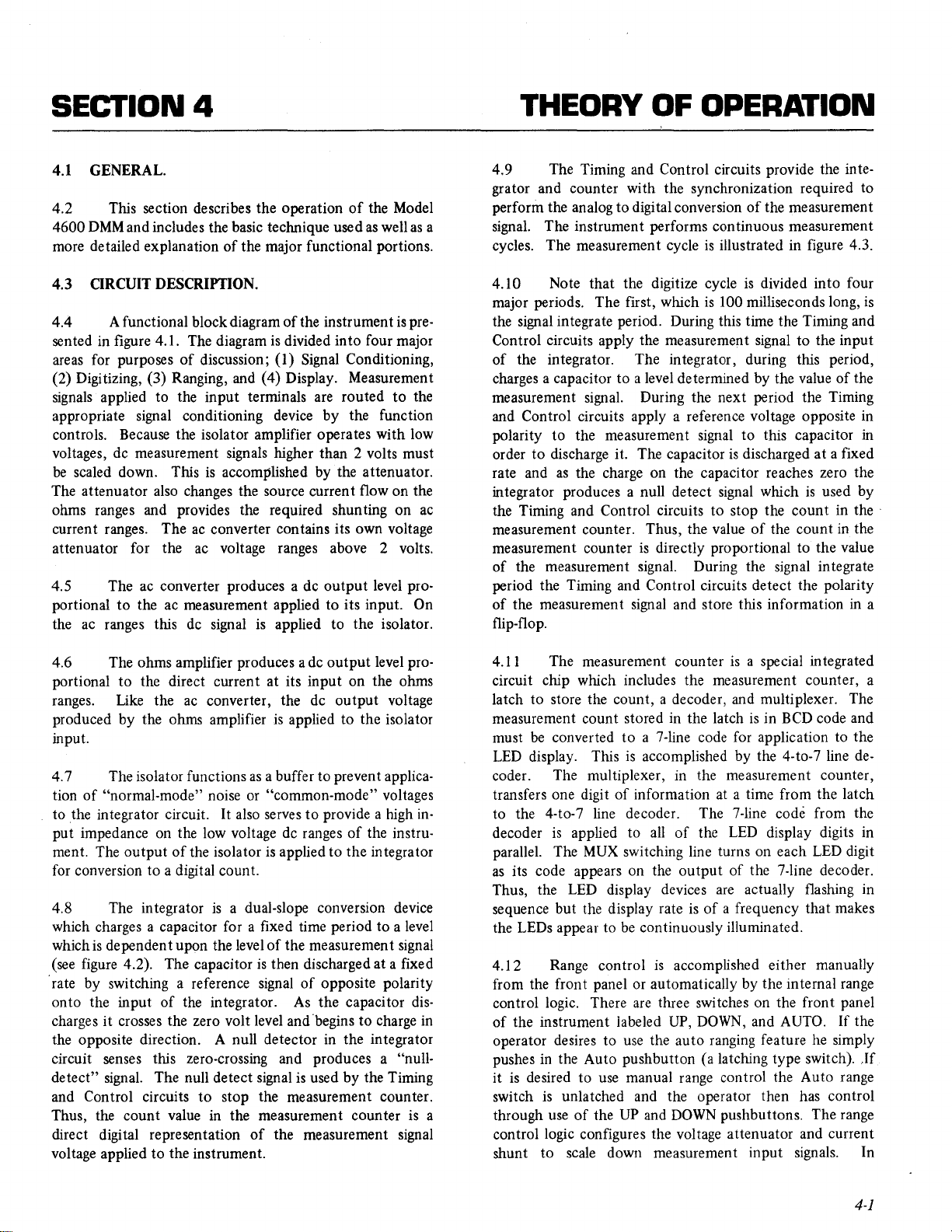

4.2 This section describes the operation

4600

DMM

and includes the basic teclmique used

of

more detailed explanation

CIRCUIT DESCRIPTION.

4.3

4.4 A functional block diagram

sented in figure 4.1. The diagram

areas for purposes

(2) Digitizing, (3) Ranging, and (4) Display. Measurement

signals applied to the input terminals are routed to the

appropriate signal conditioning device by the function

controls. Because the isolator amplifier operates with low

voltages, dc measurement signals higher than 2 volts must

be

scaled down. This

The attenuator also changes the source current flow on the

ohms ranges and provides the required shunting on

current ranges. The

attenuator for the

4.5 The ac converter produces a dc

portional

the ac ranges this

to

of

ac

the ac measurement applied to its input. On

dc

the major functional portions.

of

the instrument

is

divided into four major

discussion;

is

accomplished by the attenuator.

converter contains its own voltage

ac

voltage ranges above 2 volts.

signal

(I)

Signal Conditioning,

is

applied to the isolator.

4.9 The Timing and Control circuits provide the integrator and counter with the synchronization required to

of

perform the analog to digital conversion

a

signal. The instrument performs continuous measurement

cycles. The measurement cycle

4.10 Note that the digitize cycle

major periods. The first, which

the signal integrate period. During this time the Timing and

Control circuits apply the measurement signal to the input

of

the integrator. The integrator, during this period,

charges a capacitor to a level determined by the value

measurement signal. During the next period the Timing

Control circuits apply a reference voltage opposite in

and

polarity to the measurement signal to this capacitor

order

to

discharge it. The capacitor

as

rate and

integrator produces a null detect signal which

the Timing and

measurement counter. Thus, the value

measurement counter

of

the measurement signal. During the signal integrate

period the Timing and

of

the measurement signal and store this information

flip-flop.

the charge on the capacitor reaches zero the

Control circuits to stop the count in

is

directly proportional to the value

Control circuits detect the polarity

is

is

the measurement

illustrated in figure 4.3.

is

divided

100 milliseconds long,

is

discharged at a fixed

of

in

is

used by

the count

to four

of

the

in

the'

in

the

in

is

a

4.6 The ohms amplifier produces a dc

portional

ranges. Like the

produced by the ohms amplifier

input.

4.7 The isolator functions

tion

to

the

put impedance on the low voltage dc ranges

ment. The

for conversion to a digital count.

4.8 The integrator

which charges a capacitor for a fixed time period to a level

which

(see figure 4.2). The capacitor

'rate by switching a reference signal

onto the input

charges it crosses the zero volt level and 'begins to charge

the opposite direction. A null detector in the integrator

circuit senses this zero-crossing and produces a

detect"

and

Thus, the count value in the measurement counter is a

direct digital representation

voltage applied to the instrument.

to

the direct current at its input on the ohms

ac

converter, the dc output voltage

is

as

a buffer to prevent applica-

of

"normal-mode" noise or "common-mode" voltages

integrator circuit.

output

is

dependent upon the level

signal. The null detect signal

Control circuits

of

of

It

also serves

the isolator

is

the integrator.

to

is

applied to the integrator

a dual-slope conversion device

of

is

then discharged at a fixed

stop the measurement counter.

of

the measurement signal

output

applied to the isolator

to

provide a high

the measuremen t signal

of

opposite polarity

As

the capacitor

is

used by the Timing

level pro-

of

the instru-

in-

dis-

"null-

in

4.11 The measurement counter

circuit chip which includes the measurement counter, a

latch to store the count, a decoder, and multiplexer. The

measurement count stored in the latch

be

must

LED

coder. The multiplexer,

transfers one digit

to the 4-to-7 line decoder. The 7-line

decoder

parallel. The

as

Thus, the

sequence but the display rate

the LEDs appear to

4.12 Range control

from the front panel or automatically by the internal range

control logic. There

of

operator desires to

pushes

it

switch

through

control logic configures the voltage attenuator and current

shunt to scale down measurement input signals. In

converted

display. This

is

applied to

its code appears on the

LED

the instrument labeled

in

the Auto pushbutton (a latching type switch) . .If

is

desired to use manual range control the Auto range

is

unlatched and the operator then has control

use

of

to

a 7-line code for application to the

is

accomplished by the 4-to-7 line

in

of

information at a time from the latch

all

of

MUX

switching line turns on each LED digit

output

display devices

be

continuously illuminated.

is

accomplished either manually

are

three switches on the front panel

UP,

use

the auto ranging feature he simply

the

UP

and

DOWN

is

a special integrated

is

in

BCD

code and

the measurement counter,

code from the

the

LED

display digits in

of

the 7-line decoder.

are

actually flashing in

is

of

a frequency that makes

DOWN,

and AUTO. If the

pushbuttons. The range

de-

4-1

SIGNAL CONDITIONING

ARTEKMEDIA => 2012

AC

CONVERTER

~".-t

t

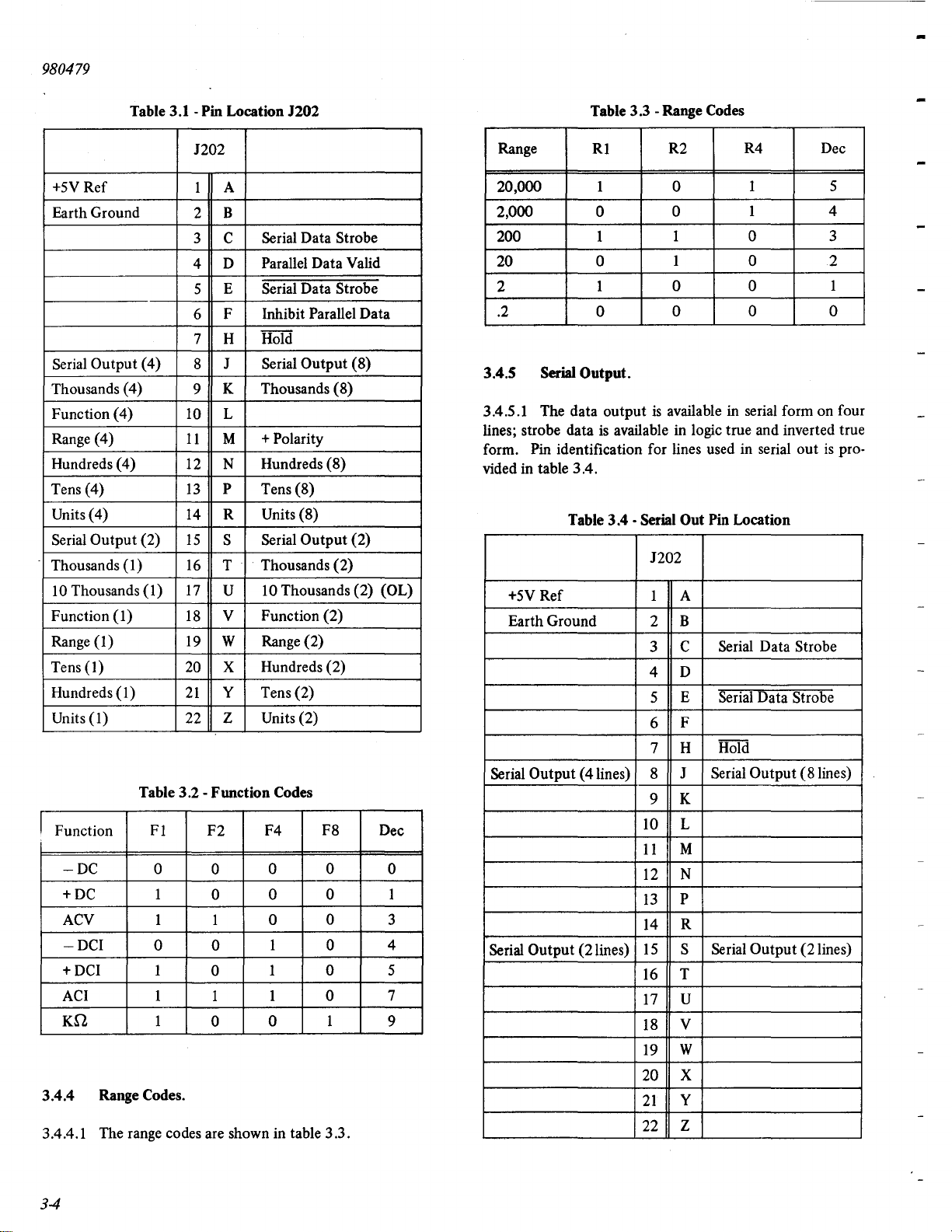

•

MEASUREMENT

INPUT

TERMINALS

~

~

~

RANGE

REFERENCE

r------.,

INTEGRATOR

REFERENCE

GENERATOR

FUNCTION

CONTROLS

CONTROL

NULL

DETECT

....

VOLTAGE

\

--......

\

CONTROL

SIGNALS

~VOLTAGE~

ATTEN

l......a...

r-"""""

~

AND

CURRENT

SHUNT

1=======I=======lISOLATOR

~

f t

LATCH

4-LlNE

AND

MULTI

OHMS

AMP

LI

FIE

I

~

BCD

~

I

________________

I

I

I

R

r.o-

DECODER

~

1.",0..

MEASUREMENT

_---

TIMING

AND

CONTROL

START/

..

STOP

..--~

TIMING

SIGNALS

COUNTER,

DECODER

PLEXER

~----~--

L-~P~O~L=A~R~IT~Y~

MUX

4-TO-7

LINE

__

I--

SWITCHING

~-r~r-~---+---+---r/

~

~

LED

DISPLAY

I'

~

7·LlNE

I I

::ODE

4-2

____

I

RANGE RANGE RANGE

CONTROLS

L.........

,---.-

CO

NT

RO

LOGIC

L

Figure

DIC:T~IN~

:

~ISPLAY

__

_

RANGING

CODE

4.1 -Functiona I Block

DECIMAL

DECODER

CIRCUIT

AC~

OHMS~

DC

DECIMAL

1-

_______________

PATH

LEGEND

Diagram

POINT

...tL._...,.L-_...,.L-

__

-----L.

__

---'

ISOLATOR

ARTEKMEDIA => 2012

REFERENCE

GENERATOR

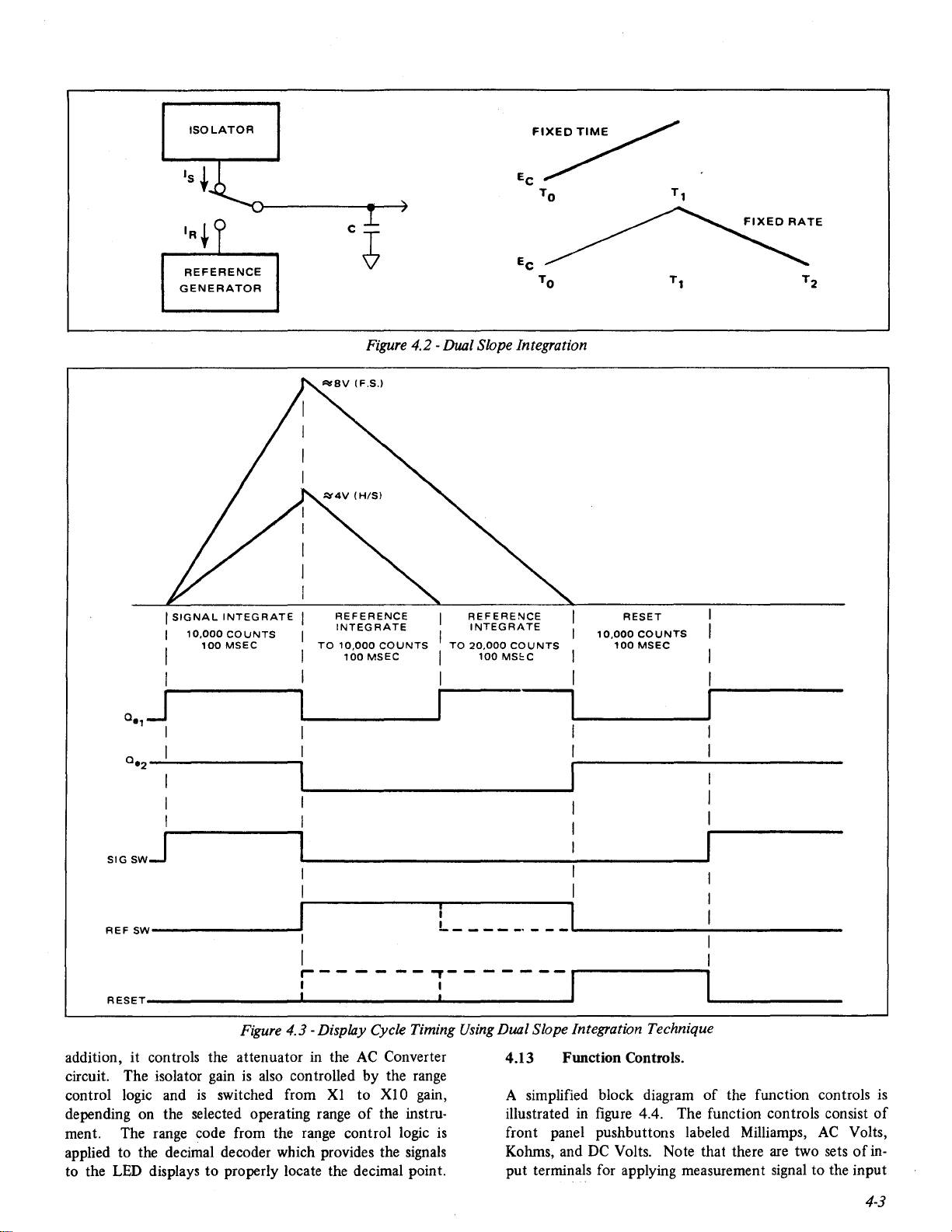

Figure 4.2 -Dual Slope Integration

I

SIGNAL

I

I

10,000

100

INTEGRATE

COUNTS

MSEC

REFERENCE

INTEGRATE

TO

10,000

100

COUNTS

MSEC

I

a.

J

1

I

I

a·2~--------------~

I

REFSW--

RESET

addition, it controls the attenuator in the

circuit, The isolator gain

control logic and

depending on the selected operating range

ment,

The range code from the range control logic

applied to the decimal decoder which provides the signals

to the

LED

______________

__________________

Figure 4.3 -Display Cycle Timing Using Dual Slope Integration Technique

is

is

switched from

displays

to

properly locate the decimal point,

~--------------~L--------------.-----~-I~------------------

r-

- - - - - - "'T - - - - - - -

:~

______________

AC

Converter

also controlled by the range

Xl

to

XIO gain,

of

the instru-

REFERENCE

INTEGRATE

TO

20,000

100

:~

____________

is

RESET

10,000

COUNTS

MS~C

100

COUNTS

MSEC

I

I

..

---------------i

__________

__

~I

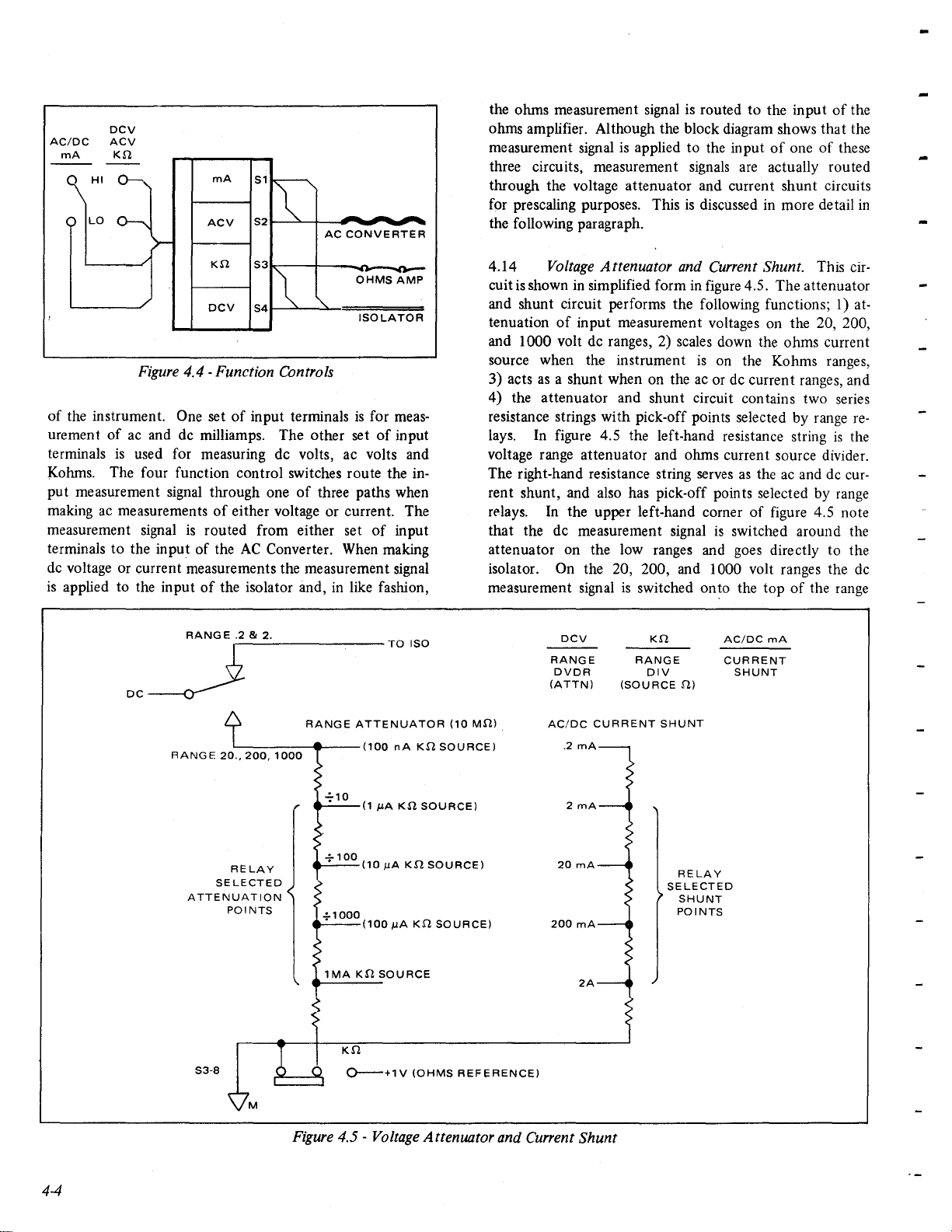

4.13 Function Controls.

A simplified block diagram

illustrated

in

figure 4.4. The function controls consist

front panel pushbuttons labeled Milliamps,

Kohms, and

DC

Volts. Note that there are two sets

put terminals for applying measurement signal to the input

of

the function controls

AC

Volts,

of

in-

is

of

4-3

q

ARTEKMEDIA => 2012

HI

LO

DCV

ACV

Kn

--

0----,

~

rnA

ACV

S1

~

S2

---

-

AC

CONVERTER

--

AC/DC

rnA

>-

Kn

S3

1\

S4

of

input terminals

Figure

of

the instrument. One set

urement

terminals

of

ac and dc milliamps. The other set

is

used for measuring dc volts, ac volts and

DCV

4.4

-Function Controls

Kohms. The four function control switches route the

put measurement signal through one

ac

making

measurements

measurement signal

to

terminals

the input

of

either voltage or current. The

is

routed from either set

of

the

AC

of

Converter. When making

dc voltage or current measurements the measurement signal

is

applied to the input

of

the isolator and,

OHMSAMP

""-

ISOLATOR

is

for meas-

of

input

in-

three paths when

of

input

in

like fashion,

the ohms measurement signal

is

routed to the input

of

the

ohms amplifier. Although the block diagram shows that the

is

measurement signal

applied to the input

three circuits, measuremen t signals

of

one

are

actually routed

of

these

through the voltage attenuator and current shunt circuits

for pre scaling purposes. This

discussed in more detail

in

is

the following paragraph.

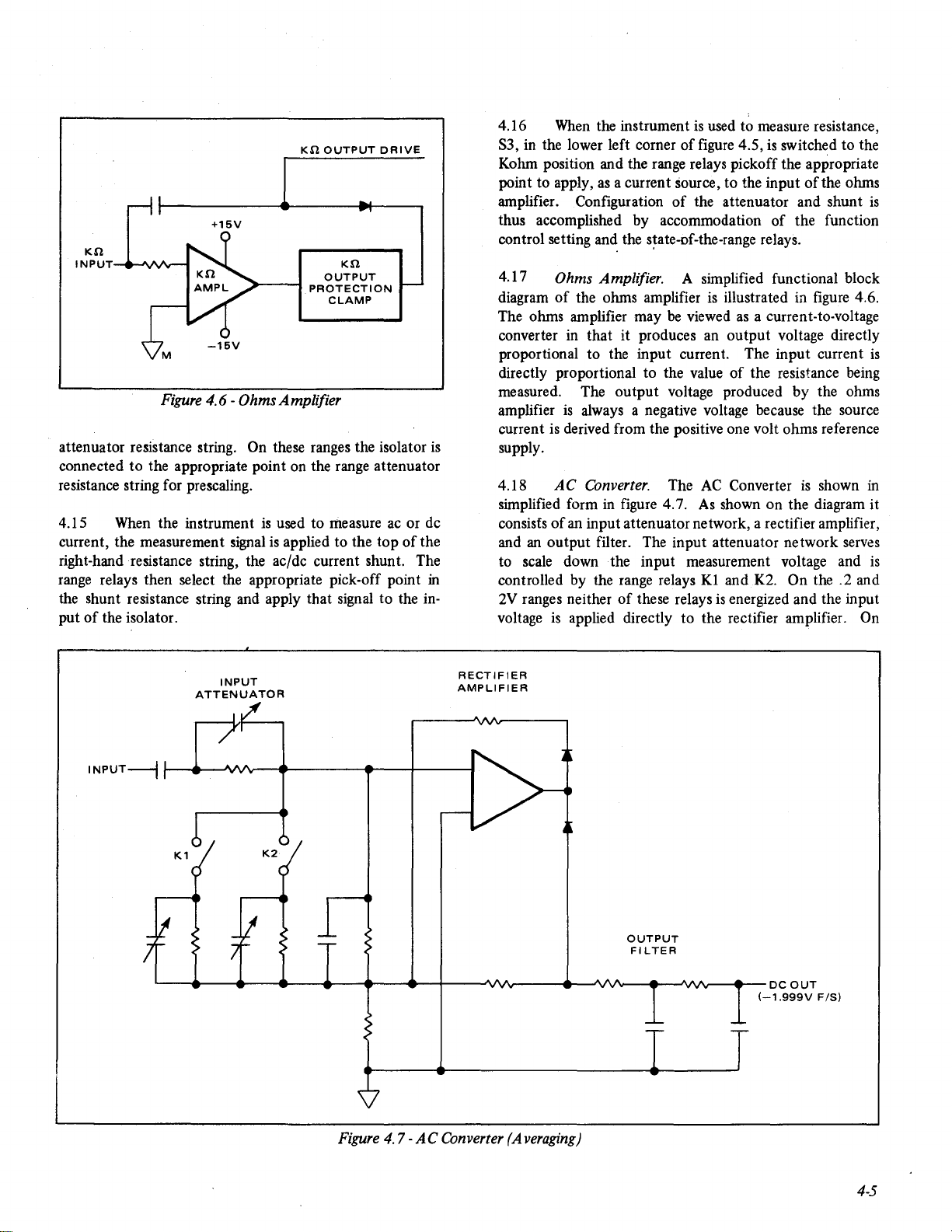

4.14 Voltage Attenuator and Current Shunt. This cir-

cuit

is

shown in simplified form in figure 4.5. The attenuator

and shunt circuit performs the following functions;

tenuation

of

input measurement voltages on the 20, 200,

1)

at-

and 1000 volt dc ranges, 2) scales down the ohms current

is

source when the instrument

as

3) acts

a shunt when on the

on the Kohms ranges,

ac

or dc current ranges, and

4) the attenuator and shunt circuit contains two series

resistance strings with pick-off

pOints selected by range

lays. In figure 4.5 the left-hand resistance string

re-

is

the

voltage range attenuator and ohms current source divider.

as

The right-hand resistance string serves

the ac and dc current shunt, and also has pick-off points selected by range

relays. In the upper left-hand corner

that the dc measurement signal

of

figure 4.5 note

is

switched around the

attenuator on the low ranges and goes directly to the

isolator.

On the 20, 200, and 1000 volt ranges the

measurement signal

is

switched onto the top

of

dc

the range

DC--.()--

RANGE

RANGE

20.,200,1000

SELECTED

ATTENUATION

S3-8

.2

8.

2.

,---------

'------__.--(100

RELAY

POINTS

RANGE

":"10

•

-'-100

• (10J.LA

.!-1000

•

1MA

Kn

TO

ATTENUATOR

nA

(1

J.LA

Kn

(100

J.LA

KnSOURCE

0--+1

V

ISO

(10

Kn

SOURCE)

SOURCE)

KnSOURCE)

Kn

SOURCE)

(OHMS

REFERENCE)

Mnl

DCV

RANGE

DVDR

(ATTN)

AC/DC

.2

2

20

200

CURRENT

rnA

rnA

rnA

rnA

2A

Kn

RANGE

DIV

(SOURCE

SHUNT

m

RELAY

SELECTED

SHUNT

POINTS

AC/DC

rnA

CURRENT

SHUNT

44

M

Figure 4.5 - Voltage Attenuator and Current Shunt

Kn

ARTEKMEDIA => 2012

IN

Kn

PUT_

........

/V\..-

+15V

>----1

OUTPUT

OUTPUT

PROTECTION

CLAMP

DRIVE

Kn

Figure 4.6 - Ohms Amplifier

attenuator resistance string. On these ranges the isolator

connected to the appropriate point on the range attenuator

resistance string for pre scaling.

When

4.15

the instrument

current, the measurement

is

used to measure

signal

is

ac

applied to the top

or dc

of

the

right-hand resistance string, the ac/dc current shunt. The

range

relays then select the appropriate pick-off point

the shunt resistance string and apply that signal to the

put

of

the isolator.

in

in-

is

4.16

S3,

When

the instrument

in

the lower left corner

is

used to measure resistance,

of

figure 4.5,

is

switched to the

Kohm position and the range relays pickoff the appropriate

point to apply,

amplifier. Configuration

thus accomplished by accommodation

control setting

as

a current source, to the input

of

the attenuator and shunt

an~

the

s~ate-of-the-range

of

the function

relays.

of

the ohms

is

4.17 Ohms Amplifier. A simplified functional block

of

diagram

The ohms amplifier may

converter in that it produces

proportional to the input current. The input current

directly proportional to the

the ohms amplifier is illustrated in figure 4.6.

be

viewed

value

as

a current-to-voltage

an

output voltage directly

of

the resistance being

is

measured. The output voltage produced by the ohms

amplifier

current

is

always a negative voltage because the source

is

derived from the positive one volt ohms reference

supply.

4.18

simplified form

consists

and

to

controlled by the range relays

2V

voltage

AC

Converter. The

in

figure 4.7.

of

an

input attenuator network, a rectifier amplifier,

an

output filter. The input attenuator network

scale

down the input measurement voltage and

ranges neither

is

applied directly to the rectifier amplifier. On

of

these relays

AC

Converter

As

shown on the diagram it

K1

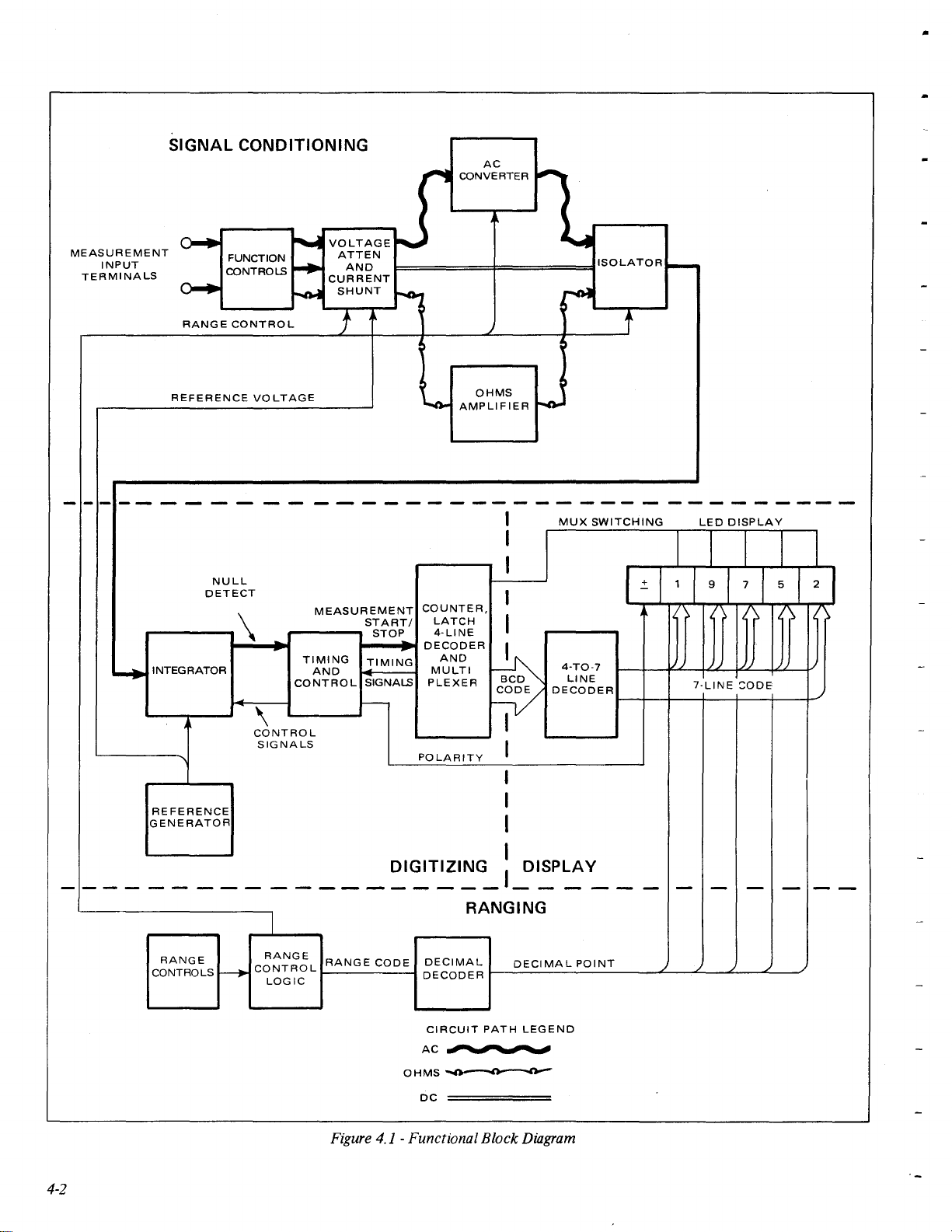

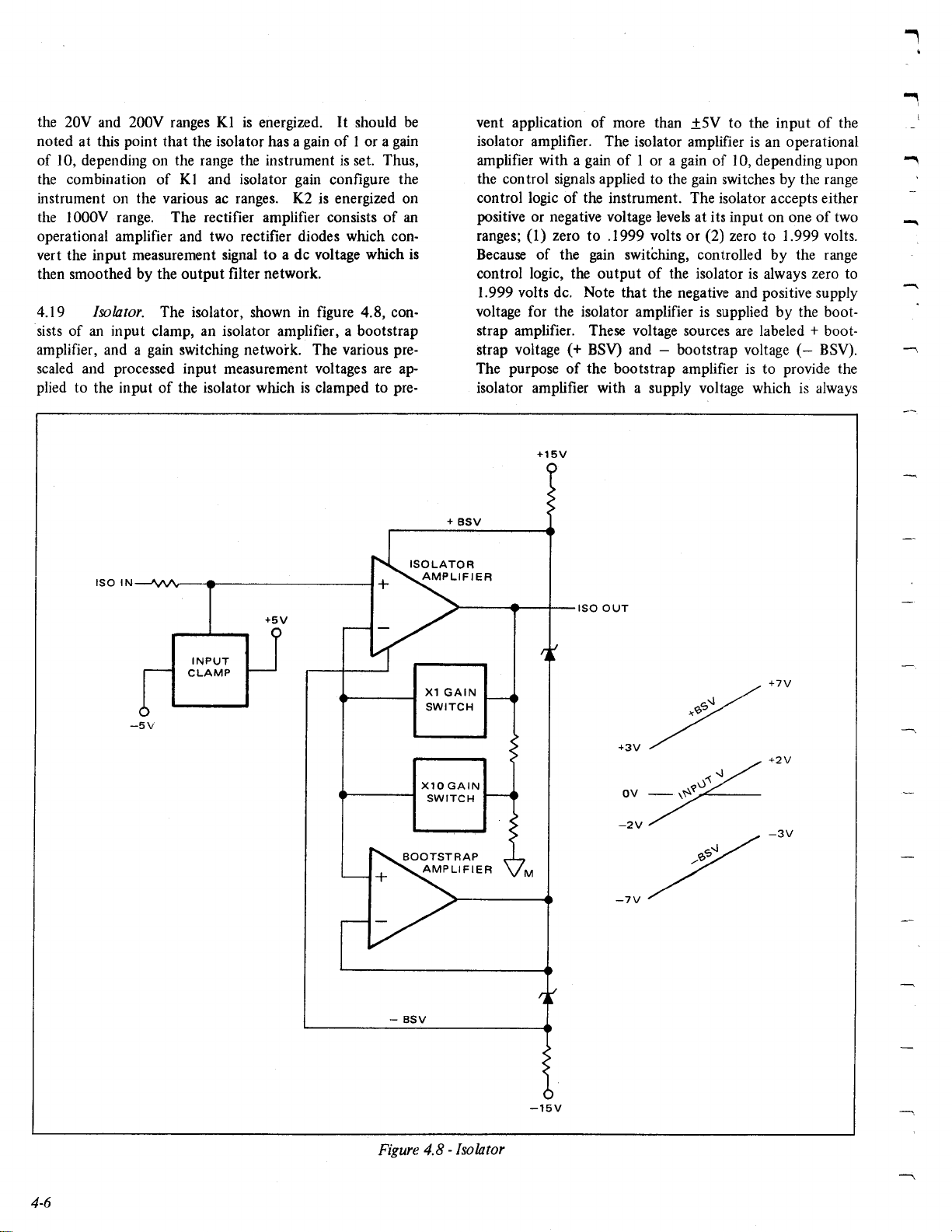

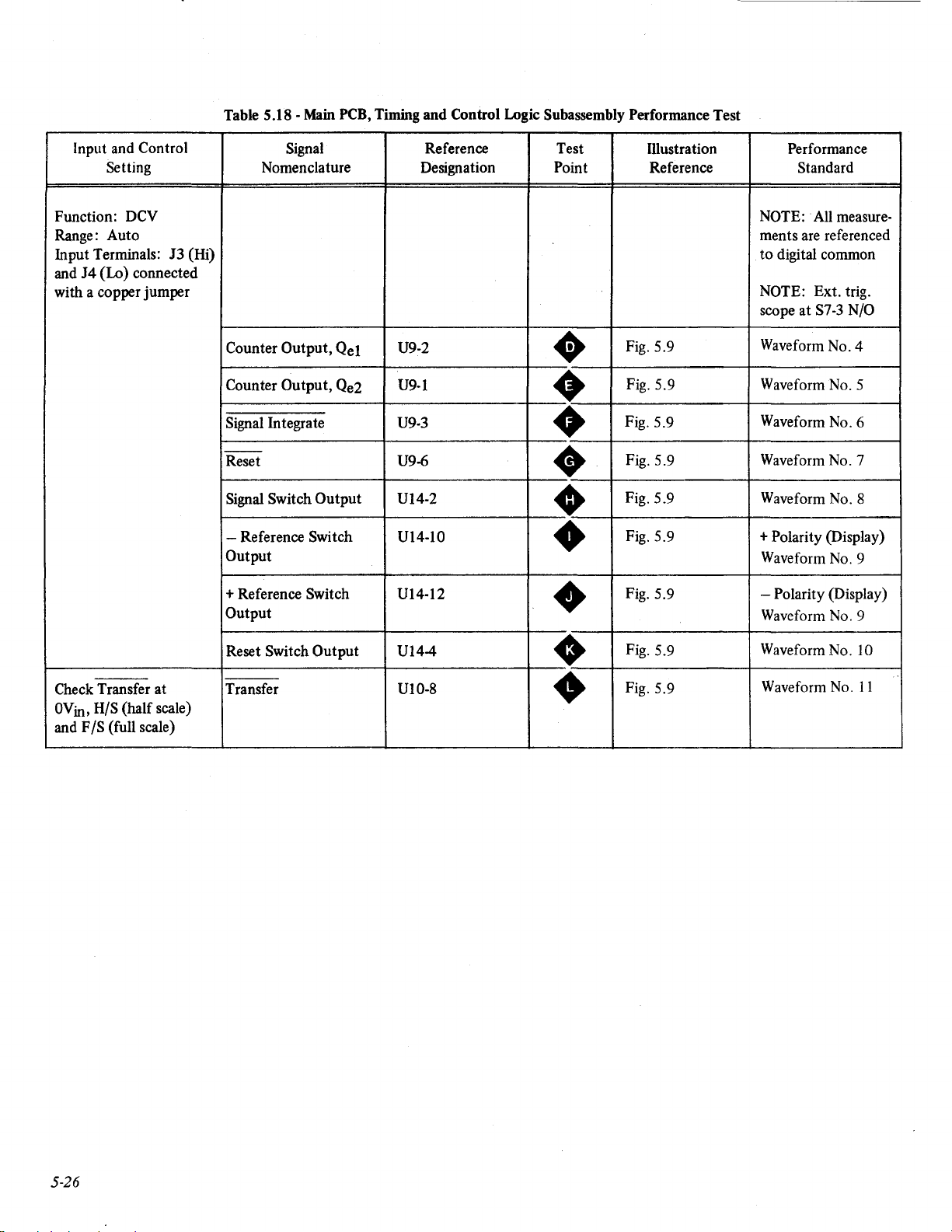

and