Dallas Semiconductor DS9503X, DS9503P-T-R, DS9503P Datasheet

1 of 3 102199

SPECIAL FEATURES

§ Zener characteristic with voltage snap–back

to protect against ESD hits

§ High avalanche voltage, low leakage and low

capacitance avoid signal attenuation

§ Compatible to all 5V logic families

§ Space saving, low inductance TSOC surface

mount package

§ On–chip 5Ω resistors for isolation at both

anode and cathode terminals

§ Industrial temperature range

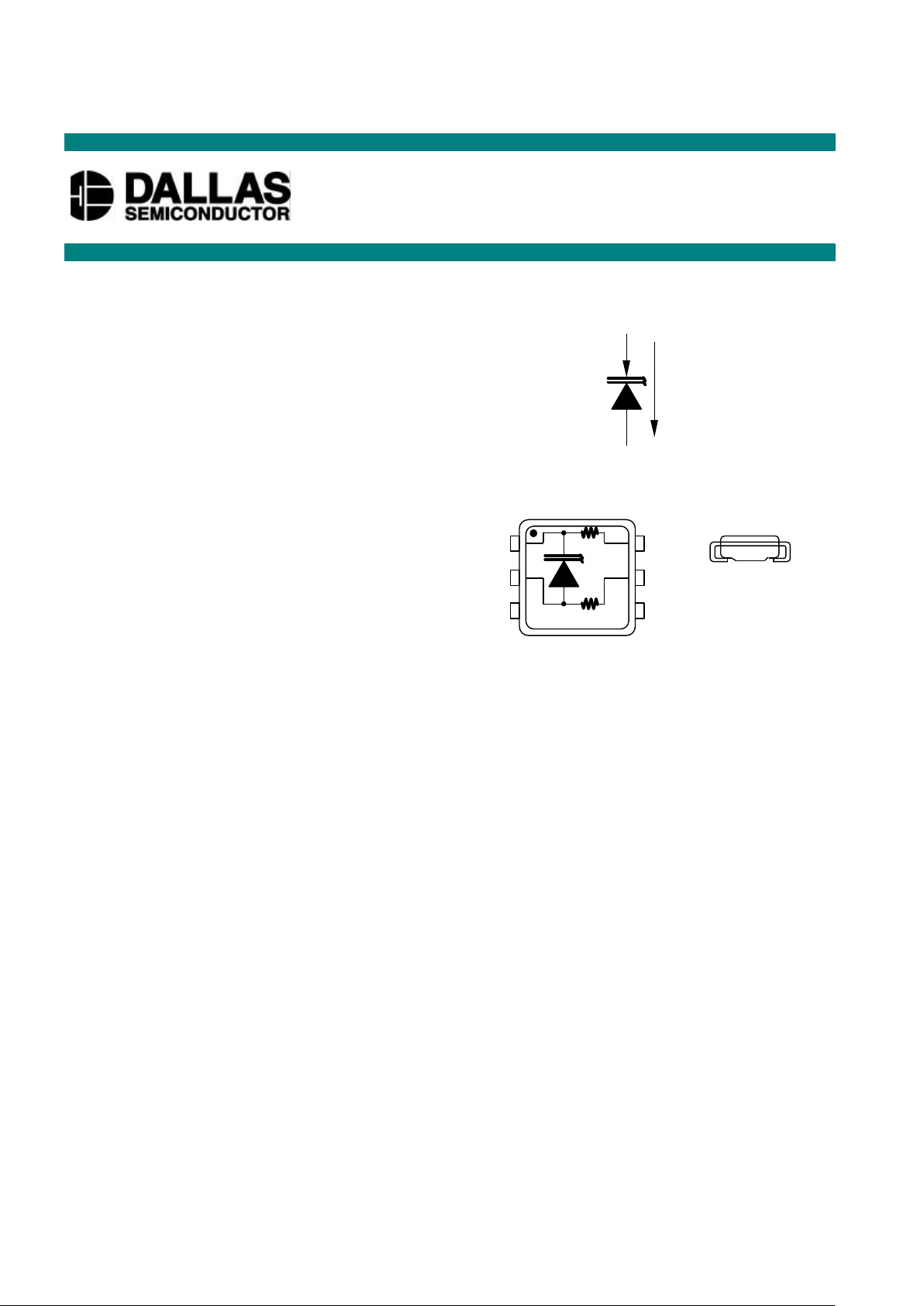

SYMBOL AND CONVENTIONS

PACKAGE OUTLINE

ORDERING INFORMATION

DS9503P 6-lead TSOC package

DESCRIPTION

This DS9503 is designed as an ESD protection device for 1–Wire MicroLAN interfaces. In contrast to the

DS9502, the DS9503 includes two 5Ω isolation resistors on chip. Although 5Ω are negligible during

communication, they represent a high impedance relative to the conducting diode during an ESD event.

Thus, the diode absorbs the energy while the resistors further isolate and protect the circuit at the other

side of the package. If used with circuits that already have a strong ESD–protection at their I/O port, the

ESD protection level is raised to more that 27 kV (IEC 801–2 Reference model). In case of abnormal

ESD hits beyond its maximum ratings the DS9503 will eventually fail “short” thus preventing further

damage.

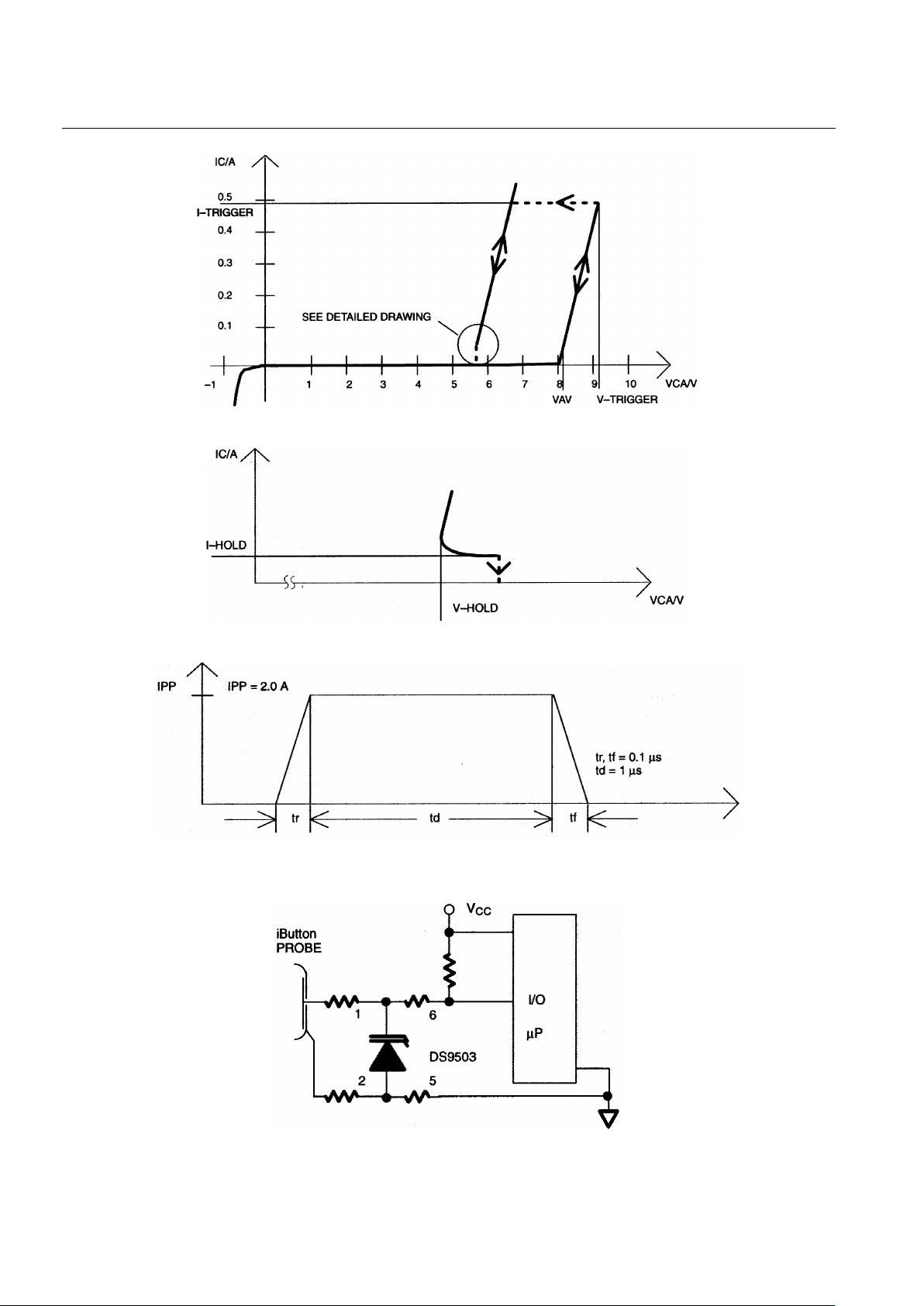

During normal operation the DS9503 behaves like a regular 7.5V Zener Diode. When the voltage

exceeds the trigger voltage, the I/V characteristic of the device will “snapback” allowing the same or

higher amount of current to flow, but at a significantly lower voltage. As long as a minimum current or

voltage is maintained, the device will stay in the “snapback mode”. If the voltage or the current falls

below the holding voltage or holding current, the device will abruptly change to its normal mode and

conduct only a small leakage current.

VCA

A

IC

C

TSOC SURFACE MOUNT PACKAGE

3.7 X 4.0 X 1.5 mm

See Mech. Drawings

Section

61

52

43

TOP VIEW

DS9503

ESD Protection Diode with Resistors

www.dalsemi.com

SIDE VIEW

DS9503

2 of 3 102199

DC CHARACTERISTICS Figure 1

DC CHARACTERISTICS DETAIL DRAWING Figure 2

TEST PULSE WAVEFORM Figure 3

TYPICAL APPLICATION Figure 4

Loading...

Loading...