Dallas Semiconductor DS80C310-QCG, DS80C310-MCG, DS80C310-ECG Datasheet

www.dalsemi.com

DS80C310

High-Speed Micro

FEATURES

80C32-compatible

- 8051 pin- and instruction set-compatible

- Full duplex serial port

- Three 16-bit timer/counters

- 256 bytes scratchpad RAM

- Multiplexed address/data bus

- Addresses 64 kB ROM and 64 kB RAM

High-Speed Architecture

- 4 clocks/machine cycle (8051 = 12)

- Runs DC to 33 MHz clock rates

- Single-cycle instruction in 121 ns

- Dual data pointer

- Optional variable length MOVX to access

fast/slow RAM /peripherals

10 total interrupt sources with 6 external

Internal power-on reset circuit

Upwardly compatible with the DS80C320

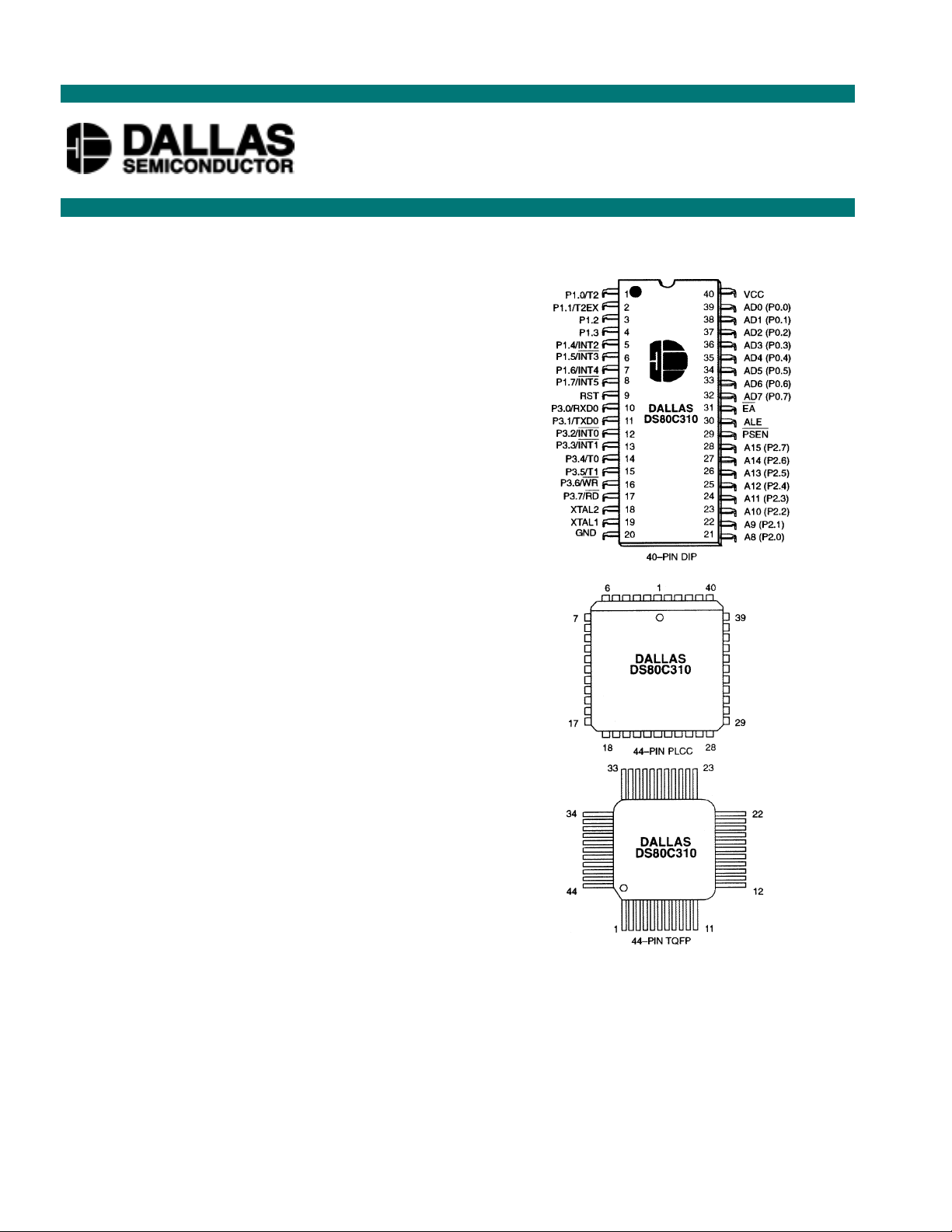

Available in 40-pin PDIP, 44-pin PLCC, and

44-pin TQFP

PACKAGE OUTLINE

DESCRIPTION

The DS80C310 is a fast 80C31/80C32-compatible microcontroller. It features a redesigned processor

core without wasted clock and memory cycles. As a result, it executes every 8051 instruction between 1.5

and 3 times faster than the original architecture for the same crystal speed. Typical applications will see a

speed improvement of 2.5 times using the same code and the same crystal. The DS80C310 offers a

maximum crystal speed of 33 MHz, resulting in apparent execution speeds of 82.5 MHz (approximately

2.5X).

1 of 23 112299

DS87C520/DS83C520

The DS80C310 is pin-compatible with the standard 80C32 and includes standard resources such as three

timer/counters, 256 bytes of RAM, and a serial port. It also provides dual data pointers (DPTRs) to speed

block data memory moves. It also can adjust the speed of MOVX data memory access between two and

nine machine cycles for flexibility in selecting external memory and peripherals. The DS80C310 offers

upward compatibility with the DS80C320.

ORDERING INFORMATION:

PART

NUMBER

DS80C310-MCG

DS80C310-QCG

DS80C310-ECG

DS80C310-MCL

DS80C310-QCL

DS80C310-ECL

PACKAGE MAX. CLOCK SPEED

40-pin plastic DIP

44-pin PLCC

44-pin TQFP

40-pin plastic DIP

44-pin PLCC

44-pin TQFP

25 MHz

25 MHz

25 MHz

33 MHz

33 MHz

33 MHz

TEMPERATURE

RANGE

0°C to 70°C

0°C to 70°C

0°C to 70°C

0°C to 70°C

0°C to 70°C

0°C to 70°C

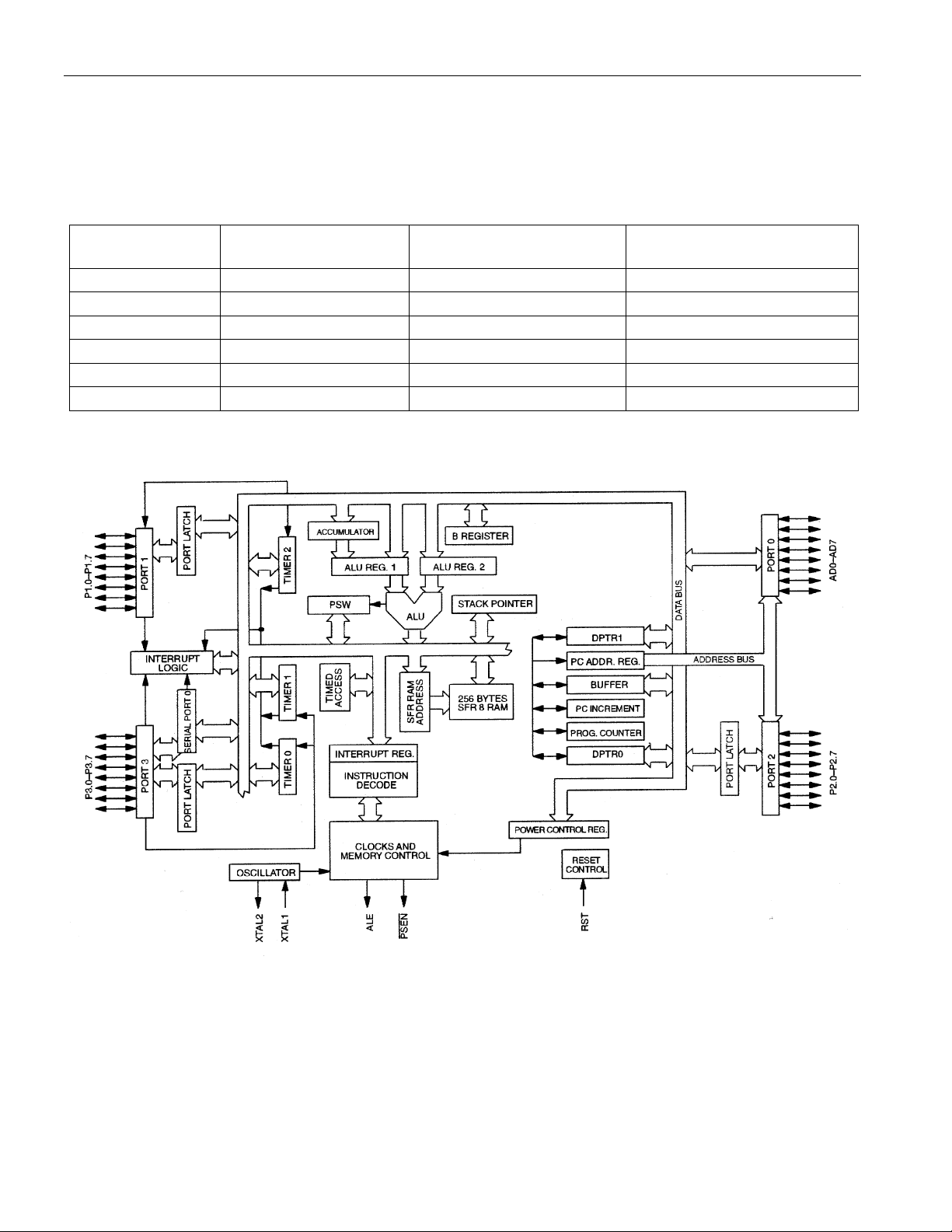

DS80C310 BLOCK DIAGRAM Figure 1

2 of 23

DS87C520/DS83C520

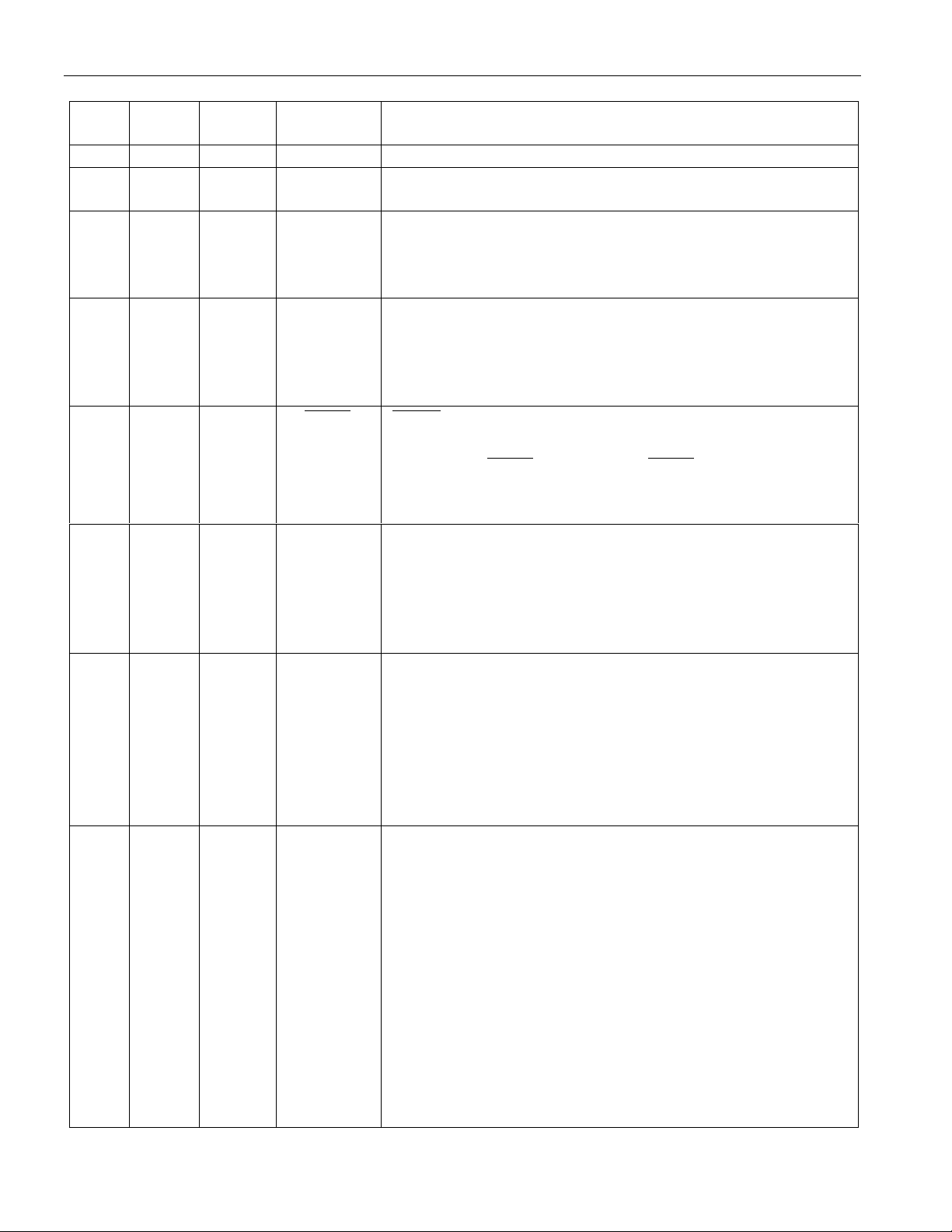

PIN DESCRIPTION Table 1

DIP PLCC TQFP SIGNAL

NAME

40 44 38 V

20 22,23116,17,

GND GND- Digital circuit ground.

CC

VCC -+5V.

39

910 4 RSTRST - Input. The RST input pin contains a Schmitt voltage

input to recognize external active high reset inputs. The pin

also employs an internal pulldown resistor to allow for a

combination of wired OR external Reset sources.

18

19

20

21

14

15

XTAL2

XTAL1

XTAL1, XTAL2 - The crystal oscillator pins XTAL1 and

XTAL2 provide support for parallel resonant, AT cut

crystals. XTAL1 acts also as an input in the event that an

external clock source is used in place of a crystal. XTAL2

serves as the output of the crystal amplifier.

29 32 26

PSEN PSEN - Output. The Program Store Enable output. This

signal is commonly connected to external ROM memory as a

chip enable.

PSEN is active low. PSEN is driven high

when data memory (RAM) is being accessed through the bus

and during a reset condition.

30 33 27 ALE ALE - Output. The Address Latch Enable output functions

as clock to latch the external address LSB from the

multiplexed address/data bus on Port 0. This signal is

commonly connected to the latch enable of an external 373

family transparent latch.ALE is forced high when the

DS80C310 is in a Reset condition.

39

38

37

36

35

34

33

32

43

42

41

40

39

38

37

36

37

36

35

34

33

32

31

30

1-8 2-9 40-44

1-3

AD0 (P0.0)

AD1 (P0.1)

AD2 (P0.2)

AD3 (P0.3)

AD4 (P0.4)

AD5 (P0.5)

AD6 (P0.6)

AD7 (P0.7)

AD0-7 (Port 0) - I/O. Port 0 is the multiplexed address/data

bus. During the time when ALE is high, the LSB of a

memory address is presented. When ALE falls to a logic 0,

the port transitions to a bidirectional data bus. This bus is

used to read external ROM and read/write external RAM

memory or peripherals. Port 0 has no true port latch and can

not be written directly by software. The reset condition of

Port 0 is high.

P1.0-P1.7 Port 1 - I/O. Port 1 functions as both an 8-bit bidirectional

I/O port and an alternate functional interface for Timer 2 I/O

and new External Interrupts. The reset condition of Port 1 is

with all bits at a logic 1. In this state, a weak pullup holds the

port high. This condition also serves as an input mode, since

any external circuit that writes to the port will overcome the

weak pullup. When software writes a 0 to any port pin, the

DS80C310 will activate a strong pulldown that remains on

until either a 1 is written or a reset occurs. Writing a 1 after

the port has been at 0 will cause a strong transition dr iver to

turn on, followed by a weaker sustaining pullup. Once the

momentary strong driver turns off, the port once again

becomes the output high (and input) state. The alternate

modes of Port 1 are outlined as follows:

DESCRIPTION

3 of 23

DS87C520/DS83C520

DIP PLCC TQFP SIGNAL

NAME

1

2

3

4

5

6

7

8

21

22

23

24

25

26

27

28

10-17

2

3

4

5

6

7

8

9

24

25

26

27

28

29

30

31

11,

40

41

42

43

44

1

2

3

18

19

20

21

22

23

24

25

5,7-13

A8 (P2.0)

A9 (P2.1)

A10(P2.2)

A11(P2.3)

A12(P2.4)

A13 P2.5)

A14(P2.6)

A15(P2.7)

P3.0-3.7 Port 3 - I/O. Port 3 functions as both an 8-bit bidirectional I/O

13-19

10

11

12

13

14

15

16

17

11

13

14

15

16

17

18

19

31 35 29

-12346

5

7

8

9

10

11

12

13

EA

NC NC - Reserved. These pins should not be connected. They

28

DESCRIPTION

Port Alternate Function

P1.0 T2 External I/O for Timer/Counter 2

P1.1 T2EX Timer/Counter 2 Capture/Reload Trigger

P1.2 none (DS80C320 has a serial port RXD)

P1.3 none (DS80C320 has a serial port TXD)

P1.4 INT2 External Interrupt 2 (Positive Edge Detect)

P1.5

INT3 External Interrupt 3 (Negative Edge Detect)

P1.6 INT4 External Interrupt 4 (Positive Edge Detect)

P1.7

INT5 External Interrupt 5 (Negative Edge Detect)

A8-15 (Port 2) -Output. Port 2 serves as the MSB for external

addressing. P2.7 is A15 and P2.0 is A8. The DS80C310 will

automatically place the MSB of an address on P2 for external

ROM and RAM access. Although Port 2 can be accessed like

an ordinary I/O port, the value stored on the Port 2 latch will

never be seen on the pins (due to memory access). Therefore

writing to Port 2 in software is only usef ul for the instructions

MOVX A, @ Ri or MOVX @ Ri, A. These instructions use the

Port 2 internal latch to supply the external address MSB; the

Port 2 latch value will be supplied as the address information.

port and an alternate functional interface for external Interrupts,

Serial Port 0, Timer 0 and 1 Inputs,

RD and WR strobes. The

reset condition of Port 3 is with all bits at a logic 1. In this

state, a weak pullup holds the port high. This condition also

serves as an input mode, since any external circuit that writes

to the port will overcome the weak pullup. When software

writes a 0 to any port pin, the DS80C310 will activate a strong

pulldown that remains on until either a 1 is written or a reset

occurs. Writing a 1 after the port has been at 0 will cause a

strong transition driver to turn on, followed by a weaker

sustaining pullup. Once the momentary strong driver turns off,

the port once again becomes both the output high and input

state. The alternate modes of Port 3 are outlined below.

Port Alternate Mode

P3.0 RXD0 Serial Port 0 Input

P3.1 TXD0 Serial Port 0 Output

P3.2

P3.3

INT0 External Interrupt 0

INT1 External Interrupt 1

P3.4 T0 Timer 0 External Input

P3.5 T1 Timer 1 External Input

P3.6

P3.7

WR External Data Memory Write Strobe

RD External Data Memory Read Strobe

EA - Input. This pin must be connected to ground for proper

operation.

are reserved for use with future devices in this family.

4 of 23

DS87C520/DS83C520

COMPATIBILITY

The DS80C310 is a fully static CMOS 8051-compatible microcontroller designed for high p erformance.

In most cases the DS80C310 can drop into an existing socket for the 80C31 or 80C32 to improve the

operation significantly. In general, software written for existing 8051-based systems works without

modification on the DS80C310. The exception is critical timing since the High-Speed Micro performs its

instructions much faster than the original for any given crystal selection. The DS80C310 runs the

standard 8051 family instruction set and is pin compatible with DIP, PLCC or TQFP packages. The

DS80C310 is a streamlined version of the DS80C320. It maintains upward compatibility but has fewer

peripherals.

The DS80C310 provides three 16-bit timer/counters, a full-duplex serial port, and 256 bytes of direct

RAM. I/O ports have the same operation as a standard 8051 product. Timers will default to a 12-clock per

cycle operation to keep their timing compatible with original 8051 family systems. However, timers are

individually programmable to run at the new 4 clocks per cycle if desired.

The DS80C310 provides several new hardware functions that are controlled by Special Function

registers. A summary of the Special Function Registers is provided in Table 2.

PERFORMANCE OVERVIEW

The DS80C310 features a high-speed 8051 compatible core. Higher spe ed comes not just from incr easin g

the clock frequency, but from a newer, more efficient design.

This updated core does not have the dummy memory cycles that are present in a standard 8051. A

conventional 8051 generates machine cycles using the clock frequenc y divided by 12. In the DS80C310,

the same machine cycle takes four clocks. Thus the fastest instructi on, 1 machine cycle, executes three

times faster for the same crystal frequency. Note that these are identical instructions. The majority of

instructions on the DS80C310 will see the full 3 to 1 speed improvement. Some instructions will get

between 1.5 and 2.4 to 1 improvement. All instructions are faster than the original 8051.

The numerical average of all opcodes gives approximately a 2.5 to 1 speed improvement. Improvement of

individual programs will depend on the actual instructions used. Speed-sensitive applications would make

the most use of instructions that are three times faster. However, the sheer number of 3 to 1 improved

opcodes makes dramatic speed improvements likely for any code. These archite cture improvements and

0.8

µm CMOS produce a peak instruction cycle in 121 ns (8.25 MIPs). The Dual Data Pointer feature

also allows the user to eliminate wasted instructions when moving blocks of memory.

INSTRUCTION SET SUMMARY

All instructions in the DS80C310 perform the same functions as their 8051 counterparts. Their effect on

bits, flags, and other status functions is identical. However, the timing of each instruction is different.

This applies both in absolute and relative number of clocks.

For absolute timing of real time events, the timing of software loops can be calculated using a table in the

High-Speed Microcontroller User’s Guide. However, counter/timers default to run at the older 12 clocks

per increment. In this way, t imer-based events occur at the standard intervals with software executing at

higher speed. Timers optionally can run at 4 clocks per increment to take advantage of faster processor

operation.

The relative time of two instructions might be different in the new architecture than it was previously. For

example, in the original architecture the “MOVX A, @ DPTR” i nstruction and the “MOV direct , direct”

instruction used two machine cycles or 24 oscillator cycles. Therefore, they required the same amount of

5 of 23

DS87C520/DS83C520

time. In the DS80C310, the MOVX instruction takes as little as two machine cycles or eight oscillator

cycles but the “MOV direct, direct” uses three machine cycles or 12 oscillator cycles. While both are

faster than their original counterparts, they now have different execution times. This is because the

DS80C310 usually uses one instruction cycle for each instruction byte. The user concerned with precise

program timing should examine the timing of each instruction for familiarity with the changes. Note that

a machine cycle now requires just four clocks, and provides one ALE pulse per cycle. Many instructions

require only one cycle, but some require five. In the original architecture, all were one or two cycles

except for MUL and DIV. Refer to the High-Speed Microcontroller User’s Guide for details and

individual instruction timing.

6 of 23

DS87C520/DS83C520

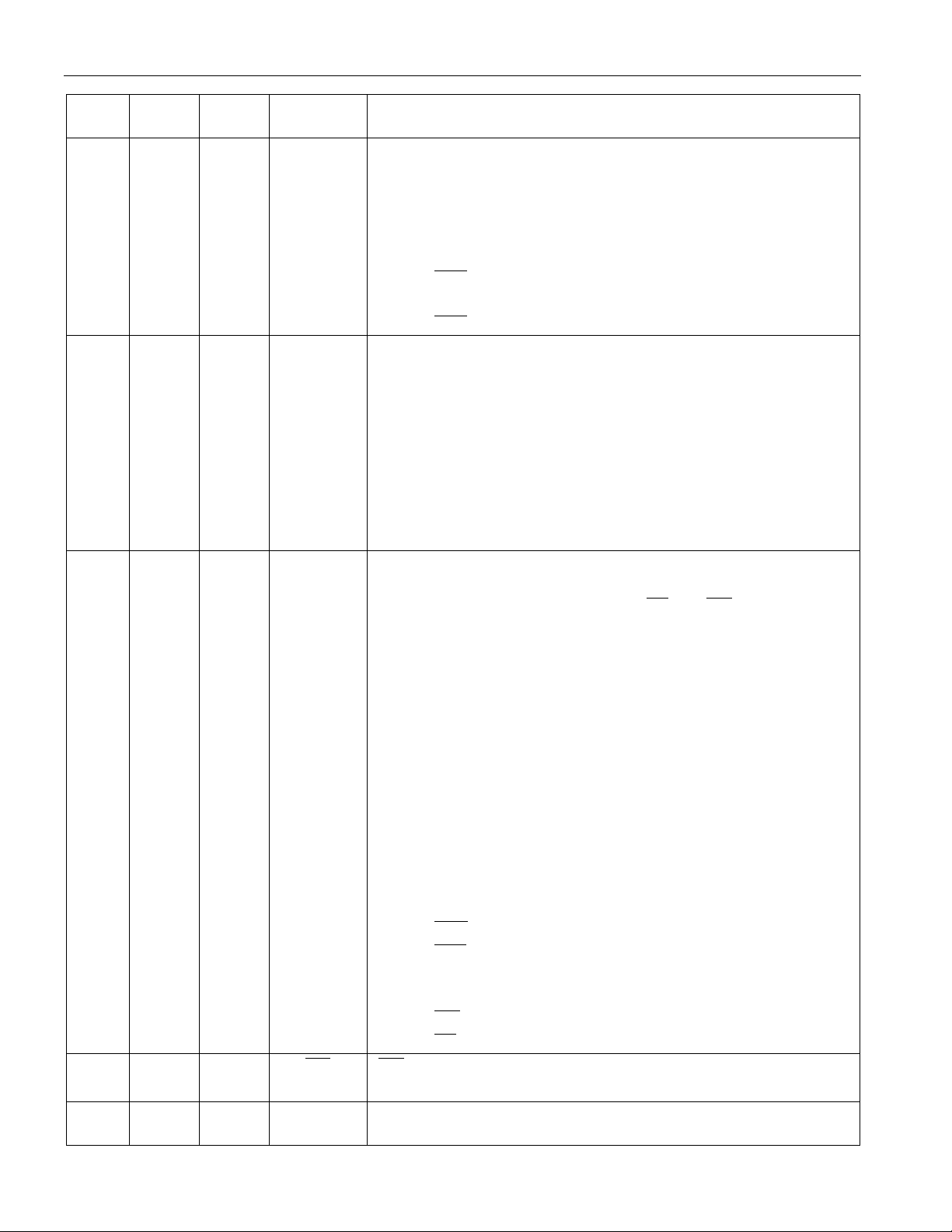

SPECIAL FUNCTION REGISTERS

Special Function Registers (SFRs) control most special features of the DS80C310. The High-Speed

Microcontroller User’s Guide describes all SFRs. Functions that are not part of the standa rd 80C32 are in

bold.

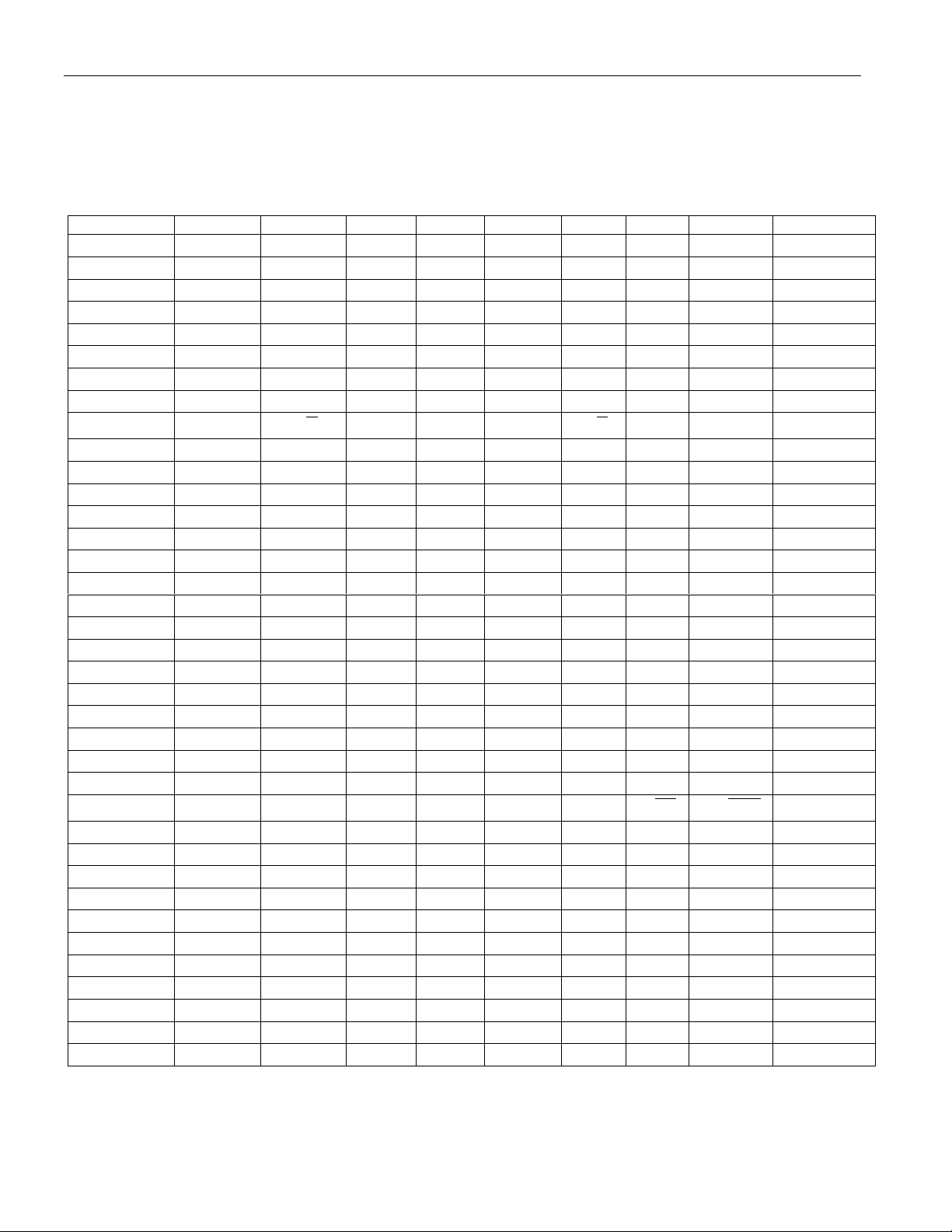

SPECIAL FUNCTION REGISTERS Table 2

REGISTER BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 ADDRESS

SP

DPL

DPH

DPL1

DPH1

DPS

PCON SMOD SM0D0 - - GF1 GF0 STOP IDLE

TCON TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

TMOD GATE

TL0

TL1

TH0

TH1

CKCON - - T2M T1M T0M MD2 MD1 MD0

P1 P1.7 P1.6 P1.5 P1.4 P1.3 P1.2 P1.1 P1.0

EXIF IE5 IE4 IE3 IE2

SCON SMO/FE SM1 SM2 REN TB8 RB8 TI RI

SBUF

P2 P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0

IE EA - ET2 ES0 ET1 EX1 ET0 EX0

SADDR0

P3 P3.7 P3.6 P3.5 P3.4 P3.3 P3.2 P3.1 P3.0

IP - - PT2 PSO PT1 PX1 PT0 PX0

SADEN0

STATUS 0 HIP LIP 1 1 1 1 1

T2CON TF2 EXF2 RCLK TCLK EXEN2 TR2

T2MOD - - - - - - T2OE DCEN

RCAP2L

RCAP2H

TL2

TH2

PSW CY AC F0 RS1 RS0 OV FL P

WDCON

ACC

EIE

B

EIP

0000000SEL

C/

T

M1 M0 GATE

C/

T

M1 M0

----

T2 CP/RL2

C/

-

POR

----

----

-- --- -

EX5 EX4 EX3 EX2

PX5 PX4 PX3 PX2

7 of 23

Loading...

Loading...