Dallas Semiconductor DS2224Z, DS2224Y, DS2224T, DS2224, DS2223Z Datasheet

...

DS2223/DS2224

DS2223/DS2224

EconoRAM

FEATURES

• Low–cost, general–purpose, 256–bit memory

– DS2223 has 256–bit SRAM

– DS2224 has 32–bit ROM, 224–bit SRAM

• Reduces control, address and data interface to a

single pin

• Each DS2224 32–bit ROM is factory–lasered with a

unique serial number

• DS2224 portion of ROM with custom code and unique

serial number available

• Minimal operating power: 45 nanocoulombs per

transaction @1.5V typical

• Less than 15 nA standby current at 25°C

• Nonvolatile data retention easily achieved via low–

cost alkaline batteries or capacitors

• Directly connects to a port pin of popular microcontrol-

lers

• Operation from 1.2 to 5.5 volts

• Popular TO–92 or SOT–223 surface mount package

• Operates over industrial temperature range –40°C to

+85°C

PACKAGE OUTLINE

TO–92

123

123

See Mech. Drawings

Section

See Mech. Drawings

PIN CONNECTIONS

Pin 1 GND – Ground

Pin 2 DQ – Data In/Out

Pin 3 V

Pin 4 GND – Ground

CC

– Supply

SOT–223

1

234

TOP VIEWBOTTOM VIEW

Section

DESCRIPTION

The DS2223 and DS2224 EconoRAMs are fully static,

micro–powered, read/write memories in low–cost

TO–92 or SOT–223 packages. The DS2223 is organized as a serial 256 x 1 bit static read/write memory.

The DS2224’s first 32 bits are lasered with a unique ID

code at the time of manufacture; the remaining 224 bits

are static read/write memory. Signaling necessary for

reading or writing is reduced to just one interface lead.

Both the DS2223 and DS2224 are not recommended

for new designs. However, the parts will remain available until the year 2003, at least.

ORDERING INFORMATION

DS2223 256–bit SRAM – TO–92 Package

DS2223Z 256–bit SRAM – SOT–223 Package

DS2223T 1000 piece tape–and–reel of DS2223

DS2223Y 2500 piece tape–and–reel of DS2223Z

DS2224 32–bit serial number (ROM), 224–bit

SRAM – TO–92 Package

DS2224Z 32–bit serial number (ROM), 224–bit

SRAM – SOT–223 Package

DS2224T 1000 piece tape–and–reel of DS2224

DS2224Y 2500 piece tape–and–reel of DS2224Z

080598 1/10

DS2223/DS2224

OPERATION

All communications to and from the EconoRAM are

accomplished via a single interface lead. EconoRAM

data is read and written through the use of time slots. All

data is preceded by a command byte to specify the type

of transaction. Once a specific transaction has been

initiated, either a read or a write, it must be completed for all memory locations before another

transaction can be started.

1–WIRE SIGNALLING

The EconoRAM requires strict protocols to insure data

integrity . The protocol consists of three types of signalling on one line: Write 0 time slot, Write 1 time slot and

Read Data time slot. All these signals are initiated by the

host.

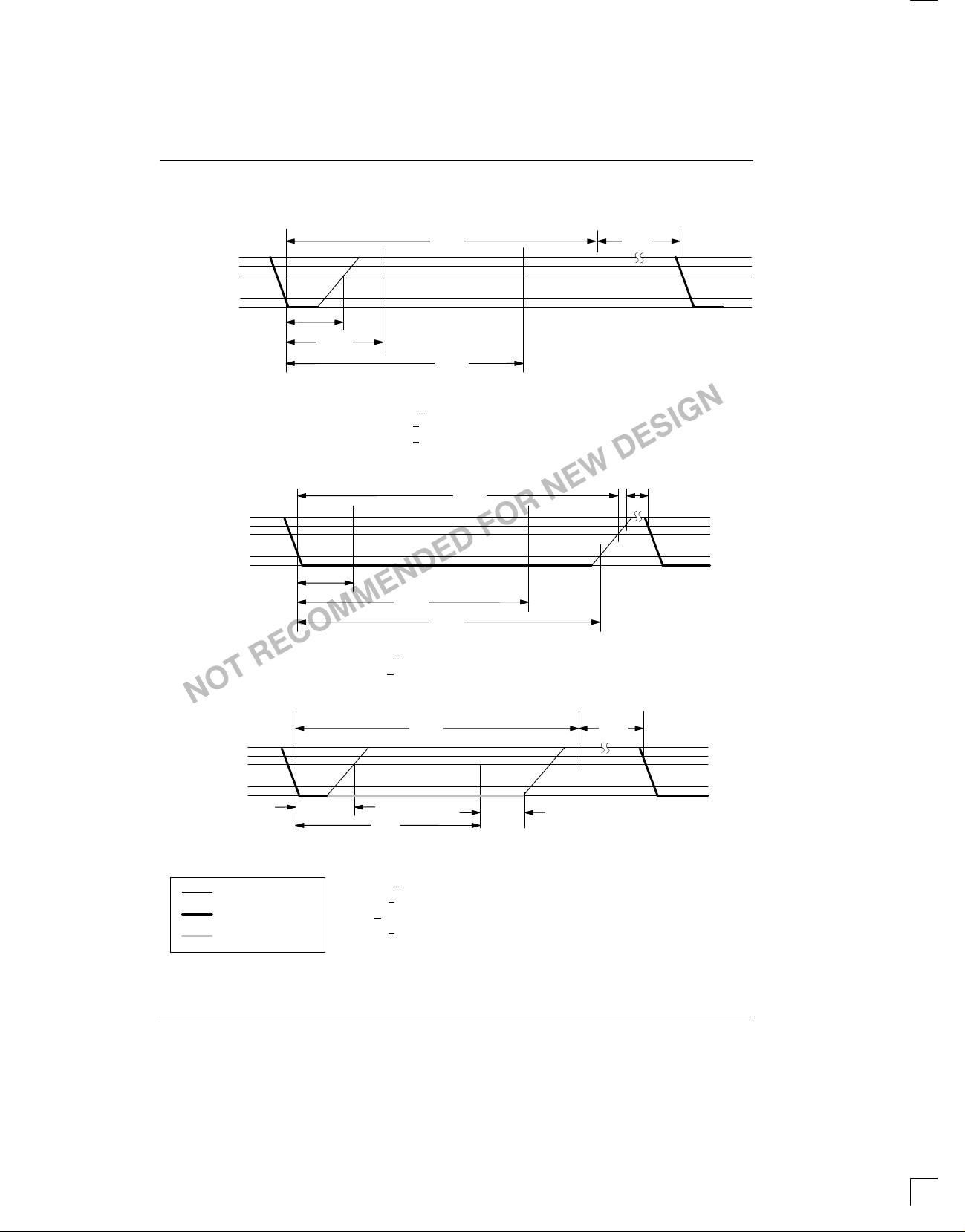

READ/WRITE TIME SLOTS

The definitions of write and read time slots are illustrated

in Figures 1 through 3. All time slots are initiated by the

host driving the data line low. The falling edge of the data

line synchronizes the EconoRAM to the host by triggering a delay circuit in the EconoRAM. During write time

slots, the delay circuit determines when the EconoRAM

will sample the data line. For a read data time slot, if a “0”

is to be transmitted, the delay circuit determines how

long the EconoRAM will hold the data line low overriding

the 1 generated by the host. If the data bit is a “1”, the

EconoRAM will leave the read data time slot

unchanged.

COMMAND BYTE

The command byte to specify the type of transaction is

transmitted LSB first from the host to the EconoRAM

using write time slots. The first bit of the command byte

(see Figure 4) is a logic 1. This indicates to the EconoRAM that a command byte is being written. The next two

bits are the select bits which denote the physical

address of the EconoRAM that is to be accessed (set to

00 currently). The remaining five bits determine whether

a read or a write operation is to follow. If a write operation

is to be performed, all five bits are set to a logic 1 level. If

a read operation is to be performed, any or all of these

bits are set to a logic 0 level. All eight bits of the command byte are transmitted to the EconoRAM with a separate time slot for each bit.

READ OR WRITE TRANSACTION

Read or write transactions are performed by initializing

the EconoRAM to a known state, issuing a command

byte, and then generating the time slots to either read

EconoRAM contents or write new data. Each transaction consists of 264 time slots. Eight time slots transmit

the command byte, the remaining 256 time slots transfer the data bits. (See Figure 5.) Once a transaction is

started, it must be completed before a new transaction

can begin.

To initially set the EconoRAM into a known state, 264

Write Zero time slots must be sent by the host. These

Write Zero time slots will not corrupt the data in the EconoRAM since a command byte has not been written.

This operation will increment the address pointer internal to the EconoRAM to its maximum count value. Upon

reaching this maximum value, the EconoRAM will

ignore all additional Write Zero time slots issued to it and

the internal address pointer will remain locked at the top

count value. This condition is removed by the reception

of a Write One time slot, typically the first bit of a command byte.

Once the EconoRAM has been set into a known state,

the command byte is transmitted to the EconoRAM with

eight write time slots. This resets the address pointer

internal to the EconoRAM and prepares it for the

appropriate operation, either a read or a write.

After the command byte has been received by the EconoRAM, the host controls the transfer of data. In the

case of a read transaction, the host issues 256 read time

slots. In the case of a write transaction, the host issues

256 write time slots according to the data to be written.

All data is read and written least significant bit first.

Although the DS2224 has the first 32 bits replaced by

lasered ROM rather than SRAM, it requires 256 write

time slots for a complete write transaction. The data

being sent during the first 32 write time slots has no

effect on the DS2224 other than advancing the internal

address pointer. As stated previously, it is not possible

to change from read to write or vice versa before a transaction is completed.

080598 2/10

READ/WRITE TIMING DIAGRAM

Write–One Time Slot Figure 1

DS2223/DS2224

V

PULLUP

V

PULLUP MIN

V

IH MIN

V

IL MAX

0V

t

LOW1

15 µs

Write–Zero Time Slot Figure 2

V

PULLUP

V

PULLUP MIN

V

IH MIN

V

IL MAX

0V

15 µs

60 µs <

1 µs <

1 µs <

SAMPLING WINDOW

60 µs

60 µs < t

t

1 µs <

REC

t

SLOT

DS2223/DS2224

SAMPLING WINDOW

60 µs

t

<

SLOT

t

< 15 µs

LOW1

t

<

REC

t

SLOT

DS2223/DS2224

t

LOW0

< t

SLOT

<

LOW0

<

t

REC

t

REC

Read–Data Time Slot Figure 3

V

PULLUP

V

PULLUP MIN

V

IH MIN

V

IL MAX

0V

RESISTOR

MASTER

DS2223/DS2224

t

LOWR

HOST SAMPLING

WINDOW

t

RDV

60 µs < t

SLOT

1 µs <

t

LOWR

0 <

t

RELEASE

t

1 µs <

REC

t

= 15 µs

RDV

t

SLOT

< 15 µs

<

<

< 45 µs

t

RELEASE

t

REC

080598 3/10

Loading...

Loading...