dallas semiconductor DS21Q352 service manual

DALLAS SEMICONDUCTOR Preliminary

Quad T1/E1 Transceiver (5V)

Quad T1/E1 Transceiver (3.3V)

FEATURES

P

• Four (4) Completely Independent T1 or E1 Transceivers

In One Small 27mm x 27mm Package

• Each Transceiver Contains a Short & Long Haul Line Interface

Plus a Full Featured Framer with Alarm Detection/Generation,

Elastic Stores, Hardware Based Signaling Support, Per DS0

Channel Control and HDLC Controller

• Each Multi-Chip Module (MCM) Contains Four Die of:

DS21352 (DS21Q352)

DS21552 (DS21Q552)

DS21354 (DS21Q354)

DS21554 (DS21Q554)

• Selection Guide:

Supply Device

T1 3.3V DS21Q352

T1 5V DS21Q552

E1 3.3V DS21Q354

E1 5V DS21Q554

DS21Q552/DS21Q554

DS21Q352/DS21Q354

• See the Specific DS21352/DS21552 and DS21354/DS21554

Data Sheets for Details on their Feature Set and Operation

• All Four T1 or E1 Transceivers Can be Concatenated into a Single

8.192MHz Backplane Data Stream

• IEEE 1149.1 JTAG-Boundary Scan Architecture

• DS21Q352/DS21Q552 and DS21Q354/DS21Q554 are Pin Compatible

to Allow the Same Footprint to Support T1 and E1 Applications

• 256–lead MCM BGA package (27mm X 27mm)

• Low Power 5V CMOS or Low Power 3.3V CMOS with 5V

Tolerant Input & Outputs

DESCRIPTION

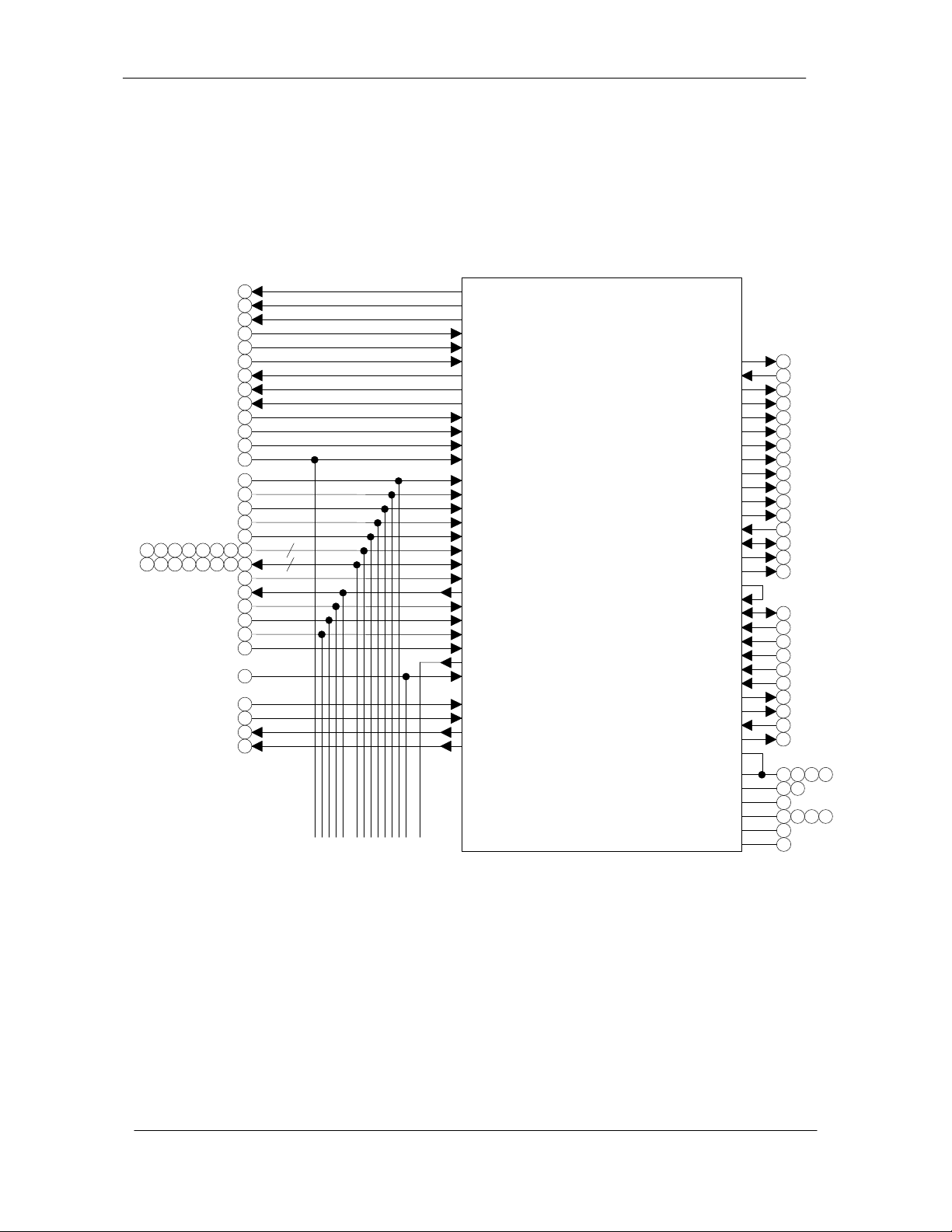

The Quad T1 and E1 Transceiver MCMs offer a high density packaging arrangement for the

DS21352/DS21552 T1 Single-Chip Transceivers and the DS21354/DS21554 E1 Single-Chip Transceivers.

Four silicon die of one of these devices is packaged in a Multi-Chip Module (MCM) with the electrical

connections as shown in Figure 1. All of the functions available on the DS21352/DS21552 and

DS21354/DS21554 are also available in the MCM packaged version however in order to minimize package

size, some signals have been deleted. These differences are detailed in Table 1.

This data sheet describes the electrical connections and the mechanical dimensions only. Please see the

DS21352/DS21552 and DS21354/DS21554 data sheets for full details on all of the features and the

operating characteristics of the device.

December 29, 1998

DALLAS SEMICONDUCTOR DS21Q352/DS21Q552/DS21Q354/DS21Q554 Preliminary Data Sheet

Changes from Normal DS21Q352/DS21Q552 & DS21Q354/DS21Q554 Configuration Table 1

1. The following signals are not available: XTALD / 8XCLK / TESO / TDATA / RCL / RDATA

DS21Q352 / DS21Q552 / DS21Q354 / DS21Q554 Schematic Figure 1

8

8

See Connecting Page

RCLKO

RPOSO

RNEGO

RCLKI

RPOSI

RNEGI

TCLKO

TPOSO

TNEGO

TCLKI

TPOSI

TNEGI

LIUC

TEST

BTS

MUX

WR*

RD*

A0 to A7/ALE

D0/AD0 to D7/AD7

CS*

INT*

JTRST

JTMS

JTCLK

JTDI

JTDO

MCLK

RTIP

RRING

TTIP

TRING

Signals Not Connected & Left Open Circuited

Include: 8XCLK / XTALD / RDATA / RCL

SCT # 1

DS21352 / DS21552 /

DS21354 / DS21554

CO

RCLK

RLOS/LOTC

8MCLK

RLINK

RLCLK

RCHBLK

RCHCLK

RSIGF

RSIG

RSER

RSYSCLK

RSYNC

RMSYMC

RFSYNC

TESO

TDATA

TSYNC

TSSYNC

TSYSCLK

TSER

TSIG

TCLK

TCHBLK

TCHCLK

TLINK

TLCLK

FMS

DVSS

RVSS

TVSS

DVDD

RVDD

TVDD

CI

December 29, 1998 2

DALLAS SEMICONDUCTOR DS21Q352/DS21Q552/DS21Q354/DS21Q554 Preliminary Data Sheet

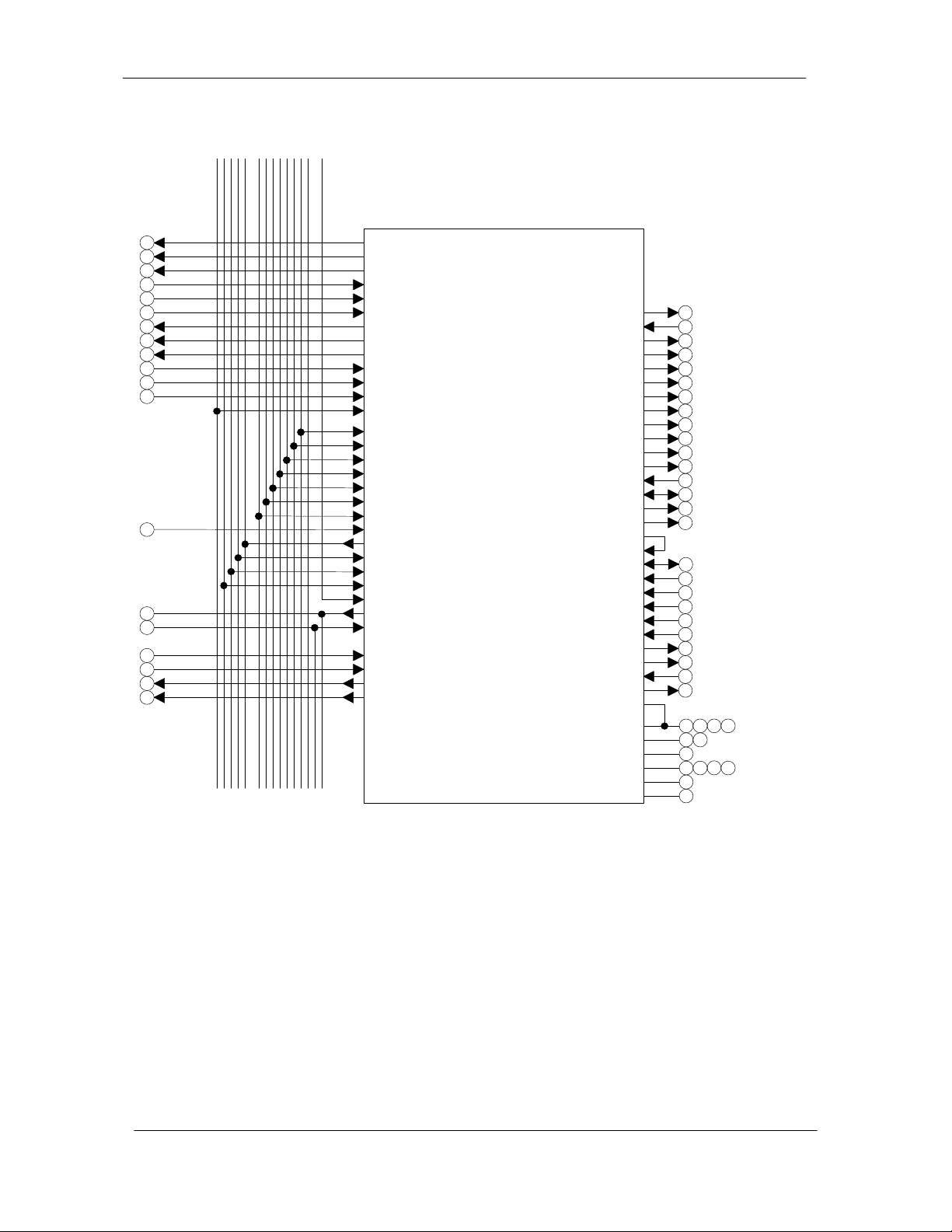

DS21Q352 / DS21Q552 / DS21Q354 / DS21Q554 Schematic Figure 1 (continued)

See Connecting Page

See Connecting Page

RCLKO

RPOSO

RNEGO

RCLKI

RPOSI

RNEGI

TCLKO

TPOSO

TNEGO

TCLKI

TPOSI

TNEGI

LIUC

TEST

BTS

MUX

WR*

RD*

A0 to A7/ALE

D0/AD0 to D7/AD7

CS*

INT*

JTRST

JTMS

JTCLK

JTDI

JTDO

MCLK

RTIP

RRING

TTIP

TRING

Signals Not Connected & Left Open Circuited

Include: 8XCLK / XTALD / RDATA / RCL

SCT # 2

DS21352 / DS21552 /

DS21354 / DS21554

CO

CI

RCLK

RLOS/LOTC

8MCLK

RLINK

RLCLK

RCHBLK

RCHCLK

RSIGF

RSIG

RSER

RSYSCLK

RSYNC

RMSYMC

RFSYNC

TESO

TDATA

TSYNC

TSSYNC

TSYSCLK

TSER

TSIG

TCLK

TCHBLK

TCHCLK

TLINK

TLCLK

FMS

DVSS

RVSS

TVSS

DVDD

RVDD

TVDD

December 29, 1998 3

DALLAS SEMICONDUCTOR DS21Q352/DS21Q552/DS21Q354/DS21Q554 Preliminary Data Sheet

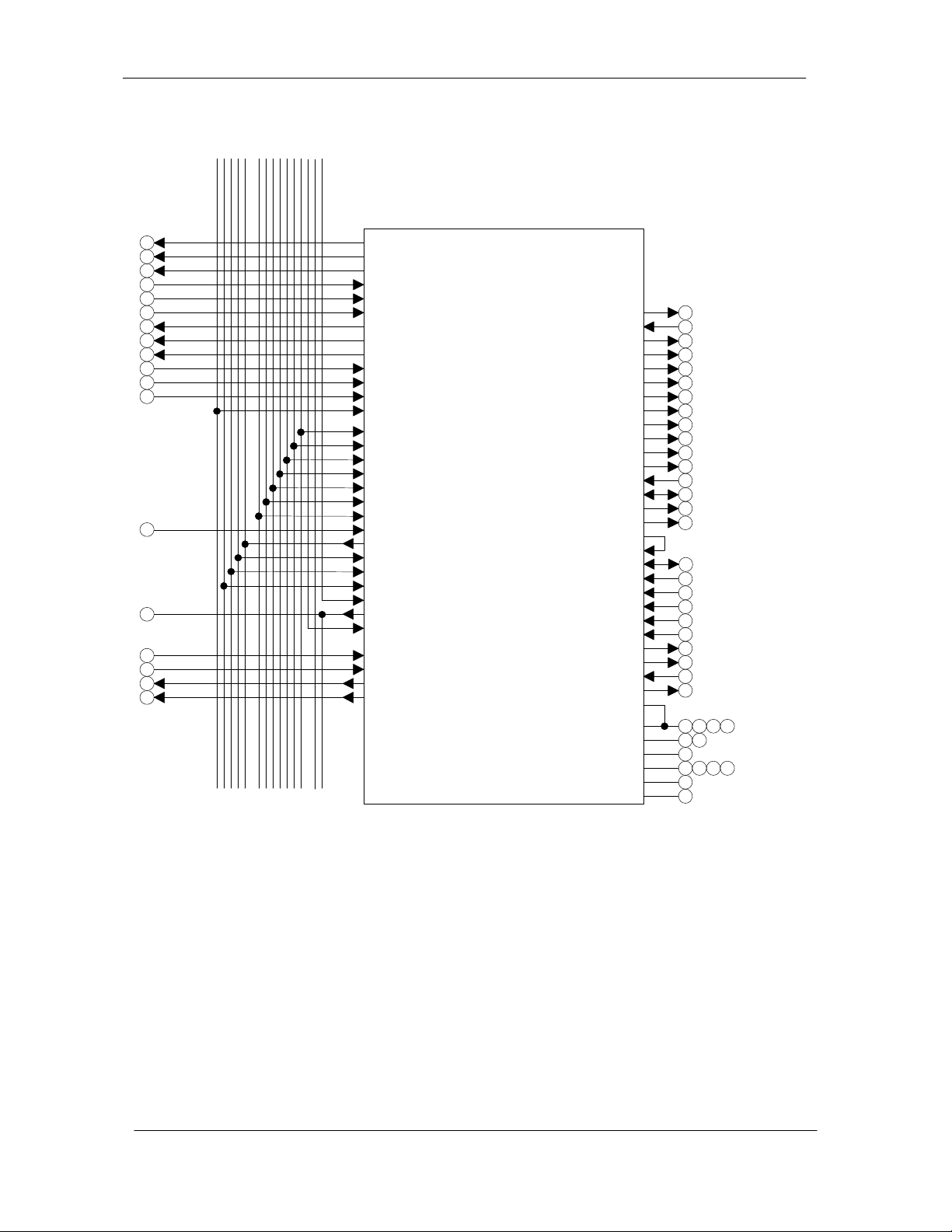

DS21Q352 / DS21Q552 / DS21Q354 / DS21Q554 Schematic Figure 1 (continued)

See Connecting Page

See Connecting Page

RCLKO

RPOSO

RNEGO

RCLKI

RPOSI

RNEGI

TCLKO

TPOSO

TNEGO

TCLKI

TPOSI

TNEGI

LIUC

TEST

BTS

MUX

WR*

RD*

A0 to A7/ALE

D0/AD0 to D7/AD7

CS*

INT*

JTRST

JTMS

JTCLK

JTDI

JTDO

MCLK

RTIP

RRING

TTIP

TRING

Signals Not Connected & Left Open Circuited

Include: 8XCLK / XTALD / RDATA / RCL

SCT # 3

DS21352 / DS21552 /

DS21354 / DS21554

CO

CI

RCLK

RLOS/LOTC

8MCLK

RLINK

RLCLK

RCHBLK

RCHCLK

RSIGF

RSIG

RSER

RSYSCLK

RSYNC

RMSYMC

RFSYNC

TESO

TDATA

TSYNC

TSSYNC

TSYSCLK

TSER

TSIG

TCLK

TCHBLK

TCHCLK

TLINK

TLCLK

FMS

DVSS

RVSS

TVSS

DVDD

RVDD

TVDD

December 29, 1998 4

Loading...

Loading...