r

A

RSER

AD7AD6AD5AD4AD3AD2AD1A

查询DS2153Q供应商

www.dalsemi.com

DS2153Q

E1 Single-Chip Transceive

FEATURES

Complete E1(CEPT) PCM-30/ISDN-PRI

transceiver functionality

Onboard line interface for clock/data recovery

and waveshaping

32-bit or 128-bit jitter attenuator

Generates line build-outs for both 120-ohm

and 75-ohm lines

Frames to FAS, CAS, and CRC4 formats

Dual onboard two-frame elastic store slip

buffers that can connect to backplanes up to

8.192 MHz

8-bit parallel control port that can be used on

either multiplexed or non-multiplexed buses

Extracts and inserts CAS signaling

Detects and generates Remote and AIS alarms

Programmable output clocks for Fractional

E1, H0, and H12 applications

Fully independent transmit and receive

functionality

Full access to both Si and Sa bits

Three separate loopbacks for testing

Large counters for bipolar and code

violations, CRC4 code word errors, FAS

errors, and E bits

Pin-compatible with DS2151Q T1 Single-

Chip Transceiver

5V supply; low power CMOS

Industrial grade version (-40°C to +85°C)

available (DS2153QN)

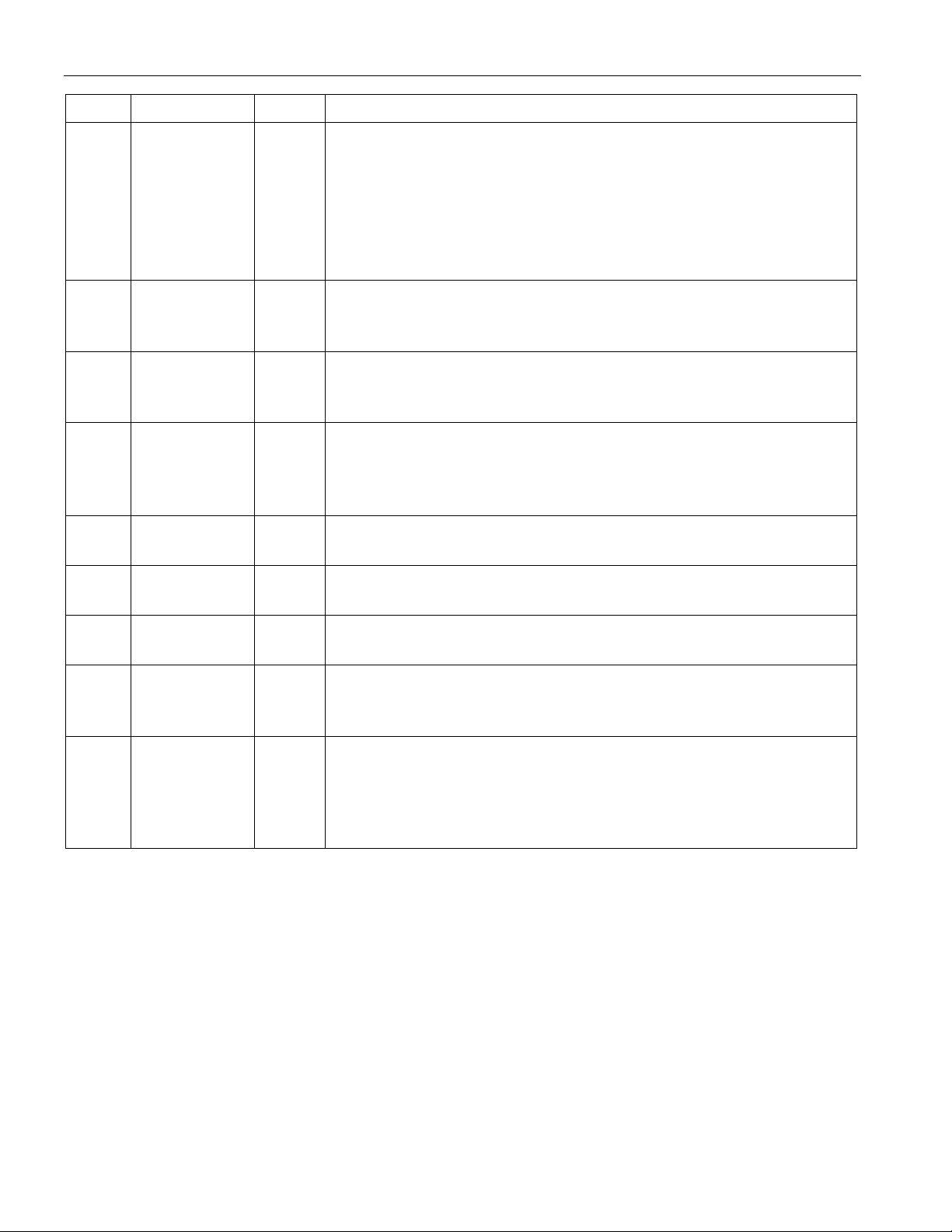

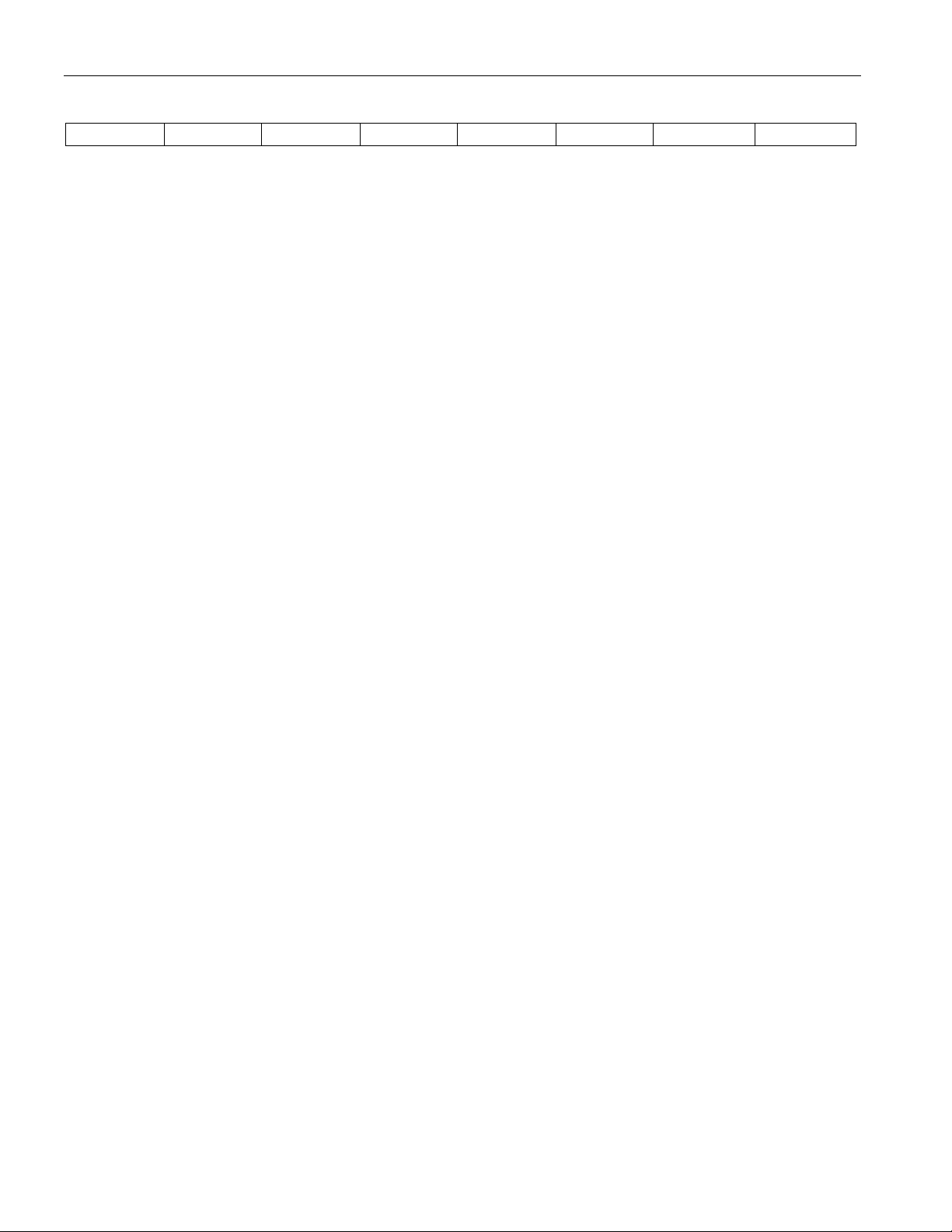

PIN ASSIGNMENT

FUNCTIONAL BLOCKS

HAUL LINE

INTERFACE

LONG & SHORT

PARALLEL CONTROL

DALLAS

DS2153Q

E1 SCT

LE

WR

RLINK

RLCLK

DVSS

RCLK

RCHCLK

RSYNC

RLOS/LOTC

SYSCLK

ACTUAL SIZE OF 44-PIN PLCC

CS

RD

65432

7

8

9

10

11

12

13

14

15

16

17

1819202122232425262728

FRAMER

PORT

1

4443424140

STORES

ELASTIC

D0

TCHCLK

39

TSER

38

TCLK

37

DVDD

36

TSYNC

35

TLINK

34

TLCLK

33

TCHBLK

32

TRING

31

TVDD

30

TVSS

29

TTIP

DESCRIPTION

BTS

RTIP

ACLKI

RCHBLK

RVDD

RRING

RVSS

INT1

XTAL1

INT2

XTAL2

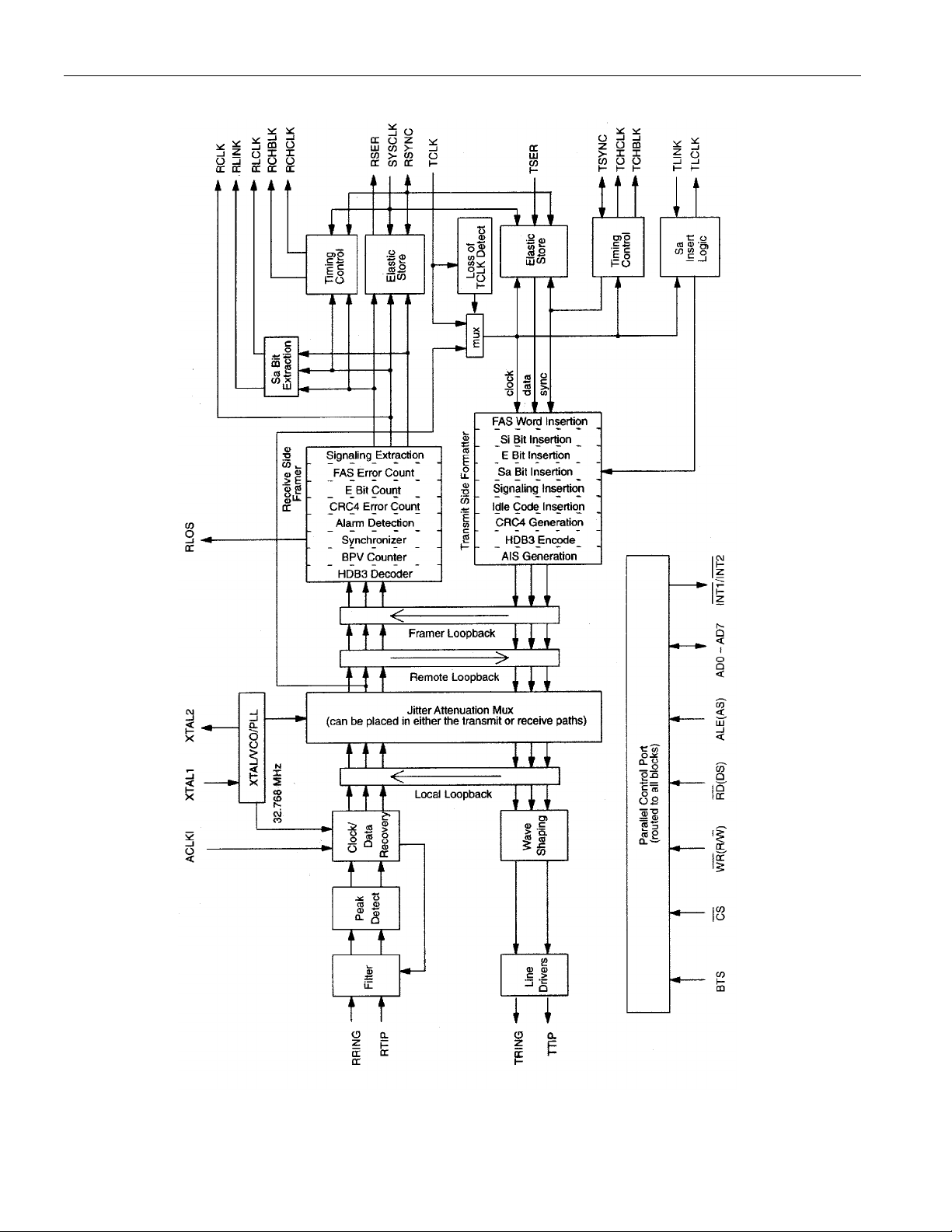

The DS2153Q T1 Single-Chip Transceiver (SCT) contains all of the necessary functions for connection

to E1 lines. The onboard clock/data recovery circuitry coverts the AMI/HDB3 E1 waveforms to a NRZ

serial stream. The DS2153 automatically adjusts to E1 22 AWG (0.6 mm) twisted-pair cables from 0 to

1.5 km. The device can generate the necessary G.703 waveshapes for both 75-ohm and 120-ohm cables.

The onboard jitter attenuator (selectable to either 32 bits or 128 bits) can be placed in either the transmit

or receive data paths. The framer locates the frame and multiframe boundaries and monitors the data

stream for alarms. It is also used for extracting and inserting signaling data, Si, and Sa-bit information.

The device contains a set of 71 8-bit internal registers which the user can access to control the operation

1 of 52 070299

DS2153Q

of the unit. Quick access via the parallel control port allows a single micro to handle many E1 lines. The

device fully meets all of the latest E1 specifications, including ITU G.703, G.704, G.706, G.823, and

I.431 as well as ETSI 300 011, 300 233, TBR 12 and TBR 13.

TABLE OF CONTENTS

1. Introduction

2. Parallel Control Port

3. Control and Test Registers

4. Status and Information Registers

5. Error Count Registers

6. Sa Data Link Control and Operation

7. Signaling Operation

8. Transmit Idle Registers

9. Clock Blocking Registers

10. Elastic Store Operation

11. Additional (Sa) and International (Si) Bit Operation

12. Line Interface Control Function

13. Timing Diagrams, Synchronization Flowchart, and Transmit flow Diagram

14. DC and AC Characteristics

1.0 INTRODUCTION

The analog AMI waveform off of the E1 line is transformer coupled into the RRING and RTIP pins of

the DS2153Q. The device recovers clock and data from the analog signal and passes it through the jitter

attenuation mux to the receive side framer where the digital serial stream is analyzed to locate the framing

pattern. If needed, the receive side elastic store can be enabled in order to absorb the phase and frequency

differences between the recovered E1 data stream and an asynchronous backplane clock which is

provided at the SYSCLK input.

The transmit side of the DS2153Q is totally independent from the receive side in both the clock

requirements and characteristics. The transmit formatter will provide the necessary data overhead for E1

transmission. Once the data stream has been prepared for transmission, it is sent via the jitter attenuation

mux to the waveshaping and line driver functions. The DS2153Q will drive the E1 line from the TTIP

and TRING pins via a coupling transformer.

2 of 52

DS2153Q

Reader’s Note

This data sheet assumes a particular nomenclature of the E1 operating environment. There are 32 8-bit

timeslots in E1 systems which are numbered 0 to 31. Timeslot 0 is transmitted first and received first.

These 32 timeslots are also referred to as channels with a numbering scheme of 1 to 32. Timeslot 0 is

identical to channel 1, timeslot 1 is identical to channel 2, and so on. Each timeslot (or channel) is made

up of 8 bits which are numbered 1 to 8. Bit number 1 is the MSB and is transmitted first. Bit number 8 is

the LSB and is transmitted last. Throughout this data sheet, the following abbreviations will be used:

FAS Frame Alignment Signal

CAS Channel Associated Signaling

MF Multiframe

Si International Bits

CRC4 Cyclical Redundancy Check

CCS Common Channel Signaling

Sa Additional bits

E-bit CRC4 Error bits

3 of 52

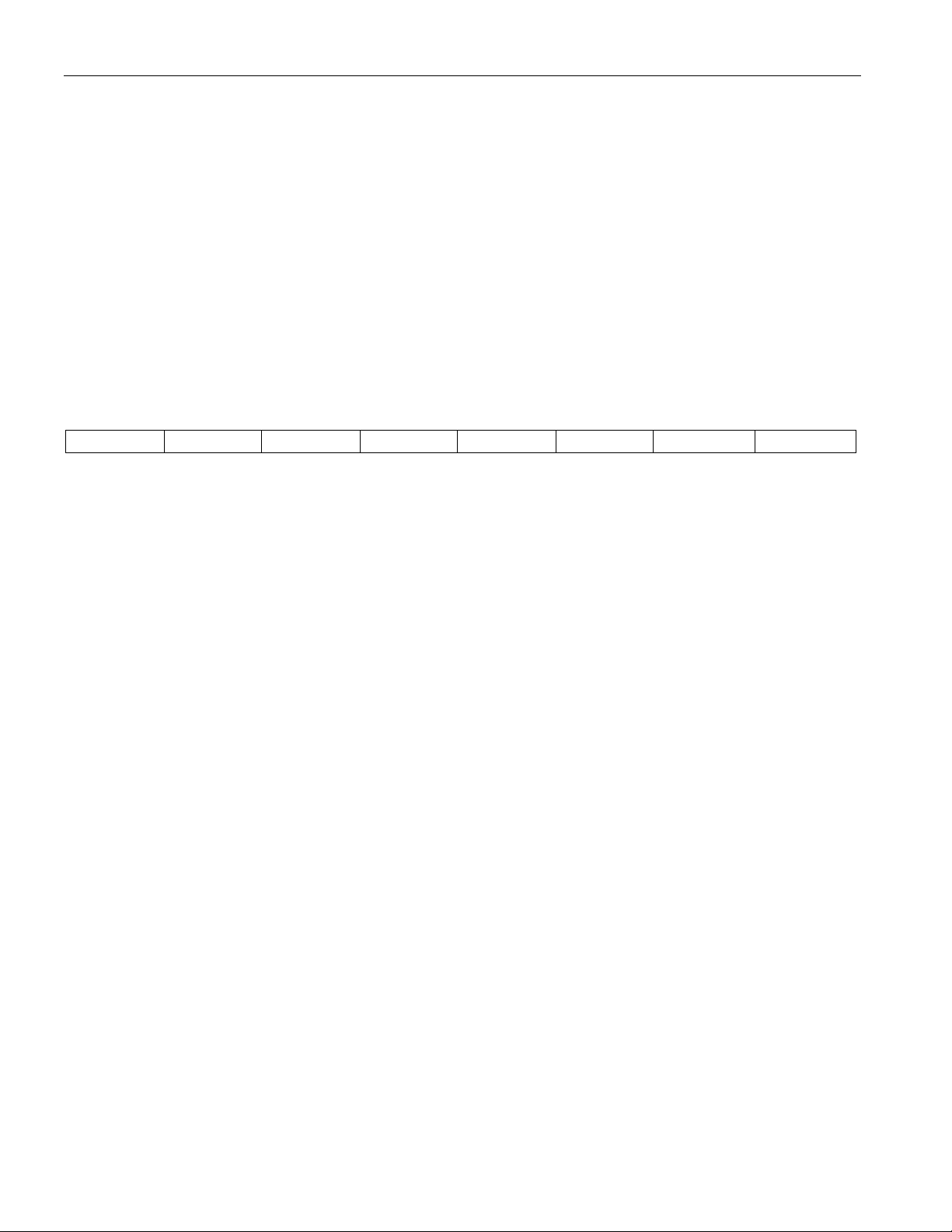

DS2153Q BLOCK DIAGRAM Figure 1-1

DS2153Q

4 of 52

PIN DESCRIPTION Table 1-1

PIN SYMBOL TYPE DESCRIPTION

DS2153Q

1

2

3

4

5

6

AD4

AD5

AD6

AD7

RD (DS)

CS

I/O Address/Data Bus. An 8-bit multiplexed address/data bus.

I Read Input (Data Strobe).

I Chip Select. Must be low to read or write the port.

7ALE(AS) IAddress Latch Enable (Address Strobe). A positive going edge

serves to demultiplex the bus.

8

WR

(R/W)

I Write Input (Read/Write).

9RLINKOReceive Link Data. Outputs the full receive data stream including

the Sa bits. See Section 13 for timing details.

10 RLCLK O Receive Link Clock. 4 kHz to 20 kHz demand clock for the RLINK

output; controlled by RCR2. See Section 13 for timing details.

11 DVSS -

Digital Signal Ground. 0.0 volts. Should be tied to local ground

plane.

12 RCLK O Receive Clock. Recovered 2.048 MHz clock.

13 RCHCLK O

Receive Channel Clock. 256 kHz clock which pulses high during

the LSB of each channel. Useful for parallel to serial conversion of

channel data. See Section 13 for timing details.

14 RSER O Receive Serial Data. Received NRZ serial data, updated on rising

edges of RCLK or SYSCLK.

15 RSYNC I/O

Receive Sync. An extracted pulse, one RCLK wide, is output at this

pin which identifies either frame (RCR1.6=0) or multiframe

boundaries (RCR1.6=1). If the elastic store is enabled via the

RCR2.1, then this pin can be enabled to be an input via RCR1.5 at

which a frame boundary pulse is applied. See Sect ion 13 for timing

details.

16 RLOS/LOTC O Receive Loss of Sync/Loss of Transmit Clock. A dual function

output. If TCR2.0=0, will toggle high when the synchronizer is

searching for the E1 frame and multiframe; if TCR2.0=1, will toggle

high if the TCLK pin has not toggled for 5 µs.

17 SYSCLK I System Clock. 1.544 MHz or 2.048 MHz clock. Only used when

the elastic store functions are enabled via RCR2.1. Should be tied

low in applications that do not use the elastic store. If tied high for at

least 100 µs, will force all output pins (including the parallel port) to

3-state.

5 of 52

DS2153Q

PIN SYMBOL TYPE DESCRIPTION

18 RCHBLK O Receive Channel Block. A user-programmable output that can be

forced high or low during any of the 32 E1 channels. Useful for

blocking clocks to a serial UART or LAPD controller in

applications where not all E1 channels are used, such as Fractional

E1, 384 kbps service (H0), 1920 kbps (H12), or ISDN-PRI. Also

useful for locating individual channels in drop-and-insert

applications. See Section 13 for timing details.

19 ACLKI I

Alternate Clock Input. Upon a receive carrier loss, the clock

applied at this pin (normally 2.048 MHz) will be routed to the

RCLK pin. If no clock is routed to this pin, then it should be tied to

DVSS VIA A 1 kΩ resistor.

20 BTS I Bus Type Select. Strap high to select Motorola bus timing; strap

low to select Intel bus timing. This pin controls the function of the

RD (DS), ALE(AS), and

(R/W) pins. If BTS=1, then these pins

WR

assume the function listed in parenthesis ().

21

22

23 RVDD -

RTIP

RRING

- Receive Tip and Ring. Analog inputs for clock recovery circuitry;

connects to a 1:1 transformer (see Section 12 for details).

Receive Analog Positive Supply. 5.0 volts. Should be tied to

DVDD and TVDD pins.

24 RVSS -

Receive Signal Ground. 0.0 volts. Should be tied to local ground

plane.

25

26

27

XTAL1

XTAL2

INT1

- Crystal Connections. A pullable 8.192 MHz crystal must be

applied to these pins. See Section 12 for crystal specifications.

O

Receive Alarm Interrupt 1. Flags host controller during alarm

conditions defined in Status Register 1. Active low, open drain

output.

28

INT2

O Receive Alarm Interrupt 2. Flags host controller during conditions

defined in Status Register 2. Active low, open drain output.

29 TTIP -

Transmit Tip. Analog line driver output; connects to a step-up

transformer (see Section 12 for details).

30 TVSS - Transmit Signal Ground. 0.0 volts. Should be tied to local ground

plane.

31 TVDD - Transmit Analog Positive Supply. 5.0 volts. Should be tied to

DVDD and RVDD pins.

32 TRING - Transmit Ring. Analog line driver outputs; connects to a step-up

transformer (see Section 12 for details).

6 of 52

DS2153Q

PIN SYMBOL TYPE DESCRIPTION

33 TCHBLK O Transmit Channel Block. A user-programmable output that can be

forced high or low during any of the 32 E1 channels. Useful for

blocking clocks to a serial UART or LAPD controller in

applications where not all E1 channels are used, such as Fractional

E1, 384 kbps service (H0), 1920 kbps (H12), or ISDN-PRI. Also

useful for locating individual channels in drop-and-insert

applications. See Section 13 for timing details.

34 TLCLK O

Transmit Link Clock. 4 kHz to 20 kHz demand clock for the

TLINK input; controlled by TCR2. See Section 13 for timing

details.

35 TLINK I Transmit Link Data. If enabled, this pin will be sampled on the

falling edge of TCLK to insert the Sa bits See Section 13 for timing

details.

36 TSYNC I/O Transmit Sync. A pulse at this pin will establish either frame or

multiframe boundaries for the DS2153Q. Via TCR1.1, the DS2153Q

can be programmed to output either a frame or multiframe pulse at

this pin. See Section 13 for timing details.

37 DVDD - Digital Positive Supply. 5.0 volts. Should be tied to RVDD and

TVDD pins.

38 TCLK I

Transmit Clock. 2.048 MHz primary clock. Needed for proper

operation of the parallel control port.

39 TSER I Transmit Serial Data. Transmit NRZ serial data, sampled on t he

falling edge of TCLK.

40 TCHCLK O Transmit Channel Clock. 256 kHz clock which pulses high during

the LSB of each channel. Useful for parallel to serial conversion of

channel data. See Section 13 for timing details.

41

42

43

44

AD0

AD1

AD2

AD3

I/O Address/Data Bus. A 8-bit multiplexed address/data bus.

7 of 52

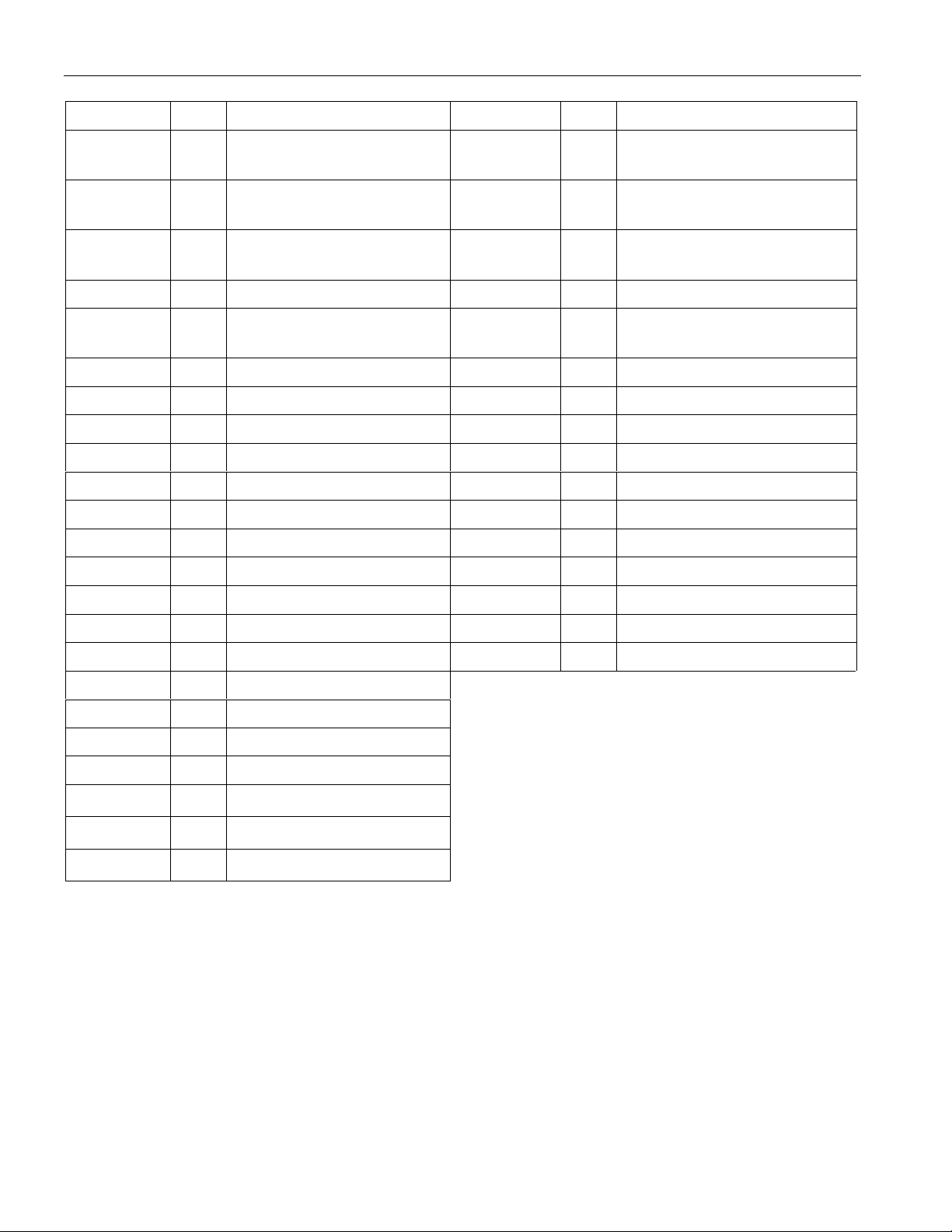

DS2153Q REGISTER MAP

ADDRESS R/W REGISTER NAME ADDRESS R/W REGISTER NAME

DS2153Q

00 R

01 R BPV or Code Violation

02 R CRC4 Count 1/FAS Error

03 R CRC4 Error Count 2 23 R/W Transmit Channel Blocking 2

04 R E-Bit Count 1/FAS Error

05 R E-Bit Count 2 25 R/W Transmit Channel Blocking 4

06 R Status 1 26 R/W Transmit Idle 1

07 R Status 2 27 R/W Transmit Idle 2

08 R/W Receive Information 28 R/W Transmit Idle 3

10 R/W Receive Control 1 29 R/W Transmit Idle 4

11 R/W Receive Control 2 2A R/W Transmit Idle Definition

12 R/W Transmit Control 1 2B R/W Receive Channel Blocking 1

13 R/W Transmit Control 2 2C R/W Receive Channel Blocking 2

BPV or Code Violation

Count 1

Count 2

Count 1

Count 2

20 R/W Transmit Align Frame

21 R/W Transmit Non-Align Frame

22 R/W Transmit Channel Blocking 1

24 R/W Transmit Channel Blocking 3

14 R/W Common Control 1 2E R/W Receive Channel Blocking 3

15 R/W Test 1 2E R/W Receive Channel Blocking 4

16 R/W Interrupt Mask 1 2F R Receive Align Frame

17 R/W Interrupt Mask 2

18 R/W Line Interface Control

19 R/W Test 2

1A R/W Common Control 2

1B R/W Common Control 3

1E R Synchronizer Status

1F R Receive Non-Align Frame

8 of 52

DS2153Q

ADDRESS R/W REGISTER NAME ADDRESS R/W REGISTER NAME

30 R Receive Signaling 1 40 R/W Transmit Signaling 1

31 R Receive Signaling 2 41 R/W Transmit Signaling 2

32 R Receive Signaling 3 42 R/W Transmit Signaling 3

33 R Receive Signaling 4 43 R/W Transmit Signaling 4

34 R Receive Signaling 5 44 R/W Transmit Signaling 5

35 R Receive Signaling 6 45 R/W Transmit Signaling 6

36 R Receive Signaling 7 46 R/W Transmit Signaling 7

37 R Receive Signaling 8 47 R/W Transmit Signaling 8

38 R Receive Signaling 9 48 R/W Transmit Signaling 9

39 R Receive Signaling 10 49 R/W Transmit Signaling 10

3A R Receive Signaling 11 4A R/W Transmit Signaling 11

3B R Receive Signaling 12 4B R/W Transmit Signaling 12

3C R Receive Signaling 13 4C R/W Transmit Signaling 13

3D R Receive Signaling 14 4D R/W Transmit Signaling 14

3E R Receive Signaling 15 4E R/W Transmit Signaling 15

3F R Receive Signaling 16 4F R/W Transmit Signaling 16

Note: the Test Registers 1 and 2 are used only by the factory; these registers must be cleared (set to all 0s)

on power-up initialization to insure proper operation.

2.0 PARALLEL PORT

The DS2153Q is controlled via a multiplexed bidirectional address/data bus by an external

microcontroller or microprocessor. The DS2153Q can operate with either Intel or Motorola bus timing

configurations. If the BTS pin is tied low, Intel timing will be selected; if tied high, Mot orola t iming will

be select ed. All Motorola bus signals are listed in parenthesis (). See the timing diagrams in the AC

Electrical Characteristics for more details. The multiplexed bus on the DS2153Q saves pins because the

address information and data information share the same signal paths. The addresses are presented to the

pins in the first portion of the bus cycle and data will be transferred on the pins during second portion of

the bus cycle. Addresses must be valid prior to the falling edge of ALE(AS), at which time the DS2153Q

latches the address from the AD0 to AD7 pins. Valid write data must be present and held stable during

the later portion of the DS

pulses. In a read cycle, the DS2153Q outputs a byte of data during the

WR

latter portion of the DS or RD pulses. The read cycle is terminated and the bus returns to a high

impedance state as RD transitions high in Intel timing or as DS transitions low in Motorola timing.

3.0 CONTROL AND TEST REGISTERS

The operation of the DS2153Q is configured via a set of seven registers. Typically, the control registers

are only accessed when the system is first powered up. Once the DS2153Q has been initialized, the

control registers will only need to be accessed when there is a change in the system configuration. There

are two Receive Control Register (RCR1 and RCR2), two Transmit Control Registers (TCR1 and TCR2),

and three Common Control Registers (CCR1, CCR2 and CCR3). Each of the seven registers are

described in this section.

The Test Registers at addresses 15 and 19 hex are used by the factory in testing the DS2153Q. On powerup, the Test Registers should be set to 00 hex in order for the DS2153Q to operate properly.

9 of 52

DS2153Q

RCR1: RECEIVE CONTROL REGISTER 1 (Address=10 Hex)

(MSB) (LSB)

RSMF RSM RSIO - - FRC SYNCE RESYNC

SYMBOL POSITION NAME AND DESCRIPTION

RSMF RCR1.7 RSYNC Multiframe Function. Only used if the RSYNC pin is

programmed in the multiframe mode (RCR1.6=1).

0=RSYNC outputs CAS multiframe boundaries

1=RSYNC outputs CRC4 multiframe boundaries

RSM RCR1.6 RSYNC Mode Select.

0=frame mode (see the timing in Section 13)

1=multiframe mode (see the timing in Section 13)

RSIO RCR1.5 RSYNC I/O Select.

0=RSYNC is an output (depends on RCR1.6)

1=RSYNC is an input (only valid if elastic store enabled) (note:

this bit must be set to 0 when RCR2.1=0)

- RCR1.4 Not Assigned. Should be set to 0 when written.

- RCR1.3 Not Assigned. Should be set to 0 when written.

FRC RCR1.2 Frame Resync Criteria.

0=resync if FAS received in error 3 consecutive times

1=resync if FAS or bit 2 of non-FAS is received in error 3

consecutive times

SYNCE RCR1.1 Sync Enable.

0=auto resync enabled

1=auto resync disabled

RESYNC RCR1.0 Resync. When toggled from low to high, a resync is initiated.

Must be cleared and set again for a subsequent resync.

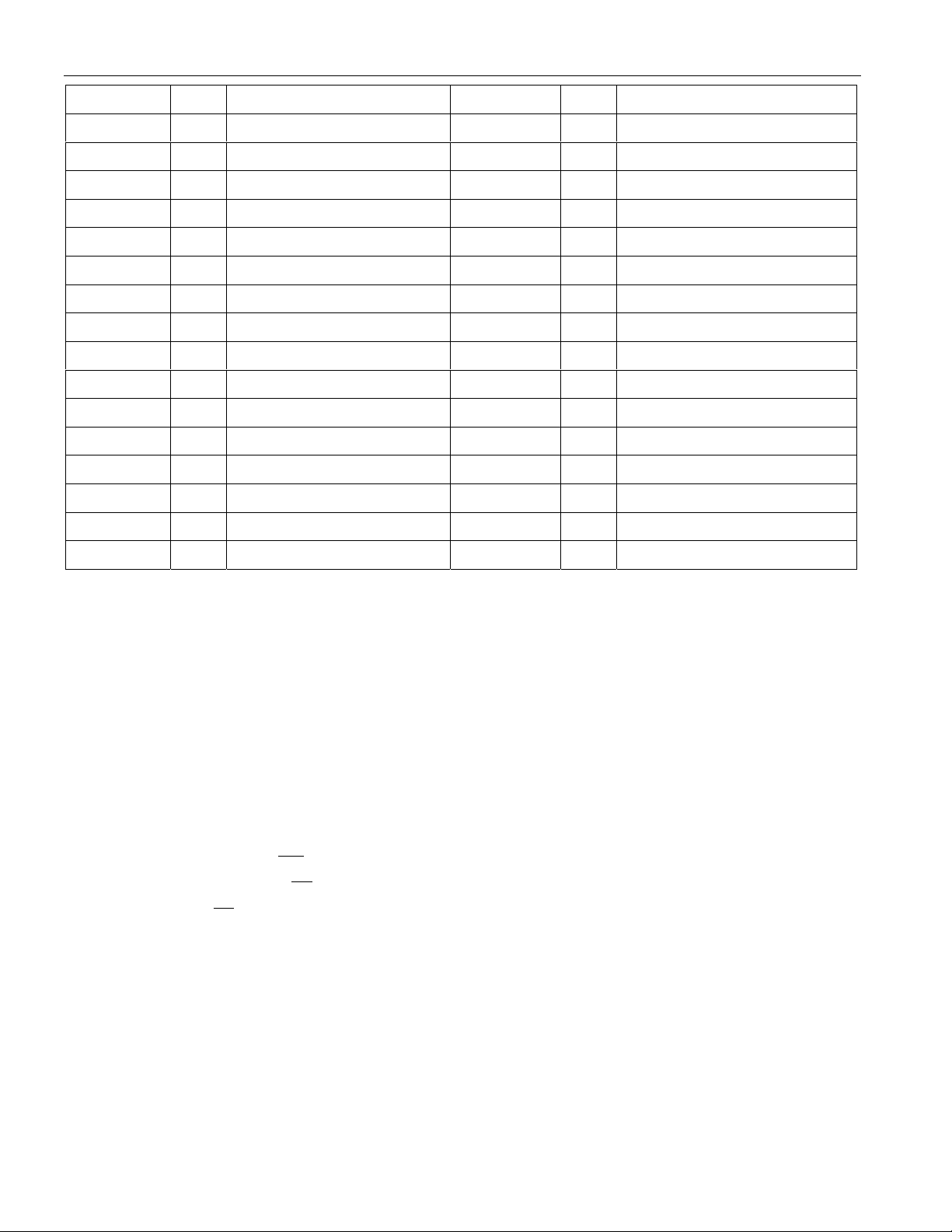

SYNC/RESYNC CRITERIA Table 3-1

FRAME OR

MULTIFRAME

LEVEL

FAS FAS present in frames N and N + 2, and

FAS not present in frame N + 1.

SYNC CRITERIA RESYNC CRITERIA

Three consecutive incorrect FAS

received.

Alternate (RCR1.2=1) the above

criteria is met or three consecutive

incorrect bit 2 of non-FAS received.

ITU

SPEC.

G.706

4.1.1

4.1.2

CRC4

CAS Valid MF alignment word found and

Two valid MF alignment words found

within 8 ms.

previous time slot 16 contains code

other than all 0s.

10 of 52

915 or more CRC4 code words out

of 1000 received in error.

Two consecutive MF alignment

words received in error.

G.706

4.2

4.3.2

G.732

5.2

DS2153Q

RCR2: RECEIVE CONTROL REGISTER 2 (Address=11 Hex)

(MSB) (LSB)

Sa8S Sa7S Sa6S Sa5S Sa4S RSCLKM RESE -

SYMBOL POSITION NAME AND DESCRIPTION

Sa8S RCR2.7 Sa8 Bit Select. Set to 1 to report the Sa8 bit at the RLINK pin;

set to 0 to not report the Sa8 bit.

Sa7S RCR2.6 Sa7 Bit Select. Set to 1to report the Sa7 bit at the RLINK pin;

set to 0 to not report the Sa7 bit.

Sa6S RCR2.5 Sa6 Bit Select. Set to 1 to report the Sa6 bit at the RLINK pin;

set to 0 to not report the Sa6 bit.

Sa5S RCR2.4 Sa5 Bit Select. Set to 1 to report the Sa5 bit at the RLINK pin;

set to 0 to not report the Sa5 bit.

Sa4S RCR2.3 Sa4 Bit Select. Set to 1 to report the Sa4 bit at the RLINK pin;

set to 0 to not report the Sa4 bit.

RSCLKM RCR2.2 Receive Side SYSCLK Mode Select.

0=if SYSCLK is 1.544 MHz

1=if SYSCLK is 2.048 MHz

RESE RCR2.1 Receive Side Elastic Store Enable.

0=elastic store is bypassed

1=elastic store is enabled

- RCR2.0 Not Assigned. Should be set to 0 when written.

11 of 52

DS2153Q

TCR1: TRANSMIT CONTROL REGISTER 1 (Address=12 Hex)

(MSB) (LSB)

- TFPT T16S TUA1 TSiS TSA1 TSM TSIO

SYMBOL POSITION NAME AND DESCRIPTION

- TCR1.7 Not Assigned. Should be set to 0 when written to.

TFPT TCR1.6 Transmit Timeslot 0 Pass Through.

0=FAS bits/Sa bits/Remote Alarm sourced internally from the

TAF and TNAF registers

1=FAS bits/Sa bits/Remote Alarm sourced from TSER

T16S TCR1.5 Transmit Timeslot 16 Data Select.

0=sample timeslot 16 at TSER pin

1=source timeslot 16 from TS1 to TS16 registers

TUA1 TCR1.4 Transmit Unframed All 1s.

0=transmit data normally

1=transmit an unframed all 1’s code at TPOS and TNEG

TSiS TCR1.3 Transmit International Bit Select.

0=sample Si bits at TSER pin

1=source Si bits from TAF and TNAF registers (in this mode,

TCR1.6 must be set to 0)

TSA1 TCR1.2 Transmit Signaling All 1s.

0=normal operation

1=force timeslot 16 in every frame to all 1s

TSM TCR1.1 TSYNC Mode Select.

0=frame mode (see the timing in Section 13)

1=CAS and CRC4 multiframe mode (see the timing in Section

13)

TSIO TCR1.0 TSYNC I/O Select.

0=TSYNC is an input

1=TSYNC is an output

Note: See Figure 13-9 for more details about how the Transmit Control Registers affect the operation of

the DS2153Q.

12 of 52

DS2153Q

TCR2: TRANSMIT CONTROL REGISTER 2 (Address=13 Hex)

(MSB) (LSB)

Sa8S Sa7S Sa6S Sa5S Sa4S - AEBE P16F

SYMBOL POSITION NAME AND DESCRIPTION

Sa8S TCR2.7 Sa8 Bit Select. Set to 1 to source the Sa8 bit from the TLINK

pin; set to 0 to not source the Sa8 bit.

Sa7S TCR2.6 Sa7 Bit Select. Set to 1 to source the Sa7 bit from the TLINK

pin; set to 0 to not source the Sa7 bit.

Sa6S TCR2.5 Sa6 Bit Select. Set to 1 to source the Sa6 bit from the TLINK

pin; set to 0 to not source the Sa6 bit.

Sa5S TCR2.4 Sa5 Bit Select. Set to 1 to source the Sa5 bit from the TLINK

pin; set to 0 to not source the Sa5 bit.

Sa4S TCR2.3 Sa4 Bit Select. Set to 1 to source the Sa4 bit from the TLINK

pin; set to 0 to not source the Sa4 bit.

- TCR2.2 Not Assigned. Should be set to 0 when written.

AEBE TCR2.1 Automatic E-Bit Enable.

0=E-bits not automatically set in the transmit direction

1=E-bits automatically set in the transmit direction

P16F TCR2.0 Function of Pin 16.

0=Receive Loss of Sync (RLOS)

1=Loss of Transmit Clock (LOTC)

13 of 52

DS2153Q

CCR1: COMMON CONTROL REGISTER 1 (Address=14 Hex)

(MSB) (LSB)

FLB THDB3 TG802 TCRC4 RSM RHDB3 RG802 RCRC4

SYMBOL POSITION NAME AND DESCRIPTION

FLB CCR1.7 Framer Loopback.

0=loopback disabled

1=loopback enabled

THDB3 CCR1.6 Transmit HDB3 Enable.

0=HDB3 disabled

1=HDB3 enabled

TG802 CCR1.5 Transmit G.802 Enable. See Section 13 for details.

0=do not force TCHBLK high during bit 1 of timeslot 26

1=force TCHBLK high during bit 1 of timeslot 26

TCRC4 CCR1.4 Transmit CRC4 Enable.

0=CRC4 disabled

1=CRC4 enabled

RSM CCR1.3 Receive Signaling Mode Select.

0=CAS signaling mode

1=CCS signaling mode

RHDB3 CCR1.2 Receive HDB3 Enable.

0=HDB3 disabled

1=HDB3 enabled

RG802 CCR1.1 Receive G.802 Enable. See Section 13 for details.

0=do not force RCHBLK high during bit 1 of timeslot 26

1=force RCHBLK high during bit 1 of timeslot 26

RCRC4 CCR1.0 Receive CRC4 Enable.

0=CRC4 disabled

1=CRC4 enabled

FRAMER LOOPBACK

When CCR1.7 is set to a 1, the DS2153Q will enter a Framer LoopBack (FLB) mode. This loopback is

useful in testing and debugging applications. In FLB, the DS2153Q will loop data from the transmit side

back to the receive side. When FLB is enabled, the following will occur:

1. data will be transmitted as normal at TTIP and TRING

2. data off the E1 line at RTIP and RRING will be ignored

3. the RCLK output will be replaced with the TCLK input.

14 of 52

DS2153Q

CCR2: COMMON CONTROL REGISTER 2 (Address=1A Hex)

(MSB) (LSB)

ECUS VCRFS AAIS ARA RSERC LOTCMC RLB LLB

SYMBOL POSITION NAME AND DESCRIPTION

ECUS CCR2.7 Error Counter Update Select.

0=update error counters once a second

1=update error counters every 62.5 ms (500 frames)

VCRFS CCR2.6 VCR Function Select.

0=count BiPolar Violations (BPVs)

1=count Code Violations (CVs)

AAIS CCR2.5 Automatic AIS Generation.

0=disabled

1=enabled

ARA CCR2.4 Automatic Remote Alarm Generation.

0=disabled

1=enabled

RSERC CCR2.3 RSER Control.

0=allow RSER to output data as received under all conditions

1=force RSER to 1 under loss of frame alignment conditions

LOTCMC CCR2.2 Loss of Transmit Clock Mux Control. Determines whether the

transmit side formatter should switch to the ever present RCLK

if the TCLK should fail to transition (see Figure 1.1).

0=do not switch to RCLK if TCLK stops

1=switch to RCLK if TCLK stops

RLB CCR2.1 Remote Loopback.

0=loopback disabled

1=loopback enabled

LLB CCR2.0 Local Loopback.

0=loopback disabled

1=loopback enabled

REMOTE LOOPBACK

When CCR2.1 is set to a 1, the DS2153Q will be forced into Remote LoopBack (RLB). In this loopback,

data recovered off of the E1 line from the RTIP and RRING pins will be transmitted back onto the E1 line

(with any BPV’s that might have occurred intact) via the TTIP and TRING pins. Data will continue to

pass through the receive side of the DS2153Q as it would normally and the data at the TSER pin will be

ignored. Data in this loopback will pass through the jitter attenuator. Please see Figure 1.1 for more

details.

15 of 52

DS2153Q

LOCAL LOOPBACK

When CCR2.0 is set to a 1, the DS2153Q will be forced into Local LoopBack (LLB). In this loopback,

data will continue to be transmitted as normal through the transmit side of the SCT. Data being received

at RTIP and RRING will be replaced with the data being transmitted. Data in this loopback will pass

through the jitter attenuator. Please see Figure 1.1 for more details.

AUTOMATIC ALARM GENERATION

When either CCR2.4 or CCR2.5 is set to 1, the DS2153Q monitors the receive side to determine if any of

the following conditions are present: loss of receive frame synchronization, AIS alarm (all 1s) reception,

or loss of receive carrier (or signal). If any one (or more) of the above conditions is present, then the

DS2151Q will either force an AIS alarm (if CCR2.5=1) or a Remote Alarm (CCR2.4=1) to be transmitted

via the TTIP and TRING pins. It is an illegal state to have both CCR2.4 and CCR2.5 set to 1 at the same

time.

CCR3: COMMON CONTROL REGISTER 3 (Address=1B Hex)

(MSB) (LSB)

TESE TCBFS TIRFS ESR LIRST - TSCLKM -

SYMBOL POSITION NAME AND DESCRIPTION

TESE CCR3.7

TCBFS CCR3.6

TIRFS CCR3.5 Transmit Idle Registers (TIR) Function Select.

ESR CCR3.4 Elastic Stores Reset. Setting this bit from a 1 to a 0 will force

LIRST CCR3.3 Line Interface Reset. Setting this bit from a 0 to a 1 will initiate

Transmit Elastic Store Enable.

0 = elastic store is disabled

1 = elastic store is enabled

Transmit Channel Blocking Registers (TCBR) Function

Select.

0=TCBRs define the operation of the TCHBLK output pin

1=TCBRs define which signaling bits are to be inserted

0=TIRs define in which channels to insert idle code

1=TIRs define in which channels to insert data from RSER

the elastic stores to a known depth. Should be toggled after

SYSCLK has been applied and is stable. Must be set and cleared

again for a subsequent reset. Do not leave this bit set high.

an internal reset that affects the slicer, AGC, clock recovery state

machine, and jitter attenuator. Normally this bit is only toggled

on power-up. Must be cleared and set again for a subsequent

reset.

- CCR3.2 Not Assigned. Should be set to 0 when written.

TSCLKM CCR3.1 Transmit Backplane Clock Select. Must be set like RCR2.2.

0 = 1.544 MHz

1 = 2.048 MHz

- CCR3.0 Not Assigned. Should be set to 0 when written.

16 of 52

Loading...

Loading...