Dallas Semiconductor DS21372TN, DS21372T Datasheet

www.dalsemi.com

A

DS21372

FEATURES

Generates/detects digital bit patterns for

analyzing, evaluating and troubleshooting

digital communications systems

Operates at speeds from DC to 20 MHz

Programmable polynomial length and

feedback taps for generation of any other

pseudorandom pattern up to 32 bits in length

including: 2

32

and 2

Programmable user-defined pattern and

length for generation of any repetitive pattern

up to 32 bits in length

Large 32-bit error count and bit count

registers

Software programmable bit error insertion

Fully independent transmit and receive

sections

8-bit parallel control port

Detects test patterns with bit error rates up to

-2

10

6

-1, 29-1, 211-1, 215-1, 220-1, 223-1,

-1

PIN ASSIGNMENT

TDATA

TDIS

TCLK

VSS

VDD

RCLK

RDIS

RDATA

TL

AD0

AD1

TEST

VSS

AD2

AD3

AD4

32 31 30 29 28 27 26 25

1

2

3

4

DS21372

32-PIN TQFP

5

6

7

8

9 10 11 12 13 14 15 16

AD5

AD6

AD7

BTS

VSS

VDD

24

23

22

21

20

19

18

17

RD(DS)

RL

RLOS

LC

VSS

VDD

INT

WR(R/W)

LE(AS)

CS

ORDERING INFORMATION

DS21372T (00 C to 700 C)

DS21372TN (-400 C to +850 C)

DESCRIPTION

The DS21372 Bit Error Rate Tester (BERT) is a software programmable test pattern generator, receiver,

and analyzer capable of meeting the most stringent error performance requirements of digital

transmission facilities. Two categories of test pattern generation (Pseudo-random and Repetitive)

conform to CCITT/ITU O.151, O.152, O.153, and O.161 standards. The DS21372 operates at clock rates

ranging from DC to 20 MHz. This wide range of operating frequency allows the DS21372 to be used in

existing and future test equipment, transmission facilities, switching equipment, multiplexers, DACs,

Routers, Bridges, CSUs, DSUs, and CPE equipment.

The DS21372 user-programmable pattern registers provide the unique ability to generate loopback

patterns required for T1, Fractional-T1, Smart Jack, and other test procedures. Hence the DS21372 can

initiate the loopback, run the test, check for errors, and finally deactivate the loopback.

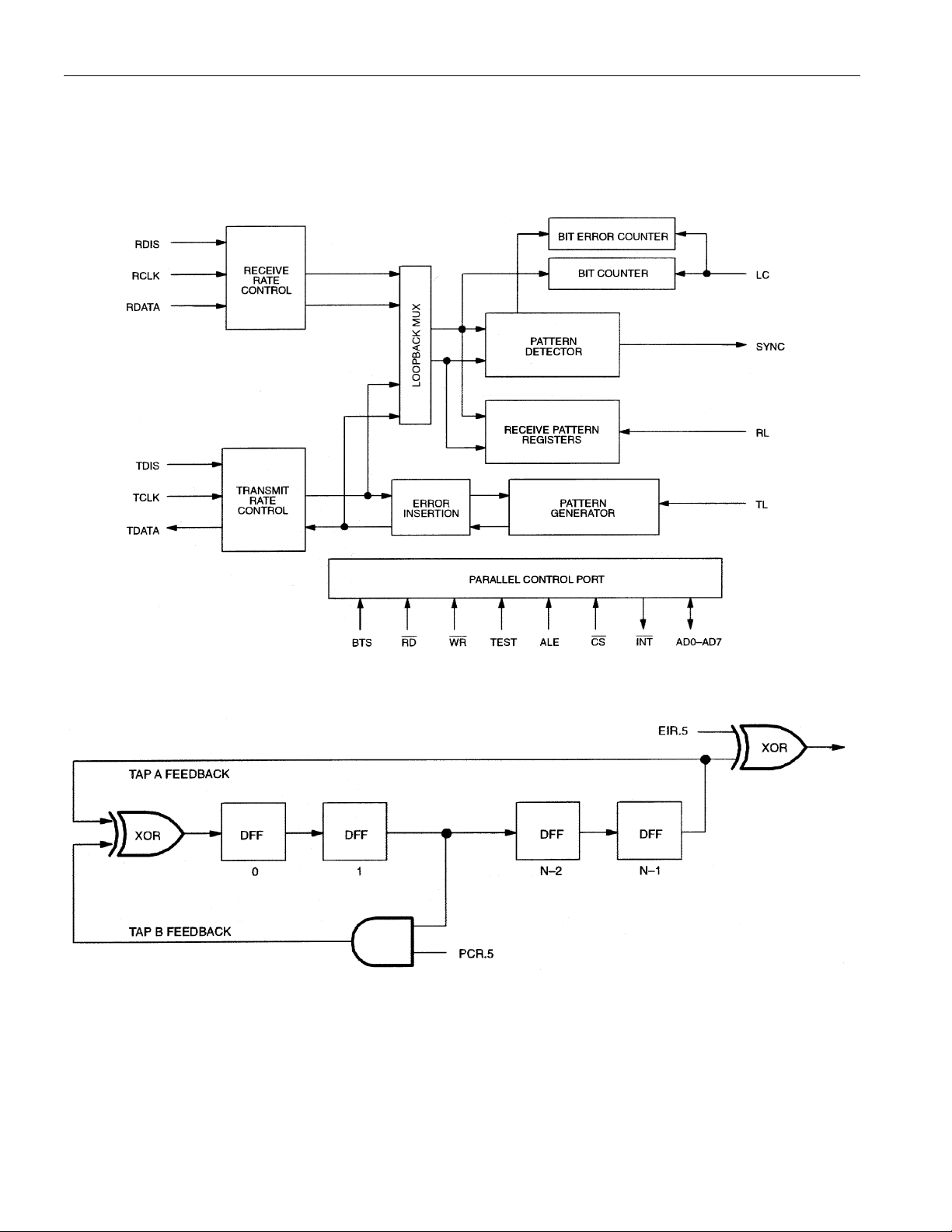

The DS21372 consists of four functional blocks: the pattern generator, pattern detector, error counte r, and

control interface. The DS21372 can be programmed to generate any pseudorandom pattern with length up

32

-1 bits (see Table 5, Note 9) or any user programmable bit pattern from 1 to 32 bits in length. Logic

to 2

inputs can be used to configure the DS21372 for applications requiring gap clocking such as FractionalT1, Switched-56, DDS, normal framing requirements, and per-channel test procedures. In addition, the

DS21372 can insert single or 10

-1

to 10-7 bit errors to verify equipment operation and connectivity.

1 of 21 050400

DS21372

1. GENERAL OPERATION

1.1 PATTERN GENERATION

The DS21372 is programmed to generate a particular test pattern by programming the following registers:

- Pattern Set Registers (PSR)

- Pattern Length Register (PLR)

- Polynomial Tap Register (PTR)

- Pattern Control Register (PCR)

- Error Insertion Register (EIR)

Please see Tables 4 and 5 for examples of how to program these registers in order to generate some

standard test patterns. Once these registers are programmed, the user will then toggle the TL (Transmit

Load) bit or pin to load the pattern into the onboard pattern generation circuitry and the pattern will begin

appearing at the TDATA pin.

1.2 PATTERN SYNCHRONIZATION

The DS21372 expects to receive the same pattern that it transmitted. The s ynchronizer examines the data

at RDATA and looks for characteristics of the transmitted pattern. The user can control the onboard

synchronizer with the Sync Enable and Resync bits in the Pattern Control Register.

In pseudorandom mode, the received pattern is tested to see if it fits the polynomial generator as defined

in the transmit side. For pseudorandom patterns, only the original pattern and an all ones pattern or an all

0s pattern will satisfy this test. Synchronization in pseudorandom pattern mode should be qualified by

using the RA1 and RA0 indicators in the Status Register. Synchronization is declared after 34 + n bits are

received without error, where n is the exponent in the pol ynomial from Table 4. Once in synchronization

(SR.0 = 1) any deviation from this pattern will be counted by the Bit Error Count Register.

In repetitive pattern mode a received pattern of the same length as being transmitted will satisfy this test.

Synchronization in repetitive pattern mode should be qualified by using the RA1 and RA0 indicators in

the Status Register and examining the Pattern Receive Register (PRR0--3). See section 10 for an

explanation of the Pattern Receive Register. Once in synchronization (SR.0 = 1) an y deviation from this

pattern will be counted by the Bit Error Count Register.

1.3 BER CALCULATION

Users can calculate the actual Bit Error Rate (BER) of the digital communications channel by reading the

bit error count out of the Bit Error Count Register (BECR) and reading the bit count out of the Bit Count

Register (BCR) and then dividing the BECR value with the BCR value. The user has total control over

the integration period of the measurement. The LC (Load Count) bit or pin is used to set the integration

period.

1.4 GENERATING ERRORS

Via the Error Insertion Register (EIR), the user can intentionally inject a particular error rate into the

transmitted data stream. Injecting errors allows users to stress communication links and to check the

functionality of error monitoring equipment along the path.

2 of 21

DS21372

1.5 POWER-UP SEQUENCE

On power-up, the registers in the DS21372 will be in a random state. The user must program all the

internal registers to a known state before proper operation can be insured.

DS21372 FUNCTIONAL BLOCK DIAGRAM Figure 1

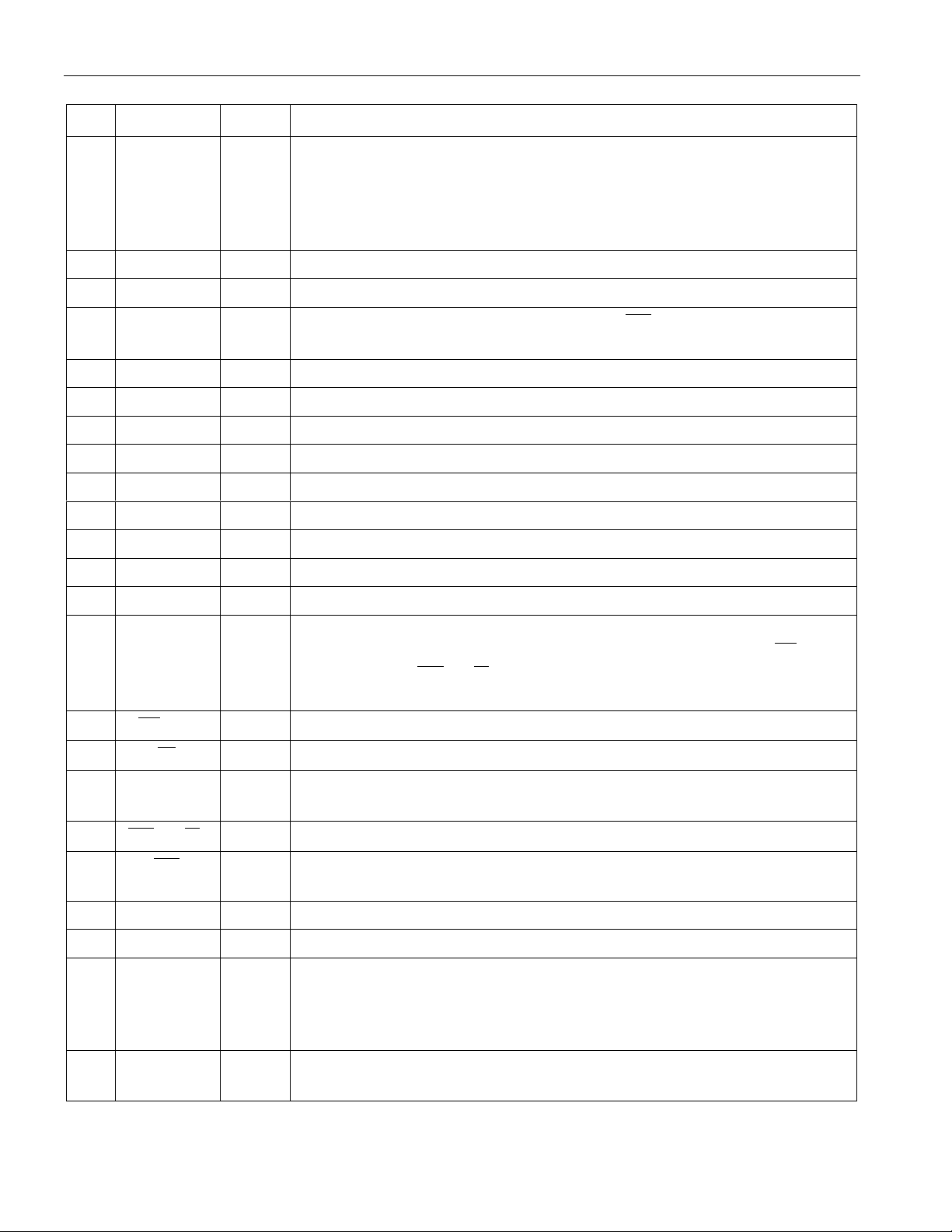

DS21372 PATTERN GENERATION BLOCK DIAGRAM Figure 2

NOTES:

1. Tap A always equals length (N-1) of pseudorandom or repetitive pattern.

2. Tab B can be programmed to any feedback tap for pseudorandom pattern generation.

3 of 21

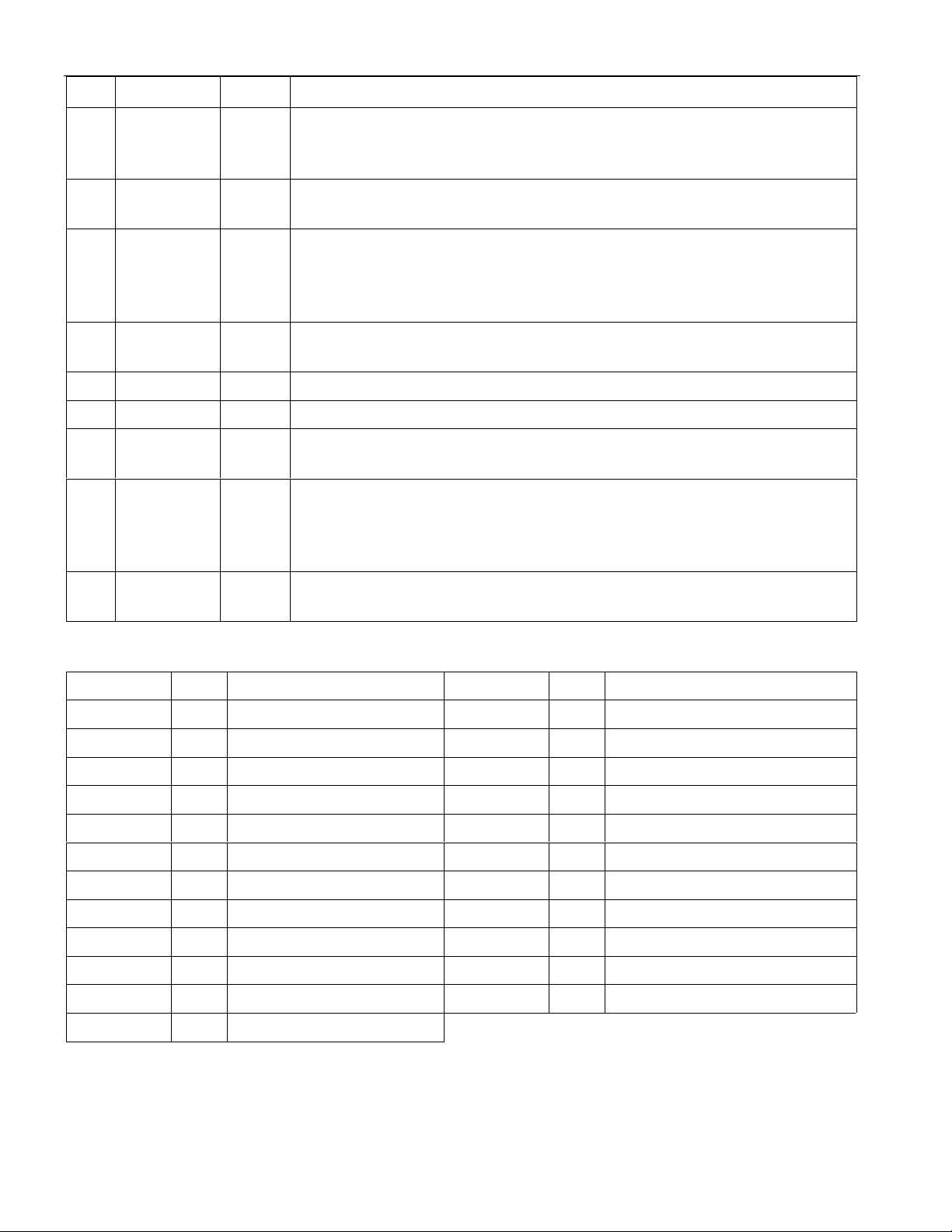

DETAILED PIN DESCRIPTION Table 1

PIN SYMBOL TYPE DESCRIPTION

1TL ITransmit Load. A positive-going edge loads the pattern generator with

the contents of the Pattern Set Registers. The MSB of the repetitive or

pseudorandom pattern appears at TDATA after the third positive edge of

TCLK from asserting TL. TL is logically OR’ed with PCR.7 and should

be tied to VSS if not used. See Figure 8 for timing information.

2 AD0 I/O Data Bus. An 8-bit multiplexed address/data bus.

3 AD1 I/O Data Bus. An 8-bit multiplexed address/data bus.

DS21372

4 TEST I

Test. Set high to 3-state all output pins ( INT , ADx, TDATA, RLOS).

Should be tied to VSS to enable all outputs.

5VSS- Signal Ground. 0.0 volts. Should be tied to local ground plane.

6 AD2 I/O Data Bus. An 8-bit multiplexed address/data bus.

7 AD3 I/O Data Bus. An 8-bit multiplexed address/data bus.

8 AD4 I/O Data Bus. An 8-bit multiplexed address/data bus.

9 AD5 I/O Data Bus. An 8-bit multiplexed address/data bus.

10 AD6 I/O Data Bus. An 8-bit multiplexed address/data bus.

11 AD7 I/O Data Bus. An 8-bit multiplexed address/data bus.

12 V

13 V

SS

DD

- Signal Ground. 0.0 volts. Should be tied to local ground plane.

- Positive Supply. 3.3 volts.

14 BTS I Bus Type Select. Strap high to select Motorola bus timing; strap low to

select Intel bus timing. This pin controls the function of the RD (DS),

ALE(AS), and WR (R/ W ) pins. If BTS = 1, then these pins assume the

function listed in parenthesis ().

15

16

RD (DS)

CS

I

Read Input (Data Strobe).

I Chip Select. Must be low to read or write the port.

17 ALE(AS) I Address Latch Enable (Address Strobe). A positive going edge serves

to demultiplex the bus.

18

19

WR (R/ W )

INT

I

Write Input (Read/Write).

O Alarm Interrupt. Flags host controller during conditions defined in

Status Register. Active low, open drain output.

20 V

21 V

DD

SS

22 LC I

- Positive Supply. 3.3 volts.

- Signal Ground. 0.0 volts. Should be tied to local ground plane.

Load Count. A positive-going edge latches the current bit and bit error

count into the user accessible BCR and BECR registers and clears the

internal count registers. LC is logically OR’ed with control bit PCR.4.

Should be tied to VSS if not used.

23 RLOS O Receive Loss Of Sync. Indicates the real time status of the receive

synchronizer. Active high output.

4 of 21

DS21372

PIN SYMBOL TYPE DESCRIPTION

24 RL I Receive Load. A positive-going edge loads the previous 32 bits of data

received at RDATA into the Pattern Receive Registers. RL is logicall y

OR’ed with control bit PCR.3. Should be tied to VSS if not used.

25 RDATA I

Receive Data. Received NRZ serial data, sampled on the rising edge of

RCLK.

26 RDIS I Receive Disable. Set high to prevent the data at RDATA from being

sampled. Set low to allow bits at RDATA to be sampled. Should be tied

to VSS if not used. See Figure 6 for timing information. All receive side

operations are disabled when RDIS is high.

27 RCLK I

Receive Clock. Input clock from transmission link. 0 to 20 MHz. Can

be a gapped clock. Fully independent from TCLK.

28 V

29 V

DD

SS

- Positive Supply. 3.3 volts.

- Signal Ground. 0.0 volts. Should be tied to local ground plane.

30 TCLK I Transmit Clock. Transmit demand clock. 0 to 20 MHz. Can be a

gapped clock. Fully independent of RCLK.

31 TDIS I Transmit Disable. Set high to hold the current bit being transmitted at

TDATA. Set low to allow the next bit to appear at TD ATA. Should be

tied to VSS if not used. See Figure 7 for timing information. All transmit

side operations are disabled when TDIS is high.

32 TDATA O Transmit Data. Transmit NRZ serial data, updated on the rising edge of

TCLK.

DS21372 REGISTER MAP Table 2

ADDRESS R/W REGISTER NAME ADDRESS R/W REGISTER NAME

00 R/W Pattern Set Register 3. 0C R Bit Error Counter Register 3.

01 R/W Pattern Set Register 2. 0D R Bit Error Counter Register 2.

02 R/W Pattern Set Register 1. 0E R Bit Error Counter Register 1.

03 R/W Pattern Set Register 0. 0F R Bit Error Counter Register 0.

04 R/W Pattern Length Register. 10 R Pattern Receive Register 3.

05 R/W Polynomial Tap Register. 11 R Pattern Receive Register 2.

06 R/W Pattern Control Register. 12 R Pattern Receive Register 1.

07 R/W Error Insert Register. 13 R Pattern Receive Register 0.

08 R Bit Counter Register 3. 14 R Status Register.

09 R Bit Counter Register 2. 15 R/W Interrupt Mask Register.

0A R Bit Counter Register 1. 1C R/W Test Register (see note 1)

0B R Bit Counter Register 0.

NOTE:

1. The Test Register must be set to 00 hex to insure proper operation of the DS21372.

5 of 21

DS21372

2. PARALLEL CONTROL INTERFACE

The DS21372 is controlled via a multiplexed bi-directional address/data bus by an external

microcontroller or microprocessor. The DS21372 can operate with either Intel or Motorola bus timing

configurations. If the BTS pin is tied low, Intel timing will be selected; if tied high, Motorola timing will

be selected. All Motorola bus signals are listed in parenthesis (). See the timing diagrams in the A.C.

Electrical Characteristics for more details. The multiplexed bus on the DS21372 saves pins because the

address information and data information share the same signal paths. The address es are presented to the

pins in the first portion of the bus cycle and data will be transferred on the pins during second portion of

the bus cycle. Addresses must be valid prior to the falling edge of ALE(AS), at which time the DS21372

latches the address from the AD0 to AD7 pins. Valid write data must be present and held stable during

the later portion of the DS or WR pulses. In a read cycle, the DS21372 outputs a byte of data during the

latter portion of the DS or RD pulses. The read cycle is terminated and the bus returns to a high

impedance state as RD transitions high in Intel timing or as DS transitions low in Motorola timing. The

DS21372 can also be easily connected to non-multiplexed buses. RCLK and TCLK are used to update

counters and load transmit and receive pattern registers. At slow clock rates, sufficient time must be

allowed for these port operations.

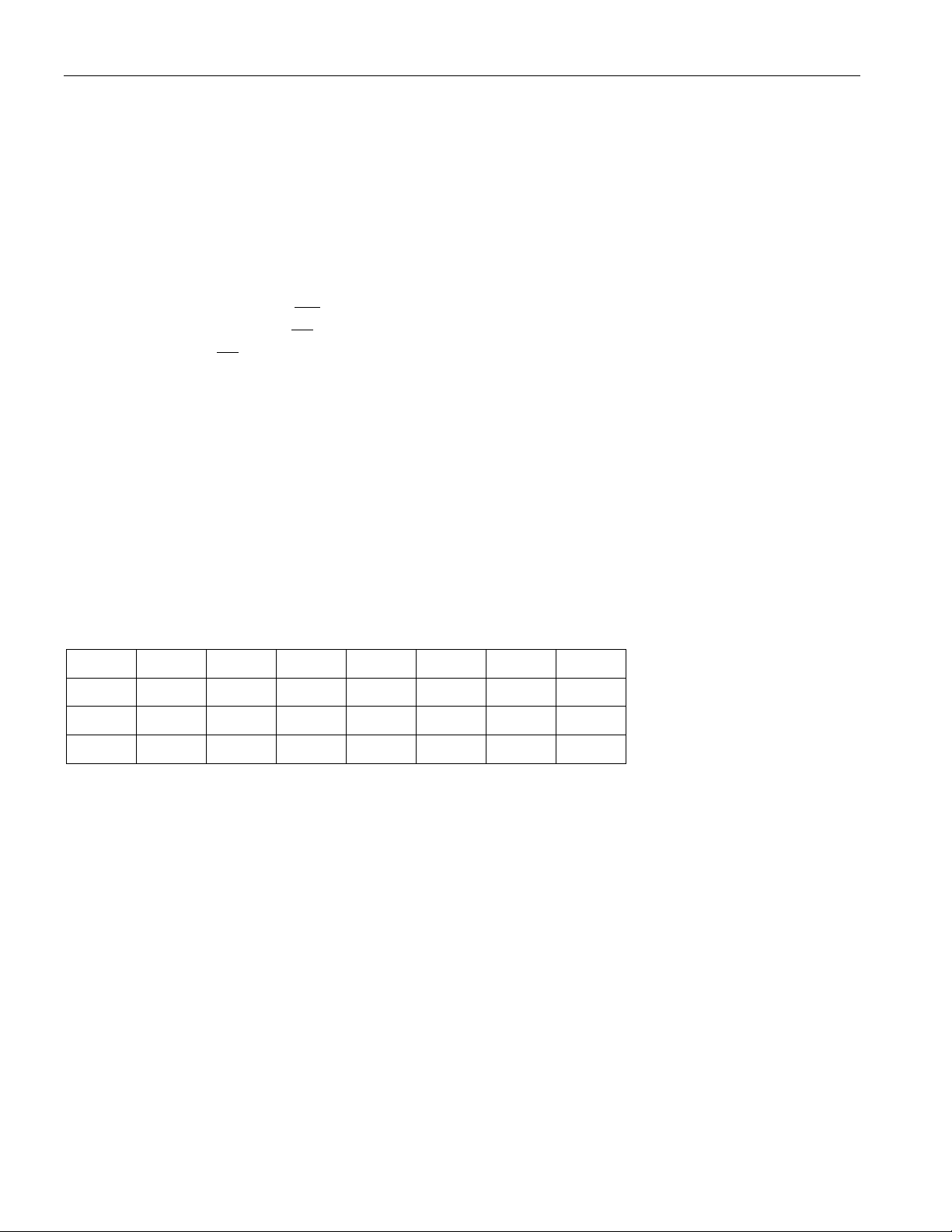

3. PATTERN SET REGISTERS

The Pattern Set Registers (PSR) are loaded each time a new pattern (whether it be pseudorandom or

repetitive) is to be generated. When a pseudorandom pattern is generated, all four PSRs must be loaded

with FF Hex. When a repetitive pattern is to be created, the four PSRs are loaded with the pattern that is

to be repeated. Please see Tables 4 and 5 for some programming examples.

PATTERN SET REGISTERS

(MSB) (LSB)

PS31 PS30 PS29 PS28 PS27 PS26 PS25 PS24 PSR3 (addr.=00 Hex)

PS23 PS22 PS21 PS20 PS19 PS18 PS17 PS16 PSR2 (addr.=01 Hex)

PS15 PS14 PS13 PS12 PS11 PS10 PS9 PS8 PSR1 (addr.=02 Hex)

PS7 PS6 PS5 PS4 PS3 PS2 PS1 PS0 PSR0 (addr.=03 Hex)

4. PATTERN LENGTH REGISTER

Length Bits LB4 to LB0 determine the length of the pseudorandom polynomial or programmable

repetitive pattern that is generated and detected. With the pseudorandom patterns, the “Tap A” fe edback

position of the pattern generator is always equal to the value in the Pattern Length Register (PLR). Please

refer to Figure 2 for a block diagram of the pattern generator and to Tables 4 and 5 for some

programming examples.

6 of 21

DS21372

PLR: PATTERN LENGTH REGISTER (ADDRESS=04 HEX)

(MSB) (LSB)

- - - LB4 LB3 LB2 LB1 LB0

SYMBOL POSITION NAME AND DESCRIPTION

- PLR1.7 Not Assigned. Should be set to 0 when written to.

- PLR1.6 Not Assigned. Should be set to 0 when written to.

- PLR1.5 Not Assigned. Should be set to 0 when written to.

LB4 PLR1.4

LB3 PLR1.3

LB2 PLR1.2

LB1 PLR1.1

LB0 PLR1.0

Length Bit 4.

Length Bit 3.

Length Bit 2.

Length Bit 1.

Length Bit 0.

5. POLYNOMIAL TAP REGISTER

Polynomial Tap Bits PT4 - PT0 determine the feedback position of Tap B connected to the XOR input of

the pattern generator. Feedback Tap B provides one of two feedback paths within the pattern generator.

Please refer to Figure 2 for a block diagram of the pattern generator and to Tables 4 and 5 for register

programming examples.

PTR: POLYNOMIAL TAP REGISTER (ADDRESS=05 HEX)

(MSB) (LSB)

- - - PT4 PT3 PT2 PT1 PT0

SYMBOL POSITION NAME AND DESCRIPTION

-PTR.7Not Assigned. Should be set to 0 when written to.

-PTR.6Not Assigned. Should be set to 0 when written to.

-PTR.5Not Assigned. Should be set to 0 when written to.

PT4 PTR.4

PT3 PTR.3

PT2 PTR.2

PT1 PTR.1

PT0 PTR.0

Polynomial Tap Bit 4.

Polynomial Tap Bit 3.

Polynomial Tap Bit 2.

Polynomial Tap Bit 1.

Polynomial Tap Bit 0.

7 of 21

Loading...

Loading...