dallas semiconductor DS1963S service manual

查询DS2050W供应商

www.iButton.com

特性

4096 位可读/写非易失(NV)存储器,分

为 16 页,每页 256位

8 个存储页分别具有独立的 64 位密钥和

32 位只读、不滚动、页写计数器

密钥只可写入,并具有自己独立的写循环

计数器

片内 512 位 SHA-1 (FIPS 180-1,ISO/IEC

10118-3) 引擎可计算 160 位信息鉴定码

(MAC),生成页密钥

器件可作为漫游

iButton

®

或主机的协处理

器使用

256 位暂存器保证传送数据的完整性

片内 16 位 CRC 发生器确保数据正确传送

高速模式提升通信速度至 125kbps

工作温度范围-20°C 至+85°C

数据保留 10 年以上

SHA

DS1963S

iButton

坚固的不锈钢外壳,表面铭刻注册码,可

抵御恶劣工作环境

便于安装,可用自粘胶、固定凸缘、或在

边缘嵌装箍环等办法安装

当阅读器首次上电时进行在线检测应答

符合 UL#913 (第四版)标准;本质安全器

件,经过 I 级,1 区,A、B、C、D 组指

定区域的认证(申请中)

F5 MicroCan

5.89

0.51

®

16.25

51 18

000000FBC52B

1-Wire

®

®

17.35

iButton的共性

唯一的、经工厂光刻和测试的 64 位注册

码(8 位家族码 + 48 位序列码 + 8 位 CRC

校验码)保证绝对可溯性,因为没有任何

两个器件是相同的

MicroLAN 多点控制器

通过瞬间接触完成数字识别和信息传递

基于芯片的数据载体实现信息的紧凑存储

可附着在目标物体上读取数据

通过一条信号线与主机通信,速率达

15.4kbps,极为经济

®

标准 16mm直径,使用 1-Wire

证与其它

iButton系列器件兼容

协议,保

钮扣外形,可自动对准杯状探头

iButton 和 1-Wire 是 Dallas Semiconductor

本文是Maxim正式英文资料的译文,Maxim不对翻译中存在的差异或由此产生的错误负责。请注意译文中可能存在文字组织或翻译

错误,如需确认任何词语的准确性,请参考Maxim提供的英文版资料。

索取免费样品和最新版的数据资料,请访问 Maxim 的主页:www.maxim-ic.com.cn。

1 of 37 021704

的注册商标。

IO GND

图中尺寸均以毫米为单位

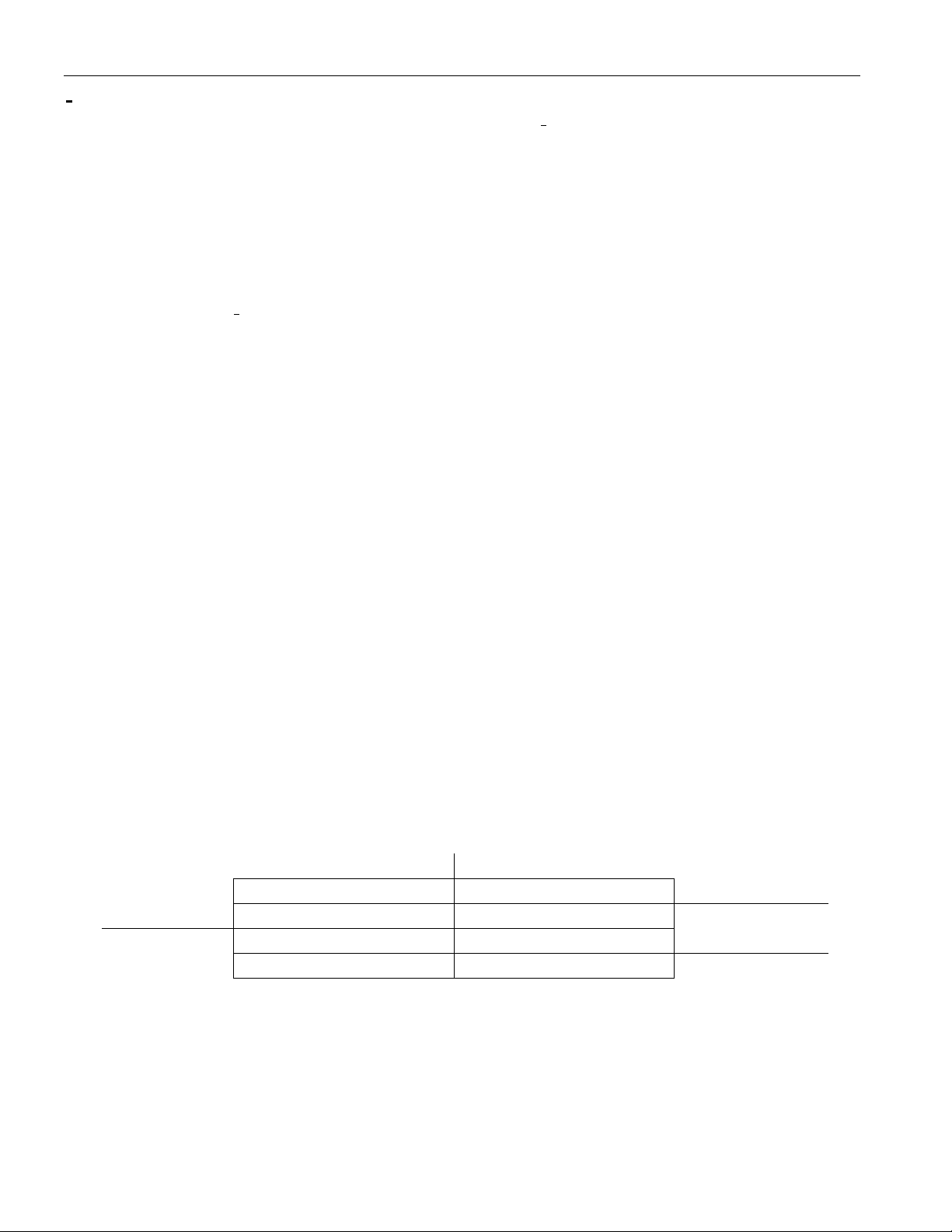

定购信息

DS1963S F5 MicroCan

相关产品

DS9096P 自粘胶垫

DS9101 多用途夹

DS9093RA 安装固定环

DS9093A 链扣

DS9092

iButton读取探头

DS1963S

iButton 概述

DS1963S是一个带有SHA-1 功能和 4k位读/写数据区的金融iButton,通过简单硬件就可完成数据读

写。它的非易失存储器可根据需要建立公用数据和器件持有者或应用环境的私有数据微数据库。

其片内的 512 位SHA-1 引擎可根据器件内部存储的信息计算 160 位信息鉴定码(MAC)。数据通

过 1-Wire协议串行传送,仅需一条信号线和地线。采用TMEX文件格式(参见应用笔记 114),

单一DS1963S可被用于四个相互独立的应用,例如作为安全电子钱包为本地运输系统、付费电

话、停车管理、售货机等应用提供电子支付手段。另外,DS1963S也可作为一个协处理器协助主

机计算签名,以便在消费结束后,利用一个安全签名密钥,将新的余额写回漫游装置。

与其他基于SRAM的iButton一样,DS1963S也具有一个附加的存储区域,称为暂存器,在对主存

储器进行写操作时可作为一个缓冲器使用。DS1963 的暂存器也被用于向SHA-1 引擎提供数据,

或者接收/比较信息鉴定码。

在进行写操作时,数据首先被写入暂存器,并可以从这里读回数据进行核对。数据经过核对之

后,一条 Copy Scratchpad(复制暂存器)命令就可将数据传送到主存储器。这种处理方式保证了

在不可靠接触条件下写入主存储器数据的完整性。

每个 DS1963S 都在出厂时都写入了一个 64 位 ROM 注册码,这个唯一的 ID 确保每个器件都绝对

可溯。坚固耐用的 MicroCan 封装保证器件具有很高的防污、防潮和抗冲击性能。DS1963S 紧凑

的钮扣外形可自动对准与之相配套的读写头,使用者操作起来非常容易。各种附件使 DS1963S 可

以安装在塑料钥匙扣、证件和印制电路板等各种物体的表面上。

安全性

使用移动数据载体的系统主要由 3 部分组成:1)读、写数据载体的主机;2)数据载体(“从设

备”);3)系统的使用者(使用者有可能会试图篡改数据或假造数据载体)。DS1963S 专门设

计用于抵御对所有这些环节的攻击,并且没有使用任何有产权限制的算法。该器件的安全性基于

安全散列标准 SHA-1(Secure Hash Standard),相关文档参见 http://www.itl.nist.gov/div897/pubs/

fip180-1.htm。

下表以真值表的形式列出了各种可能的非暴力攻击手段。表中涉及的注解解释了防范这些攻击的

典型方法。关于其中所用到的功能的完整描述详见“存储器和 SHA 功能命令”章节及 SHA-1 算

法和信息格式。

授权 见注释 2 见注释 2、3 假从机

主机 正常操作 见注释 3 可信

非授权 见注释 1 不考虑 从机

主机 不考虑 不考虑 假从机

可信数据 伪造数据

2 of 37

DS1963S

注释 1: 基于保存在漫游数据载体存储页中的系统级密钥、器件 ROM注册号和用户选定的用户密

码,器件可被用于主机的鉴定。

注释 2: 为了确认从设备的可信度,主机向暂存器写入一个 3 字节的“质询”,然后发出命令令

其针对质询、某存储页的数据、页号、该页的写循环计数器、设备的 ROM 注册码、以及

和该页相关的密钥计算 SHA-1 MAC。通过每次变换由从机读出的质询,主机可以确认从

机是否拥有正确的密钥,并在要求的时间内完成 SHA 计算。

注释 3: 如果数据在从机内被授权主机“签署”,伪造数据就能被发现。签署时需要计算一个

160 位的 SHA-1 MAC,计算过程涉及被保护数据、数据所在页的写循环计数器、存储数

据的从设备的 ROM ID,以及任何只有授权主机知晓的专用密钥。MAC 和应用数据(例

如货币数值和交易 ID 号)一同存放在特定的存储页。要验证数据的可信度,主机可重复

签署过程。任何数据,循环计数器,数据载体的改变或使用无效(不属于该系统)的签

署密钥都会导致签名验证失败。

概述

图 1 所示为DS1963S的主控和存储单元间的关系。DS1963S有 6 个主要的数据部件:1)64 位光刻

ROM,2)256 位暂存器,3)8 个 32 字节通用SRAM页,4)8 个受写循环计数器保护的 32 字节

SRAM页,5)保存着八个 64 位密钥(每个密钥具有独立的写循环计数器)的两个 32 字节页以

及,6)一个 512 位SHA-1 引擎(SHA = 安全散列算法)。图 2 为 1-Wire总线协议的分层结构。

全部写循环计数器都为 32 位长,并且到达最大计数后不再滚动。计数器的内容可使用特定命令和

内存数据一起被读出。总线主控制器必须首先发出以下 7 条ROM功能命令之一,1)Read ROM

(读ROM),2)Match ROM(匹配ROM),3)Search ROM(搜索ROM),4)Skip ROM(跳

过ROM),5)Resume Communication(恢复通信),6)Overdrive-Skip ROM(高速跳过ROM)

或 7)Overdrive-Match ROM(高速匹配ROM)。以标准速度完成一条Overdrive ROM命令后,器

件将进入高速模式(Overdrive mode),接下来的通信将以较高的速度进行。这些ROM功能命令

所要求的协议见图 10 所示。成功运行完一条ROM功能命令后,便可进入存储器功能的执行,主

机可运行 8 条存储器功能命令的任意一条。这些存储器功能命令的流程参见图 7 所示。全部数据

的读和写都为低位先、高位后。

寄生供电

下列框图(图 1)为寄生供电原理电路。该电路在数据触点为逻辑高时“窃取”能量。只要遵守

规定的定时和电压要求,所窃得的能量就足以满足数据线为逻辑低状态时电路的需要。寄生供电

有两方面的优点:1)通过从输入端获取能量,节省了 DS1963S 内部的锂电池;2)如果某种原因

导致锂电池耗尽,仍然可以正常读取 ROM。DS1963S 的其余电路则只能由锂电池提供能量。

3 of 37

DS1963S

64 位光刻 ROM

每个DS1963S具有一个 64 位长的特有ROM码。前 8 位是 1-Wire家族码。接着是 48 位的唯一序列

号。最后 8 位是前 56 位的CRC校验码(见图 3)。如图 4所示,1-Wire CRC由移位寄存器和异或

8

门组成的生成多项式产生。多项式表示为X

见Book of DS19xx

iButton Standards。移位寄存器初值为零。然后,从家族码的最低位开始,一次

+ X5 + X4 + 1。关于Dallas的 1-Wire循环冗余校验参

移入一位。家族码的第 8 位移入后,开始移入序列号。第 48 位序列号移完后,移位寄存器的值就

是CRC码。如果再移入 8 位CRC,移位寄存器应恢复为全零。

DS1963S 框图 图 1

DATA

Parasite-Powered

Circuitry

Lid

Contact

1-Wire

Function Control

Flag and Mode

Register

64-bit

Lasered ROM

Memory and

SHA Function

Control Unit

CRC16

Generator

Data Memory

8 Pages of

256 bits each

Data Memory

8 Pages of

256 bits each

8 Write-Cycle

Counters

one for each

Memory Page

512-bit

Secure Hash

Algorithm

Engine (SHA-1)

256-bit

Scratchpad

R

8 Write-Cycle

Counters

one for each

Secret

S

Secrets Memory

storing 8 Secrets

of 64 bits each

PRNG

Counter

2 Pages of

256 bits

4 of 37

DS1963S

1-Wire 协议的层次结构 图 2

Bus

Master

Command

Level

1-Wire ROM Function

Commands (see Figure 10)

DS1963S specific

Memory Function

Commands (see Figure 7)

1-Wire Bus

DS1963S

Available

Commands

Read ROM

Match ROM

Search ROM

Skip ROM

Resume

Overdrive Skip

Overdrive Match

Write Scratchpad

Read Scratchpad

Copy Scratchpad

Match Scratchpad

Erase Scratchpad

Read Memory

Read Authenti-

Compute SHA

cated Page

Other

Devices

Data Fields

Affected

64-bit ROM, RC-Flag

64-bit ROM, RC-Flag

64-bit ROM, RC-Flag

RC-Flag

RC-Flag

64-bit ROM, RC-Flag, OD-Flag

64-bit ROM, RC-Flag, OD-Flag

256-bit Scratchpad, Flags

256-bit Scratchpad, HIDE Flag

Data Memory, Secrets Memory,

W/C Counter, Flags

160 bits of Scratchpad, Flags

256-bit Scratchpad, Flags

Data Memory, Flags

Data Memory, W/C Counters of

Memory Page and Secret, Secret, 64bit ROM Registration Number, 160 bits

of Scratchpad, Flags, PRNG Counter

Several of the following Items,

depending on selected Sub-Function:

Data Memory, W/C Counter of

Memory Page, Secret, 64-bit ROM

Registration Number, Scratchpad,

Flags, PRNG Counter

64 位光刻 ROM 图 3

MSB LSB

8 位 CRC 码 48 位序列号 8位家族码(18h)

MSB LSB MSB LSB MSB LSB

5 of 37

DS1963S

1-Wire CRC 发生器 图 4

Polynomial = X8 + X5 + X4 + 1

R

S

0

X

1ST

STAGE

STAGE

1

X

2ND

2

X

3RD

STAGE

3

X

4TH

STAGE

4

X

5TH

STAGE

5

X

6TH

STAGE

7TH

STAGE

6

X

INPUT DATA

7

X

8TH

STAGE

8

X

存储器映像

如框图所示,DS1963S 有 4 个存储区:数据存储器,密钥存储器,计数器存储器和暂存器。这些

存储器区域被组织为 32 字节页。详见图 5 所示。当写数据或密钥时,暂存器被作为缓冲器使用。

0 至 15 页可自由读/写。它们总计包含 4096 位的 NV SRAM。页 16 和 17 含有用户只可写入的八

个 64 位密钥。密钥只能被 SHA 引擎读取,后者用它来计算信息鉴定码。16 个 32 位写循环计数

器计算写入第 8 至 15 存储器页和 8 个密钥的次数。这些计数器位于页 19 和 20,可自由读取。第

21 页包括一个计数器,每次启动 SHA 引擎时都会递增。该计数器为产生伪随机数提供种子,并

因此而被称为 PRNG 计数器。由于 SHA 引擎所需的功耗要比复制整个暂存器到某存储区的功耗

高出约 20 倍,PRNG 计数器的内容可用做器件剩余电量的指示。第 18 页是 32 字节暂存器的物理

地址。

地址寄存器和传送状态

DS1963S 使用了 3 个地址寄存器:TA1,TA2 和 E/S(图 6)。寄存器 TA1 和 TA2 用来存放读写

数据的目标地址。寄存器 E/S 是一个只读的字节计数器和传送状态寄存器,用来检验与写命令相

关的数据的完整性。E/S 寄存器的低 5 位指示最后写入暂存器、以后将复制到主存储器的数据字

节的地址。这个地址称为终止位置。E/S 寄存器的第 5 位称为 PF 或“半字节标志(partial byte

flag)”,当主机写入的数据位数不是 8 的整数倍时被置为逻辑 1。位 6 无任何功能,读取时总是

0。需要注意的是,目标地址的低 5 位同时也决定了暂存器内部开始存放数据的起始地址。这个地

址被称为字节偏移。例如,如果一条 Write(写)命令的目标地址(TA1)是 3Ch,那么暂存器将

从字节偏移量 1Ch 处开始存放输入数据,并且 4 个字节后将会被充满,终止位置变为 1Fh。在执

行一条 Write 命令后,主机可以利用终止位置和半字节标志来检验数据的完整性。E/S 寄存器的最

高位 AA 或 Authorization Accepted(授权认可)用以指示暂存器中保存的数据已被复制到了目标

存储器地址。写数据到暂存器将清除该标志。

6 of 37

DS1963S

DS1963S 存储器映像 图 5

允许读/写访问的数据存储器

页号 地址范围 密钥号 计数器号 计数器递增条件

0

0000h至 001Fh

0 0

无

4k 位

NV RAM

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

页号 地址范围 说明

0020h至 003Fh

0040h至 005Fh

0060h至 007Fh

0080h至 009Fh

00A0h 至 00BFh

00C0h 至 00DFh

00E0h 至 00FFh

0100h至 011Fh

0120h至 013Fh

0140h至 015Fh

0160h至 017Fh

0180h至 019Fh

01A0h 至 01BFh

01C0h 至 01DFh

01E0h 至 01FFh

1 1

2 2

3 3

4 4

5 5

6 6

7 7

0 0

1 1

2 2

3 3

4 4

5 5

6 6

7 7

只允许用户写入的密钥存储器

无

无

无

无

无

无

无

写循环

写循环

写循环

写循环

写循环

写循环

写循环

写循环

16

17

0200h至 0207h 密钥 0

0208h至 020Fh 密钥 1

0210h至 0217h 密钥 2

0218h至 021Fh 密钥 3

0220h至 0227h 密钥 4

0228h至 022Fh 密钥 5

0230h至 0237h 密钥 6

0238h至 023Fh 密钥 7

7 of 37

DS1963S

DS1963S 存储器映像(续) 图 5

只允许用户读取的密钥存储器

页号 地址范围 说明

地址寄存器 图 6

19

20

21

0260h至 0263h 计数器 0(页 8的写循环)

0264h至 0267h 计数器 1(页 9的写循环)

0268h至 026Bh 计数器 2(页 10的写循环)

026Ch至 026Fh 计数器 3(页 11的写循环)

0270h至 0273h 计数器 4(页 12 的写循环)

0274h至 0277h 计数器 5(页 13 的写循环)

0278h至 027Bh 计数器 6(页 14的写循环)

027Ch至 027Fh 计数器 7(页 15的写循环)

0280h至 0283h 密钥 0 的写循环计数器

0284h至 0287h 密钥 1 的写循环计数器

0288h至 028Bh 密钥 2 的写循环计数器

028Ch至 028Fh 密钥 3 的写循环计数器

0290h至 0293h 密钥 4 的写循环计数器

0294h至 0297h 密钥 5 的写循环计数器

0298h至 029Bh 密钥 6 的写循环计数器

029Ch至 029Fh 密钥 7 的写循环计数器

02A0h 至 02A3h PRNG 计数器

目标地址(TA1)

目标地址(TA2)

截止地址和数据状态(E/S)

(只读)

T7 T6 T5 T4 T3 T2 T1 T0

T15 T14 T13 T12 T11 T10 T9 T8

AA 0 PF E4 E3 E2 E1 E0

写入及验证

为了向 DS1963S 写入数据,必须把暂存器用作中间存储器。首先,主控制器发 Write Scratchpad

(写暂存器)命令并指定目的地址,然后将数据写入暂存器。在一定条件下(见“Write

Scratchpad 命令”),主控在写暂存命令流程快结束时会收到一个反码的 CRC16,用于校验命

令、地址和数据。知道了这个 CRC,主控制器将其与自己的计算结果相比较,就可以判断通信是

否成功,以及是否继续 Copy Scratchpad 命令。如果主控制器未能收到 CRC16,则应该通过 Read

Scratchpad(读暂存器)来验证数据的完整性。读暂存器时,在暂存器数据之前,DS1963S 会重新

发回目的地址 TA1 和 TA2,以及 E/S 寄存器的内容。如果 PF 标志置位,说明数据未能正确送达

暂存器。主控不必再继续读;它可尝试再次向暂存器写数据。类似地,如果 AA 标志置位,则说

明器件未能认可 Write 命令。一切步骤正确的话,两个标志都清零,并且终止位置指向最后一个

8 of 37

DS1963S

写入暂存器的字节的地址。然后,主控制器可以继续读取和验证每个数据字节。验证数据后,主

控制器就可以发 Copy Scratchpad 命令了。该命令之后必须紧随三个地址寄存器的内容:TA1,

TA2 和 E/S。主控制器可以通过读暂存获得这些内容,或者也可以从目标地址和将要写入数据的

数量中获得该信息。一旦 DS1963S 正确地收到这些字节,数据将被立即复制到从目标地址开始的

规定位置。

存储器和 SHA 功能命令

DS1963S是专门为数据安全设计的器件,因而其操作与其他存储器iButton有所区别。DS1963S的

数据存储器的读取方法和其他基于NV SRAM的存储器iButton一样,但是在读取页 16和 17(用于

存放密钥)、页 18(暂存器的物理地址)时,所得数据字节将为FFh,而非真实数据。DS1963S

和其他常规存储器

被清零时,这些功能的使用和其他基于NV SRAM的器件相同。HIDE标志主要受控于(置位或清

零)那些涉及到SHA引擎的操作。为防止暂存器数据偶然泄露,每次将DS1963S置于探头上,内

部寄生供电的电路执行上电复位的同时,HIDE标志都会被自动置位。HIDE标志可通过Erase

Scratchpad(擦除暂存器)命令清除,该命令同时擦除了留在暂存器内的全部数据。

“存储器和 SHA 功能流程”(图 7)描述了访问存储器和操作 SHA 引擎的必要协议。主机和

DS1963S 之间的通信可以常规速率(缺省,OD=0)或高速(OD=1)模式进行。如果没有明确设

定为高速模式,DS1963S 总默认为常规速率。

iButton所共有的一些功能由一个被称为HIDE的标志位控制。当这个HIDE标志

Write Scratchpad 命令 [0Fh]

HIDE = 0,目标地址范围仅限于 0000h 至 01FFh

发出 Write Scratchpad 命令之后,主机必须首先提供两字节的目标地址,随后是要写入暂存器的数

据。数据将由字节偏移(T4:T0)开始写入暂存器。终止位置(E4:E0)将是主机停止写入数据时

的字节偏移。暂存器只接受完整的数据字节。如果最后一个数据字节不完整,它将被丢弃,半字

节标志 PF 将被置位。

在执行 Write Scratchpad 命令时,DS1963S 内的 CRC 产生器(参见图 12)计算整个数据流的

CRC,始于命令代码,止于主机发送的最后一个数据字节。该 CRC 由一个 CRC16 多项式发生器

产生,首先清除 CRC 产生器,然后移入 Write Scratchpad命令码(0Fh),接着是由主机发出的目

标地址 TA1、TA2 和所有数据字节。主机可随时结束 Write Scratchpad 命令。不过,如果终止位

置为 11111b,主机就可以通过 16 个读时隙读到由 DS1963S 产生的 CRC。

HIDE = 1:目标地址范围仅限于 0200h 至 023Fh

该命令的功能仅限于选择密钥,选出的密钥即将被暂存器中的当前数据覆盖,这个数据通常是上

一次运行 Compute First Secret(计算第一密钥)或 Compute Next Secret(计算下一密钥)命令后

的结果。八个密钥的地址如图 5 所示。命令代码之后发送的地址可以指向密钥寄存器地址范围内

的任何位置。紧随目标地址之后,主机可以象写暂存一样发送数据字节。一旦发送的数据字节填

满由指定的目标地址开始的暂存器空间时,主机就可以通过 16 个读时隙读到由 DS1963S 产生的

CRC。数据字节被用于 CRC 的计算,但不会真正写入暂存器。

9 of 37

DS1963S

Read Scratchpad 命令[AAh]

HIDE = 0:

Read Scratchpad 命令用于验证目标地址、终止位置和暂存器中数据的完整性。发出命令代码后主

机开始读入数据。前两个字节为目标地址。下一个字节是终止位置/数据状态字节(E/S),紧随

其后的便是由字节偏移(T4:T0)开始的暂存器数据。主机可以一直读完暂存器,随后,便可收

到由 DS1963S 生成的反码 CRC。如果主机在读完 CRC 后继续读,则读出数据全为逻辑 1。

HIDE = 1:

该命令的功能仅限于读取目标地址和终止位置。在读取暂存器数据时,主机收到的将为逻辑 1,

直到暂存器底部,此后主机将收到由 DS1963S 产生的 CRC。如果主机继续读,读出数据将全为

逻辑 1。

Copy Scratchpad [55h]

HIDE = 0:目标地址范围仅限于 0000h 至 01FFh

Copy Scratchpad 命令用于将暂存器数据复制到某存储页中。发出命令之后,主机必须发送一个 3

字节的授权码型,这个数据应该通过紧邻此条命令之前的一个 Read Scratchpad 命令获得。这个 3

字节码型必须与三个地址寄存器(依次为 TA1,TA2,E/S)中的数据完全匹配。如果码型匹配,

AA(授权接受)标志将置位,并开始复制。当正在复制数据时,主机只能读到逻辑 1。数据复制

结束后,它将向主机发送 1、0 交错的码型,直到主机发出复位脉冲(reset pulse)为止。当正在

进行复制时,任何复位操作都将被忽略。复制操作需花费大约 30µs 的时间。主机必须读取至少 8

位交错码型,否则器件可能无法正确响应随后的复位脉冲。

三个地址寄存器中的内容决定了将要被复制的数据。暂存器中从起始偏移到终止位置间的数据将

被复制到由目标地址开始的内存中。通过这条命令,可将 1 至 32 个字节的数据复制到内存中的任

意位置。只有运行 Write Scratchpad 命令时 AA 标志才会被清除。

HIDE = 1:目标地址范围仅限于 0200h 至 023Fh

如果目标地址和终止位置与某个密钥相匹配,功能的执行和上述常规流程相同。如果目标地址指

向主存储区地址范围中的某个位置,但是 HIDE 标志置位(例如,当寄生供电电路经历了上电复

位之后),将不会复制任何暂存器数据。为了复制一个已知的数据(“口令”)到密钥中,我们

可以先将数据写入暂存器,然后置位 HIDE 标志,发出一条 Write Scratchpad 命令以便选定一个密

钥,最后,发一条 Copy Scratchpad 命令。不过,这种操作会降低系统的安全性,因此不建议使

用。

Read Memory [F0h]

Read Memory(读存储器)命令可用来读取存储页 0 至 15、位于页 19 和 20 的写循环计数器和页

21 前端的 PRNG 计数器中的内容。位于页 16 和 17 密钥存储区中的数据不可读出。在读取页 18

时,如果 HIDE 标志清零(HIDE=0),将读回暂存器中的数据,如果该标志置位(HIDE=1),

将返回 FFh。命令发出后,主机还必须提供 2 字节的目标地址。这两个字节之后,主机便可读出

自目标地址开始的数据,读操作可一直持续到 PRNG 计数器的底部乃至于超出。PRNG 计数器之

后还有 12 个未定义的字节。如果主机继续读,结果将为逻辑 1。需要特别注意的是,目标地址寄

存器将指向最后一个读取的字节。终止位置/数据状态字节不受影响。

10 of 37

DS1963S

DS1963S 提供的硬件手段能够保证写入存储单元的数据正确无误。为了保证在 1-Wire 环境下读取

数据的可靠性,同时提高数据传输的速率,建议将数据按照存储器页的大小进行分组。然后,在

每个分组内包含一个由主控制器计算的、针对每页数据的 16 位 CRC。这样,主控制器就不必多

次重复地读取一页数据来检验数据的正确与否,从而保证了快速、无误地传输数据(推荐的文件

结构参见应用笔记 114,有时也称之为 TMEX 格式)。

Erase Scratchpad [C3h]

该命令的目的是清零 HIDE 标志和擦除前次操作留在暂存器中的数据。发送命令码后,如 Write

Scratchpad 命令那样,主机发送一个目标地址,但不发送数据。接下来整个暂存器将被自动添满

FFh 字节,而与目标地址无关。此过程用时约 32µs,其间主机将读到 1。此后主机会读到一个

0、1 交替的码型,表示命令执行完毕。主机必须读取至少 8 位交错码型,否则器件可能无法正确

响应随后的复位脉冲。

Match Scratchpad [3Ch]

由 DS1963S 计算出的 SHA-1 MAC 被写入暂存器中。有些操作中,例如 Authenticate Host(主机

认证)和 Validate Data Page(数据页确认),执行运算的同时还会置位 HIDE 标志。通过 Match

Scratchpad(匹配暂存器)命令可实现对于该数据有效性的检验,同时又不需要将其读出。每执行

一次 SHA 运算后(关于算法的详细说明参见“SHA-1 算法”和“SHA-1 输出信息格式”章

节),160 位的信息鉴定码被保存在暂存器偏移地址 8 至 27 中,通过该条命令,可以将它与主机

自己的计算结果相比较。Match Scratchpad 命令发出后,主机开始逐字节发送数据,从第 8 字节开

始到第 27 字节结束。如果所有字节匹配,主机就会读到一个 0、1 交替的码型。如果 AUTH 标志

置位,MATCH 标志也被置位。如果匹配不成功,主机将读到全 1。收到反码的 CRC16 后主机必

须读取至少 8 位交错码型,否则器件可能无法正确响应随后的复位脉冲。

11 of 37

DS1963S

存储器和 SHA 功能流程 图 7

DS1963S

increments

Address

Counter

Bus Master TX Memory or

SHA Function Command

F0h

Read Memory

?

YY

CHLG = 0 ; AUTH = 0

Bus Master TX

TA1(T7:T0), TA2 (T15:T8)

Address

< 2B0h ?

Y

DS1963S sets Memory

Address = (T15:T0)

Pages

16 to 17 ?

Bus Master RX

Data Byte from

Memory Address

Y

Master

TX Reset ?

NN

N

Y

N

From ROM Functions

Flow Chart (Figure 10)

S

DS1963S

R

increments

SP. Offset

Bus Master RX

FFh byte

3Ch

Match Scratch-

pad

?

CHLG = 0 ; MATCH = 0

DS1963S sets Scratch-

pad Offset = 8 decimal

Bus Master TX

data byte

Master

TX Reset ?

N

SP Offset = 27

Y

N

AUTH=1?

Y

AUTH=0; MATCH=1

To Figure 7

2nd Part

Y

N

Y

N

Address

< 2AFh ?

N

Bus Master

RX "1"s

Bus Master

RX "1"s

N

Master

TX Reset ?

Y

To ROM Functions

Flow Chart (Figure 10)

DS1963S TX CRC16 of

Command and Data

N

Data Bytes

Match ?

Y

DS1963S TX "0"

DS1963S TX "1"

Master

TX Reset ?

Y

N

Vertical

Spare

From Figure 7

2nd Part

12 of 37

Loading...

Loading...