dallas semiconductor DS1803 service manual

DS1803

DS1803

Addressable Dual Digital Potentiometer

FEATURES

• 3V or 5V Power Supplies

• Ultra–low power consumption

• Two digitally controlled, 256–position potentiometers

• 14–Pin TSSOP (173 mil) and 16–Pin SOIC (150 mil)

packaging available for surface mount applications

• Addressable using 3–Chip Select Inputs

• Serial/Synchronous Bus Interface

• Operating Temperature

– Industrial: –40°C to +85°C

• Standard Resistance Values:

– DS1803–010 10KΩ

– DS1803–050 50KΩ

– DS1803–100 100KΩ

DESCRIPTION

The DS1803 is an addressable device having two independently controlled potentiometers. Each potentiometer’s wiper can be set to one of 256 positions. Device

control is achieved via a 2–wire serial interface having a

data I/O terminal and a clock input terminal. Device

addressing is provided through three chip select input

terminals and correct communication protocol. Addressing capability, when operating in a bus topology , allows

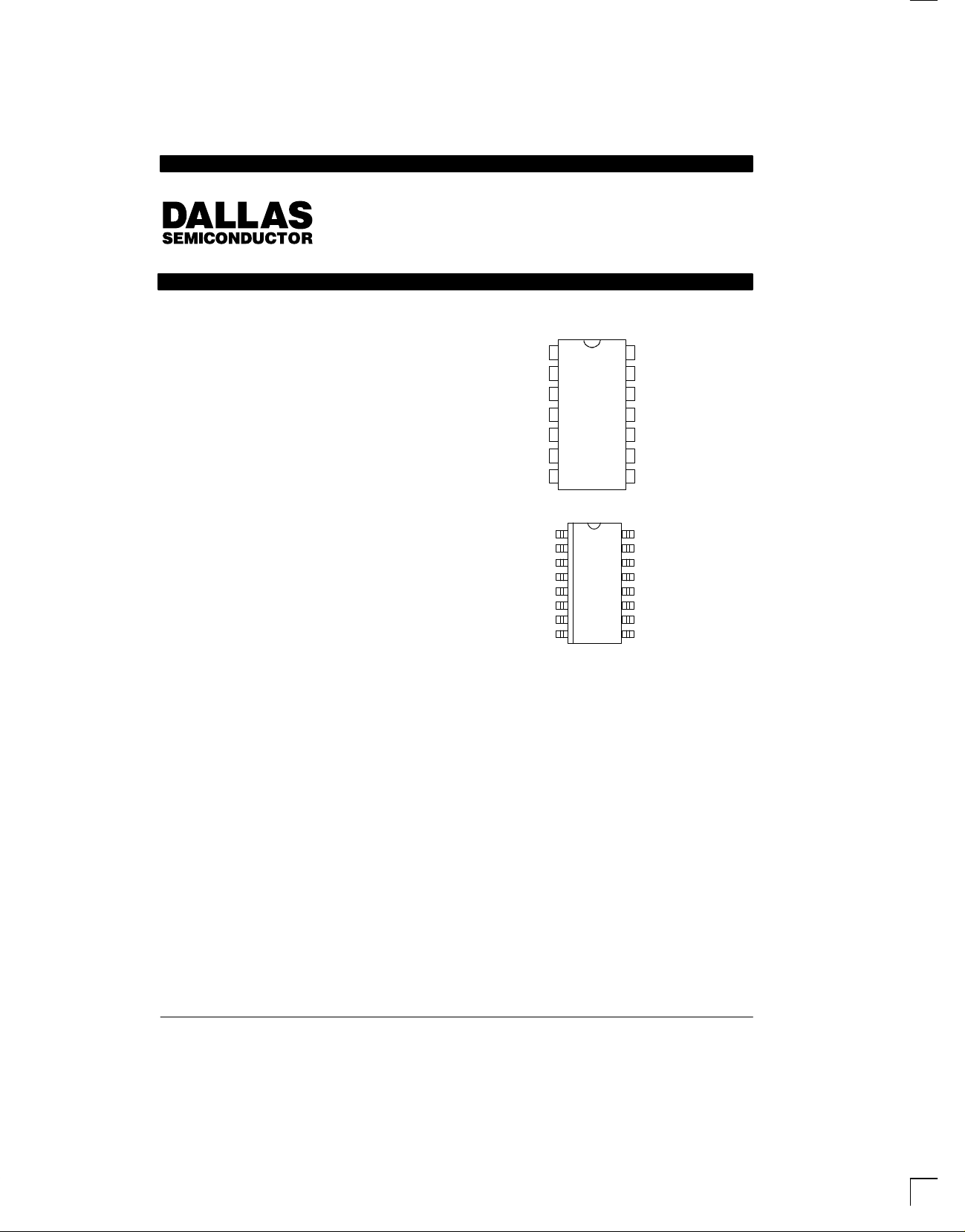

PIN ASSIGNMENT

1

2

3

4

5

6

7

8

Section

14

VCC

13

NC

12

H0

11

L0

10

W0

9

SDA

8

SCL

16

VCC

15

NC

14

H0

13

L0

12

W0

11

NC

10

SDA

9

SCL

H1

1

L1

2

W1

3

A2

4

A1

5

A0

6

GND

7

DS1803E 14–PIN TSSOP (173 MIL)

H1

NC

L1

W1

A2

A1

A0

GND

DS1803Z 16–PIN SOIC (150 MIL)

DS1803 16–PIN DIP (300 MIL)

See Mech. Drawings

PIN DESCRIPTION

L0, L1 – Low End of Resistor

H0, H1 – High End of Resistor

W0, W1 – Wiper Terminal of Resistor

V

CC

A0 ..A2 – Chip Select Inputs

SDA – Serial Data I/O

SCL – Serial Clock Input

GND – Ground

NC – No connection

up to eight devices to be controlled by the serial interface. The exact wiper position of each potentiometer

can be written or read. The DS1803 is available in a

16–pin DIP , 16–pin SOIC and 14–pin TSSOP package.

The device is available in three standard resistance values: 10KΩ, 50KΩ , and 100KΩ , and is specified over the

industrial temperature range.

– 3V/5V Power Supply Input

Copyright 1995 by Dallas Semiconductor Corporation.

All Rights Reserved. For important information regarding

patents and other intellectual property rights, please refer to

Dallas Semiconductor data books.

062097 1/10

DS1803

DEVICE OPERATION

The DS1803 is an addressable, digitally controlled

device which has two 256–position potentiometers. A

functional block diagram of the part is shown in Figure 1.

Communication and control of the device is accomplished via a 2–wire serial interface having signals SDA

and SDL. Device addressing is attained using the

device chip select inputs A0, A1, A2 and correct communication protocol over the 2–wire serial interface.

Each potentiometer is composed of a 256 position resistor array. Two 8–bit registers, each assigned to a

respective potentiometer , are used to set wiper position

on the resistor array. The wiper terminal is multiplexed

to one of 256 positions on the resistor array based on its

corresponding 8–bit register value. For example, the

high–end terminals, H0 and H1, have wiper position values FF(Hex) while the low–end terminals, L0 and L1,

have wiper position values 00(Hex).

The DS1803 is a volatile device that does not maintain

the position of the wiper during power–down or loss of

power. On power–up, the DS1803 wipers’ position will

be set to position 00(Hex) –– the low–end terminals.

The user may then reset the wiper value to a desired

position.

Communication with the DS1803 takes place over the

2–wire serial interface consisting of the bi–directional

data terminal, SDA, and the serial clock input, SCL.

Complete details of the 2–wire interface are discussed

in the section entitled “2–wire Serial Bus”.

The 2–wire interface and chip select inputs A0, A1, and

A2 allow operation of up to eight devices in a bus topology; with A0, A1, and A2 being the address of the

device.

Application Considerations

The DS1803 is offered in three standard resistor values

which include the 10KΩ, 50KΩ , and 100KΩ. The resolution of the potentiometer is defined as R

R

is the total resistor value of the potentiometer . The

TOT

DS1803 is designed to operate using 3V or 5V power

supplies over the industrial (–40°C to +85°C) temperature range. Maximum input signal levels across the

potentiometer cannot exceed the operating power supply of the device.

/255, where

TOT

2–WIRE SERIAL DATA BUS

The DS1803 supports a bi–directional 2–wire bus and

data transmission protocol. A device that sends data on

the bus is defined as a transmitter, and a device receiving data as a receiver. The device that controls the message is called a “master”. The devices that are controlled by the master are “slaves”. The bus must be

controlled by a master device which generates the serial

clock (SCL), controls the bus access, and generates the

STAR T and STOP conditions. The DS1803 operates as

a slave on the 2–wire bus. Connections to the bus are

made via the open–drain I/O lines SDA and SCL.

The following bus protocol has been defined (see

Figure 2).

• Data transfer may be initiated only when the bus is not

busy.

• During data transfer, the data line must remain stable

whenever the clock line is HIGH. Changes in the data

line while the clock line is high will be interpreted as

control signals.

Accordingly, the following bus conditions have been

defined:

Bus not busy: Both data and clock lines remain HIGH.

Start data transfer: A change in the state of the data

line, from HIGH to LOW, while the clock is HIGH, defines

a START condition.

Stop data transfer: A change in the state of the data

line, from LOW to HIGH, while the clock line is HIGH,

defines the STOP condition.

Data valid: The state of the data line represents valid

data when, after a START condition, the data line is

stable for the duration of the HIGH period of the clock

signal. The data on the line must be changed during the

LOW period of the clock signal. There is one clock pulse

per bit of data. Figure 2 details how data transfer is

accomplished on the 2–wire bus. Depending upon the

state of the R/W

possible.

* bit, two types of data transfer are

062097 2/10

DS1803

Each data transfer is initiated with a START condition

and terminated with a STOP condition. The number of

data bytes transferred between START and STOP

conditions is not limited, and is determined by the master device. The information is transferred byte–wise and

each receiver acknowledges with a ninth bit.

Within the bus specifications a regular mode (100 KHz

clock rate) and a fast mode (400 KHz clock rate) are

defined. The DS1803 works in both modes.

Acknowledge: Each receiving device, when

addressed, is obliged to generate an acknowledge after

the reception of each byte. The master device must

generate an extra clock pulse which is associated with

this acknowledge bit.

A device that acknowledges must pull down the SDA

line during the acknowledge clock pulse in such a way

that the SDA line is stable LOW during the HIGH period

of the acknowledge related clock pulse. Of course,

setup and hold times must be taken into account. A

master must signal an end of data to the slave by not

generating an acknowledge bit on the last byte that has

been clocked out of the slave. In this case, the slave

must leave the data line HIGH to enable the master to

generate the STOP condition.

1. Data transfer from a master transmitter to a

slave receiver: The first byte transmitted by the

master is the control byte (slave address). Next follows a number of data bytes. The slave returns an

acknowledge bit after each received byte.

2. Data transfer from a slave transmitter to a mas-

ter receiver: The first byte (the slave address) is

transmitted by the master. The slave then returns an

acknowledge bit. Next follows a number of data

bytes transmitted by the slave to the master. The

master returns an acknowledge bit after all received

bytes other than the last byte. At the end of the last

received byte, a ‘not acknowledge’ is returned.

The master device generates all of the serial clock

pulses and the STAR T and STOP conditions. A transfer

is ended with a STOP condition or with a repeated

STAR T condition. Since a repeated ST ART condition is

also the beginning of the next serial transfer, the bus will

not be released.

The DS1803 may operate in the following two modes:

1. Slave receiver mode: Serial data and clock are

received through SDA and SCL. After each byte is

received, an acknowledge bit is transmitted. STAR T

and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the

slave address and direction bit.

2. Slave transmitter mode: The first byte is received

and handled as in the slave receiver mode. However, in this mode the direction bit will indicate that

the transfer direction is reversed. Serial data is

transmitted on SDA by the DS1803 while the serial

clock is input on SCL. STAR T and STOP conditions

are recognized as the beginning and end of a serial

transfer.

SLAVE ADDRESS

A control byte is the first byte received following the

START condition from the master device. The control

byte consist of a four bit control code; for the DS1803,

this is set as 0101 binary for read/write operations. The

next three bits of the control byte are the device select

bits (A2, A1, A0). They are used by the master device to

select which of eight devices are to be accessed. The

select bits are in effect the three least significant bits of

the slave address. Additionally, A2, A1 and A0 can be

changed anytime during a powered condition of the

part. The last bit of the control byte (R/W

operation to be performed. When set to a one a read

operation is selected, and when set to a zero a write

operation is selected. Figure 3 shows the control byte

structure for the DS1803.

Following the START condition, the DS1803 monitors

the SDA bus checking the device type identifier being

transmitted. Upon receiving the 0101 address code and

appropriate device select bits, the slave device outputs

an acknowledge signal on the SDA line.

*) defines the

062097 3/10

Loading...

Loading...