Dallas Semiconductor DS1682X, DS1682S Datasheet

www.dalsemi.com

N/CN

PRELIMINARY

DS1682

Total Elapsed Time Recorder with Alarm

FEATURES

Records the total time that the Event Input has

been active and the number of events that

have occurred

Elapsed Time Counter to monitor event

durations with quarter second resolution

Built in 32 bit non-volatile Total Time

Accumulator Register (34 years)

Non-volatile 17-bit Event Counter records the

total number of times an event has occurred

Programmable 32 bit non-volatile alarm trip

point to trigger Alarm# output

Alarm# output to alert the user that the total

accumulated time limit has been reached

Calibrated, Temperature Compensated RC

time base (accurate to 1% typ)

Stores the contents of the Elapsed Time

Counter with the previous total and

increments the event counter at the end of

each event or power down

Reset Enable bit to allow the device to be

cleared to zero, if desired

10 bytes of write protectable EEPROM user

memory

Write Disable bit to prevent the memory from

being changed or erased

Anti-Glitch filter will prevent noise spikes

from triggering false events on the Event

Input

2-wire serial communication

Wide power supply range (2.5V – 5.5V)

PIN ASSIGNMENT

EVENT

ALARM

GND

1

2

3

Bottom View

DS1682X 6-pin Flip Chip

EVENT

1

/C

2

ALARM

GND

3

4

Top View

DS1682S 8-Pin SOIC (150 mil)

Vcc

6

SCL

5

SDA

4

8

Vcc

7

6

SCL

SDA

5

PIN DESCRIPTION

EVENT - Event Input

ALARM - Alarm Output

GND - Ground

SDA - 2-wire Data Input/Output

SCL - 2-wire Clock Input

V

CC

- Voltage Supply

N/C - No Connect

ORDERING INFORMATION

DS1682 8-Pin µSOP

DS1682S 8-Pin SOIC (150 mil)

DS1682X 6-Pin Flip Chip Package

** For more information of Flip Chip Packaging,

go to www.dalsemi.com to the Released Data

Sheets section and select Chip Scale and Flip

Chip Package Data Index.

DESCRIPTION

The DS1682 is an integrated elapsed time recorder that will provide the total amount of time that an event

is/has been active since the DS1682 was last reset to zero via the 2-wire bus. When the total time

accumulated is equal to the preset alarm trip point and the pola rity bit is set to a zero, the Ala rm# output

will become active to alert the user, or with the polarity bit set to a one, the Alarm# output will become

inactive when the values match. This is ideal for applications such as monitoring the total amount of time

that something is turned on or in operation, how long something has been used, or the total number of

uses since the last calibration or repair.

1 of 13 052400

DS1682

The DS1682 uses a calibrated, temperature compensated RC time base to increment an elapsed time

counter while an event is active. When the event becomes active, the contents of the non-volatile Total

Time Accumulator register are downloaded to the Elapsed Time Counter (ETC) and as the event

continues, the ETC is incremented in quarter second increments. When the event becomes inactive or the

power is removed, the DS1682 will increment the 17-bit non-volatile Event Counter register and put the

contents of the ETC into the 32-bit non-volatile Total Accumulated Time register which can hold up to

34 years of active event time. A storage cap may be required on V

to provide enough power to store

CC

the value in the ETC to the Total Time Accumulator register if power is taken away at the same time the

event ends.

When the 32-bit non-volatile Alarm Trip Point register is programmed to a non-zero number via the

2-wire bus and the AoR bit in the Configuration register set to a zero, the Alarm# output will be enabled

and the DS1682 will begin to monitor the values in the ETC for the programmed value in the Alarm Trip

Point register. Once the number in the ETC is equal to or greater than the value in the Alarm Trip Point

register, and the polarity bit is set to a zero, the Alarm# output will become active to alert the user, or

with the polarity bit set to a one, the Alarm# output will become inactive when the values match. The

DS1682 will activate the Alarm# output by pulling the pin low four times at power up, when the alarm

becomes active, or when the Alarm# pin is pulled low and released if the AOS bit is set to a 1. If the

AOS bit is a 0, the Alarm# output will be constantly low when the alarm is active.

In order to reset the device, the Reset Enable bit or the AoR bit in the Configuration register must be set

to a 1. With the Reset Enable bit set to a 1 or the AoR bit set to a 1 with the Alarm# pin held high, the

DS1682 can be reset by the Reset command sent over the 2-wire bus. If the Write Disable flag in the

Configuration register is set to a 1 by writing the Write Disable command two times, the Configuration

registers and Alarm Trip Point register will not be able to be written. If the Write Disable flag is set to a

1, the Total Time Accumulator, Elapsed Time Counter, and Event Counter will be able to be reset, if the

Reset Enable or AoR bits have been set to a 1, but the status of the Reset Enable or AoR bits will not be

able to be changed since the Configuration register is locked by the WDF being set to a 1.

The Write Memory Disable is similar to the Write Disable and is used to control the writability of the

10 bytes of EEPROM User memory. The Write Memory Disable Flag is also set to a 1 when the Write

Memory Disable command is written twice and can not be changed once it is set to a 1. If the Write

Memory Disable bit is set to a 1, the 10 bytes of memory will not be able to be written or erased. If the

Write Memory Disable bit is a 0, the user will have full access to the bytes with the standard EEPROM

write time restrictions. If the Write Disable is a 0, the device is fully writable or erasable except for the

User Memory and the Write Memory Disable flag, which are only controlled by the Write Memory

Disable command. With both the Write Disable and Write Memory Disable set to 1’s, the only inputs

that will be accessible are the Reset command if it is enabled, the Event input and the Alarm#

input/output. The rest of the part will be read only.

When data is written to the device, the device slave address will be sent first followed by the address

pointer and the desired byte of data. Once a single byte of data is sent, there must be at least 200 mS to

allow the EEPROM to update the data.

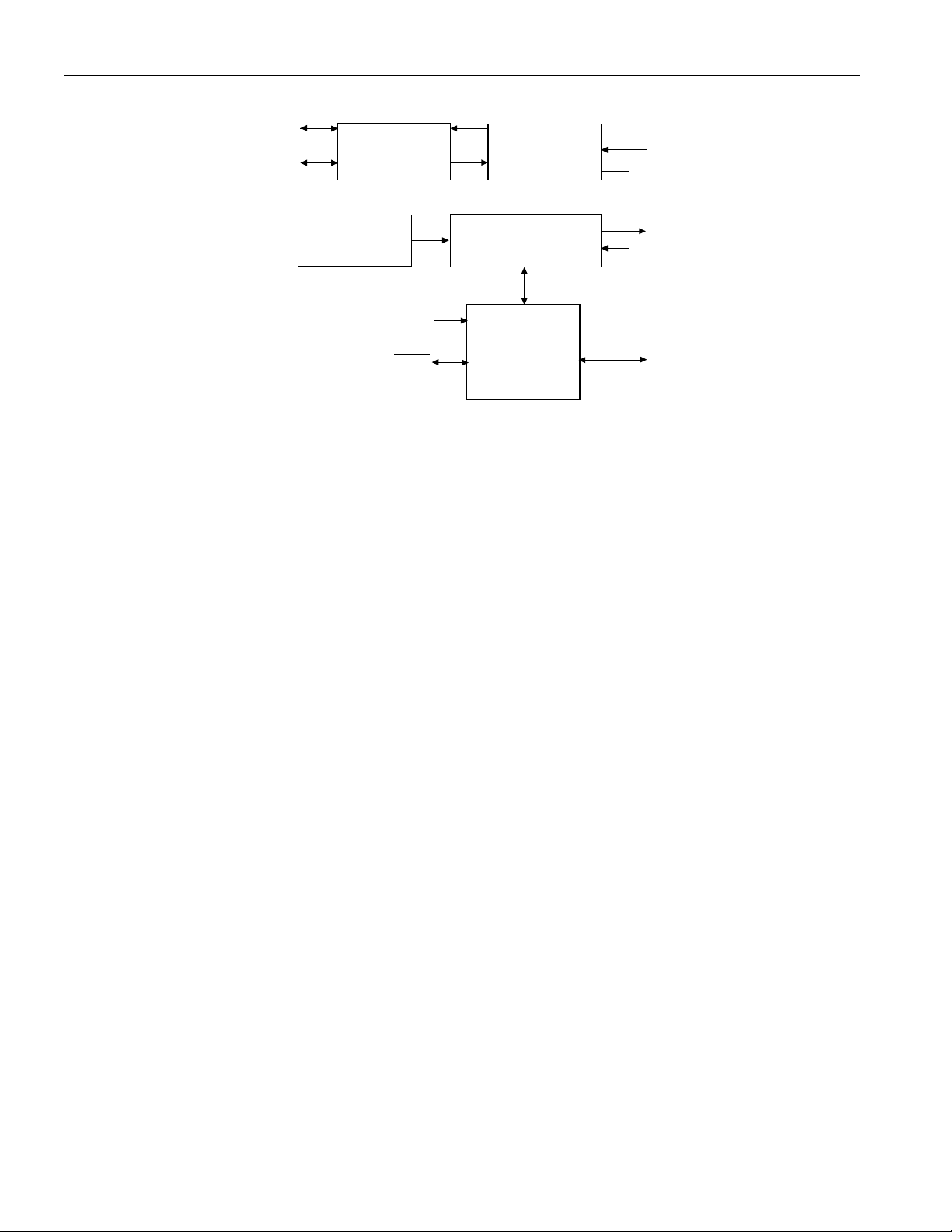

OVERVIEW

The block diagram in Figure 1 shows the relationship between the major control and memory I/O sections

of the DS1682. The device has three major components: 1) clock generator and control blocks, 2)

elapsed time counter and accumulator registers, and 3) 2-wire interface.

2 of 13

DS1682 BLOCK DIAGRAM Figure 1

A

A

DS1682

SCL

SDA

SERIAL

INTERFACE

OSCILLATOR

ND

DIVIDER

ELAPSED TIME COUNTER

EVENT

ALARM

MEMORY

FUNCTION

CONTROL

ND ACCUMULATOR

REGISTERS

CONTROL

LOGIC

SIGNAL DESCRIPTIONS

The following paragraphs describe the function of each pin.

VCC – VCC is a +3-5 volt input supply. A capacitor or other temporary energy sour ce may be required to

hold the Voltage 150 mS after the event has completed if the system power is removed at the same time

as the event ends in order to allow the contents of the ETC to be stored properly. With less than the

150 mS of power after the end of the event, the data may be lost. The LSB is written first to be sure that

the most likely changed data is saved first.

GND - Ground

SCL (2-wire Serial Clock Input) – The SCL pin is the serial clock input for the 2-wire synchronous

communications channel. The SCL pin is an open drain input, which requires an external pull–up

resistor.

SDA (2-wire Input/Output) – The SDA pin is the data Input/Output signal for the 2-wire synchronous

communications channel. The SDA pin is an open drain I/O, which requires an external pull–up resistor.

EVENT (Event Interrupt Input) – The Event pin is an input that will be activated by an external device to

signify an event has occurred and should be logged. When the pin is pulled high, the Elapsed Time

Counter (ETC) will begin to keep track of the time with quarter second resolution and when the pin is

pulled low, the contents of the ETC will be stored to the non-volatile Total Time Accumulator register

and the Event Counter register will be incremented. A pull-down resistor has been internally connected

to the Event input to prevent power-up glitches from triggering a false event. The Event input has a

Glitch filter to prevent very short noise spikes from triggering an event. A capacitor or other temporary

energy source may be required to hold the Voltage 150 mS after the event has completed if the system

power is removed at the same time as the event ends in order to allow the contents of the ETC to be

stored properly. With less than the 150 mS of power after the end of the event, the data may be lost. The

LSB is written first to be sure that the most likely changed data is saved first. When the Event pin

changes states, the 2-wire bus will be unavailable for communications for 200 mS.

3 of 13

DS1682

ALARM# (Alarm Output) - When there is a non-zero number programmed into the Alarm Trip Point

register and a zero in the AoR bit of the Configuration register, the Alarm# output will be enabled and the

DS1682 will begin to monitor the values in the ETC for the programmed value in the Alarm Trip Point

register. When the Polarity bit in the Configuration register is set to a zero the Alarm# output will

become active when the Alarm Trip Point is ex ceeded. When the Polari ty bit is set to a one, t he Alarm#

output will be inactive until the Alarm Trip Point is exceeded. With the AoR bit in the Configuration

register set to a one, the Reset Enable input will be mapped to the Alarm# pin.

N/C (No Connect) – This pin is not connected internally.

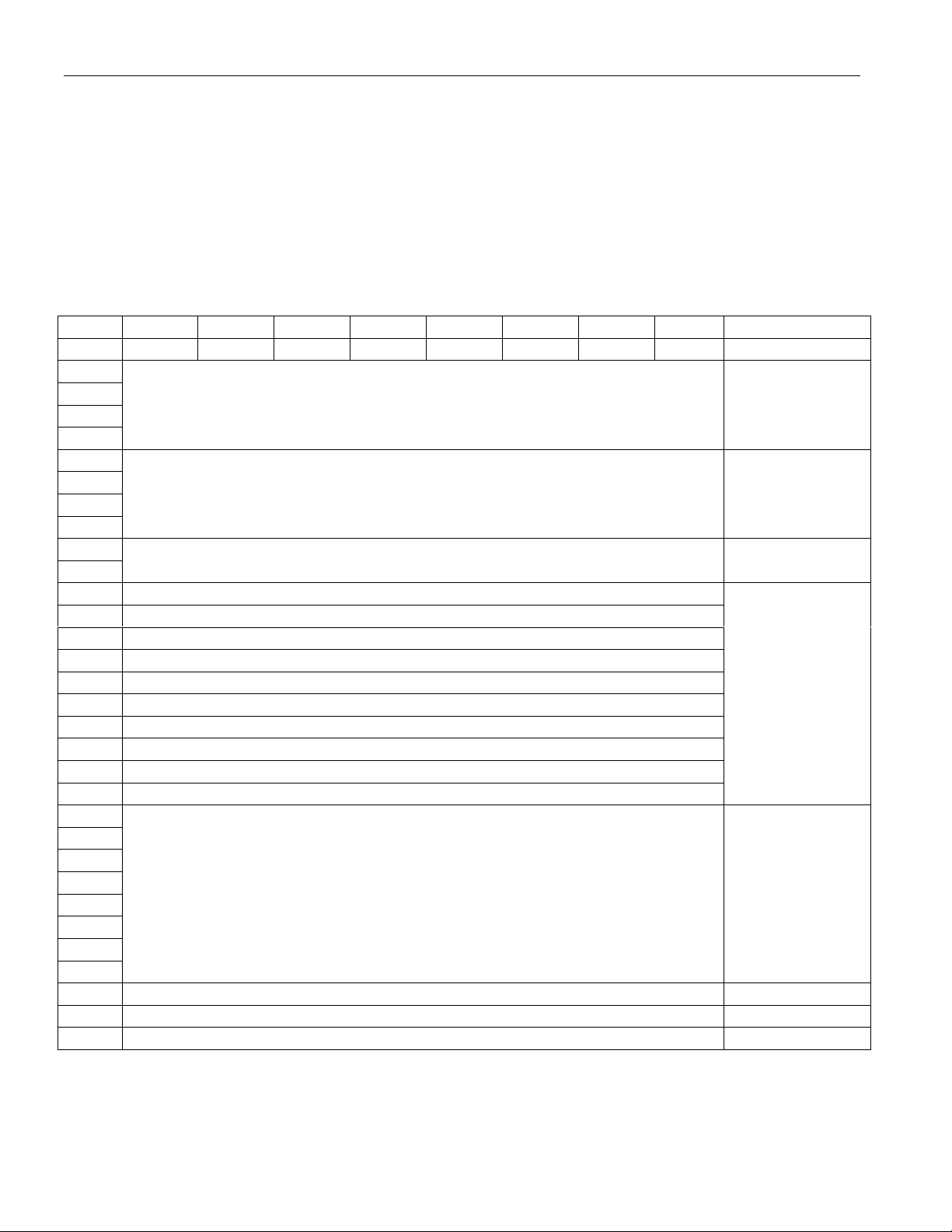

MEMORY MAP

Addr Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Function

00 AoR AF WDF WMDF AOS RE AP ERO Config. Register

01 Low Byte Alarm

02 Low-Middle Byte Trip

03 High-Middle Byte Point

04 High Byte

05 Low Byte Total

06 Low-Middle Byte Time

07 High-Middle Byte Accumulator

08 High Byte

09 Low Byte Event

0A High Byte Counter

0B Byte One

0C Byte Two

0D Byte Three User

0E Byte Four Memory

0F Byte Five

10 Byte Six

11 Byte Seven

12 Byte Eight

13 Byte Nine

14 Byte Ten

15

16

17

18 Not Used (reads 00h) Not Used

19

1A

1B

1C

1D Reset Command Reset Command

1E Write Disable Write Disable

1F Write Memory Disable Memory Disable

4 of 13

Loading...

Loading...