Dallas Semiconductor DS1667-100, DS1667-050, DS1667-010, DS1667S-100, DS1667S-050 Datasheet

...

1 of 10 032000

FEATURES

Two digitally controlled 256-position

potentiometers

Serial port provides means for setting and

reading both potentiometers

Resistors can be connected in series to

provide additional resolution

Default wiper position on power up is 50%

Resistive elements are temperature-

compensated to +20% end to end

Two high-gain, wide bandwidth operational

amplifiers

Low power CMOS design

Applications include analog-to-digital and

digital-to-analog converters, variable

oscillators, and variable gain amplifiers

20-pin DIP package or optional 20-pin SOIC

surface mount package

Operating temperature range

- Commercial: 0°C to 70°C

Resistance values:

RESOLUTION -3 dB POINT

DS1667-10: 10k 39 ohms 1.1 MHz

DS1667-50: 50k 195 ohms 200 kHz

DS1667-100: 100k 390 ohms 100 kHz

PIN ASSIGNMENT

PIN DESCRIPTION

V

CC

- +5-Volt Supply

GND - Ground

L0, L1 - Low End of Resistor

H0, H1 - High End of Resistor

W0, W1 - Wiper End of Resistor

V

B

- Substrate Bias and OP

AMP Negative Supply

SOUT - Wiper for Stacked

Configuration

RST - Serial Port Reset Input

DQ - Serial Port Input/Output

CLK - Serial Port Clock Input

COUT - Cascade Serial Port

Output

NINV0, NINVI - Noninverting OP AMP

Input

INV0, INVI - Inverting OP AMP Input

OUT0, OUT1 - OP AMP Outputs

DESCRIPTION

The DS1667 is a dual-solid state potentiometer that is adjustable by digitally selected resistive elements.

Each potentiometer is composed of 256 resistive elements. Between each resistive section of each

potentiometer are tap points accessible to the wiper. The position of the wiper on the resistive array is set

by an 8-bit register that controls which tap point is connected to the wiper output. Each 8-bit register can

be read or written by sending or receiving data bits over a 3-wire serial port. In addition, the resistors can

be stacked such that a single potentiometer of 512 sections results. When two separate potentiometers are

used, the resolution of the DS1667 is equal to the resistance value divided by 256. When the

potentiometers are stacked end to end, the resistance value is doubled while the resolution remains the

DS1667

Digital Resistor with OP AMP

www.dalsemi.com

20-Pin DIP (300-mil) and 20-Pin SOIC

See Mech. Drawings Section

1

2

3

4

5

6

7

9

8

10

20

19

18

17

16

15

14

12

13

11

V

CC

OUT0

SOUT

W0

H0

L0

COUT

INVI

DQ

NINVI

NINV0

INV0

V

B

W1

H1

L1

RST

OUT1

CLK

GND

DS1667

2 of 10

same. The DS1667 also contains two high gain wide bandwidth operational amplifiers. Each amplifier

has both the inverting and non-inverting inputs and the output available for user configuration. The

operational amplifiers can be paired with the resistive elements to perform such functions as analog to

digital conversion, digital to analog conversion, variable gain amplifiers, and variable oscillators.

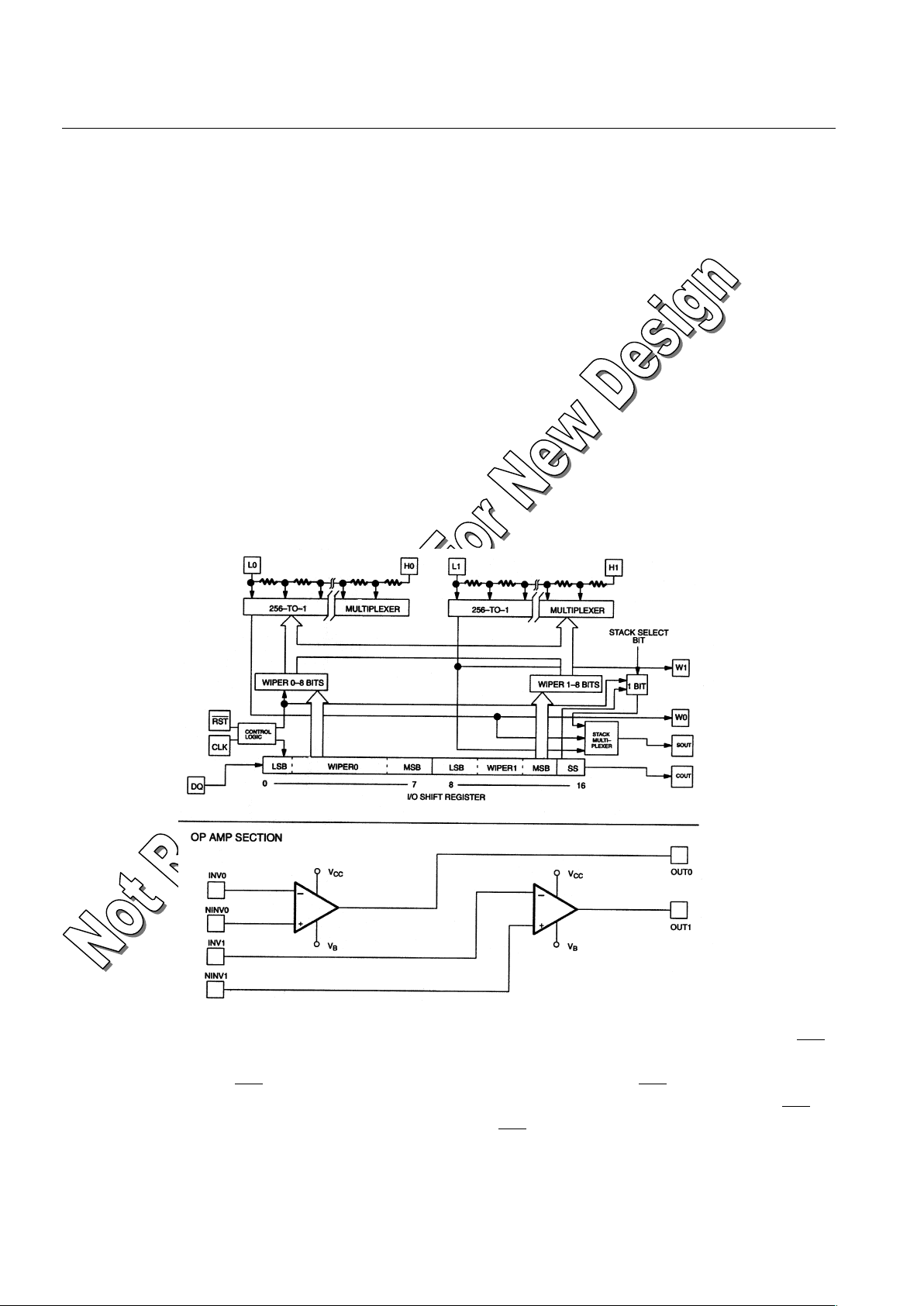

OPERATION - DIGITAL RESISTOR SECTION

The DS1667 contains two potentiometers, each of which has its wiper set by a value contained in an 8-bit

register (see Figure 1). Each potentiometer consists of 256 resistors of equal value with tap points

between each resistor and at the low end.

In addition, the potentiometer can be stacked by connecting them in series such that the high end of

potentiometer 0 is connected to the low end of potentiometer 1. When stacking potentiometers, the stack

select bit is used to select which potentiometer wiper will appear at the stack multiplexer output (SOUT).

A zero written to the stack multiplexer will connect wiper 0 to the SOUT pin. This wiper will determine

which of the 256 bottom taps of the stacked potentiometer is selected. When a 1 is written to the stack

multiplexer, wiper 1 is selected and one of the upper 256 taps of the stacked potentiometer is presented at

the SOUT pin.

BLOCK DIAGRAM Figure 1

Information is written to and read from the wiper 0 and wiper 1 registers and the stack select bit via the

17-bit I/O shift register. The I/O shift register is serially loaded by a 3-wire serial port consisting of RST ,

DQ, and CLK. It is updated by transferring all 17 bits (Figure 2). Data can be entered into the 17-bit shift

register only when the

RST input is at a high level. While at a high level, the RST function allows serial

entry of data via the D/Q pin. The potentiometers always maintain their previous value until RST is

taken to a low level, which terminates data transfer. While RST input is low, the DQ and CLK inputs are

ignored.

DS1667

3 of 10

Valid data is entered into the I/O shift register while RST is high on the low-to-high transition of the

CLK input. Data input on the DQ pin can be changed while the clock input is high or low, but onl y data

meeting the setup requirements will enter the shift register. Data is always entered starting with the value

of the stack select bit. The next 8 bits to be entered are those specifying the wiper 1 setting. The MSB of

these 8 bits is sent first. The next 8 bits to be entered are those specifying the wiper 0 setting, sent MSB

first. The 17

th

bit to be entered, therefore, will be the least significant bit of the wiper 0 setting. If fewer

than 17 bits are entered, the value of the potentiometer settings will result from the number of bits that

were entered plus the remaining bits of the old value shifted over by the number of bits sent. If more than

17 bits are sent, only the last 17 bits are left in the shift register. Therefore, sending other than 17 bits can

produce indeterminate potentiometer settings.

As bits are entered into the shift register, the previous value is shifted out bit by bit on the cascade serial

port pin (COUT). By connecting the COUT pin to the DQ pin of a second DS1667, multiple devices can

be daisy chained together as shown in Figure 3.

When connecting multiple devices, the total number of bits sent is always 17 times the number of

DS1667s in the daisy chain. In applications where it is desirable to read the settings of potentiometers, the

COUT pin of the last device connected in a daisy chain must be connected back to the DQ input of the

first device through a resistor with a value of 1k to 10k. This resistor provides isolation between COUT

and DQ when writing to the device (see Figure 3).

When reading data, the DQ line is left floating by the reading device. When

RST is held low, bit 17 is

always present on the COUT pin, which is fed back to the input DQ pin through the resistor (see Figure

4). This data bit can now be read by the reading device. The RST pin is then transitioned high to initiate a

data transfer. When the CLK input transitions low to high, bit 17 is loaded into the first position of the

I/O shift register and bit 16 becomes present on COUT and DQ. After 17 bits (or 17 times the number of

devices for a daisy chain), the data has shifted completely around and back to its original position. When

RST is transitioned back low to end data transfer, the value (the same as before the read occurred) is

loaded into the wiper 0 and wiper 1 registers and the stack select bit.

When power is applied to the DS1667, the device always has the wiper settings at half position and the

stack select bit is at 0.

Loading...

Loading...