Page 1

SPECIFICATIONS

MODEL DVT-20F4PA DVT-20F4FA DVT-21F4LA

Receiving System PAL-I PAL-B/G P/S-B/G, S-L/L'

Mains Voltage 230V AC 50Hz

Power Consumption 72W Approx.(20 inch)

76W Approx.(21 inch)

Sound Output 1.5W Approx.(at 60%, 10% THD) x 2

Antenna Impedance 75 ohm unbalanced

Tuning System Frequency Synthesis Tuning System

Number of Program 99 Programs

Reception Channel Refer to the TUNER description

Remote Control Unit R-30C(RH400) R-30C(RC1400) R-30C(RCT400)

Screen Size 20" : 480mm

(Diagonal) 21" : 510mm

Indication On Screen Display

-Program No. (01-99)

-Sleep (10-120, step 10 min)

-Mute & Volume

-AV1, AV2

-Main menu( Picture, Clock Set, TV Timer, Video Timer,

Language,Preset)

-Picture Menu(Brightness, Colour, Contrast, Sharpness)

-TV Timer Menu(ON Time, PR., OFF Time)

-Preset Menu(Full Auto Search, Auto Search, Fine Tuning, VideoPlus+

Preset)

Terminal 21 Pin EURO SCART

2

Page 2

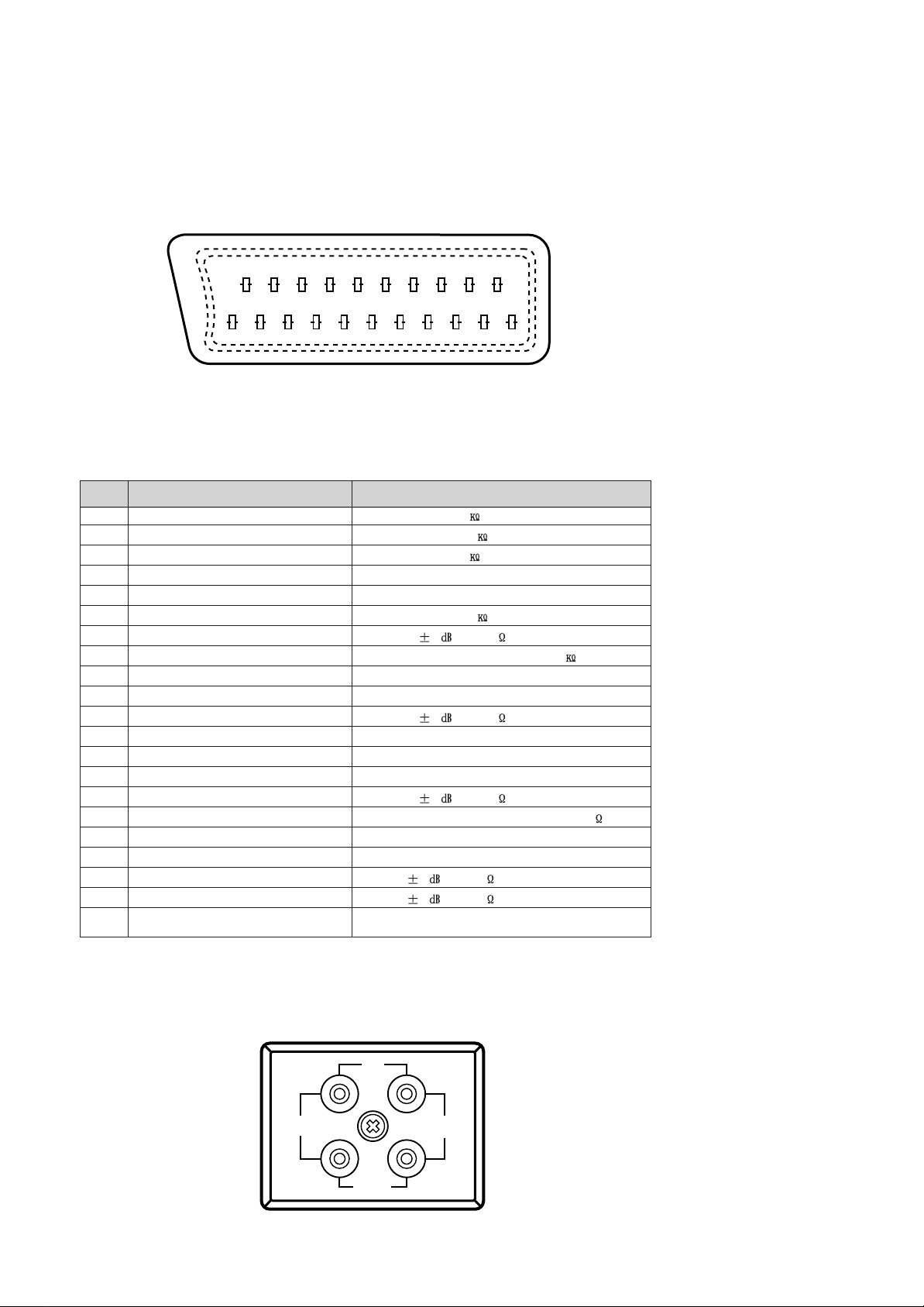

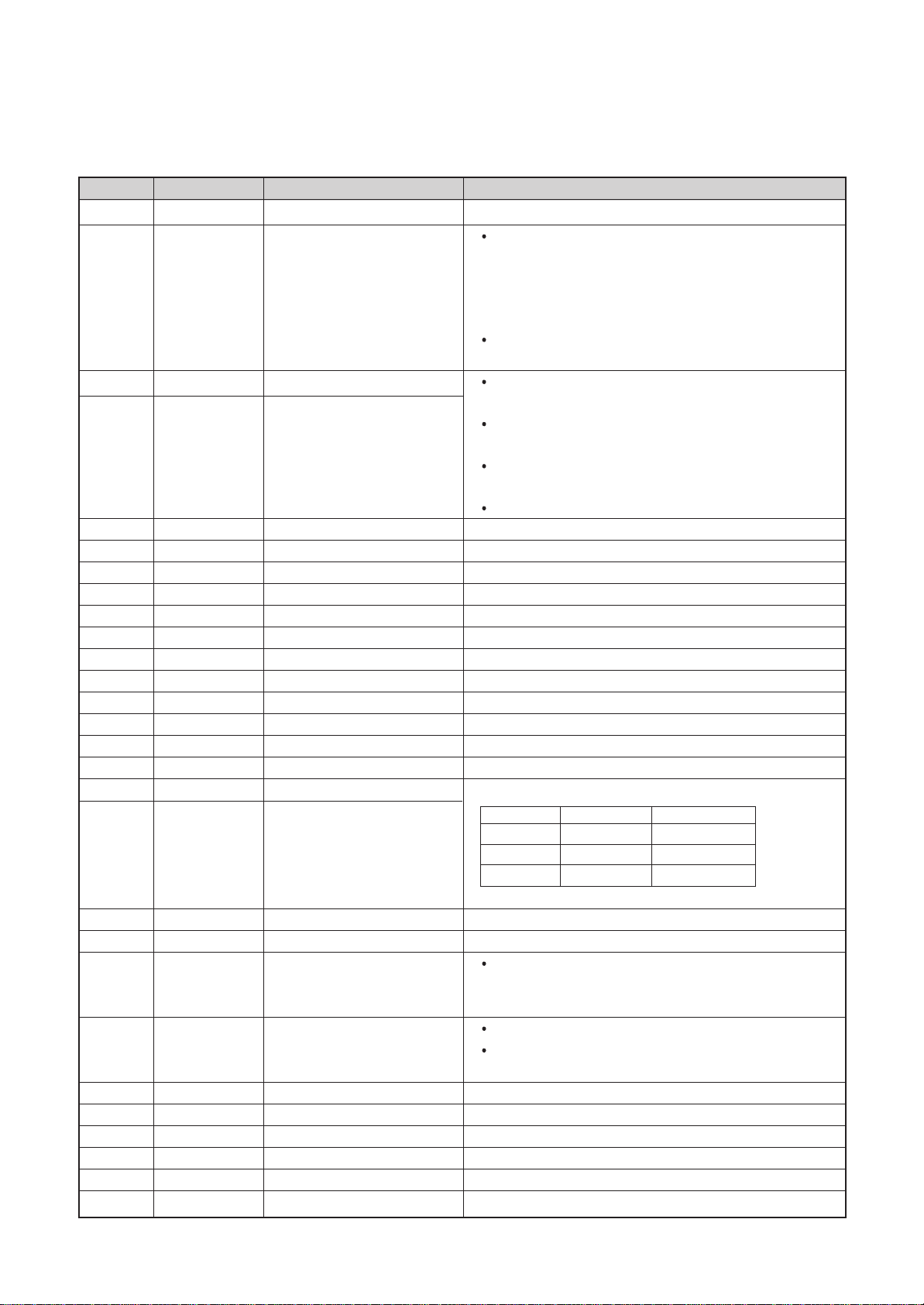

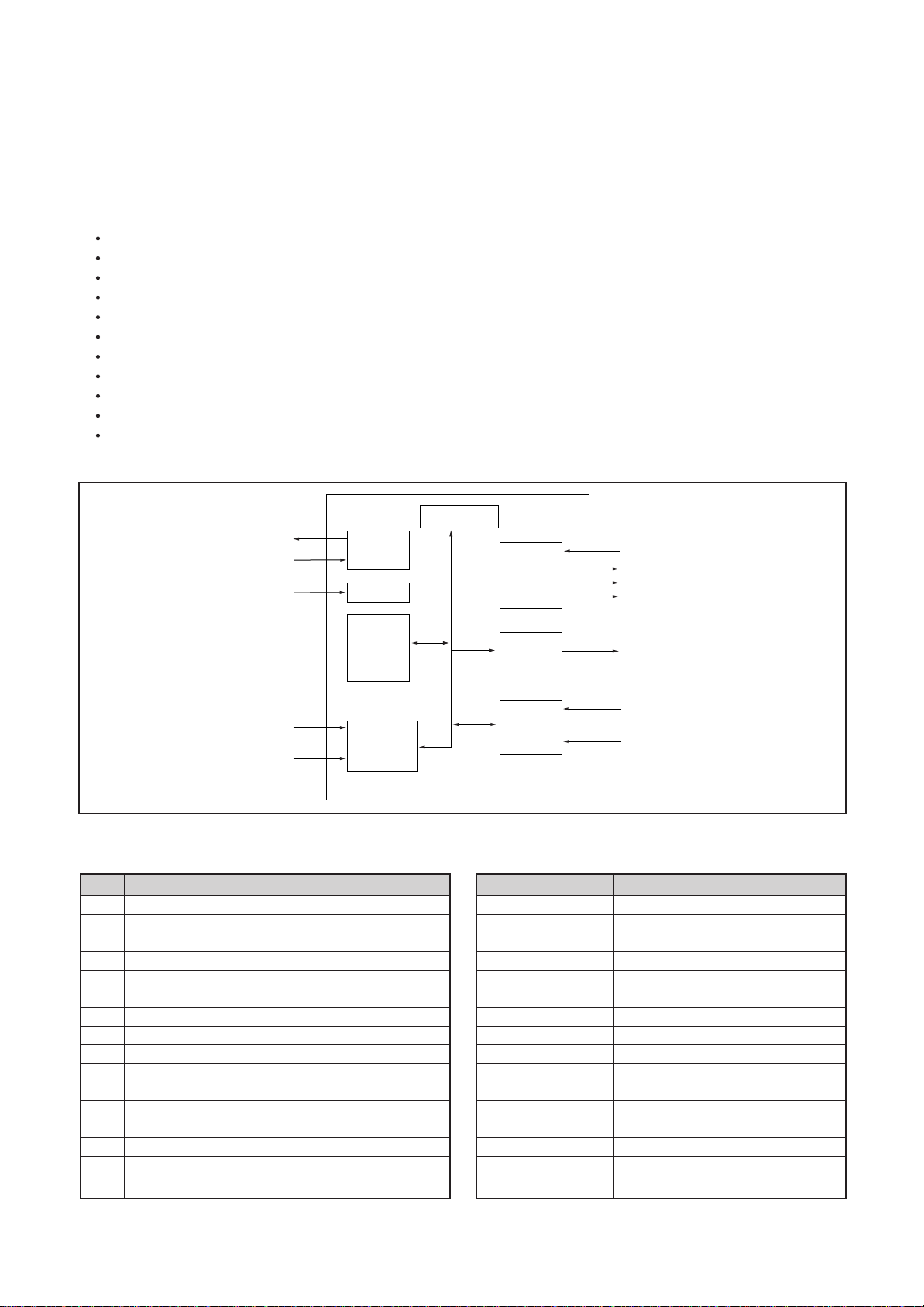

AUX TERMINAL

20 18 16 14 12 10 8 6 4 2

21 19 17 15 13 11 9 7 5 3 1

21 PIN EURO-SCART

PIN Signal Designation Matching Value

1 Audio Out(linked with 3) 0.5Vrms,lmp<1 (RF 60% MOD)

2 Audio In(linked with 6) 0.5Vrms,lmp>10

3 Audio Out(linked with 1) 0.5Vrms,lmp<1 (RF 60% MOD)

4 Audio Earth

5 Blue Earth

6 Audio in (linked with 2) 0.5Vrms,lmp>10

7 Blue in 0.7Vpp 3 ,lmp75

8 Slow(Function) Switching TV:0-2V,PERI:9.5-12V,lmp>10

9 Green Earth

10 NC

11 Green In 0.7Vpp 3 ,lmp75

12 NC

13 Red Earth

14 NC

15 Red In 0.7Vpp 3 ,lmp75

16 Rapid(Blanking) switching Logic 0:0-0.4V,Logic 1:1-3V,Imp 75

17 Video Earth

18 Rapid Blanking Earth

19 Video Out 1Vpp 3 ,lmp75

20 Video In 1Vpp 3 ,lmp75

21 Common Earth

RCA JACK

AUDIO

IN

VIDEO

OUT

3

Page 3

SAFETY INSTRUCTIONS

WARNING: BEFORE SERVICING THIS CHASSIS, READ THE "X-RAY RADIATION

PRECAUTION","SAFETY PRECAUTION" AND "PRODUCT SAFETY NOTICE" BELOW.

X-RAY RADIATION PRECAUTION

1. Excessive high voltage can produce potentially

hazardous X-RAY RADIATION.To avoid such

hazards, the high voltage must not exceed the

specified limit. The nominal value of the high

voltage of this receiver is 25.5 (21":26.5 ) at

max beam current. The high voltage must not,

under any circumstances, exceed 27.5

(21":29.0 ).

Each time a receiver requires servcing, the high

voltage should be checked following the HIGH

SAFETY PRECAUTION

1. Potentials of high voltage are present when this

receiver is operating. Operation of the receiver

outside the cabinet or with the back board

removed involves a shock hazard from the

receiver.

1) Servicing should not be attempted by anyone

who is not thoroughly familiar with the

precautions necessary when working on highvoltage equipment.

2) Always discharge the picture tube before

handling the tube. The picture tube is highly

evacuated and if broken, glass fragments will be

violently expelled.

VOLTAGE CHECK procedure on page 9 of this

manual. It is recommended the reading of the

high voltage be recorded as a part of the service

records, It is important to use an accurate and

reliable high voltage meter.

2. The only source of X-RAY Radiation in this TV

receiver is the picture tube.For continued X-RAY

RADIATION protection,the replacement tube

must be exactly the same type tube as specified

in the parts list.

2. If any Fuse in this TV receiver is blown, replace it

with the FUSE specified in the Replacement

Parts List.

3. When replacing a high wattage resistor(oxide

metal film resistor)in circuit board, keep the

resistor 10mm away from circut board.

4. Keep wires away from high voltage or high

temperature components.

5. This receiver must operate under AC230 volts,

50Hz. NEVER connect to DC supply or any other

power or frequency.

PRODUCT SAFETY NOTICE

Many electrical and mechanical parts in this have

special safety-related characteristics. These

characteristics are often passed unnoticed by a

visual inspection and the X-RAY RADIATION

protection afforded by them cannot necessarily be

obtained by using replacement components rated

for higher voltage,wattage,etc. Replacement parts

which have these special safety characteristics are

identified in this manual and its supplements,

electrical components having such features are

identified by designated symbol on the parts list.

Before replacing any of these components, read the

parts list in this manual carefully. The use of

substitute replacement parts which do not have the

same safety characteristics as specified in the parts

list may create X-RAY Radiation.

5

Page 4

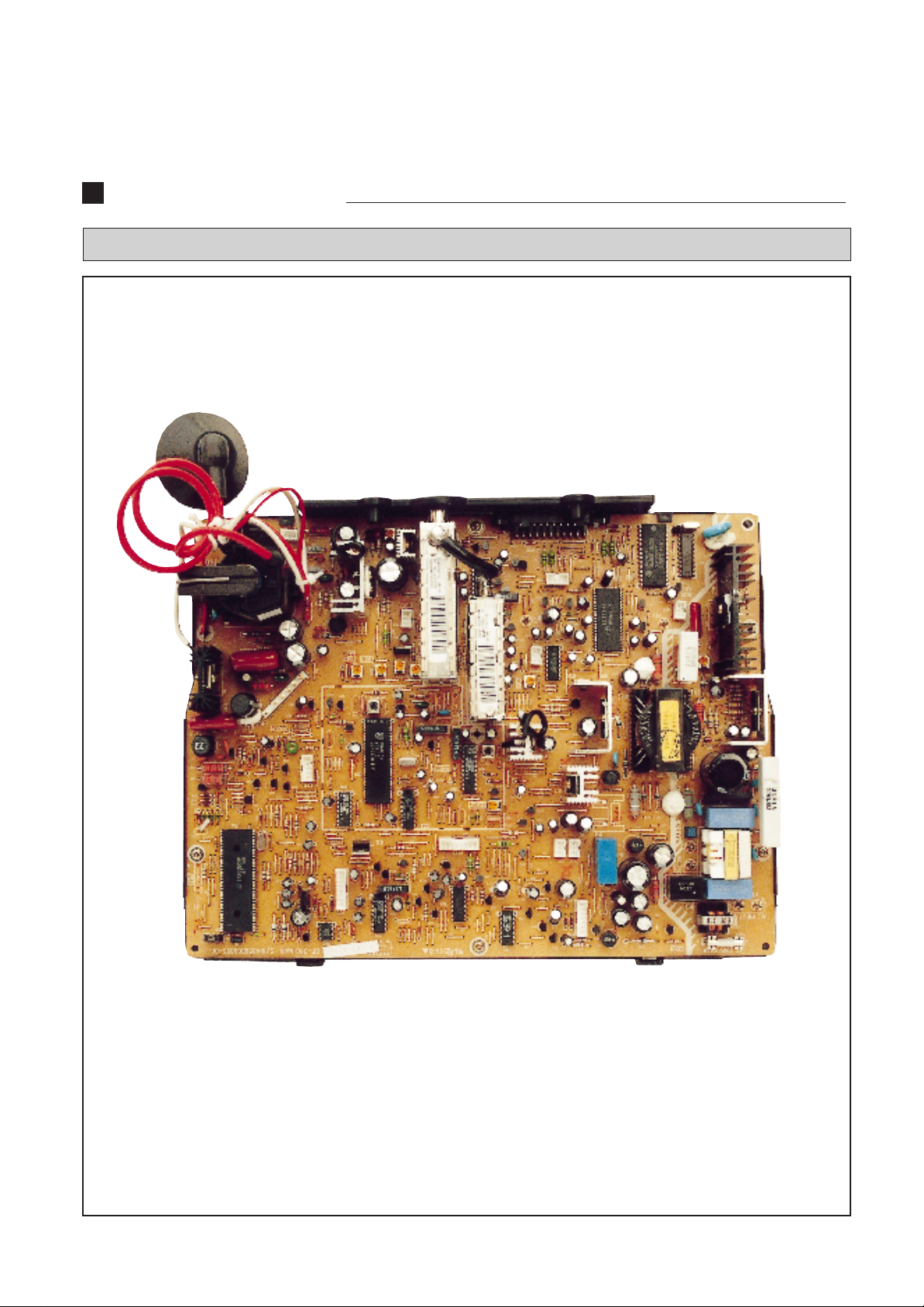

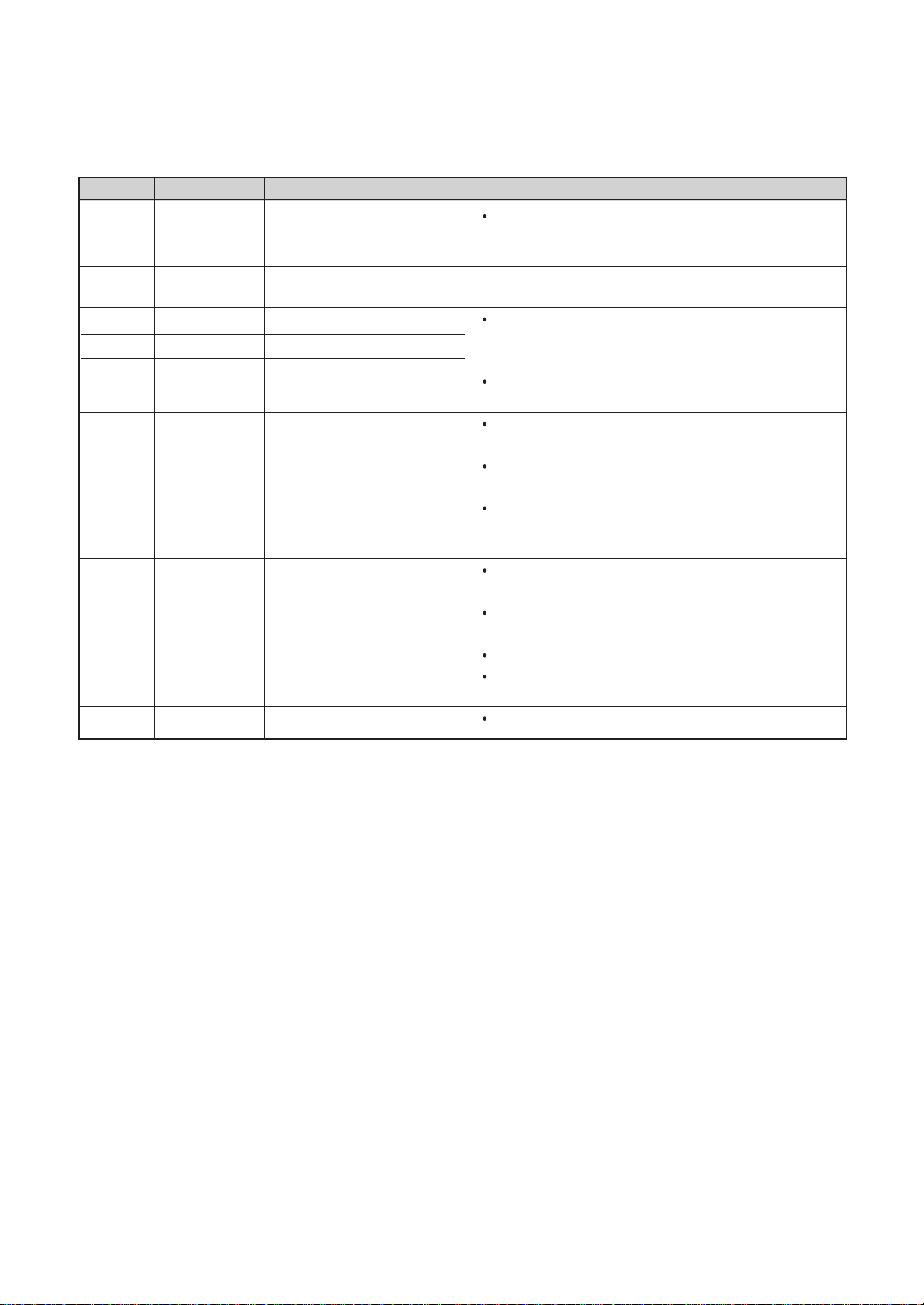

ASSEMBLY VIEW

MAIN BOARD VIEW

6

Page 5

INSTALLATION & SERVICE ADJUSTMENTS

GENERAL INFORMATION

All adjustments are thoroughly checked and

corrected when the receiver leaves the factory.

Therefore the receiver should operate normally

and produce proper colour and B/W pictures upon

installation. But, several minor adjustments may

be required depending on the particular location in

which the receiver is operated. This receiver is

shipped completely in a card-board carton.

Carefully draw out the receiver from the carton

and remove all packing materials.

Plug the power cord into an AC power outlet. Turn

the receiver ON and adjust the FINE TUNING for

the best picture detail. Check and adjust all the

customer controls such as BRIGHTNESS,

CONTRAST and COLOUR Controls to obtain a

natural B/W picture.

PROTECTION CIRCUIT CHECK

1. Turn on the receiver.

2. The receiver must be turned off and changed to

stand-by mode.

HIGH VOLTAGE CHECK

1. Connect an accurate high voltage metre to the

anode of the picture tube.

2. Turn on the receiver. Set the BRIGHTNESS

and CONTRAST controls to minimum(zero

beam current).

3. High voltage should be below 27.5 (21":29.5 )

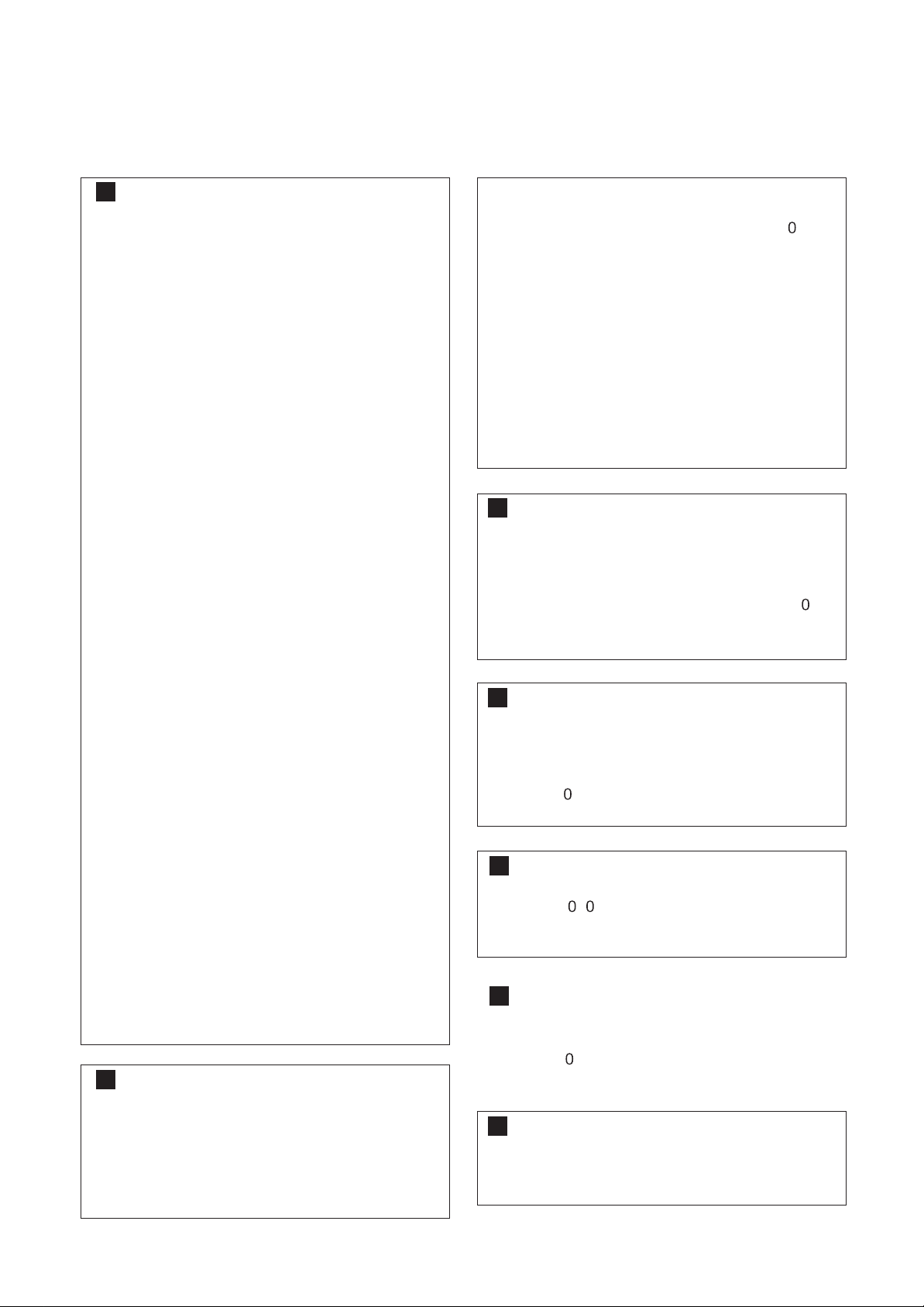

DYNAMIC CONVERGENCE

ADJUSTMENT

Dynamic convergence (convergence of the three

colour field at the edges of the CRT screen)is

accomplished by proper insertion and positioning

of three rubber wedges between the edges of the

deflection yoke and the funnel of the CRT. This is

accomplished as follows:

1. Switch the receiver on allow it to warm up for 15

minutes.

2. Apply crosshatch pattern from dot/bar generator

to the receiver. Observe spacing between lines

around edges of the CRT screen.

3. Tilt the deflection yoke up and down, and insert

tilt adjustment wedges 1 and 2 between the

deflection yoke and the CRT until the misconvergence illustrated in figure. 2(A) has been

corrected.

4. Tilt the deflection yoke right and left, and insert

tilt adjustment wedge 3 between the deflection

yoke and the CRT until mis-convergence

illustrated in figure. 2(B) has been corrected.

5. Alternately change spacing between, and depth

of the insertion of, the three wedges until proper

dynamic convergence is obtained.

6. Use a strong adhesive tape to firmly secure

latch of the three rubber wedges to the funnel of

the CRT.

7. Check purity and readjust, if necessary.

AUTOMATIC DEGAUSSING

A degaussing coil is mounted around the picture

tube so that external degaussing after moving the

receiver is normally unnecessary. Providing the

receiver is properly degaussed upon installation.

The degaussing coil operates for about 1 second

after the power of the receiver is switched ON.If the

set is moved or placed in a different direction, the

power switch must be switched off for at least 15

minutes in order to make the automatic degaussing

circuit operate properly.

Should the chassis or parts of the cabinet become

magnetized to cause poor colour purity,use an

external degaussing coil. Slowly move the

degaussing coil around the faceplate of the picture

tube, the sides and front of the receiver and slowly

withdraw the coil to a distance of about 2m before

disconnecting it from the AC source.

If colour shading still persists, perform the COLOUR

PURITY ADJUSTMENT and CONVERGENCE

ADJUSTMENTS procedures, as mentioned later.

STATIC (CENTRE) CONVERGENCE

ADJUSTMENT

1. Switch the receiver on and allow it to warm up for

15 minutes.

2. Connect the output of a crosshatch generator to

the receiver and concentrating on the centre of the

CRT screen, proceed as follows:

a. Locate the pair of 4 pole magnet rings. Rotate

individual rings (Change spacing between tabs)to

converge the vertical red and blue lines.Rotate the

pair of rings (maintaing spacing between tabs)to

converge the horizontal red and blue lines. (Refer to

fig. 1 (A))

b. After completing red and blue centre

convergence, locate the pair of 6 pole magnet rings.

Rotage individual rings (change spacing between

tabs) to converge the vertical red and blue

(Magenta)and green lines. Rotate the pair of rings

(maintaining spacing between tabs)to converge the

horizontal red and blue(Magenta) and green

lines.(Refer to Fig. 1(B))

8

Page 6

COLOR PURITY ADJUSTMENT

For the best result,it is recommended that the

purity adjustment is made in final receiver

location. If the receiver will be moved, perform

adjustment with it facing east. The receiver must

have been operating 15 minutes prior to this

procedure and the faceplate of the CRT must be

at room temperature. The receiver is equipped

with an automatic degaussing circuit. But, if the

CRT shadow mask has become excessively

magnetized, it may be necessary to degauss it

with manual coil. Do not switch the coil.

The following procedure is recommended while

using a dot generation.

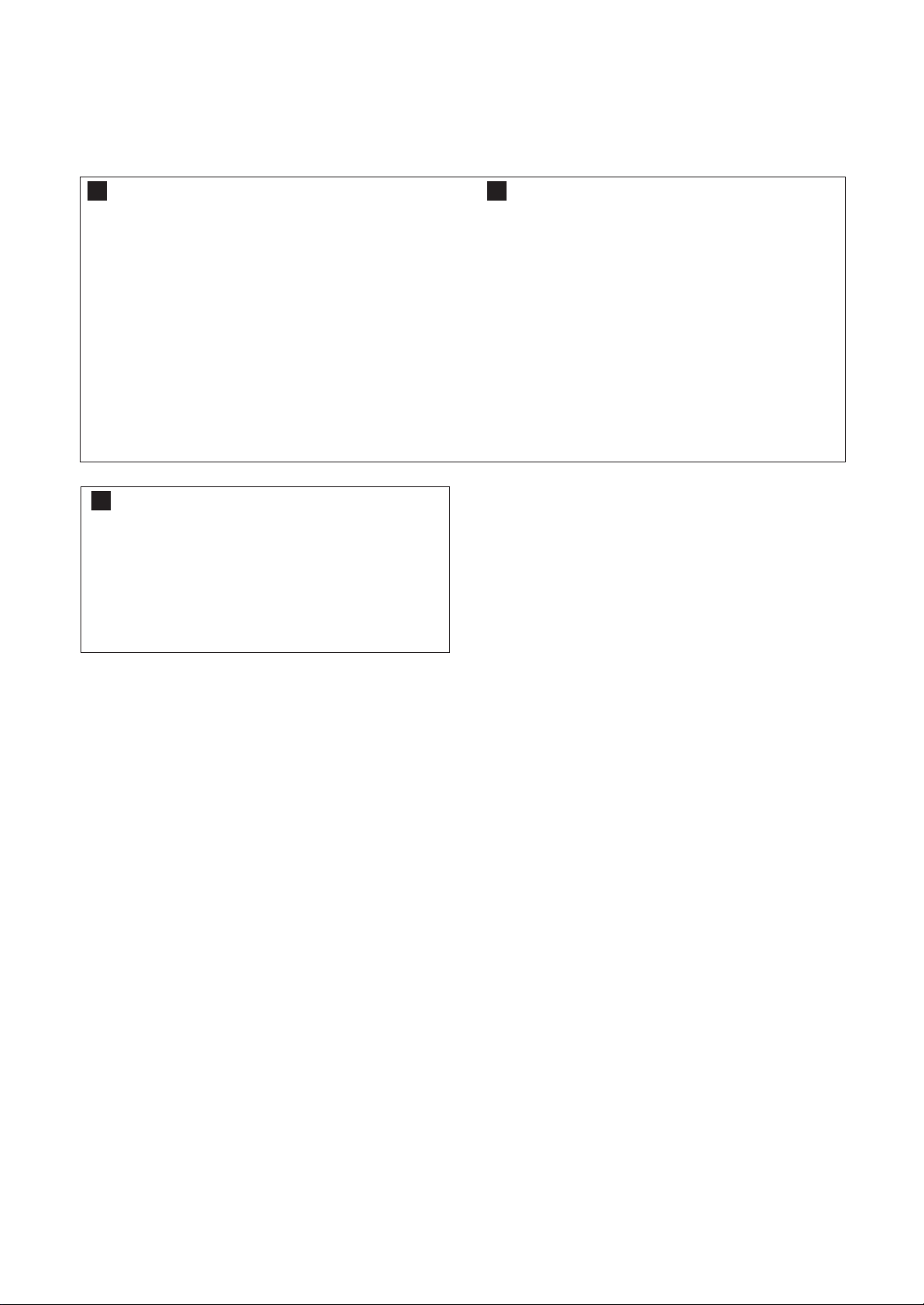

1. Check for correct location of all neck

components (See figure. 5).

2. Rough-in the static convergence at the centre

of the CRT, as explained in the static

convergence procedure.

3. Rotate the picture control to centre of its

rotation range, and rotate brightness control to

max. CW position.

4. Apply green color signal to produce a green

raster.

5. Loosen the deflection yoke tilt adjustment

wedges (3), loosen the deflection yoke clamp

screw and push the deflection yoke as close as

possible to the CRT screen.

6. Begin the following adjustment with the tabs on

the round purity magnet rings set together,

initially move the tabs on the round purity

magnet rings to the side of the CRT neck.

Then, slowly separate the two tabs while at the

same time rotaing them to adjust for a uniform

green vertical band at the CRT screen.

7. Carefully side the deflection yoke backward to

achieve green purity. (uniform green screen)

Centre purity was obtained by adjusting the

tabs on the round purity magnet rings, outer

edge purity was obtained by sliding the

deflection yoke forward.

Tighten the deflection yoke clamp screw.

8. Check for red and blue field purity by applying

red signal and touch up adjustments, if

required.

9. Perform black and white tracking procedure.

SCREEN & WHITE BALANCE

ADJUSTMENT

1. This adjustment is to be made only after

warming up at least 15 minutes.

2. Receive RETMA pattern signal.

3. Set the RGB Bias VR (R522,R512,R502) to

minimum.

4. Set the G,B Drive VR (R515,R505)to center.

5. Set the CONTRAST, BRIGHTNESS, COLOR

control to MIN, and Sub-bright VR(R 13)to

CENTER.

6. Rotate the R, G and B Bias VR of the other

color which did not appear on the screen

clockwise, until a dim white is obtained.

7. Set the CONTRAST, BRIGHTNESS, COLOR

control to MAX.

8. Set the G, B Drive VR to obtain the best white

uniformity on the screen.

9. Rotate the CONTRAST, BRIGHTNESS,

COLOR controls until a dim raster is obtained

and touch-up adjustment of RGB Bias VR to

obtain the best white uniformity on the screen.

SUB-BRIGHTNESS ADJUSTMENT

1. White balance adjustment must proceed this

procedure.

2. Set the CONTRAST, BRIGHTNESS, COLOR

control to MIN.

3. Rotate the SUB-BRIGHTNESS VR (R 13)

gradually CCW until the last beam disappears

on the screen.

VERTICAL HEIGHT ADJUSTMENT

1. Receive RETMA pattern signal.

2. Set the BRIGHTNESS control and CONTRAST

control to Max., and the COLOR control to

centre.

3. Adjust R 11 for the optimum vertical height and

over scanning.

VERTICAL CENTER ADJUSTMENT

1. Receiver RETMA pattern signal.

2. Adjust R 3 so that the vertical center of the

picture may be coincident with the mechanical

center of CRT.

HORIZONT AL CENTER

ADJUSTMENT

1. Receive RETMA pattern signal.

2. Adjust R 12 so that the horizontal center of the

picture may be coincident with the mechanical

center of CRT.

FOCUS VOLTAGE ADJUSTMENT

1. Receive RETMA pattern signal.

2. Adjust the FOCUS VOLUME on the FBT and

make the picture on the screen be finest.

9

Page 7

RF AGC ADJUSTMENT(MAIN)

RF AGC ADJUSTMENT(SUB)

1. Receive PAL COLOR BAR signal in the VHF

high band where the strength of signal can be

75dB.

2. Set the CONTRAST control to Max., the

BRIGHTNESS control to provide adequate black

and gray scales.

3. Connect an oscilloscope to P211.(Tuner AGC

point)

4. Maintain the fine tuning on the screen, and adjust

R010(AGC DELAY CONTROL VR.) to max.

5. Adjust the VR(R010) max to below

2.2V(FA/LA:2.2V).

MAIN B+(+103V) ADJUSTMENT

1. Set the picture level to service 1

mode.(Bright:31, Colour:31, Contrast:48,

Sharpness:48)

2. Connect DC voltage meter to the P805 and

adjust R080 for +103V DC.

1. Receive PAL COLOR BAR signal in the VHF

high band where the strength of signal can be

75dB.

2. Set the CONTRAST control to Max., the

BRIGHTNESS control to provide adequate black

and gray scales.

3. Connect an oscilloscope to P211.(Tuner AGC

point)

4. Maintain the fine tuning on the screen, and adjust

R090(AGC DELAY CONTROL VR.) to max.

5. Adjust the VR(R090) max to below

2.2V(FA/LA:1.6V).

10

Page 8

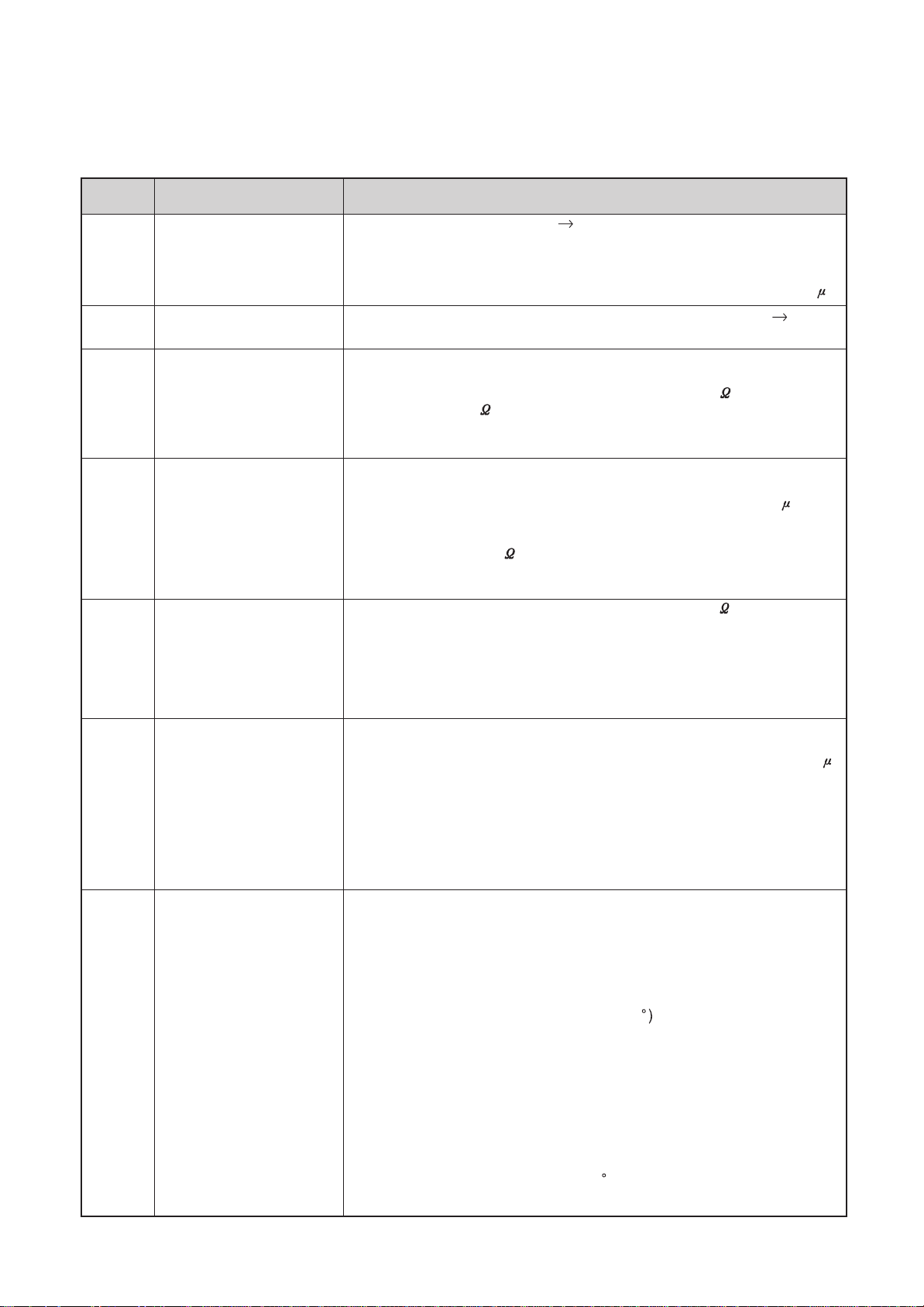

BLUE

RED

RED/BLUE

GRN

ADJUST THE

ANGLE

(VERTICAL

LINES)

BLUE

RED

RED/BLUE

GRN

(A)

4-Pole Magnets Movement

6-Pole Magnets Movement

FIG. 1 CENTER CONVERGENCE BY CONVERGENCE MAGNETS

B G R

R

G

B

R G B

B

G

R

(A)

Incline the Yoke up (or down)

B

G

R

BGR

Incline the Yoke right (or left)

FIG. 2 CIRCUMFERENCE CONVERGENCE BY DEF .YOKE

CONSTANT

(B)

(B)

R

G

B

BGR

WEDGE1

ROTATE TWO TABS AT

THE SAME TIMER

(HORIZONTAL LINES)

ADJUSTMENT OF MAGNETS

WEDGE2

DEFLECTION YOKE REAR VIEW

WEDGE3

FIG. 3 ADJUSTMENT OF MAGNETS FIG. 4 RUBBER WEDGE LOCATION

DEFLECTION

YOKE CLAMP

RUBBER

WEDGES

TAPE

SCREW

DEFLECTION YOKE

TILT ADJUSTMENT WEDBE

PURITY MAGNETS

6 POLE CONV

MAGNETS

4 POLE CONV

MAGNETS

FIG. 5 PICTURE TUBE NECK COMPONENT

11

Page 9

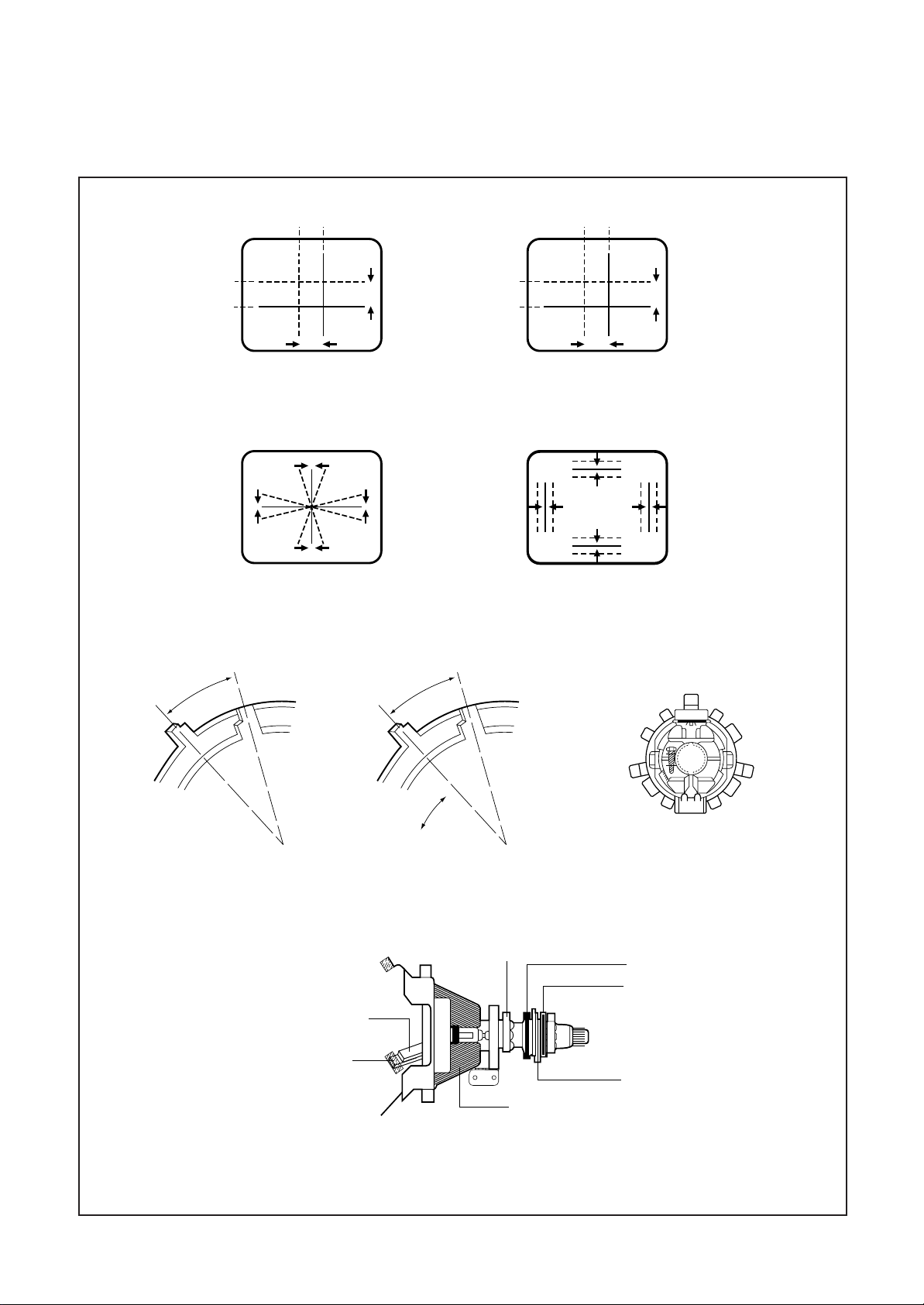

PIF ADJUSTMENT(MAIN)

1. APPARATUS CONNECTION AND

PRESETTING

CONNECTION

1) Connect H-out of LSW-480 to X-axis of the

oscilloscope and V-out of LSW-480 to Yaxis of the oscilloscope.

2) Connect the sweep signal output to TP1.

3) Set ATTENUATOR of LSW-480 to 10dB.

4) Supply 12V DC voltage(B+) to TP4 and

TP6.

5) Supply 4-5V DC voltage to TP3.

PRESET

1) Oscilloscope Scaling

a) Put the scale of X and Y of the oscilloscope

to DC level.

b) Set the horizontal time display to X-Y.

c) Put the horizontal axis(X) to 1V/div. And the

vertical axis(Y) to 2V/div.

2) LSW-480 MARKER FREQ. SETTING.

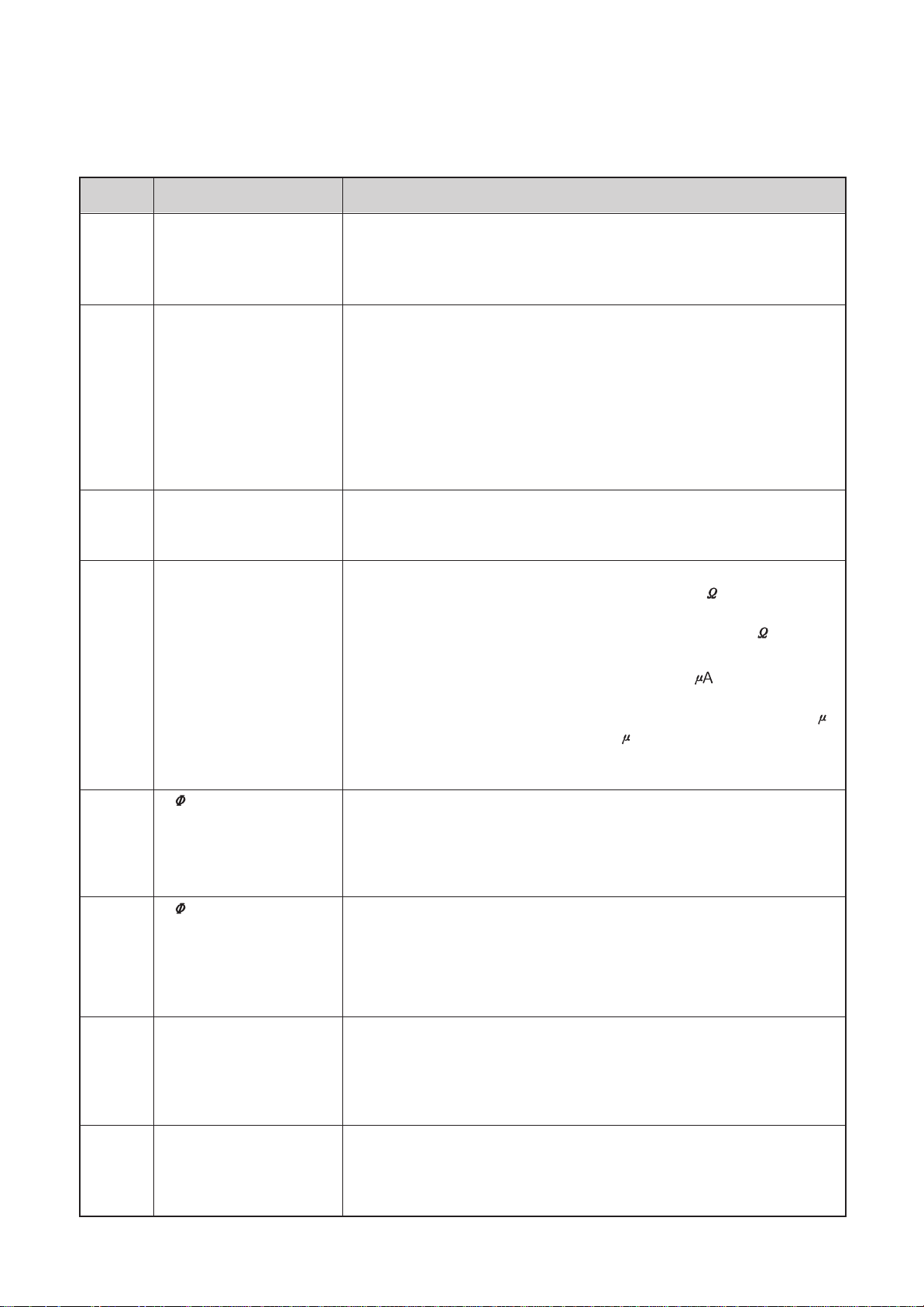

Fp(n+1) fs fc fp-2 fp fs(n-1)

B/G,L/L' 31.9 33.4 34.5 36.9 38.9 40.4

I 31.9 33.5 35.07 37.5 39.5 41

(ADJUSTMENT OF L')

T.P

PIF SWEEP MARKER

GENERATOR

(LSW-480,480-U80)

OUTPUT

V-Scope H-Scope

OSCILLOSCOPE

X

Y

Connection For PIF Adjustment

TP5 (Q205 COLLECTOR) GND

TP2 (AFT,I201 #44)

TP1 (U1, IF1)

TP4 (1717 #1) TP6(C727) TF3 (I201 #48)

(B+) (IF AGC)

14V

DC

POWER SUPPLY

2. ADJUSTMENT OF AFT(B/G, I, L)

1) Connect the test point of LSW-480 to TP2.

2) Adjust L201(AFT COIL) so that the P marker

point is located on the reference level.

MAIN PCB

Through a 4.7K resistor

4-5V

DC

POWER SUPPLY

B/G, L : 38.9MHz

I : 39.5MHz

P

3. ADJUSTMENT OF SECAM-L' AFT

1) Connect the TP5 (Q205 collector) to GND.

2) Adjust C200(L'AFT TRIMMER) so that the C

marker point (34.5MHz) is located on the

reference level.

AFT WAVEFORM

L' : 34.5MHz

C

L'AFT WAVEFORM

12

Page 10

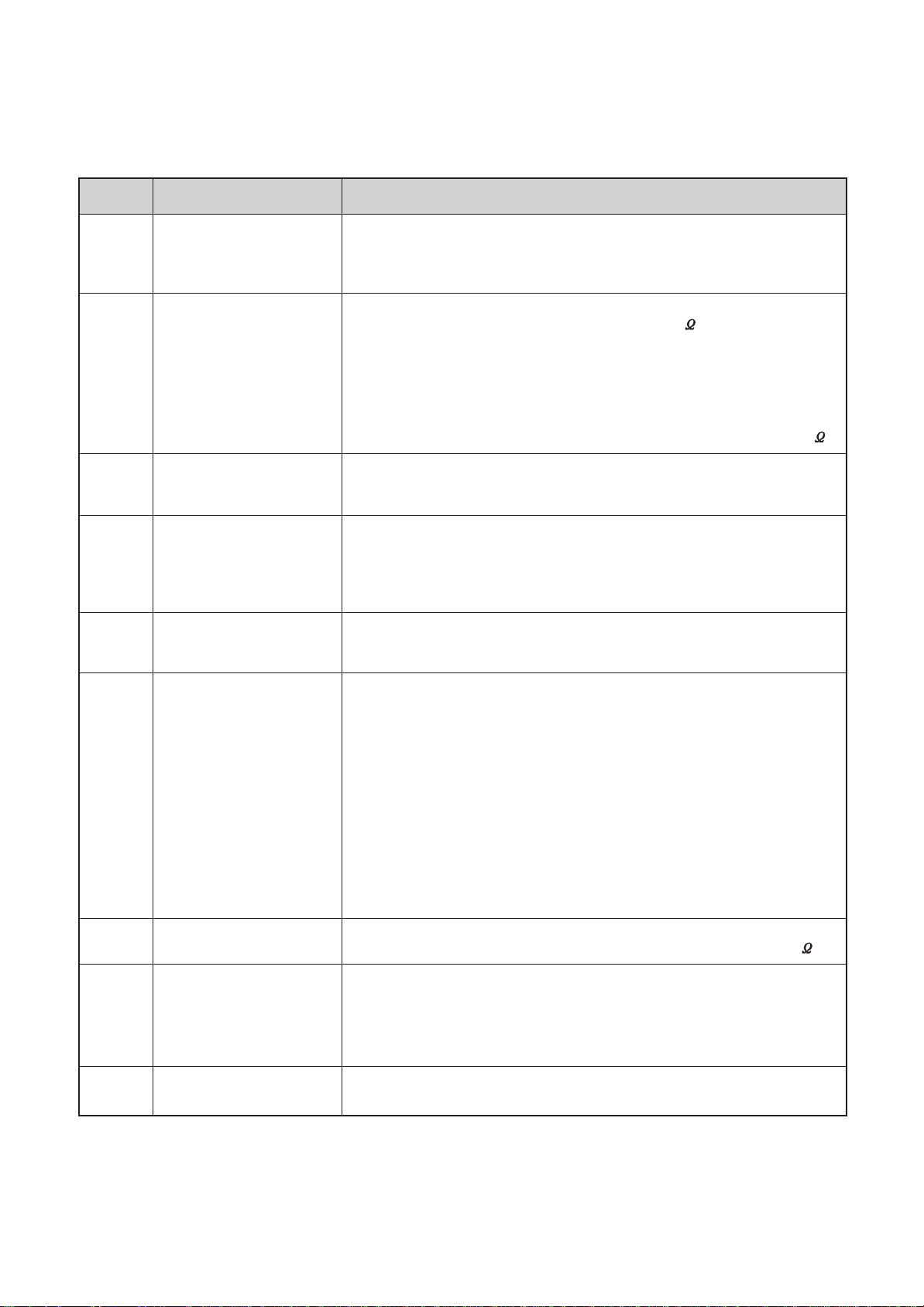

PIF ADJUSTMENT(SUB)

1. APPARATUS CONNECTION AND

PRESETTING

CONNECTION

1) Connect RF-out of PM5518 to TP7.

2) Connect DC voltage meter to TP8.

3) Supply 14V DC voltage(B+) to TP4 and TP6.

PM5518

PATTERN

GENERATOR

RF OUTPUT

TP7 (U2, IF1)

TP8 (I901 #15)

PRESET

1) PM5518 SETTING

Freq. (MHz) Remark

B/G,L 38.9 FA/LA

I 39.5 PA

L' 34.5 LA

MAIN PCB

DIGITAL

MULTIMETER

Connection For PIF Adjustment

2. ADJUSTMENT OF AFT(B/G, I, L)

1) Connect the DC voltage meter to TP8.

2) Adjust L902(AFT COIL) for 2.2±0.1V.

TP4 (I717 #1) TP6(C727) TP9 (Q904 BASE)

Through a 22K resistor

(ADJUSTMENT OF L')

14V

DC

POWER SUPPLY

5V

DC

POWER SUPPLY

3. ADJUSTMENT OF SECAM-L' AFT

1) Supply 5V DC voltage to TP9.

2) Connect the DC voltage meter to TP8.

3) Adjust R091(L'AFT VR.) for 2.2±0.1V

13

Page 11

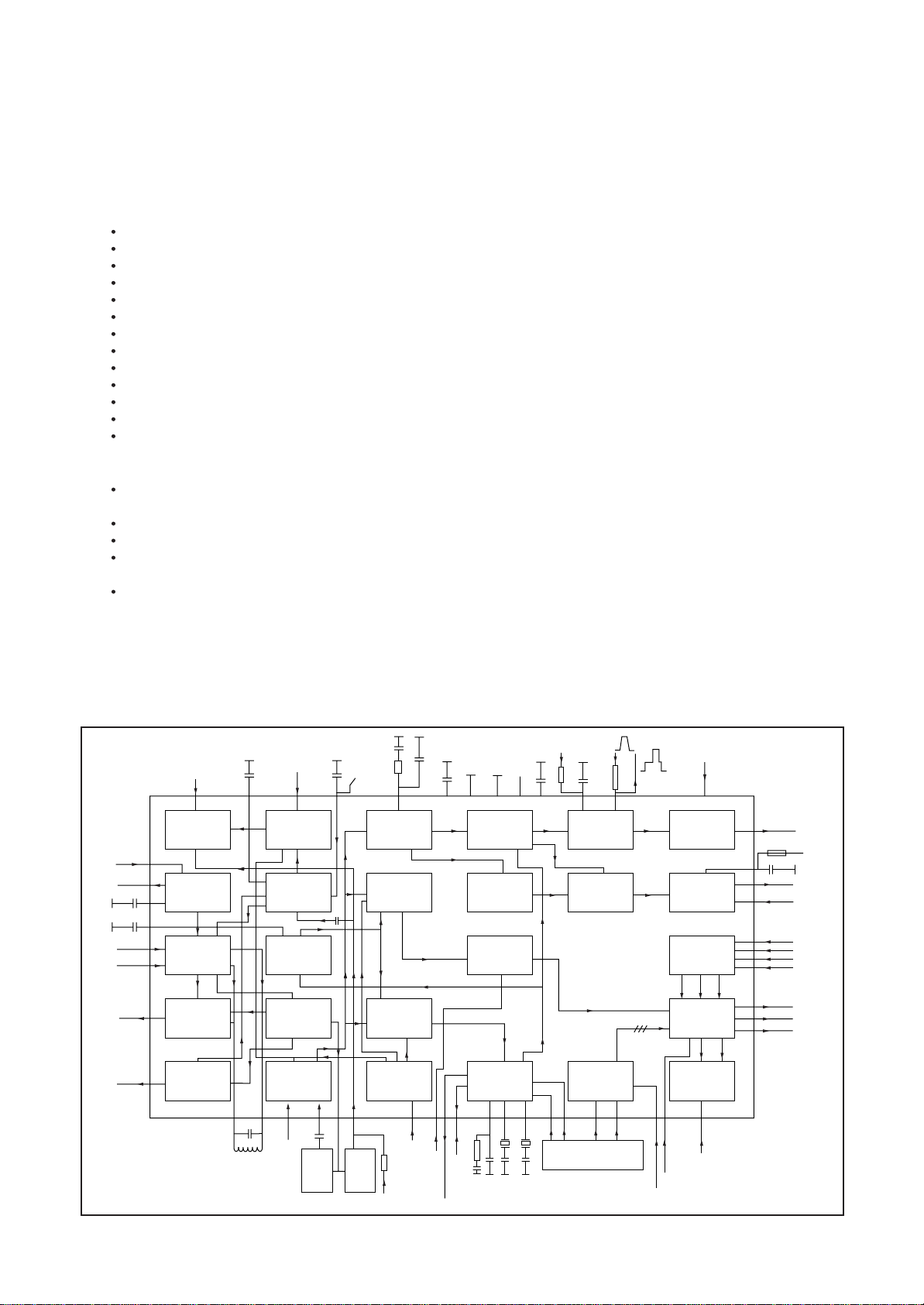

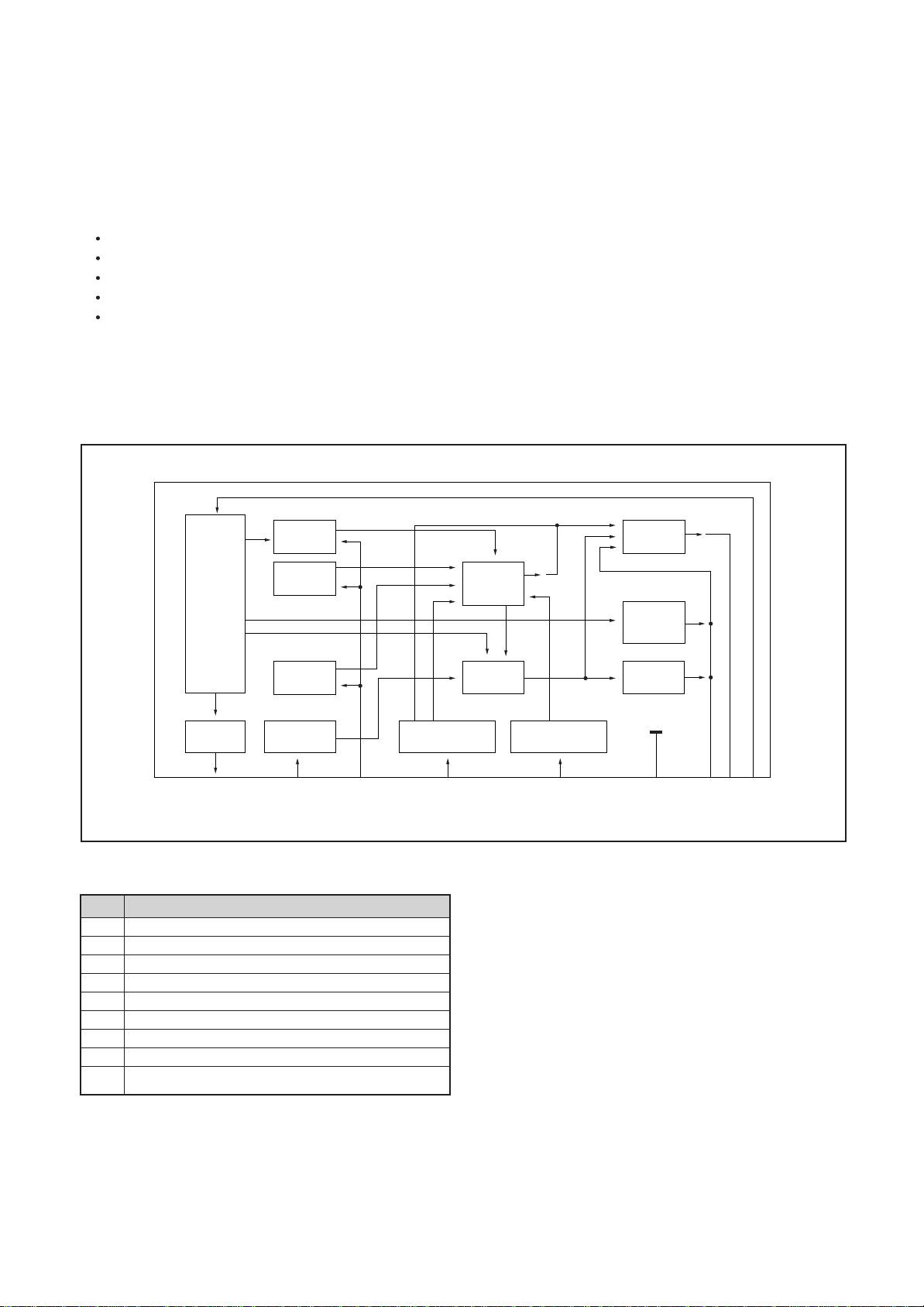

IC OPERATION DESCRIPTION

M37206MC-xxxSP (Micro-controller)

(1) General Description

It is a one-chip micro-controller with an 8-bit CPU.

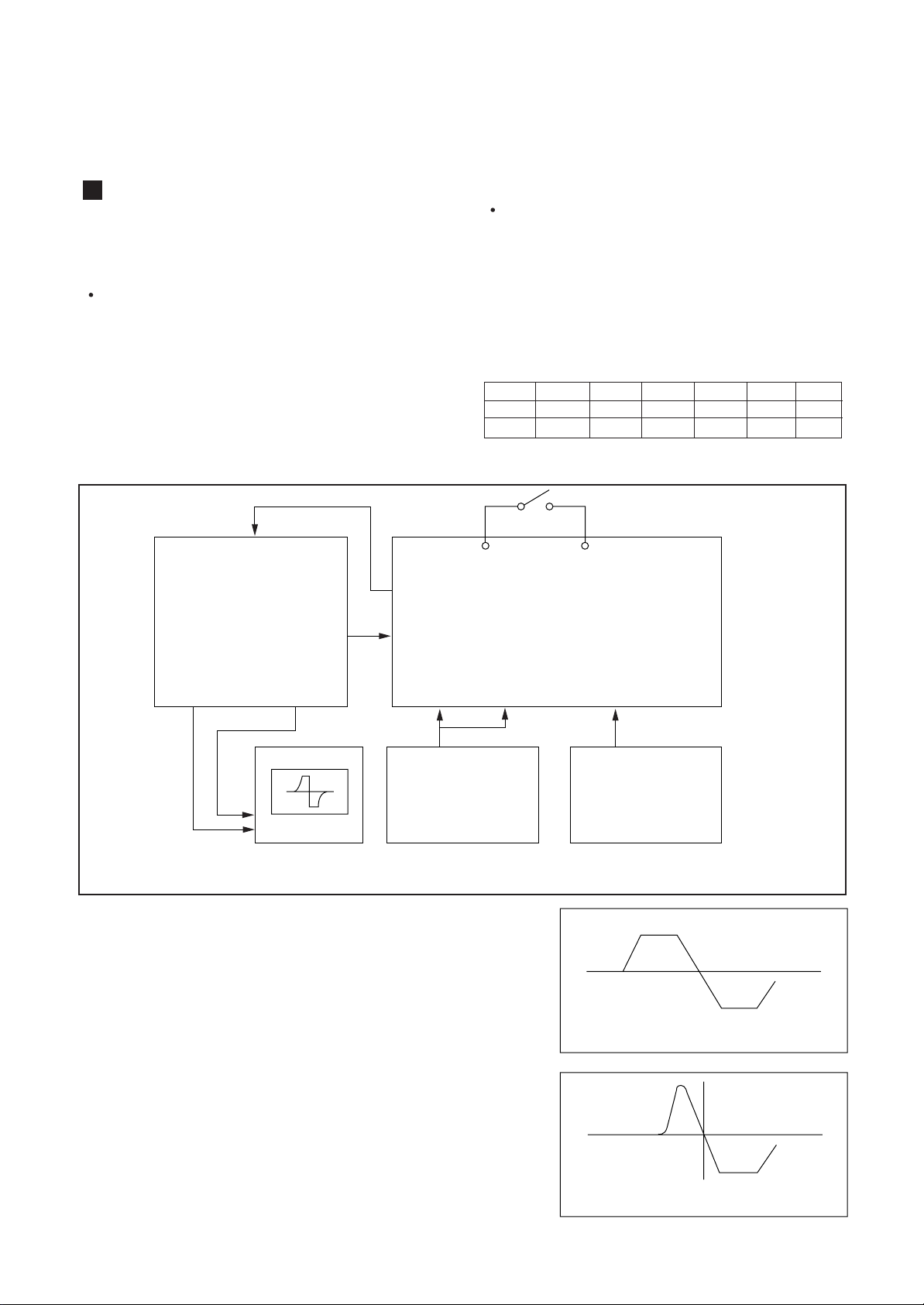

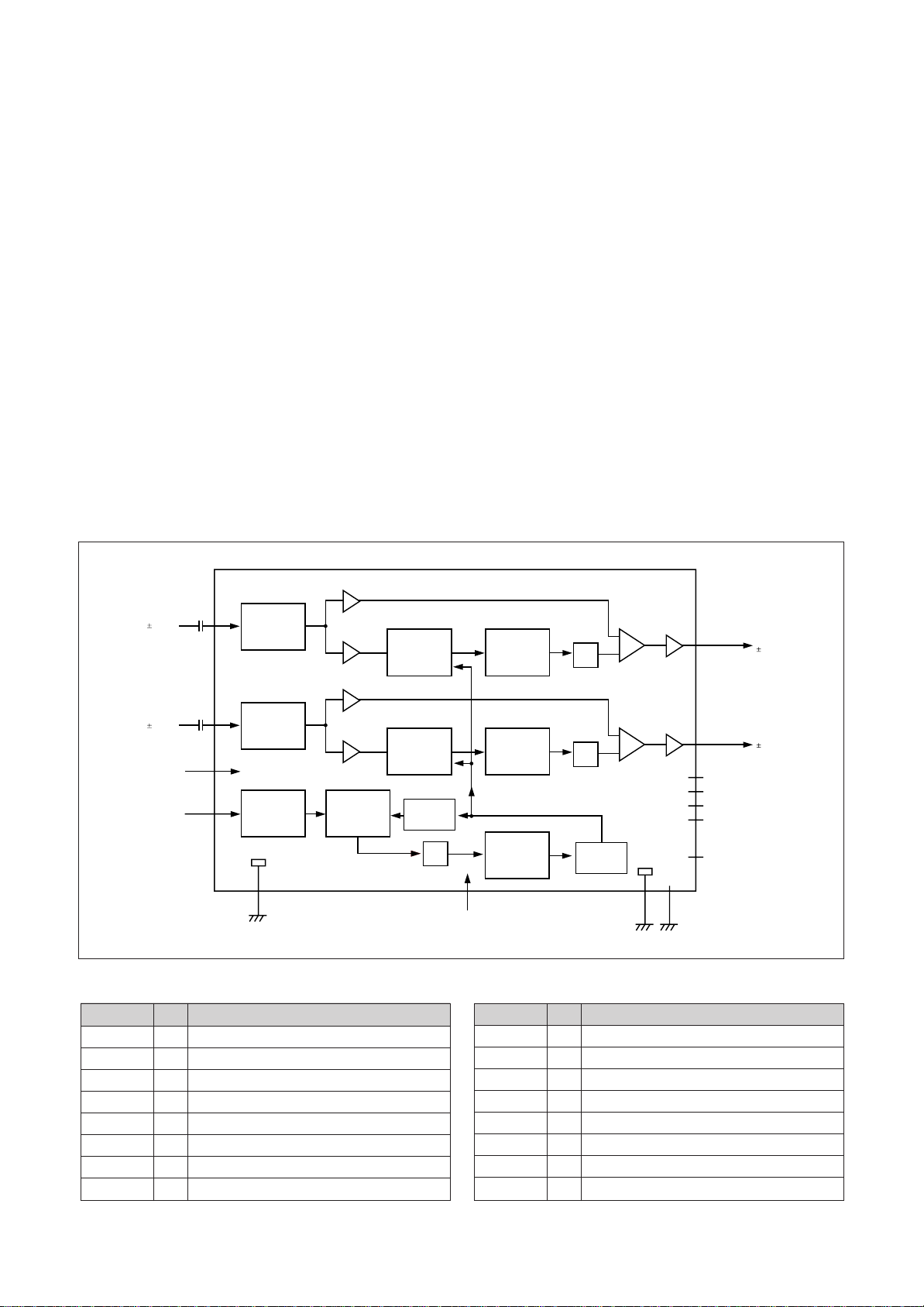

(2) Functional Block Diagram

OSD OSC

OSD OSC

(PULL UP) PIF MUTE

AFT IN1

P.F IN(L)

AFT IN2

(PULL UP) VOLUMOUT

(PULL UP)CONT. OUT

(PULL UP)BRIGHT OUT

(PULL UP)COLOUR OUT

(PULL UP)PEAKING OUT

(PULL UP)TINT OUT

(PULL UP)L1' OUT

(PULL UP)L2' OUT

TEXT1 USE

TEXT2 LANG

TEXT3 LANG

SYS OSD

SECAML

SYNC1 "H"

(PULL UP) IIC CLK

(PULL UP) IIC DATA

(IDENT) SYNC LOW IN

(PULL UP) SERIAL IN

(PULL UP) SERIAL CLK

(PULL UP) SERIAL OUT

GND

GND

RESET(L)

8.0 MHz

8.0 MHz

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

OSC1

OSD2

P MUTE

AFT1

P.F IN

AFT2

VOL. PWM

CONT. PWM

BRI. PWM

COL. PWM

PEA. PWM

TINT. PWM

L1' OUT

L2' OUT

OP.8

OP.9

OP.10

OP.11

OP.12

SYNCI

SCL

SDA

SYNC. L

SD_IN

SD_CLK

SD_OUT

GND

GND

RESET

XIN

XOUT

GND

Vcc

H. SYNC

V. SYNC

BLK

TV 1/2

SYS1

SYS2

V MUTE

S MUTE

TV PWR

DISABLE

A/V1

A/V2'

A/V1'

SCIN

A/V

OP. 7

OP. 6

OP. 5

OP. 4

OP. 3

OP. 2

OP. 1

XCOUT

XCIN

+ 5V

64

H.SYNC INPUT

63

V.SYNC INPUT

62

R

G

B

R OUT

61

GUT

60

B OUT

59

NC

58

BLANKING OUT

57

TV 1/2 SEL OUT

56

STSTEM1 OUT

55

SYSTEM2 OUT

54

53

52

51

V MUTE OUT

50

SPEAKER MUTE

49

TV POWER ON/OFF

48

DISABLE

47

A/V1 SEL OUT

46

A/V2' SEL OUT

45

A/V1' SEL OUT

44

SCART IN (S/SW)

43

A/V SEL OUT

42

VPS/PDC

41

CLK TEST

40

POWER ON START

39

SHOWVIEW

38

AV2

37

U BAND

36

TAPE SPEED

35

32.768 KHz

34

32.768 KHz

33

14

Page 12

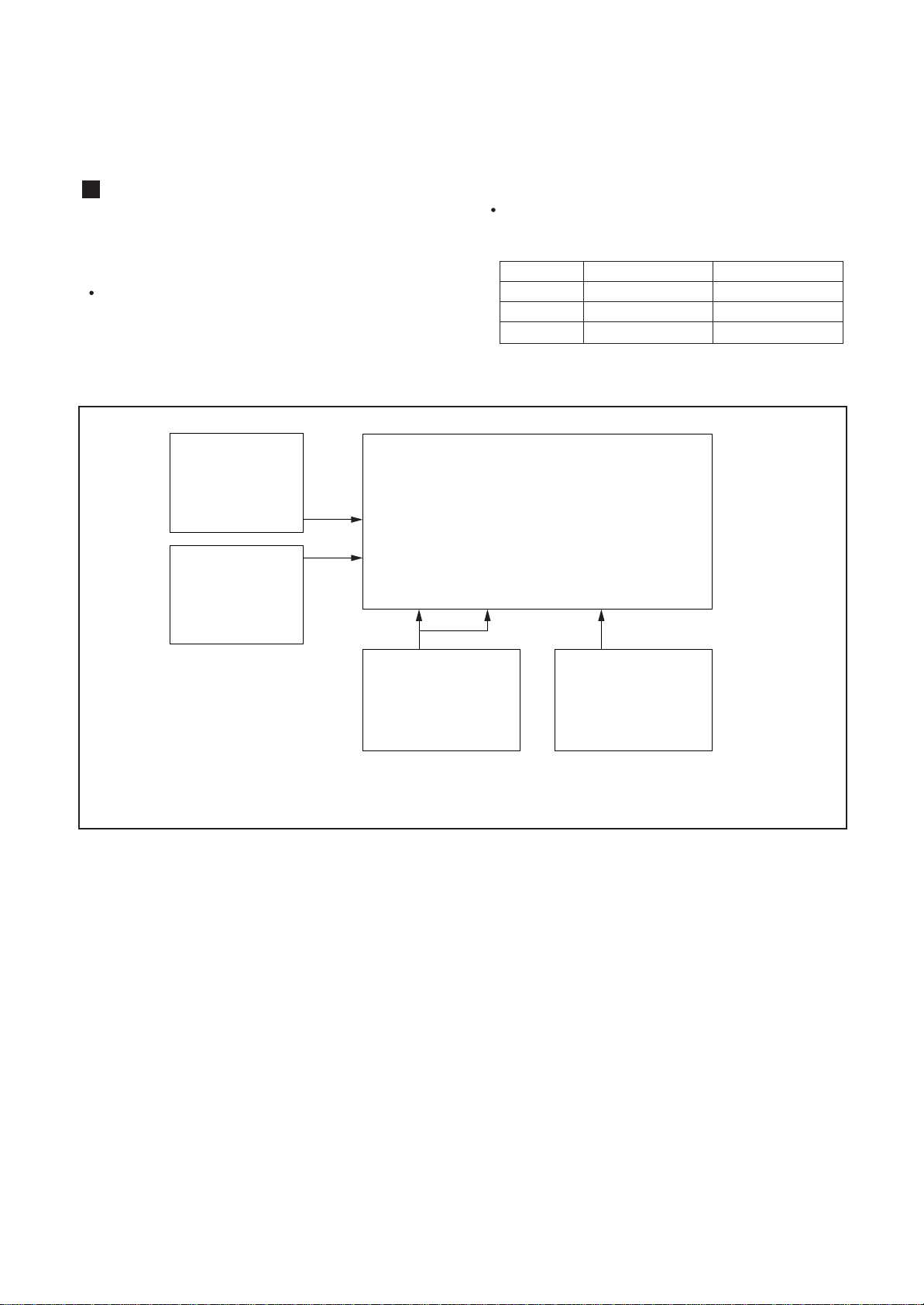

(3) Functional Block Diagram

Pin No. Symbol Name Function Description

1 OSC IN Oscillator for OSD OSD (On Screen Display)

2 OSC OUT

3 P MUTE PIF MUTE Not used

4 AFT1 ADC Input

5 P.F INPUT POWER FAIL Input Power fail detect input.

6 AFT2 ADC Input Input AFT signal from SUB TUNER with level

7 VOL Volume Control Output

8 CON Contrast Control Output

9 BRI Brightness Control Output

10 COL Colour Control Output

11 PEA Peaking Control Output

12 TINT Tint Control Output

13 L1' L1' Output(SECAM)

14 L2' L2' Output(SECAM)

15 OP. 8 Text use Option

16 OP. 9 TURKISH Option Not used

17 OP.10 EAST Option Not used

18 OP.11 System OSD Option SECAM Only

19 OP.12 SECAM-L Option

20 SYNC1 Sync Ident Input

21 SCL Clock Pin for IIC(O)

22 SDA Data Pin for IIC(I/O)

23 SYNC L Sync Low Sync low input (Ident) from SUB TUNER

24 SD IN Syscon serial DATA input

25 S CLK Syscon serial CLOCK out

26 SD OUT Syscon serial DATA out

27 GND GND

Comparison voltage input terminal connected to

built-in comparator.

Input AFT signal from MAIN TUNER with level

conversion (0 to Vdd)

The results of the comparison are used when the

auto search and digital AFT works.

conversion ( 0 to Vdd)

Output the pulse width modulated signal in 63 level

in accordance with 6-bit latch data.

Input terminal of image synchronous signal

necessary for auto search and AFT operation.

In the case of the determination of the level signal

synchronization, the signal state ("H" or "L") which

is input at this terminal is determined every 4ms.

"H" ------------ Presence of synchronization

"L" ------------ Absence of synchronization

Pin SCL and SDA are respectively the data and

clock wire or the multi-master two-wire bidirection

IIC-bus control bus.

If a transmission does not succeed the controller

will retry it for up to 5 times. If the bus is occupied

for longer than 1.18 seconds the u-controller will

generate bursts of nine clock pulses with intervals

of 1.18 seconds until bus is free again.

15

Page 13

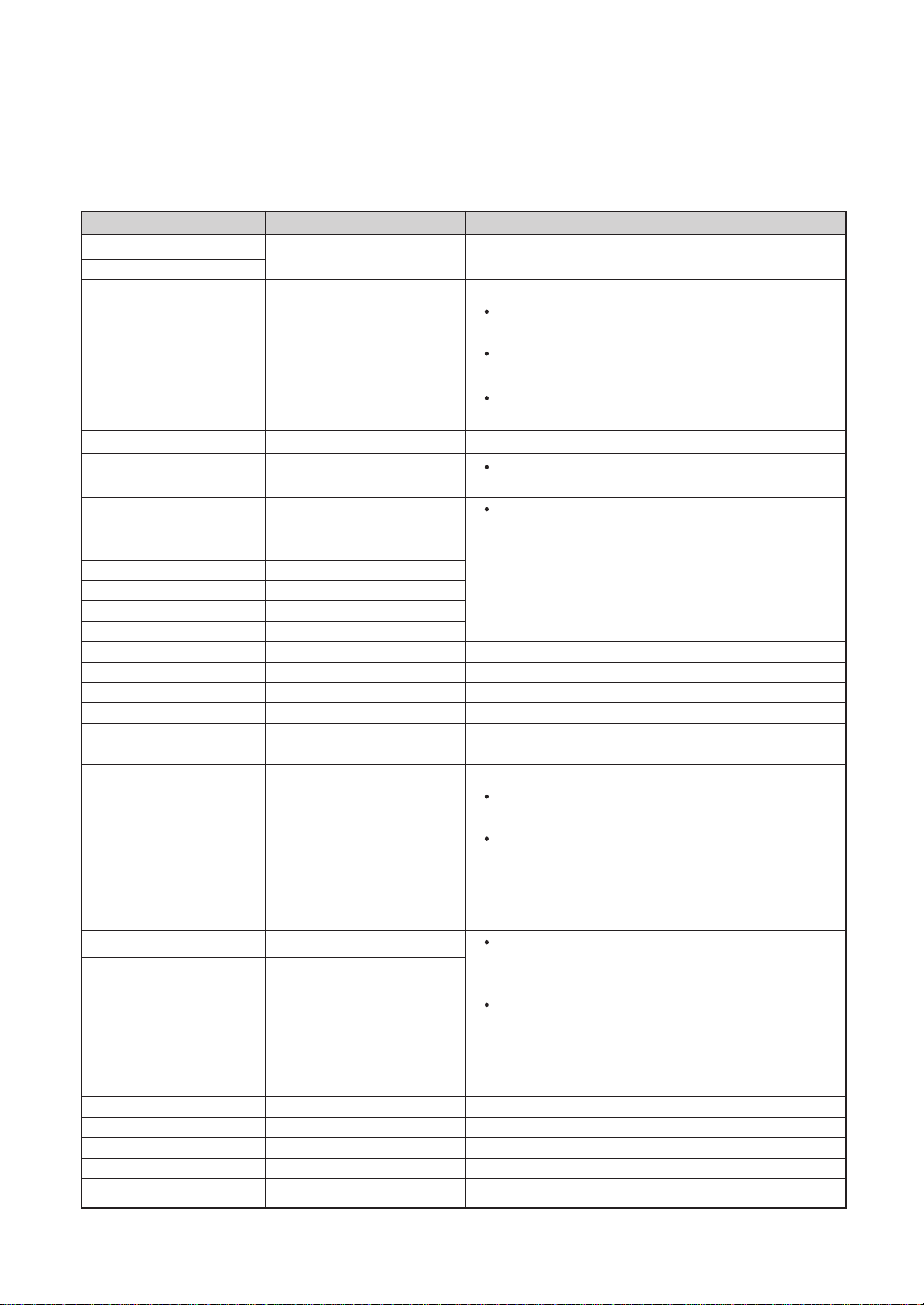

Pin No. Symbol Name Function Description

28 GND. GND

29 RESET Reset Input

30 OSCI Clock Input for CPU

31 OSCO Clock Output for CPU

32 GND GND

33 XCIN XC IN 32.768KHz input

34 XCOUT XC OUT 32.768KHz output

35 OP. 1 Tape Speed Option SP/LP option

36 OP. 2 UHF only Option

37 OP. 3 AV2 Option

38 OP. 4 ShowView Option

39 OP. 5 Factory Power Option Power-On start

40 OP. 6 Clock Test Option

41 OP. 7 VPS Option

42 A/V A/V Mode Switching Active "L"

43 S/SW Scart Input Slow switch input

44 AV1' AV1' Switching Out TV2, AV1', AV2' (VCR REC. mode)

45 AV2' AV2' Switching Out

This pin is used to reset the u-controller after a

power-on reset. In order to be sure that the ucontroller starts from an initialized state after the

supply voltage is available, a reset signal has to be

applied.

This reset signal has to be low until a stable 4.19V

supply voltage is available.

The OSCI and OSCO are used to control the onchip oscillator of the u-controller.

OSCI is the input terminal and OSCO the output

terminal.

All internal timing of the u-controller (except for the

OSD part) are derived from this oscillator.

The oscillator frequency has to be 8MHz.

AV1' AV2' Function

LHAV1

HLAV2

H H TV2

46 AV1 AV1 Switching Out Active "L"

47 DISABLE Disable Out Switching Regulator ON/OFF output

48 POWER Stand by ON/OFF

Control Output "L" ----------- power OFF

49 S. MUTE Sound Mute Control

50 V. MUTE Video Mute Control Not Connected

51 n.c. Not Connected

52 n.c. Not Connected

53 n.c. Not Connected

54 SYS2 SECAM-L/L' Switch SECAM-L/L' switch(TV2)

55 SYS1 SECAM-L/L' Switch SECAM-L/L' switch(TV1)

The switch-mode power supply is controlled.

"H" ---------- power ON

Mute Output is active "H"

On power on/off state, instantaneously cut off the

sound and video.

16

Page 14

Pin No. Symbol Name Function Description

56 TV1/2

57 BLK Blanking Signal for OSD

58 n.c. Not Connected

59 B OSD Blue Colour Output

60 G OSD Green Colour Output

61 R OSD Red Colour Output

62 V-sync V-sync input for OSD

63 H-sync H-sync input for OSD

64 Vcc Power supply input terminal

TV1 / TV2 selection switch

"H" -------------- TV1

"L" --------------- TV2

Output R,G and B deliver the colour components for

the OSD while output BLK is used as a test

blanking signal.

The output polarity of the R,G,B and BLK terminals

are active "H".

Input terminal for CRT display vertical synchronous

signal.

Input rectangular pulses whose amplitude is in the

range from 0 to 5V.

The signal state should be active for the time more

than that required for three scanning lines.

The input polarity is active "L".

Input terminal for CRT display horizontal

synchronous signal.

Input rectangular pulses whose amplitude is in the

range from 0 to 5V.

The input polarity is active "L".

The signal state should be active for the time more

than that required for three scanning lines.

Connected to the 5V power supply.

17

Page 15

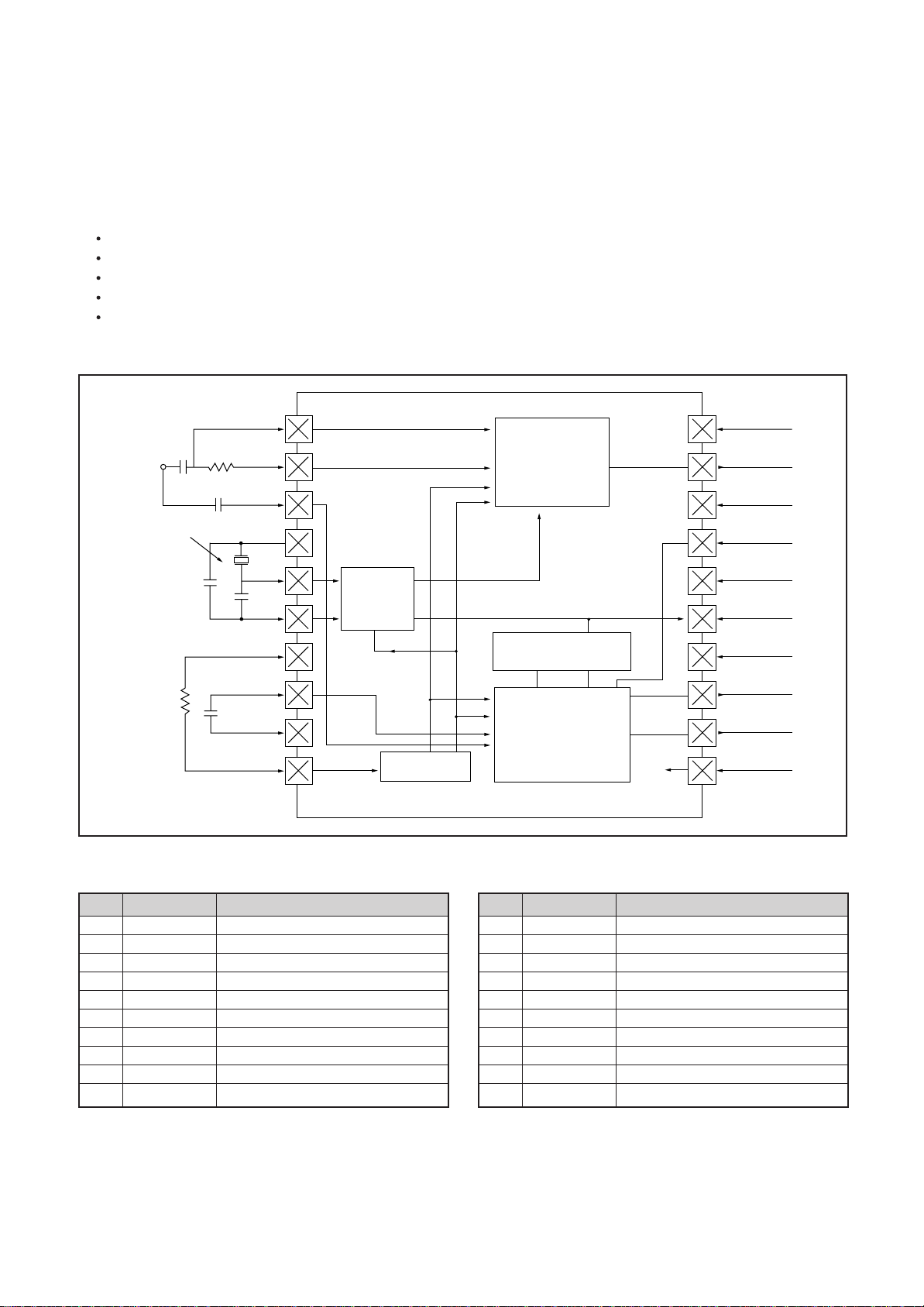

TDA 8362

(1) Features

Multi-standard vision IF circuit (positive and negative modulation)

Multi-standard FM sound demodulator (4.5 MHz to 6.5 MHz)

Video and audio switches (CVBS int/ext, S-VHS and audio int/ext)

Integrated chroma trap and bandpass filters (autocalibrated)

Luminance delay line integrated

PAL/NTSC colour decoder with automatic search system

Easy interfacing with the TDA 8395 (SECAM decoder)for multi-standard applications

RGB-control circuit with linear RGB inputs and fast blanking

Horizontal synchronization with two control loops and alignment-free horizontal oscillator

Vertical count-down circuit and vertical pre-amplifier

Low dissipation(only 600mW)

Small amount of peripheral components compared with competition IC's

Only one adjustment (vision IF demodulator)

(2) Description

Vision IF amplifier, video demodulator, video amplifier, AGC and AFC suitable for both negative and

positive modulation.

Sound limiter,demodulator and amplifier with volume control.

Inputs and switches for external audio and CVBS signals.

Synchronization circuit with drive circuits for horizontal and vertical deflection.

X-ray protection (combined with the 2nd phase detector pin).

PAL/NTSC color decoder in which the chroma filters (bandpass and trap) and the luminance delay line

have been integrated. The circuit has a separate chroma input and the filters can be switched-off so that

S-VHS signals (via an external switch) can be applied to the IC.

For SECAM applications an (alignment-free) SECAM-decoder can be added to the IC.

Peaking circuit in the luminance channel.

RGB-output circuit with linear inputs for On-screen Character Display.

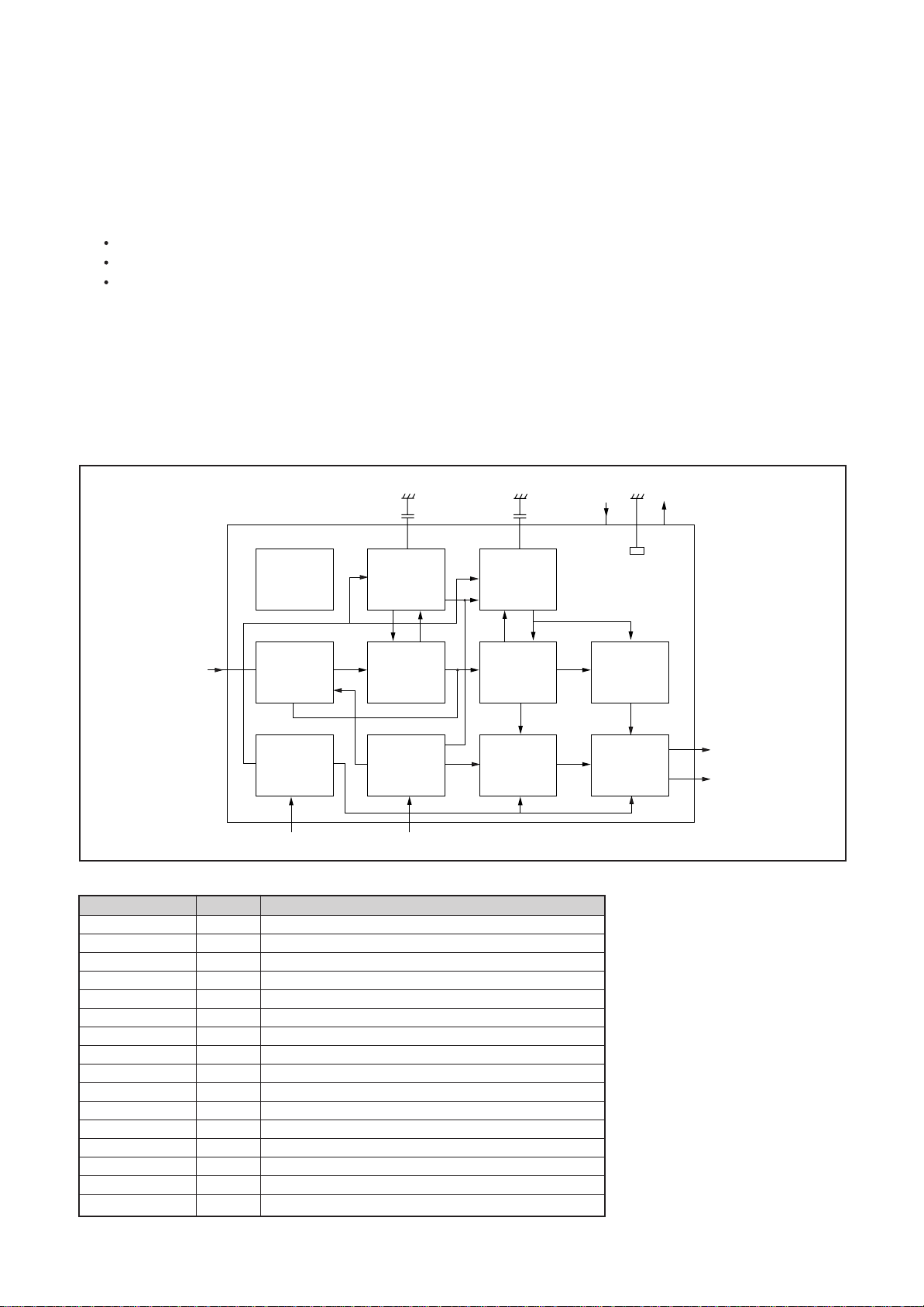

(3) Block Diagram

AUDIO OUT

AUDIO PAE-AMP

+VOL.-CONTR.

T.O.P.

TUNER

IF

AFG

IDENT

AGC FOR IF

+ TUNER

VIF AMPLIFIER

+DEMODULATOR

AFC + S/M VIDEO AMPL

VIDEO

IDENT

AUDIO

IN

AUDIO

SWITCH

SOUND LIMITER

MODULATOR

FILTER TUNING

CVBS

VIDEO SWITCH

CVS

in

SOUND

TRAP

POS/NECC

MCO.

SW

SOUND

BANDP.

SYNC

SEPARATOR

+ 1st LOOP

CHROMA

TRAP

+ DELAY LINE

CHROMA

BANDP.

SWITCH

CONTROL

Chr

+sw.

PEAKING

VOLUME

CONTROL

SHIFT

H. OUT

RGB-INPUT

+SWITCH

RGB-MATRIX

+OUTPUT

PEAK-WHITE

LIMITER

CONTRAST

BRIGHTNESS

+ START

H

+

V

BL

R

G

B

A

G

B

+BV

VCO +

CONTROL

REF

VERT.SYNC

SEPARATOR

LUMINANCE

PROCESSING

Chr

PAL/NTSC

DECODER

Chr

HUE

+ SW.

+ Chr out

SECUMREF.

R.Y B.Y R.Y B.Y

3.6

4.4

2nd LOOP

+ HOR SHIFT

H/V DIVIDER VERT.DEFL.

G+Y MATRIX +

SATURATION

CONTROL

TDA 4661

SATURATION

18

Page 16

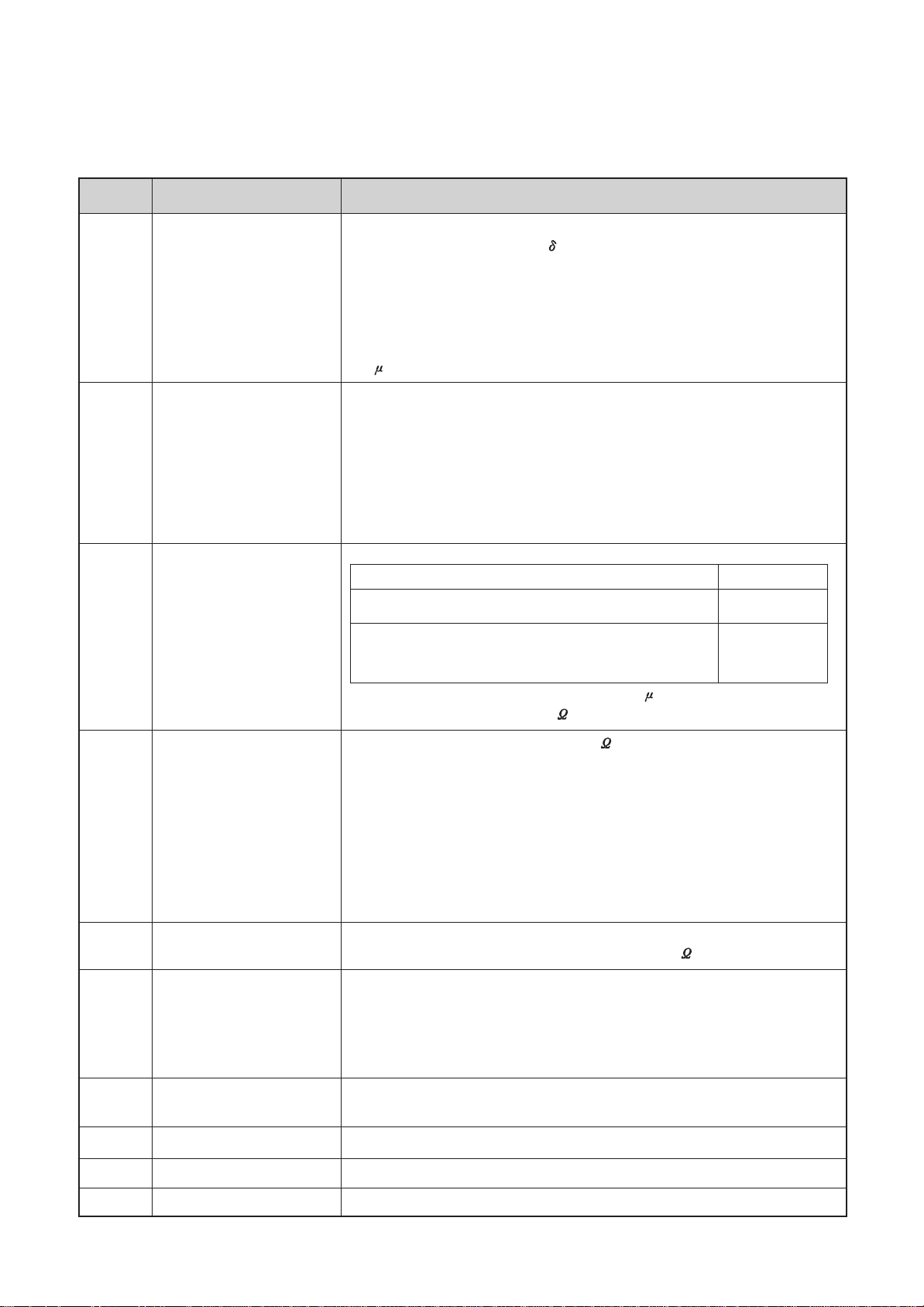

Pin No.

1 Audio De-emphasis At this pin the audio signal is available for scart. The signal has an

2,3 IF Because the demodulator performance depends on the Q factor, we

Demodulator

Tuned Circuit

4 Video The identification output has a three level output, 0.5, 6 or 8V.

Identification

Output

Name Function Description

amplitude of 350mVrms (at f= 50KHz) is non volume controlled and

has to be buffered.(notice the output impedance influences the

deemphasis).For scart requirements, the buffer should be dimensioned

as an amplifier in order to increase the output signal. A third function of

this pin is the positive modulation switch. When the voltage at this pin is

above Vcc-1V positive modulation is selected. The current needed is

100 A typical.

want to keep the Q factor as high as possible. But this means that the

steepness of the AFC will change with the Q factor of the tuned clicuit

itself and also with the input impedance of the IC A compromise has to

be made. The input impedance of the IC is as large as possible (about

12 kOhms) and the Q factor of normal tuned circuits varies from 70 to

90. By means of an external resistor, it is possible to damp the circuit to

a Q of 40 to reduce the steepness variation of the AFC.

Output voltage "video not identified" 0.5V max

Output voltage "video identified" 6V

and colour signal available with fsc = 3.5MHz

Output voltage "video identified" 8V

and colour signal available with fsc = 4.4MHz or

no colour signal detected

The maximum load current on this pin is 25 A.

The output impedance is 20 K .

5 SIF input The sound input impedance is 8.5K /5pF which has to be taken into

+Volume control

6 External Audio Input External sound signals from scart, for example, can be applied to this

7 IF Video Output A multistandard concept requires several filters at the video output

8 Decoupling Decoupling Digital Supply

digital Supply

account for the ceramic filiters. For DC, the impedance is very high. The

PLL is sensitive for high freq. AC signal > 1mVrms. Because of the

chosen principle: an adjustment free PLL it is needed to have an

internal PLL with a large bandwidth (catching range). This implies the

system also is sensitive for spurious frequencies. Both layout and

sound band pass filters need special attention. The volume can be

controlled at this pin by means of a DC voltage of 0.2-5V for min-max

gain.

pin via a capacitor. The input impedance is 25 K .

(sound-trap and sound-band pass filters). This causes a too big

capacitive load at the video output so an EMITTER FOLLOWER as

buffer should be added. The required emitter current depends on the

number of filter applied.

9 Ground Ground 1 (IF, H sync, RGB output, Digital, H output)

10 Positive Supply (8V) Supply (IF,Sound,H sync,Chroma, Filters,RGB output, Digital,)

11 Ground Ground 2 (Sound,Chroma,Filters,Hosc, PHI-1, PHI-2)

19

Page 17

Pin No.

12 Decoupling Variations in the tuning voltage outside calibration (i.e. during field

filter tuning

13 Internal CVS input The internal and external CVBS amplitudes should be 2Vpk-pk and

15 External CVS input 1Vpk-pk respectively; their source impedances should be low so as to

14 Peaking control input The input impedance of pin 14 is very high (MOS input). The DC

16 AV switch input The input impedance of the chroma and A/V switch input(pin 16) is 15K

+ Chroma (SVHS) input

Name Function Description

scan), due to external leakage current or interference sources, will

result in mistuning of the luminance notch filter, chroma bandpass filter

and luminance delay stage. Unwanted voltage signals at pin 12 due to

external leakage currents or cros-stalk from interference sources

should be less than 100mV. A capacitor of 100nF requires that external

leakage at pin 12 should be less than 0.5 A.

minimze cross-talk from interference sources. The internal CVBS input

is derived from the IF video output (pin 7) and the external CVBS input

can be derived from either SCART CVBS or YSVHS; they should be

AC coupled to pins 13 & 15 respectively. The coupling capacitors are

chosen in order to have fast clamping and minimum line/field sag.

voltage at the peaking control input controls the gain of the peaking

amplifier. The peaking control input voltage should have a DC voltage

range from 0 to 5V.

in parallel with 5pF. A DC voltage on this pin controls the internal/

external CVBS and AUDIO selection where the following table gives

the various possibilities:

Vpin 16 Internal External CSVHS Luminance Audio Model

(dc) CVBS CVBS/Y signal notch signal

<0.5V on off off on Internal TV

Between

3V &5V

>7.5V off

off on(Y) on off External S VHS

on

(CVBS)

off on External AV

17 Brightness Control input The brightness control voltage present at pin 17 controls the dc level of

the RGB outputs where a brightness control voltage of 0 5V at pin 17

results in a black level shift at the RGB outputs of 1V about the

nominal.

18 B-output The RGB output signals are supplied to the video output stages. For nominal

19 G-output input signals (i.e. CVBS and -(R-Y)/-(B-/Y) signals) and for nominal gain

20 R-output settings then the RGB output signal amplitudes (black-to-white)are

typically 4V with a black level at approximately 1.3V. The blanking level

is 0.8V and maximum peak white level is 6.0V Since the RGB output

stages are made with emitter followers, the maximum sink current is

limited to 1.5mA. Therefore the current delivered from the video output

stages to the RGB pins must not exceed 1.5mA.When the RGB switch

control (pin 21) voltage exceeds 4V then the RGB outputs are blanked

and consequently on-screen display signals (OSD) can be supplied to

the video output stages.

21 RGB insertion The RGB insertion signals are selected by means of a fast switch

22 R-input for insertion The RGB insertion signal information is coupled via 100nF to pins 22,

23 G-input for insertion 23 and 24 respectively. The coupling/clamping capacitors should always

24 B-input for insertion have a low impedance path to ground for proper clamping operation.

+ Blanking input

control.With the conditions that:0.8V<Vpin21<3.1V then the RGB insertion

signals are selected. And input voltage to blank the RGB- outputs so that

OSD signals can be applied to these outputs is 4.5V (min).

20

Page 18

Pin No.

25 Contrast Control input The contrast control input of 0 5V at pin 25 gives a 20dB gain range

26

27 Chroma output If the Vpin27>6V, the ASM does not search for NTSC signals and the

28 B-Y input The -(R-Y)/-(B-Y) signals, present at pins 11 and 12 of the TDA4661, are

29 R-Y input coupled via 100nF (these capacitors are also clamping capacitors) to

30 R-Y output

31 B-Y output signals are identified. For SECAM signals the output impedance is very

32 4.43 MHz output A SECAM reference signal (4.43 MHz only ) is delivered directly from

33 Loop Fitter One of the important aspects of the PLL is the loop filter connected to

Name Function Description

at the RGB outputs. When one of the RGB output signals exceed 6V, it

is then clipped to 6V and also the gain of the RGB output amplifiers can

be reduced by adapting the contrast voltage using the peak white

limiter (PWL) current, The PWL current during PWL operation is 100 A.

Saturation Control Input

+ Hue Control Input

for TDA8395

(Burst Phase

Detector)

The saturation control input voltage, present at pin 26, is 0 5V. this

corresponds to a 52dB gain range of the -(R-Y)/-(B-Y) signals.

decoder application can only be PAL or PAL/SECAM. The output

impedance with an external resistance of 22K to 8V is then

approximately 500 .The hue control input pin should be provided with

a voltage of 0 to 5V for NTSC decoder applications; within this voltage

range the input impedance is very high (MOS input).

pins 29 and 28. The maximum input current of both pins is 1 A. With

100nF coupling capacitors the voltage drop over a line period is less

than 0.5mV Since the output impedance of pin 11 and 12 of the TDA

4661 is maximal 400 then the signal tracks between the TDA 4661

and the TDA8362 should have good ground shielding and be as short

as possible.

The output impedance of pins 30 & 31 is approximately 250 when PAL/NTSC

high (output switch is open) and any external circuity is not loaded (i.e.

the demodulator output of the TDA 8395). During the line/field blanking

periods of the sandcastle pulse, the demodulator outputs are set to the

correct dc levels so as no offsets exist. The-(R-Y)/-(B-Y) outputs are

coupled, via 1nF, to pins 16 & 14 of the TDA4661 respectively.

pin 32 of the TDA8362 to pin 1 of the TDA8395. When SECAM

siganals are identified by the TDA8395, it withdraws a current of 150 A

from pin 32.The SECAM interface communicates the ident information

via this current to the ASM. If PAL/NTSC signals are not already

identified by the ASM and the identified signal is 50 Hz then an

acknowledge will be given by ASM to the TDA8395 by setting the

voltage at pin 32 to 5V. With SECAM identified, the SECAM reference

signal signal is gated and present at pin 32 only during the field retrace

period. When PAL/NTSC is identified, the output level is 1.5V.

pin 33. It ensures that the PLL synchronizes the VCXO, in both

frequency and phase, with the incoming burst (average burst for PAL

standards). It also determines the dynamic performance of the loop

where the important parameters are: -Noise immunity - Transient

response -Acquisition behaviour The remaining aspects of the

PLL/VCXO are static phase error and X-tal type used at pins 34 or 35.

For small static phase errors (less than 5 the requirements are: -The

combined buest phase detector and VCXO sensitivity are high. The

offset of the burst phase detector output is small. -The external leakage

current at pin 33 is small. The TDA8362 determines the first two; the

third is determined by the external leakage resistance of pin 33 to

ground. Deviations in the VCXO free running frequency due to X-tal or

X-tal load capacitance spreads have negligible influence on the static

phase error because the combined phase detector and VCXO

sensitivity is high. The static phase error is due to the internal offset of

the phase detector output and the external leakge current at pin 33.

Static phase errors much less than 5 were measured.

21

Page 19

Pin No.

34 3.58MHz X-TAL To ensure correct operation of both colour processing and

35 4.43MHz X-TAL connected to pin 34 and 3.58

36 Start Horizontal The minimum current required for the start function is 6.5mA,

37 Horizontal Output This open collector output drives the horizontal output stage. The

Name Function Description

Connection sync calibrationcircuits in the TDA8362, 4.43 X-tals must not be

Connection X-tals must not be connected to pin 35.

Oscilator then the voltage will be approx. >7.2V. The voltage at pin 36 may not

exceed 8.8V, so depending on the application external clamping is

necessary. If the start voltage is below approximately 5.8V then the

horizontal output will be disabled. The decoupling should be sufficent

because the start pin supplies the circuitries needed for the horizontal

output. (The oscillator references, however, are supplied by the

bandgap.) This pin must be connected directly to the supply pin when

no start function is used.

maximum allowable current is 10mA. The saturation voltage then will be

0.3V.

38 Flyback input

+Sandcastle Output Burst typ 5.3V, the output impedance is approx. 1k

39 -2 loop Filter The phase error on screen due to storage time variations depends on

+X-Ray Protection the PHI-2 loopgain. In principle this figure is fixed but will decrease

40 -1 loop Filter The PHI-1 behaviour depends on both the loop filter externally

41 Vertical Feedback The feedback signal is derived by sensing the deflection coil current by

Input means of a resistor. The feedback signal is related to the vertical ramp

42 Vertical Ramp The vertical ramp is defined as: -DC clamping voltage of 2V -AC

Generator amplitude of 1.5Vpp for a 50Hz field signal -AC amplitude of 1.25Vpp

A sandcastle signal is available at this pin for external use. The signal levels are:

Flyback typ 3 V, impedance defined by the flyback circuit.

Field blanking typ 2 V, the output impedance is approx. 4k

The flyback input signal is used for the PHI-2 loop and RGB line

blanking. Pin 38 requires a current of only a few in order to reach

the 3V flyback clamping level. Detection of the flyback pulse (and thus

RGB blanking) only occurs when the input current is at least 100 A.

(The maximum allowable current is 300 A.) Additonal remarks: -Due to

an internal base current at pin 38, the voltage level becomes 3V when

the pin is not loaded. -During start-up pin 38 is forced low by 2mA.

when an additional resistor comes in parallel to the capacitor at pin 39.

The time constant is defined by the external capacitor. The voltage to

switch on the X-ray protection is 6V. (min.)

connected at pin 40 and the PHI-1 output currents. The PHI-1 output

current has been made switchable during scan (a fixed current ratio) in

order to avoid the need of switching the loop filter for normal-and noisysignals. This implies the loop filter can be optimised for both VCR-and

noisy-signals.

signal. The ramp amplitude should be 1Vpp while the DC level is 2.5V

typical. The guard levels are 1 and 4Vtyp. In order to filter horizonatal

into a capacitor is mounted at the input.

for a 60Hz field signal The AC amplitude of 1.5V is important for optimal

pre-correction and 50/60Hz gain correction.

22

Page 20

Pin No.

43 Vertical Output. The vertical drive output is fed to the deflection-IC. The available output

44 AFC Output The AFC steepness can be influenced by the Q of the tuned circuit and

45,46 IF Input DC coupling is allowed, so no series capacitors are necessary. The

47 Tuner AGC Output The tuner AGC is an open collector output which is acting as a variable

48 AGC Increasing of the AGC time constant is achieved by increasing the AGC

49 Tuner Take-Over The control range at this pin is 0.5-4.5V.

Name Function Description

current is minimal 1mA, and the available output voltage is 4-5V. During

retrace the drive output has to be constant and equal to the low level of

0.3V.

output resistors at the AFC output pin (60k output impedance

intermally). Due to current reserve the steepness can be reduced by a

factor 4-5 while the output voltage swing remains 6V. Some small video

information can still be present at the AFC output pin although a S&H

function is applied. This video information can be filtered by an external

capacitor at this pin. The AFC output voltage changes from

approximately 0.5-6.3V. The output impedance of AFC circuit is 50k .

circuit matches the required load impedance for commonly used SAW

filters(2k/3pF).

current source to ground. Normally the output application circuit is

designed for an output current swing of 1-2mA. In order to improve the

dynamical behaviour during channel switching it is possible to sink with

a current of approximately 12mA maximal. The max voltage is Vcc+1V.

Decoupling Capacitor capacitor on pin 48. Increasing this capacitor also results in an

improvement in the catching and holding range of the ident circuit.

Adjustment

Characteristics:

The tuner take

over adjust voltage versus IF input signal is a linear function with a

slope of approximately 20mV/dB. (Measured at an AGC output current

of 1mA) In order to achieve a stable AGC control at strong signals a

decoupling capacitor of at least 1nF at this pin is required.

Alignment:

With the potentiometer connected to pin 49 of the TDA8362, the tuner

take over point can be adjusted when an RF signal is applied to the

aerial input of the tuner.

50 Audio Input The DC output voltage is 3.3V. The volume controlled output signal is AC

coupled to the sound output amplifier. The output impedance is 250 .

51 Decoupling This pin defines the DC voltage at the deemphasis and sound output.

Sound Demodulator The pin forms a low pass filter in the DC feedback loop. This implies

that the sound amplitude for lower frequencies, < fk, is attenuated. A

bigger capacitor, in order to decrease fk, is allowed but increases the

DC setting time.

52 Decoupling Decoupling Bandgap Supply

Bandgap Supply

23

Page 21

TDA4661(Base Band Delay Line)

(1) Features

• Two comb filters, using the switched-capacitor technique,for one line delay time (64µs)

• Adjustment free application

• No crosstalk between SECAM colour carriers

• Handles negative or positive colour-difference input signals

• Clamping of AC-coupled input signals(±(R-Y)and±(B-Y))

• VCO without external components

• 3MHz internal clock signal derived from a 6MHz VCO, line-locked by the sandcastle pulse (64µs line)

• Sample-and -hold circuits and low-pass filters to suppress the 3 MHz clock signal

• Addition of delayed and non-delayed output signals

• Output buffer amplifiers

• Comb filtering functions for NTSC colour-difference signals to suppress cross-colour

(2) General Description

The TDA4661 is an integrated baseband delay line circuit with one line delay. It is suitable for decoders with

colour-difference signal outputs±(R-Y)and±(B-Y).

(3)Block Diagram

16

14

0

5

SIGNAL

CLAMPING

SIGNAL

CLAMPING

analog supply

SANDCASTLE

DETECTOR

10

GND1

pre-amplifiers

FREQUENCY

PHASE

DETECTON

LINE

MEMORY

LINE

MEMORY

DIVIDER

BY 192

digital supply

3

output

buffers

2

6

13

15

4,8

11

colour-difference

output signals

12

n.c.

n.c.

n.c.

n.c.

7

I.c.

(R-Y)

(B-Y)

SAMPLE-

ANDHOLD

SAMPLE-

AND-

HOLD

3 MHz shifting clock

LP

6MHz

VCO

1

V

P2

LP

LP

TDA4661

DIVIDER

BY 2

addition

stages

GND2

(R-Y)

colour-difference

input signals

(B-Y)

V

P1

sandcastle

pulse input

(4)Pin Description

SYMBOL PIN DESCRIPTION

Vp2 1 +5V supply voltage for digital part

n.c. 2 not connected

GND2 3 ground for digital part (0V)

i.c. 4 internally connected

SAND 5 sandcastle pulse input

n.c. 6 not connected

i.c. 7 internally connected

i.c. 8 internally connected

SYMBOL PIN DESCRIPTION

Vp1 9 +5V supply voltage for analog part

GND1 10 ground for analog part (0V)

V0 (R-Y) 11 ± (R-Y) output signal

V0 (B-Y) 12 ± (B-Y) output signal

n.c. 13 not connected

V1 (B-Y) 14 ± (B-Y) input signal

n.c. 15 not connected

1 (R-Y) 16 ± (R-Y) input signal

V

24

Page 22

TDA8395 (Secam Decoder)

(1) Features

Fully integrated filters

Alignment free

For use with baseband delay

(2) Description

The TDA8395 is a self-calibrating,fully integrated SECAM decoder. The IC should preferably be used in conjunction

with the PAL/NTSC decoder TDA8362 and with the switch capacitor baseband delay circuit TDA4661. The IC

incorporates HF and LF filters, a demodulator and an identification circuit (Iuminance is not processed in this IC).

A highly stable reference frequency is required for calibration and a two-level sandcastle pulse for blanking and burst

gating.

(3) Block Diagram

ref PLLref GND

CLOCHE

100 nF

77362

220 nF

V

TEST

p

BANDGAP TUNING TUNING

CVBS

16

ACC

INTERFACE

115

f

ref/IDENT

CLOCHE

FILTER

CONTROL

SAND

PLL

IDENT-

IFICATION

(4) Pin Description

SYMBOL PIN DESCRIPTION

fp1/IDENT 1 reference frequency input/identification input

TEST 2 test output

Vp 3 positive supply voltage

n.c. 4 not connected

n.c. 5 not connected

GND 6 ground

CLOCHEref 7 Cloche reference filter

PLL ref 8 PLL reference

-(R-Y) 9 -(R-Y) output

-(B-Y) 10 -(B-Y) output

n.c. 11 not connected

n.c. 12 not connected

n.c. 13 not connected

n.c. 14 not connected

SAND 15 sandcastle pulse input

CVBS 16 video (chrominance) input

TDA8395

DE-

EMPHASIS

OUTPUT

STAGE

–(R-Y)

9

10

–(B-Y)

25

Page 23

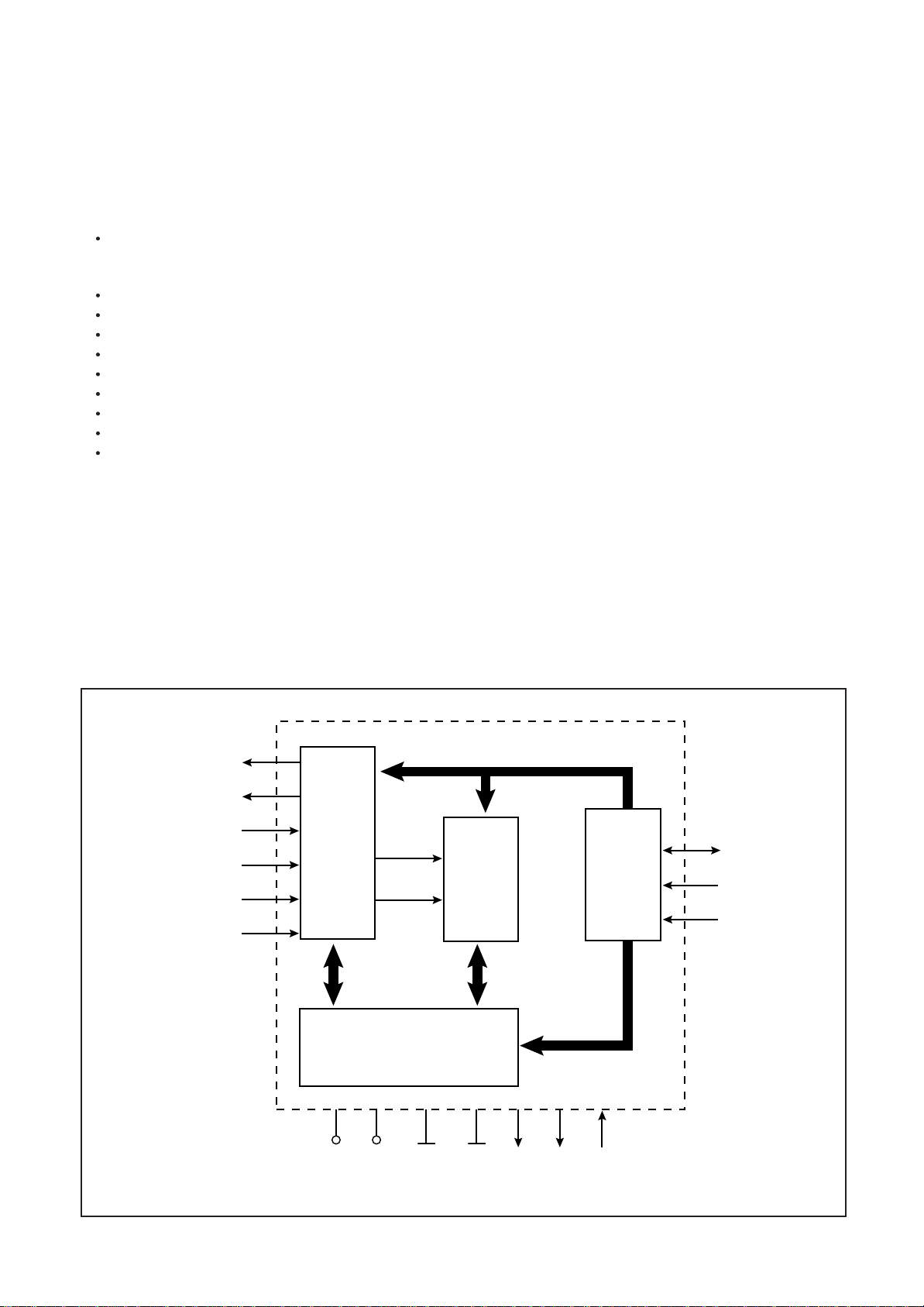

AT24C08PC (EEPROM)

(1)Features

IC Bus compatible

Low power CMOS Technology

16 Byte page write Buffer

Self-Timed write cycle with Auto-Clear

100,000 program/Erase cycles

100 Year Data Retention

Optional High Endurance Device Available

(2)General Description

The AT24C08PC is a 8K bit serial CMOS E2PROM internally organized as 1024x8bits. Catalyst's advanced

CMOS technology substantially reduces device power requirements. The AT24C08PC features a 16 byte

page write buffer.

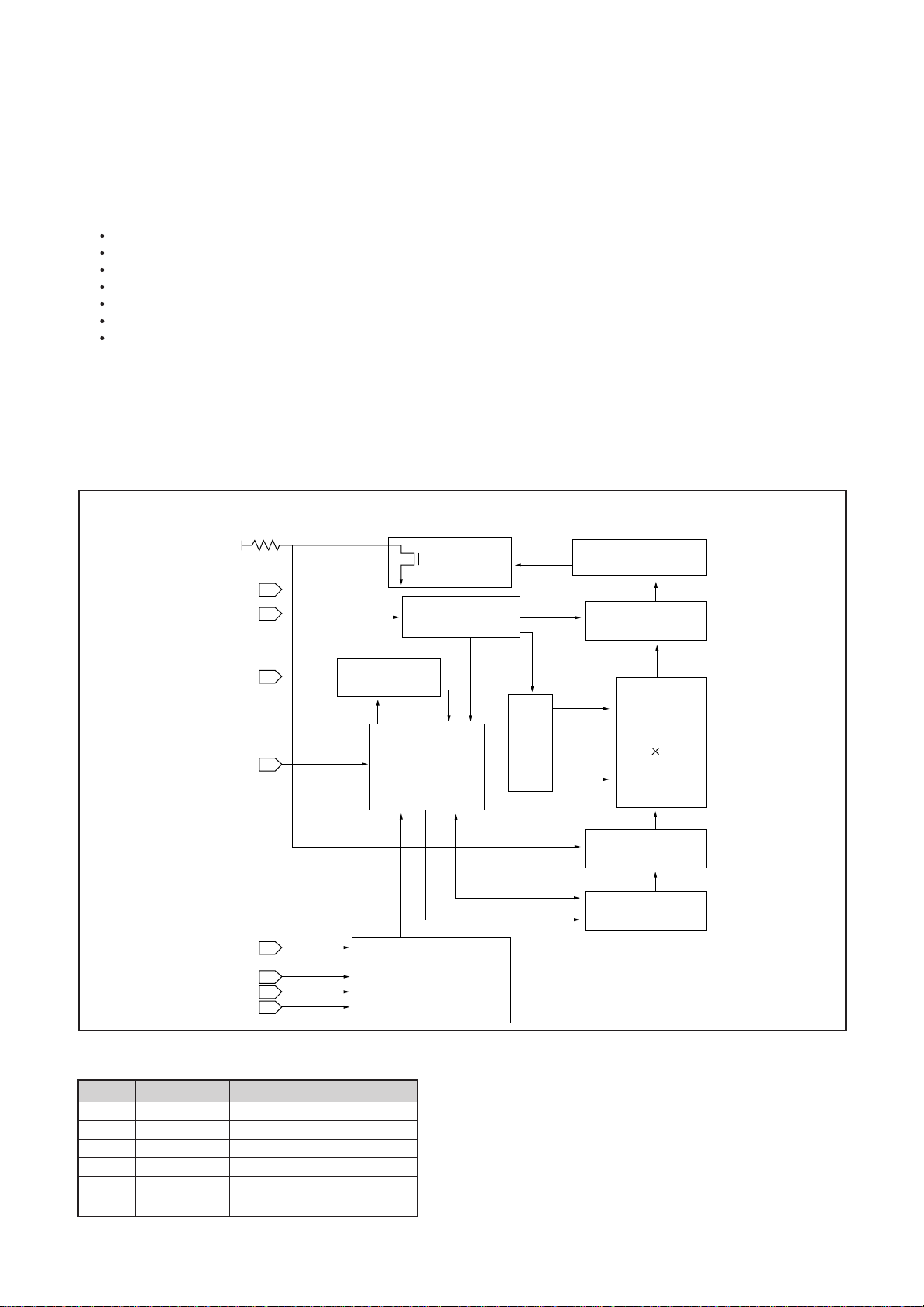

(3) Block Diagram

EXTERNAL

Vcc

Vgg

SDA

TEST

SEL

A0

A1

A3

WORD ADDRESS

BUFFERS

START/STOP

LOGIC

CONTROL

LOGIC

STATE COUNTERS

SLAVE

ADDRESS

COMPARATORS

D OUT

AKC

XDEC

SENSE AMPS

SHIFT REGISTERS

COLUMN

DECODERS

2

64

E PROM

128

64

DATE IN STORAGE

HIGH VOLTAGE/

TIMING CONTROL

(4) Pin Description

PIN SYMBOL DESCRIPTION

1-3 A0,A1,A2 Device Address Inputs

4 Vss Ground

5 SDA Serial Data/Address

6 SCL Serial Clock

7 TEST Connect to Vss

8 Vcc +5V Power supply

26

Page 24

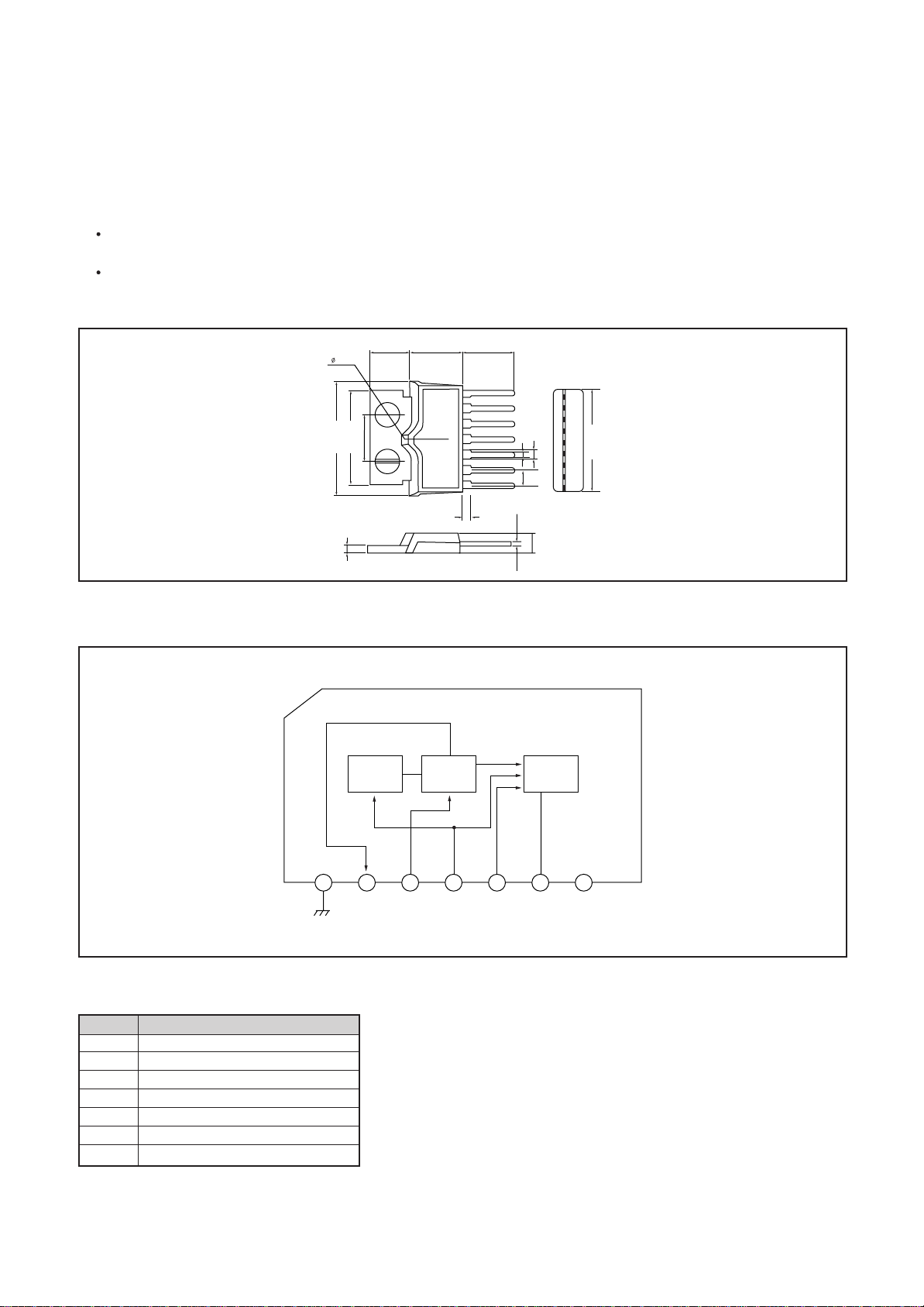

AN5515 (TV Vertical Defelection Output Circuit)

(1)Features

Low power consumption, direct deflection coil driving capability (Flyback voltage two times as high as

supply voltage is supplied during flyback period only)

High breakdown voltage: 50V

(2)General Description

(3)Block Diagram

5.9±0.25

3.6

8.2±0.3

7.8±0.25

7

6

5

1.8R

7.6±6.2

15.3±0.3

17.7±0.3

4

3

0.6±0.1

16.9±0.3

1.4

2

2.54

1.45

3.5±0.3

1.8

Pulse

Amp.

1.2±0.1

Driver

1

1.2

Output

(4)Pin Description

PIN DESCRIPTION

1 GND

2 Output

3 Supply Voltage for Output

4 Input

5 Trigger Pulse Input

6 Pulse Amp. Output

7 Vcc

1 2 3 4 5 6 7

27

Page 25

CF70200 (Teletext Decoder)

(1) Features

Eight pages of on-chip Display RAM

Europe-wide solution

Automatic FLOF & TOP decoding

Flicker-free packet 26 processing on chip

Program delivery control

Minimum software requirement

Menu page capability

Instantaneous page memory clear

75Ω RGB outputs

Digital PLL

Upgrade path from UNITEXT

(2) Block Diagram

SYNC

VIDEO

CSB

SYNC

SWITCH

PLL

RAM

REF

75Ω

DRIVER

RGBSET

R

G

B

RTSK

PROCESSOR

TDATA

TCLK

TELETEXT

FRONT END

PIN PIN NAME DESCRIPTION

1 TEST5 Test Pin

2 SYNC

The output of an internal sync

switch

3 CVBS Video input to sync switch

4 DVcc +5V

5 RSTB System reset active low

6 CLKIN System clock 13.875MHz

7 DGND Ground

8 T1 Test Pin

9 T4 Test Pin

10 TDATA Teletext Data

11 TCLK Teletext Clock Signal

12 CSB Composite Sync Signal

13 MUTE Mute

14 T2 Test Pin

VDP

IC

INTER FACE

BLANK

SDA

SCL

PIN PIN NAME DESCRIPTION

15 WIND WIND

16 T3 Test Pin

17 SCL I2C Clock Line

18 SDA I2C Data Line

19 BLK Blanking

20 B Display Data

21 AVcc +5V

22 G Display Data

23 R Display Data

24 AGND Ground

25 RGBSET

Adjustment for theRGB,Blank

levels

26 REF Internal Reference Pin

27 FLAG1 System Information

28 FLAG2 System Information

28

Page 26

CF72306

(1) Features

Forms a custom 2-chip solution when used with an ASICTEXT decoder

Low power 1um CMOS

Standard 20 pin/300mH package

Tolerates a range of video distortions

Operates with 13.875MHz fundamental mode crystal

(2) Block Diagram

10pF

220pF

13.87MHz

15pF

1 SIG

SSIG

CSIG

AGND 1

15pF

AVGC

220pF

AGND 2

BIAS

OSC 1

OSC 1

CREF

V

BIAS

OSC

13.875MHz

BIAS

I BIAS

ADAPTIVE

SYNC

SEPARATOR

FREOUENCY

MULTIPLER

69MHz

SLICER

DISADLE

DATA

CLK

SCANOUT

SYNC

DGND 1

WIND

DVCC

OSCOUT

SCANOUT

DGND 2

TCLK

TSTAPLB

(3) Pin Description

PIN SIGNAL DESCRIPTION

1 TSIG Video Sync Input 1

2 SSIG Video Sync Input 2

3 CSIG Video Data Input

4 AGND1 Analogue Ground

5 OSC1 13.875MHz Oscillator

6 OSC2 13.875MHz Oscillator

7 AVCC Analogue Vcc

8 CREF Video Data Reference Input

9 AGND2 Analogue Ground

10 BIAS Internal Reference

PIN SIGNAL DESCRIPTION

11 TSTAPLB Test/Application

12 TCLK Teletext Clock

13 TDATA Teletext Data

14 DGND2 Digital Ground

15 OSCOUT Oscillator Output

16 DVCC Digital Vcc

17 WIND Timing Signal

18 DGND1 Digital Ground

19 SYNC Separated Sync Output

20 SCANOUT Test Scan Output

29

Page 27

SDA5648 (VPS/PDC Decoder)

(1) Features

Single-chip receiver for PDC data, broadcast either

- in Broadcast Data Service Packet (BDSP) 8/30/2 according to CCIR teletext system B, or

- in dedicated line no. 16 of the vertical blanking interval(VPS)

Reception of Unified Data and Time (UDT) broadcast in BDSP 8/30/1

Low external components count

On-chip data and sync slicer

IIC-Bus interface for communication with external micro-controller

Selection of PDC/VPS operating mode software controlled by IIC-Bus register

Pin and software compatible to VPS Decoder SDA5642

Supply voltage : 5 V ±10 %

Video input signal level : 0.7 Vpp to 1.4 Vpp

Operating temperature range : 0 to 70°C

(2) General Description

The CMOS circuit SDA 5648 is intended for use in video cassette recorders to retrieve control data of the

PDC system from the data lines broadcast during the vertical blanking interval of a standard video signal.

The SDA 5648 is devised to handle PDC data transported either in Broadcast Data Service Packet(BDSP)

8/30 format 2 (bytes no. 13 through 25) of CCIR teletext system B or in the dedicated data line no. 16 in the

case of VPS.

Furthermore it is able to receive the Unified Date and Time (UDT) information transmitted in bytes no. 5

through 21 of packet 8/30 format 1.

Operating mode (PDC/VPS) is selected by a control register which can be written to via the IIC-Bus interface.

(3) Block Diagram

PD2/VCO 2

I

VCO 1

CVBS

PD1

REF

VCS

DATA-

SyncSlicer

Clock-PLL

Timing

Data-

Acquisition

2

I C Businterface

SDA

SCL

CSO

DD AVDD VSS A VSS D

V

30

DAVN EHB

TI

Page 28

(4) Pin Description

PIN SYMBOL DESCRIPTION

1 Vss GND

2 SCL Serial Clock input of I2C-Bus

3 SDA Serial Clock input of I2C-Bus

4 CS0 Chip select

20H/21H, when pulled low

22H/23H , when pulled high

5 VCS Video Composite Sync output

6 DAVN VPS/PDC data recognition

7 EHB Identification signal for first half

frame

PIN SYMBOL DESCRIPTION

8 TI Test Input

9 PD1 Phase detector/charge pump

output

10 PD2/ Connector of the Loop filter for

VCO2 the SYSPLL

11 VCO1 Oscillator control input

12 IREF Reference current

13 CVBS CVBS input

14 V

DD

Supply voltage (+ 5 V nom.)

31

Page 29

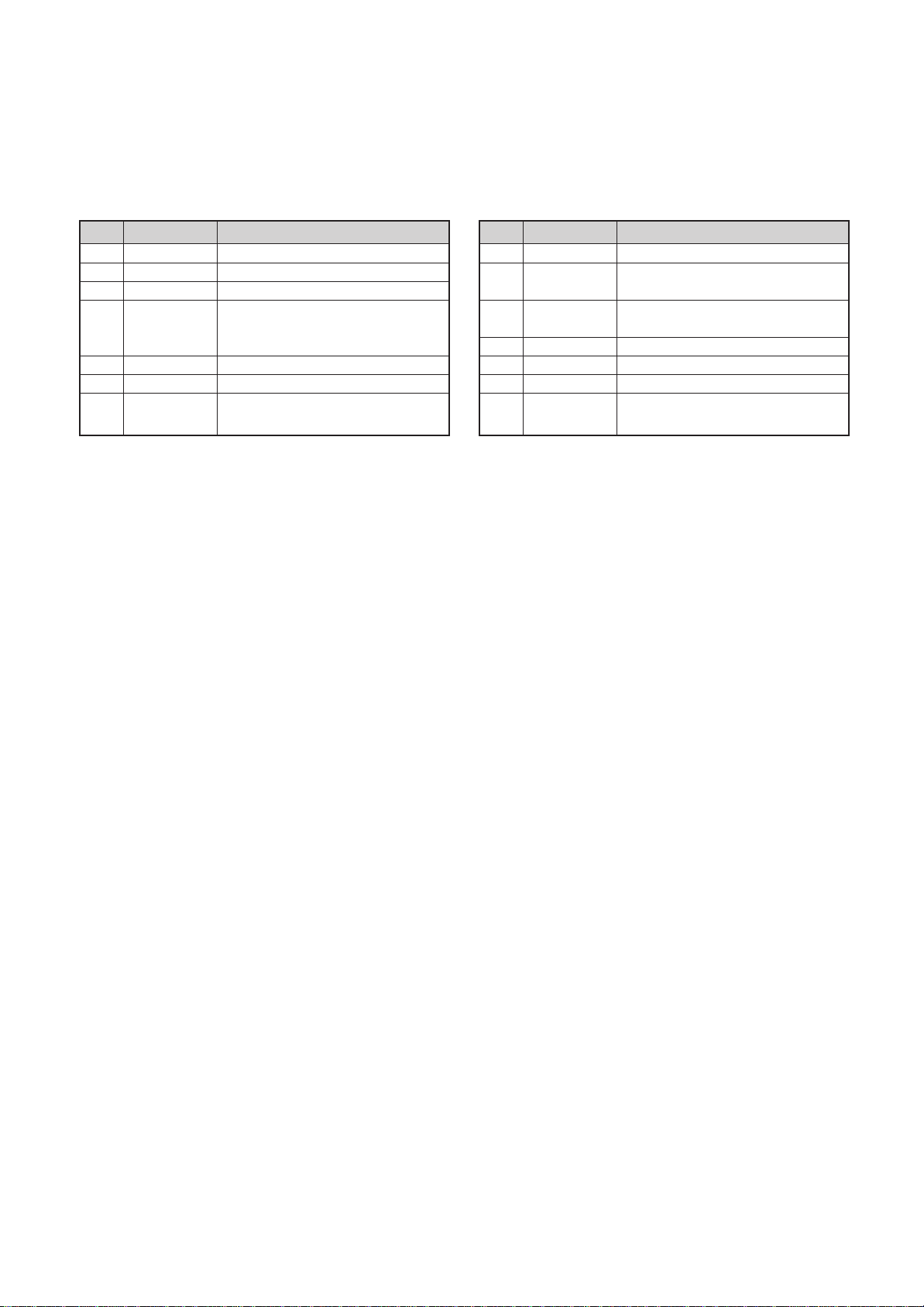

TDA 4601(SMPS Controller)

(1) Features

Direct control of the switching transistor

Low start-up current

Reversing linear overload characteristic

Base current drive proportional to collector current

Protective circuit in case of disturbance

(2) General Description

The integrated circuit TDA4601 is designed for driving, controlling and protecting the switching transistor in

self-oscillation flyback converter power supplies as well as for protecting the overall power supply unit.

(3) Block Diagram

Start-Up

Circuit

Voltage

Control

Reference

Voltage

1 2 3 4 5 6 7 8

Control

Amplifier

Standby

Operation

Overload

Identification

Zero Passage

Identification

(4) Pin Description

PIN DESCRIPTION

1VREF output

2 Zero passage identification

3 Input control amplifier,overload amplifier

4 Collector current simulation

5 Connection for additional protective circuit

6 Ground

7 DC output for charging coupling capacitor

8 Pulse output-driving of switching transistor

9 Supply voltage

Trigger

Start

Hold

Control

Logic

Collector Current

Simulation

Ext. Trigger

Blocking Function

Base Current

Amplifier

Coupling-c

Charging

Circurt

Base Current

Switch-Off

9

32

Page 30

TDA9800 (VIF-PLL demodulator and FM-PLL detector)

(1) Features

Suitable for negative vision modulation

Gain controlled 3-stage IF amplifier; suitable for VIF frequencies up to 60 MHz

True synchronous demodulation with active carrier regeneration (ultra-linear demodulation, good

intermodulation figures, reduced harmonics and excellent pulse response)

Peak sync AGC

Video amplifier to match sound trap and sound filter

AGC output voltage for pnp tuner; adjustable take over point (TOP)

AFC detector without extra reference circuit

Alignment-free FM-PLL detector with high linearity

Stabilizer circuit for ripple rejection and to achieve constant output signals

(2) General Description

Monolithic integrated circuit for vision and sound IF signal processing in TV and VTR sets.

(3) Block Diagram

VP - 5V

IF input

I PC

V

phase

adjust

18

1

2

4

take over

point

20

INTERNAL

REFERENCE

VOLTAGE

3-stage

IF amplifier

TUNER

AGC

3

tuner AGC

output

PLL 2f PC

T

17

3.6V

TRAVELLING

WAVE

DIVIDER

FREQUENCY

DETECTOR

AND PHASE

DETECTOR

6

DEMODULATOR

16

VCO AFC

VIDEO

TDA9800

IF

AGC

12 19 5 8 13 14 11

C

AGC

AGC

DETECTOR

sound MUTE

AFC

VIDEO

AMPLIFIER

n.c.

15

sound

mute

BUFFER AND

NOISE

CLIPPING

SOUND

TRAP

1 V (P-P)

AF

AMPLIFIER

FM.PLL

SOUND

FILLTER

9 V

10

7

O AF

+

C AF

CVBS

2 V (P-P)

FIG.1 Block diagram.

33

MEH191-1

Page 31

(4) Pin Description

PIN SYMBOL DESCRIPTION

1Vi IFa Vision IF differential input

2Vi IFb Vision IF differential input

3 TADJ tuner AGC take over

adjust(TOP)

4 PADJ phase detector adjust

5 MUTE mute switch input

6TPLL PLL time constant OF phase

detector

7Vo CVBS CVBS(positive) output signal

8 n.c. not connected

9VO AF audio frequency output signal

10 CAF decoupling capacitor of audio

frequency amplifier

PIN SYMBOL DESCRIPTION

11 Vi IC sound intercarrier input signal

12 TAGC tuner AGC output

13 Vo VID video and sound intercarrier

output signal

14 Vi VID video input signal to buffer

amplifier

15 AFC automatic frequency control

output

16 VCO1 VCO reference circuit for 2 fPC

17 VCO2 VCO reference circuit for 2 fPC

18 GND GND

19 CAGC AGC capacitor

20 VP positive supply voltage

34

Page 32

TDA9802 (Multistandard VIF-PLL demodulator and FM-PLL detector)

(1) Features

Suitable for negative vision modulation

Gain controlled 3-stage IF amplifier; suitable for VIF frequencies up to 60 MHz

True synchronous demodulation with active carrier regeneration (ultra-linear demodulation, good

intermodulation figures, reduced harmonics and excellent pulse response)

Peak sync AGC for negative modulation, e.g. B/G standard

Peak white AGC for positive modulation, e.g. L standard

Video amplifier to match sound trap and sound filter

AGC output voltage for tuner; adjustable take over point (TOP)

AFC detector without extra reference circuit

Alignment-free FM-PLL detector with high linearity

Stabilizer circuit for ripple rejection and to achieve constant output signals

(2) General Description

Monolithic integrated circuit for vision and sound IF signal processing in Multistandard TV and VTR sets.

V

P - 5V

PLL 2f PC

T

AFC

IF input

I PC

V

phase

adjust

18

1

2

4

take over

point

20

INTERNAL

REFERENCE

VOLTAGE

3-stage

IF amplifier

TUNER

AGC

3

tuner AGC

output

17

6

TRAVELLING

WAVE

DIVIDER

3.6V

FREQUENCY

DETECTOR

AND PHASE

DETECTOR

DEMODULATOR

TDA9802

IF

AGC

12 19 5 8 13 14 11

C

AGC

DETECTOR

16

VCO AFC

VIDEO

AGC

sound

MUTE

VIDEO

AMPLIFIER

negative/

positive

modulation

15

mute

sound

mute

BUFFER AND

NOISE

CLIPPING

SOUND

TRAP

1 V (P-P)

AF

AMPLIFIER

FM.PLL

SOUND

FILLTER

FIG.1 Block diagram.

9 V

10

7

MEH115

O AF

+

C AF

CVBS

2 V (P-P)

35

Page 33

(4) Pin Description

PIN SYMBOL DESCRIPTION

1Vi IFa Vision IF differential input

2Vi IFb Vision IF differential input

3 TADJ tuner AGC take-over adjust

(TOP)

4 PADJ phase detector adjust

5CBL black level capacitor, mute

switch input

6TPLL PLL time constant OF phase

detector

7Vo CVBS CVBS(positive) output signal

8 STD standard switch

negative = HIGH

positive = LOW

9VO AF audio frequency output signal

10 CAF decoupling capacitor of audio

frequency amplifier

PIN SYMBOL DESCRIPTION

11 Vi IC sound intercarrier input signal

12 TAGC tuner AGC output

13 Vo VID video and sound intercarrier

output signal

14 Vi VID video input signal to buffer

amplifier

15 AFC automatic frequency control

output

16 VCO1 VCO reference circuit for 2 fPC

17 VCO2 VCO reference circuit for 2 fPC

18 GND GND

19 CAGC AGC capacitor

20 VP positive supply voltage

36

Page 34

TDA9830 (TV sound AM-demodulator and audio source switch)

(1) Features

Adjustment free wideband synchronous AM demodulator

Audio source-mute switch(low noise)

Audio level according EN55049

5 to 8 V power supply or 12 V alternative

Low power consumption

(2) General Description

The TDA9830, a monolithic integrated circuit, is designed for AM-sound demodulation used in L and L'

standard. The IC provides an audio source selector and a mute switch.

(3) Block Diagram

IF

signal

V

13 14 11

4

SUPPL Y

+

BANEGAP

16

1

AGC

CONTROL

P1

V

or

P1

TDA9830

12

mute

(closed)

10

input :

open = pin 9

AGC

DETECTOR

36 97

AM output

AM input

0 dB

external

input

8

closed = pin

AF output

(4) Pin Description

PIN SYMBOL DESCRIPTION

1 IFIN sound IF differential input

signal

2 n.c. not connected

3CAGC AGC capacitor

4CREF REF voltage filtering capacitor

5 n.c. not connected

6 AMOUT AM demodulator output

7 AMIN input signal (from AM) to audio

switch

8 AFOUT output signal from audio switch

PIN SYMBOL DESCRIPTION

9 EXTIN input signal (from external) to

audio switch

10 SWITCH switch input select control

11 Vp2 supply voltage +12V

(alternative)

12 MUTE mute control

13 GND ground (0 V)

14 Vp1 supply voltage +5 to +8 V

15 n.c. not connected

16 IFIN sound IF differential input

signal

37

Page 35

TDA1519B (BTL or STEREO audio amplifier)

(1) Features

Requires very few external

components for Bridge Tied Load

(BTL)

Stereo or BTL application

High output power

Low offset voltage at output (important for BTL)

Fixed gain

Good ripple rejection

Mute/stand-by switch

Load dump protection

SC and DC short-circuit-safe to ground and VP

(2) General Description

The TDA1519B is an integrated class-B dual output amplifier in a 9-lead single in-line (SIL) plastic medium

power package. The device is primarily developed for car radio applications.

Thermally protected

Reverse polarity safe

Capability to handle high energy on outputs (VP

= 0 V)

No switch-on/switch-off plop

Protected against electrostatic discharge

Identical inputs (inverting and non-inverting)

Compatible with TDA1519A (except output

power)

(3) Block Diagram

1

60k

183

3

18.1 k

stand–by

switch

VA

15k

x1

15k

18.1 k

mute switch

VA

Vp

C

m

mute

reference

voltage

+

+

–

power stage

+

–

TDA1519B

stand–by

reference

voltage

mute

switch

PRINTING

1 NINV non-inverting input

2 GND1 ground (signal)

3 RR supply voltage ripple

rejection

4 OUT1 output 1

5 GND2 ground (substrate)

4

6 OUT2 output 2

7 Vp positive supply voltage

8 M/SS mute/stand-by switch

9 INV inverting input

8

183

9

60k

+

input

reference

voltage

VA

C

mute switch

signal

ground

275

power stage

6

m

Vp

power

ground

(substrate)

38

Page 36

MC14053BCP (IC CMOS LOGIC)

(1) Features

Triple Diode Protection on Control Inputs

Switch Function is Break Before Make

Supply Voltage range - 3.0 Vdc to 18 Vdc

Linearized transfer characteristics

(2) General Description

The MC14053B analog multiplexer are digitally controlled analog switches. The MC14053B effectively

implements an SPDT solid state switch. The device features low ON impedance and very low OFF leakage

current. Control of analog signals up to the complete supply voltage range can be achieved.

(3) Block Diagram

MC14053B

Triple 2-Channel Analog

Multiplexer/Demultiplexer

6

11

10

9

12

13

2

1

5

3

Inhibit

A

B

C

X0

X1

Y0

Y1

Z0

Z1

VDD = Pin16

VSS = Pin8

VEE = Pin7

X

Y

Z

14

15

4

39

Page 37

CP-350 CIRDUIT DESCRIPTION

The function of the circuits used in CP-350 are described in this chapter. For the component numbers used in

this description, refer to the circuit diagram.

1. Small Signal Part with TDA8362

TDA8362 is realized in BIMOS process; the high frequency bipolar process is used for video processing

and the MOS process is used for the digital part.

TDA8362 combines all small signal functions, except the tuning, required for a colour television receiver.

Newly developed internal circuitry, such as integrated luminance delay line, chroma bandpass and trap,

PLL sound demodulator and switches, reduce the number of required pins, external components and

alignments.

The reference tuned circuit is the only remaining alignment for this 52 pins (S-Dil) TV-processor.

The alignment-free SECAM add-on colour decoder circuit (TDA8395) can be used for applications with

automatic standard switching.

The internal functions of TDA8362 are

- Completely symmetrical AC-coupled vision I.F. amplifier and synchronous video demodulator

- A.G.C. detector suited for positive and negative modulation

- Tuner A.G.C., for PNP tuners

- Sample and hold A.F.C. circuit, with internal 90 phase shift

- Video pre-amplifier

- Inputs and switches for external audio, CVBS and S-VHS signals

- Sound I.F. limiter, automatic PLL demodulator and pre-amplifier with DC volume control.

- Separate supply pin to start the horizontal circuitry from the mains rectifier

- Horizontal synchronization circuit with 2 control loops

- Vertical synchronization (divider system), automatic 50/60Hz adaption

- Vertical and horizontal drive circuits

- PAL/NTSC colour decoder, with automatic standard switching

- Chroma filters (bandpass and trap) with automatic system adaption

- Luminance delay line

- Peaking circuit is the luminance channel

- Mute function

- X-ray protection possibility.

1.1. Vision I.F. Amplifier, Video Demodulator and Identification Circuit.

The vision I.F. amplifier consists of three AC-coupled differential stages.

The gain control per stage is more than 20dB, which results in a total gain control of 64dB min.

The amplifier is

completely symmetrical, which has the advantage of a less critical application; the I.F. amplifier

inputs can be

coupled directly to the SAW-filter output.

The input impedance is 2k in parallel with 3pF.

The input sensitivity for on-set of A.G.C. is 70 V (typ.), for I.F. frequencies between 38.9MHz and

58.75MHz.

The reference carrier for the video demodulator is obtained via passive regeneration of the

picture carrier. The reference tuned circuit is connected between pin 2 and 3. The IC and handle

positive and negative modulated signals, the polarity of the demodulation can be switched at pin

1(open=neg. modulation, high=pos. modulation). A transmitter identification circuit operates

independently of the synchronization circuit, to allow separate use of the front-end section and

the display section of the TDA8362.

40

Page 38

1.2. A.G.C., Tuner A.G.C. and A.F.C.

The A.G.C. detector operates at top-sync level for signals with negative modulation and at

peak-white level for positive modulated signals. This A.G.C. detector is gated for negative

modulated signals to reduce sensitivity to impulsive noise. The time constant capacitor (C216)

is connected externally at pin 48.

The tuner AGC take-over point can be set by adjusting the DC-voltage at pin 49, with a

potentiometer of 10k (R010). The tuner A.G.C. (pin 47) is an open collector output stage with

an output swing of 2mA min. the voltage swing, required by the tuner, can be obtained with an

external resistor network, connected at pin 47. Pin 47 may rise 2V above the actual supply

voltage level for min. gain.

The A.F.C. circuit is driven by the same reference signal as the video demodulator. A sample

and hold circuit avoids video bread-through from the video demodulator to the A.F.C. voltage.

The A.F.C. output voltage range is from 0 to 8V.

1.3. Sound Circuit

The sound carrier which is present at the video output pin 7 is fed via the sound bandpass to the

sound input at pin5.

This has a double function; sound I.F. input (AC) and volume control (DC). The filtered intercarrier

signal is fed to an amplifier/limiter circuit and demodulated by a PLL demodulator. This PLL

demodulator tunes automatically to the incoming frequency, hence no alignment is required. The A.F.

signal (pin 50) has an amplitude of 700mVrms at maximum volume control setting (f = 50KHz).

This volume control voltage is between 0 and 5V.

The de-emphasis capacitor (CC211) is connected externally at pin 1. The noncontrolled audio signal

(Peri-television) is also obtained from pin 1 via a amplifier buffer stage (Q730 & Q741) and has an

amplitude of 500mVrms (f=300KHz).

Audio input signal from an external source with an amplitude up to 350mVrms(+/- 6dB) can be fed to

pin 6. The audio switch is controlled via the pin 16, as described in Chapter 1.8. The volume control

operates upon the external audio input signal, when TDA8362 is switched to the external mode.

1.4. Horizontal and Vertical Synchronization

The incoming video signal, pin 15 for the video signal is fed to the synchronization separator

circuit. Internally the black level and the top sync level are detected, next the synchronization

pulses are amplified to a fixed level and sliced at 50% of that level. In this way a very good