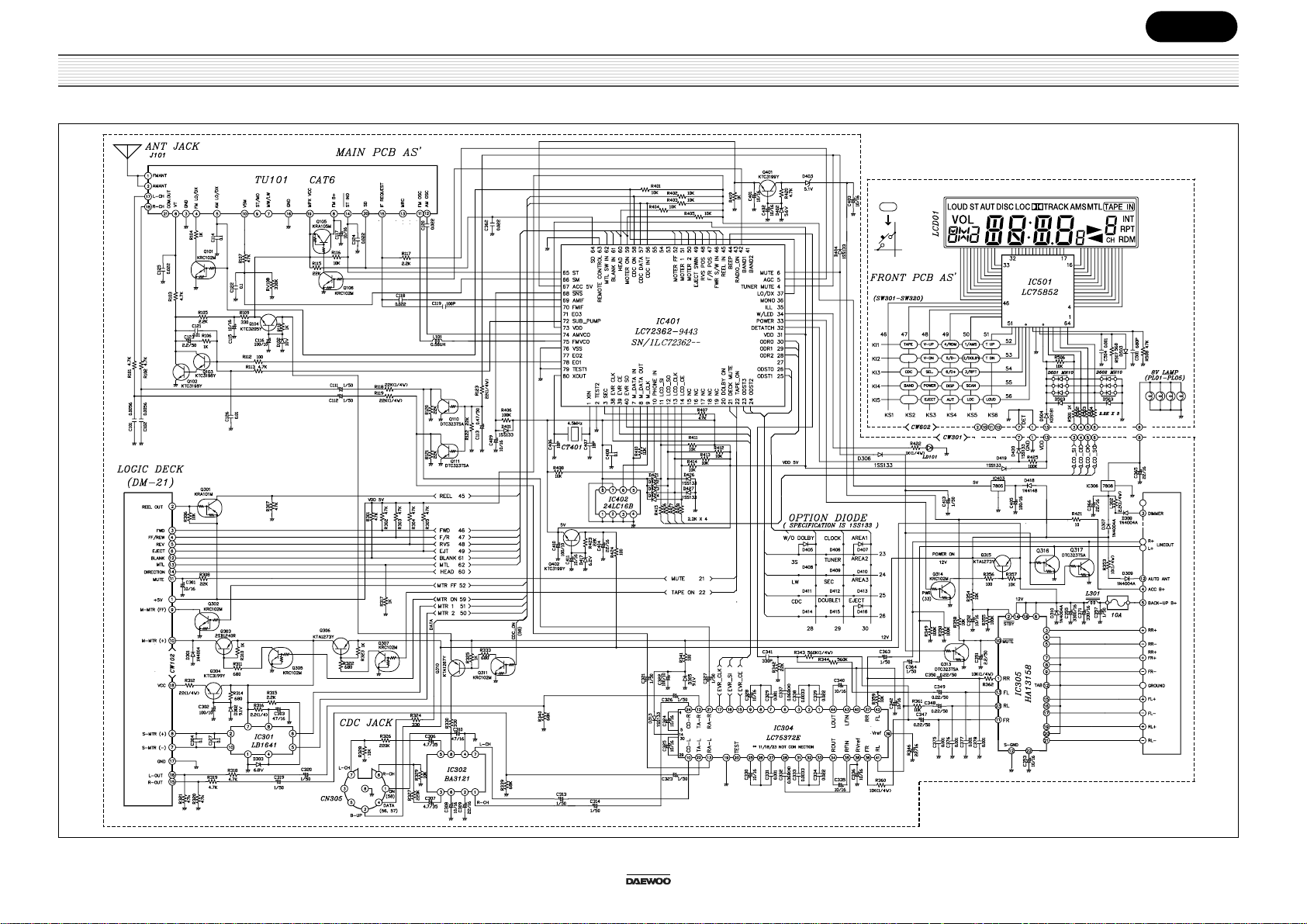

DAEWOO AKF-0305, AKF-0315 Diagram

14

5. SCHEMATIC DIAGRAMS

5-1. BASIC Series AKF-0305 / AKF-0315

Size:A3

15

5-2. RDS Series AKF-0305 / AKF-0315

SCHEMATIC DIAGRAM

Size:A3

16

5-3. OIRT Series AKF-0305 / AKF-0315

SCHEMATIC DIAGRAM

Size:A3

30

10. FUNCTION OF MICOM IC

10-1. PIN CONFIGURATION (TOP VIEW) : RDS MODEL ONLY

31

FUNCTION OF MICOM IC

10-2. PIN DESCRIPTION

PIN

1

80

78

77

71

76

73

31

75

74

72

70

69

68

67

79

51

50

PIN NAME

XIN 4.5MHz CRYSTAL

PHASE COMPARISON OUTPUT PORT

If the frequency of the partial oscillation is higher than the basic

frequency, these output high, lower than the basic frequency, output

low. Otherwise, these are high-z that those frequencies correspond.

AM 2 nd CHARGE PUMP OUTPUT PORT.

(AM FREQUENCY : 90kHz)

CAN BE SUPPLIED UP TO 6.5V

FM VCO INPUT

(the signal of the partial oscillation)

* INPUT RANGE : 0.07~1.5 Vrms

* INPUT RANGE : 0.07~1.5 Vrms

Outputs the pll lock up signal to lock up the pll frequency in

high speed.

FM IF COUNT INPUT

*

INPUT RANGE : 10.7MHz+30kHz, Vpp=0.07~1.5Vrms

AM IF COUNT INPUT

* INPUT RANGE : 450kHz + 1kHz (AM)

: 450kHz + 0.37kHz (LW)

* Vpp = 0.07 ~1.5Vrms

To check if the memory state is normal on the back-up mode.

The application circuit is illustrated on the note of back pages.

To check if it is back-up mode(LOW) or normal operation state(HIGH),

but it display clock depending on the clock option.

Connect to ground.

Dm-21 loading motor control port.

MTR1 MTR2

LOADING : HIGH LOW

EJECT : LOW HIGH

STOP : LOW LOW

AM VCO INPUT

(the signal of the partial oscillation)

XOUT

E01

E02

E03

VSS

VDD

VDD

FMIN

AMIN

SUBPD

HCTR

LCTR

SNS_

HOLD_

TEST1

TEST2

PL1

PL2

DESCRIPTION I/O

I

O

O

O

O

--

--

--

I

I

O

I

I

I

I

--

--

O

O

32

FUNCTION OF MICOM IC

PIN

59

52

53

54

55

11

12

13

14

21

40

38

39

27

28

29

30

23

24

25

26

7

8

9

63

35

PIN NAME

PJ1

PL0

DM-21 MAIN MOTOR CONTROL PORT.

INPUT DATUM FROM THE RDS DEMODULATOR IC THE

TIMING CHART OF DATA IS ILLUSTRATED ON BACK

PAGES.

KEY & LCD DRIVER IC INTERFACE PORTS

EVR IC INTERFACE PORTS.

OPTION DIODE MATRIX INPUT.

OPTION DIODE MATRIX OUTPUT.

RDS DATA MEMORY EEPROM CONTROL PORT.

MULTI-PATH INPUT PORT.

* INPUT RANGE : 0.6~0.9V

LCD BACK-LIGHTING COLOR CONTROL PORT

RESET : COLOR

---

> LOW

TWO KEY IN : COLOR CHANGE

DECK EQ IC MUTE ADJUST PORT.

PK3

PK2

INT1

PE3/SI2

PE2/SO2

PE1/SCK2

PE0

PC1

PO0

PO2

PO1

PA3

PA2

PA1

PA0

PB3

PB2

PB1

PB0

PF3

PF2

PF1

PF3

PP1

DESCRIPTION I/O

O

O

I

I

I

I

O

O

O

O

O

O

O

I

I

I

I

O

O

O

O

I

O

O

I

O

MTR_ON MTR_FF

PLAY : HIGH LOW

FF/REW : HIGH HIGH

STOP : LOW LOW

33

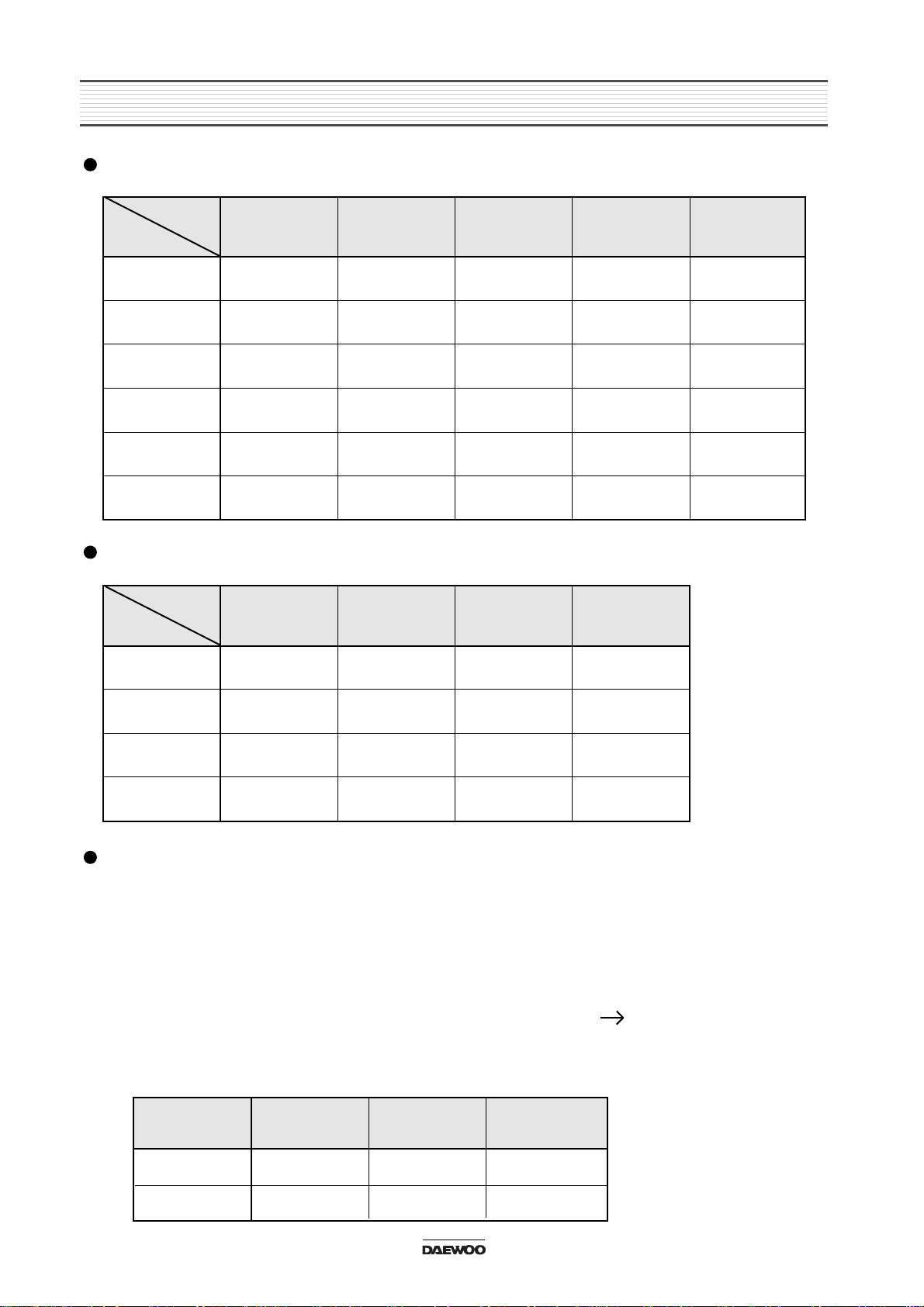

FUNCTION OF MICOM IC

KEY MATRIX TABLE

RETURN

SOURCE

KS 6 (49)

M1 (AMS)

T. UP

KI 1 (50) KI 2 (51) KI 3 (52) KI 4 (53) KI 5 (54)

T. DOWN

M2 (DOLBY)

M5

(DISC DOWN)

VOL DOWN

---

---

SEEK UP

M3 (RPT)

M6

(DISC UP)

SELECTOR

CDC/PAUSE

AUX

SEEK DOWN

LOC

TA/TA_STBY

PTY(DISP)

POWER

ON/OFF

RADIO/BAND

(LANG)

MONO

LOUD/LOC

AF/REG

ATP

TAPE EJECT

MUTE

---

M4 (SHUF)

VOL UP

TAPE/PGM

---

KS 5 (48)

KS 4 (47)

KS 3 (46)

KS 2 (45)

KS 1 (44)

KEY MATRIX TABLE

DIODE MATRIX DESCRIPTIONS

SOURCE

RETURN

ODR 3

(PA3, 27PIN)

DOUBLE 2

(D405)

---

ODST 3

(PB3, 23PIN)

ODST 2

(PB2, 24PIN)

ODST 1

(PB1, 25PIN)

ODST 0

(PB0, 26PIN)

---

LOUD/LOC

(D408)

TUNER 1,2

(D409)

AREA 2

(D410)

---

LW ENABLE

(D411)

---

AREA 3

(D413)

---

CDC/AUX IN

(D414)

DOUBLE 1

(D415)

---

CLOCK

(D406)

AREA 1

(D407)

ODR 2

(PA2, 28PIN)

ODR 1

(PA1, 29PIN)

ODR 0

(PA0, 30PIN)

-LW select (D411) 0 : LW BAND DISABLE

1 : LW BAND ENABLE

-CLOCK USE select (D406) 0 : CLOCK ENABLE

1 : CLOCK DISABLE

-LOUD/LOC USE select(D408) 0 : LOUD/LOCAL KEY DOUBLE FUNCTION

1 : LOUD KEY ONLY

-TUNER 1,2 select (D409) 0 : CAT6 or CAT7 TUNER See page 13

1 : CET6038AFL TUNER

-DOUBLE 1,2 (D415. D405)select

DOUBLE 1

(D415)

DOUBLE 2

(D405)

MEMORY 1 MEMORY 2

0

0 1 AMS

0 AMS DOLBY

---

Loading...

Loading...