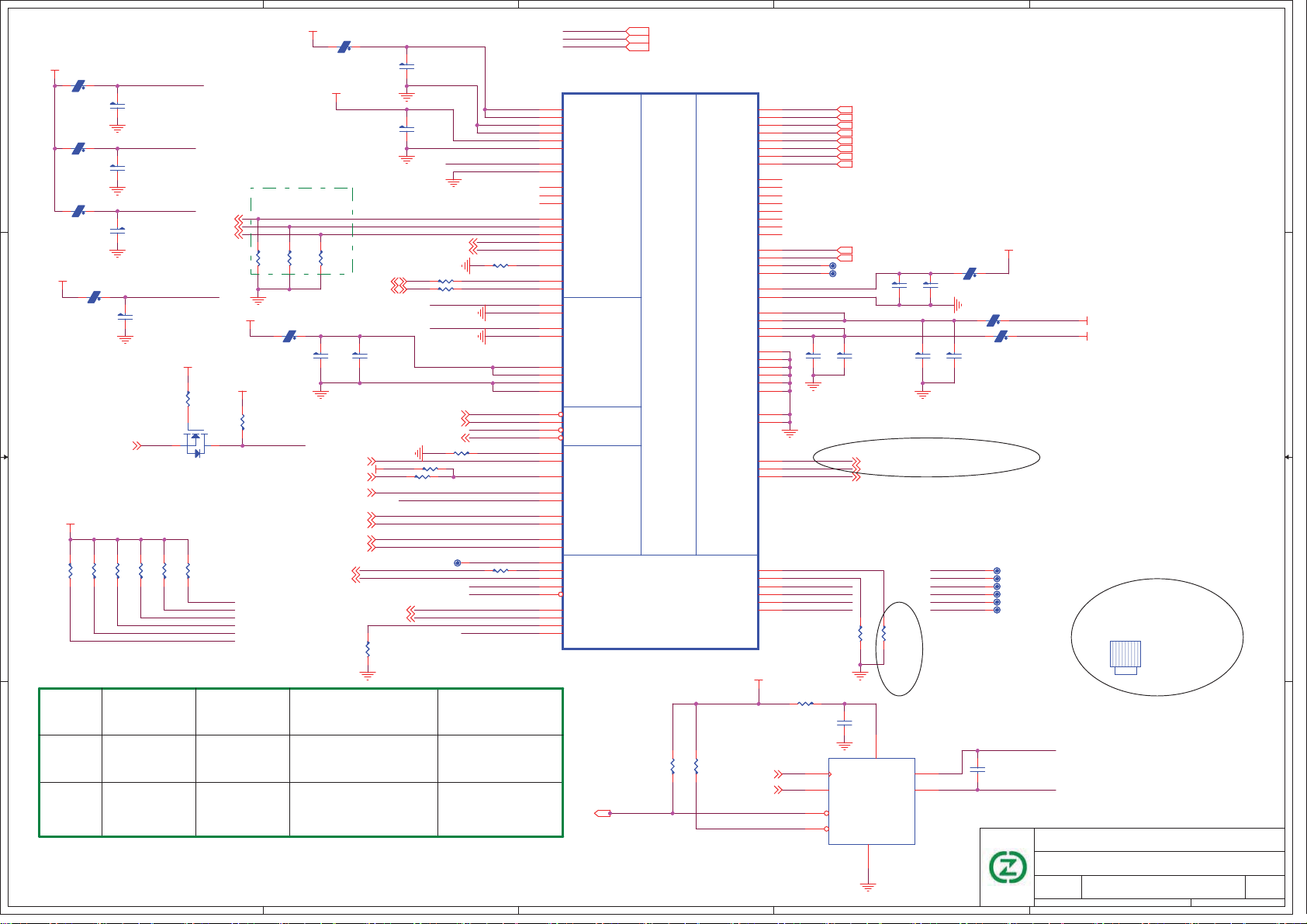

CZC Digital T11 Schematics

5 4 3 2 1

A

CZC Confidential

D

Board name: Mother Board Schematic

Project name:

T11

CZC Digital technologies Co.,LTD

1. System Block Diagram & Schematic page description;

2. Power Block Diagram & Discription;

3. Annotations & information;

Version: VerB

Start Date:Aug 29,2008

C

VerA Release Data:

4. Schematic modify Item and history;

5. Power on & off Sequence;

6. ACPI Mode Switch Timings;

7. Power On Sequence Map;

8. CLOCK Distribution;

B

Hardware drawing by:

Power drawing by:

A

Manager Sign by:

Hardware check by:

Power check by:

EMI Check by:

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A4

A4

A4

Date: Sheet

Date: Sheet

Date: Sheet

zw

zw

zw

T11 D

T11 D

T11 D

143Wednesday, August 19, 2009

143Wednesday, August 19, 2009

143Wednesday, August 19, 2009

of

of

of

5

A

4

3

2

1

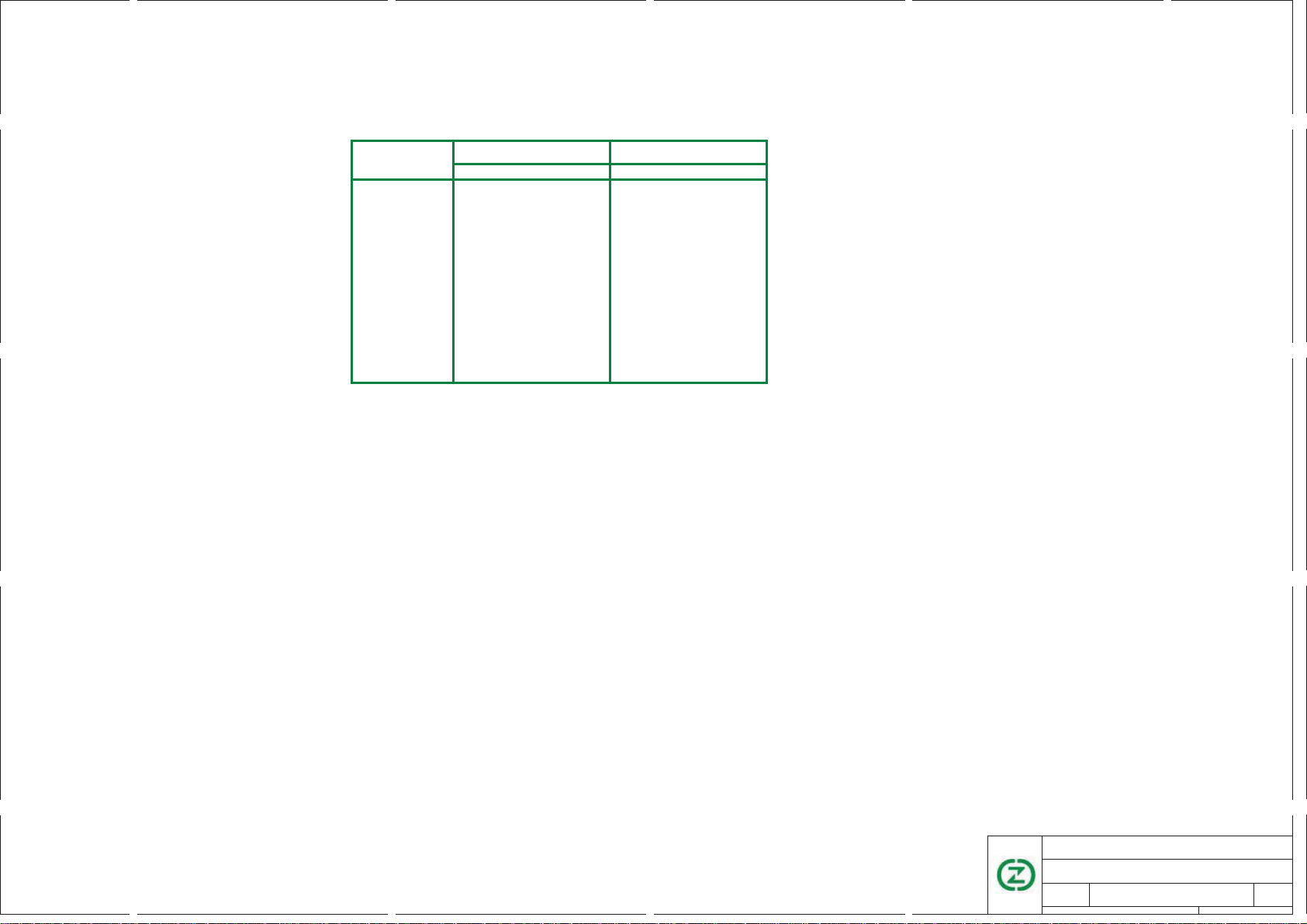

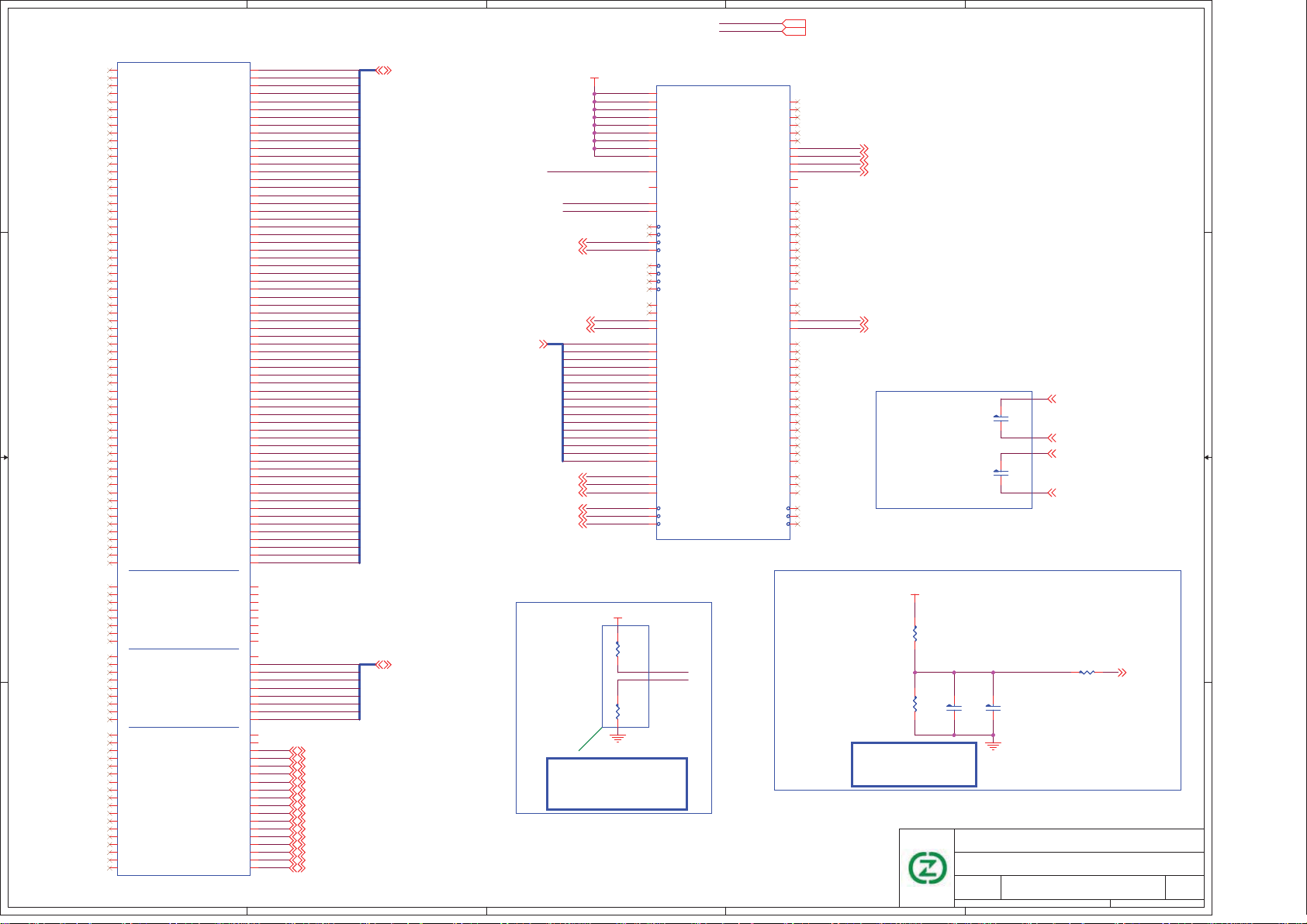

T11 System Block Ver:A

D D

EC SMBUS

G781

AMD EBGA

1G/1.5G

DDRII

HT 16X16

SO-DIMM

+V1.8,+V0.9

RJ45

PWR Switch

TFT

VGA

HDMI

LVDS

VGA

PCIE

NB

M690T/E

PCIE X1

PCIE X1

LAN Controller

RTL8111DL/RTL8102EL

USB2.0

PCIE X1

C C

SIDE PORT MEMORY

64M/128M

DDRII

A LINK 4X4

USB2.0

ODD

HDD

2.5"

SATA

SATA

SB

SB600

AZALIA LINK

Azalia Codec

ALC662

B B

R5538/TPS2231/OZ2709

mini PCIE Card

3G

mini PCIE

Card

TPA6017A2

HP Out

Co-lay

Express Card

SIM SLOT

R

L

Mic In

LPC BUS

WPC8763L

USB2.0

USB2.0 X2

Cardreader

SD/MS/MS Pro CARD

RTS5156

USB Port X2

TCM

LPC

SPI

KB Ctrl & EC

BIOS

KB Matrix

TP

TP

USB2.0

USB2.0

FINGERPRINT

Camera

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

T11 D

T11 D

T11 D

zw

zw

zw

of

of

of

243Wednesday, August 19, 2009

243Wednesday, August 19, 2009

243Wednesday, August 19, 2009

A

5

A

4

3

2

1

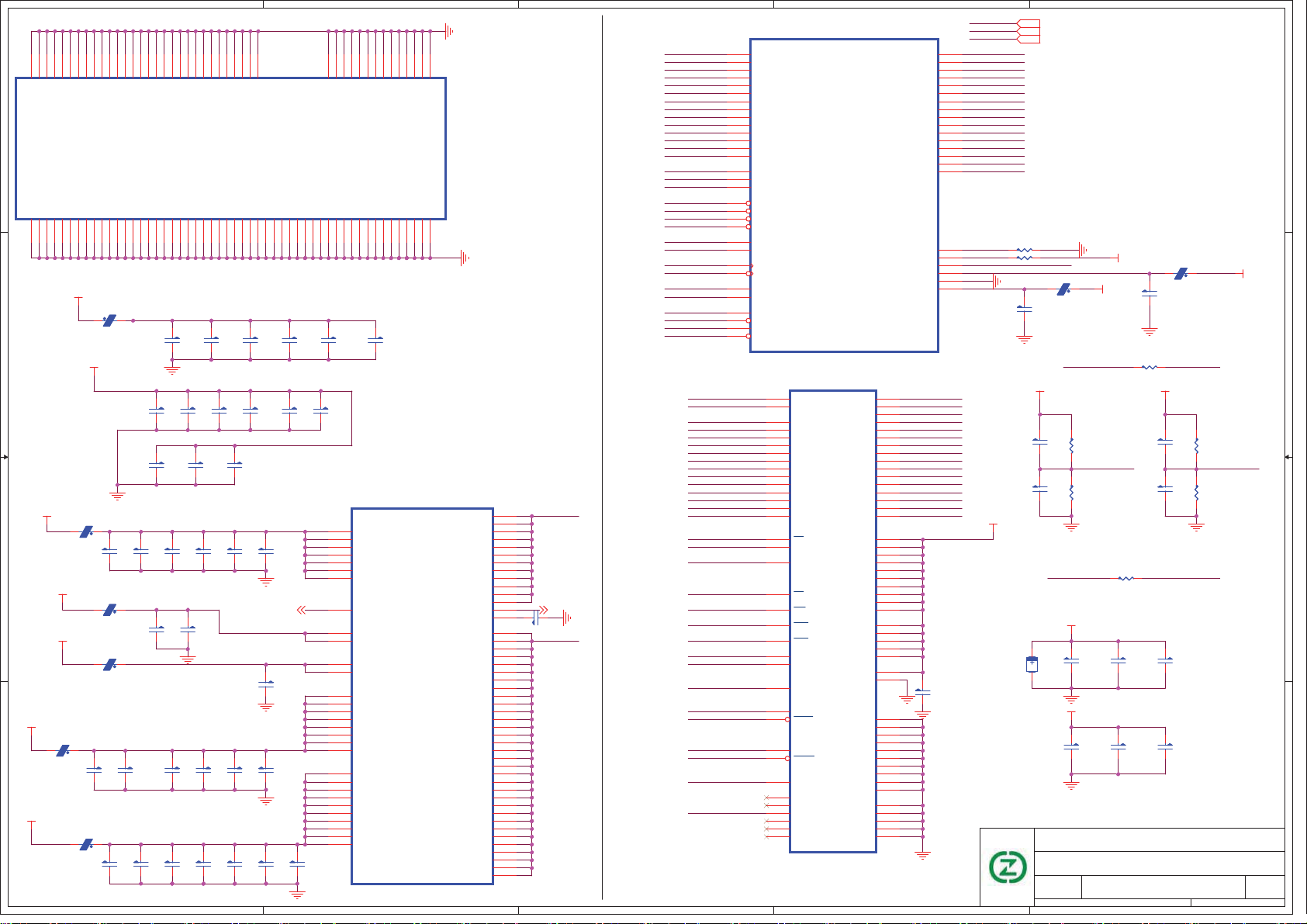

D D

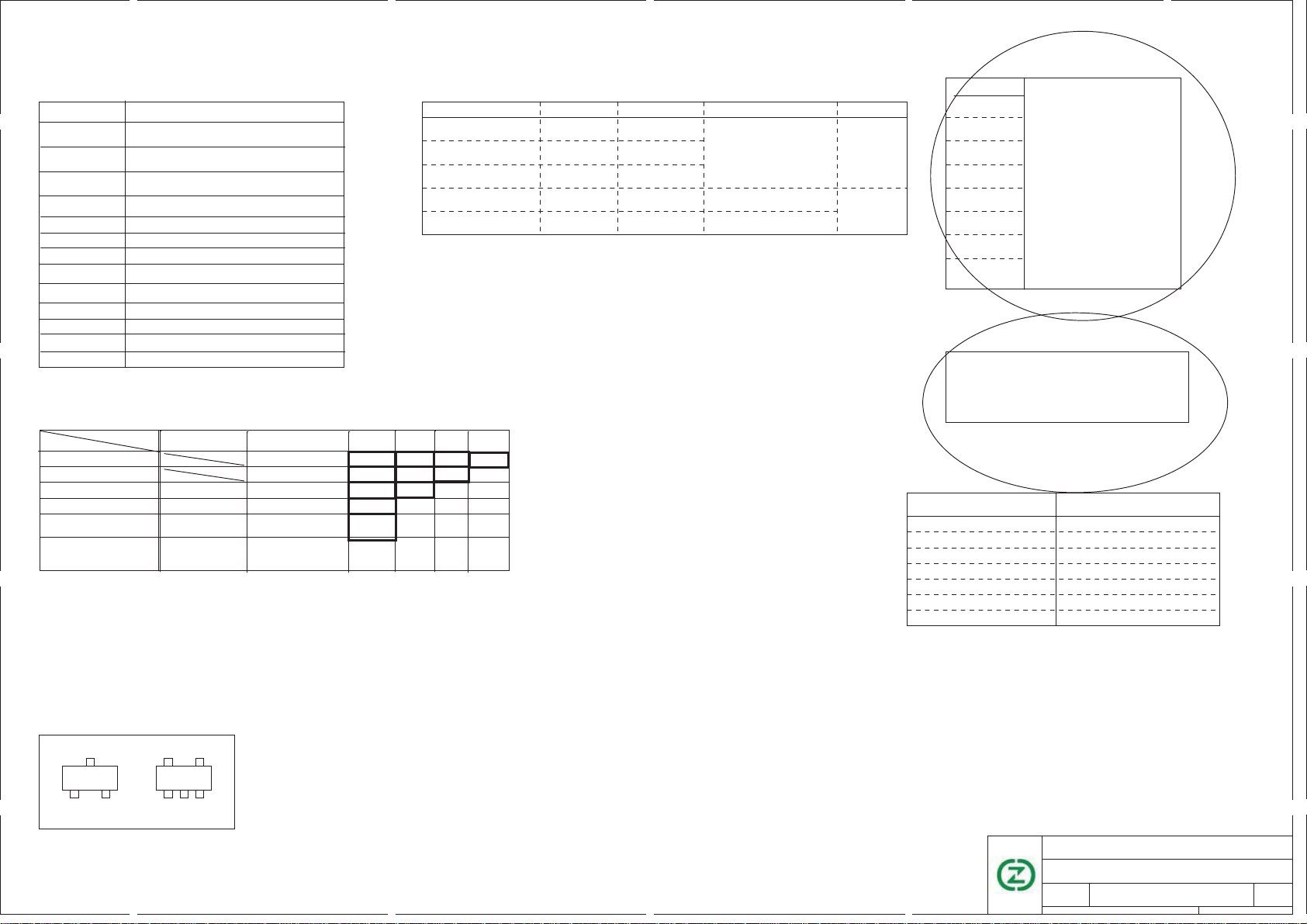

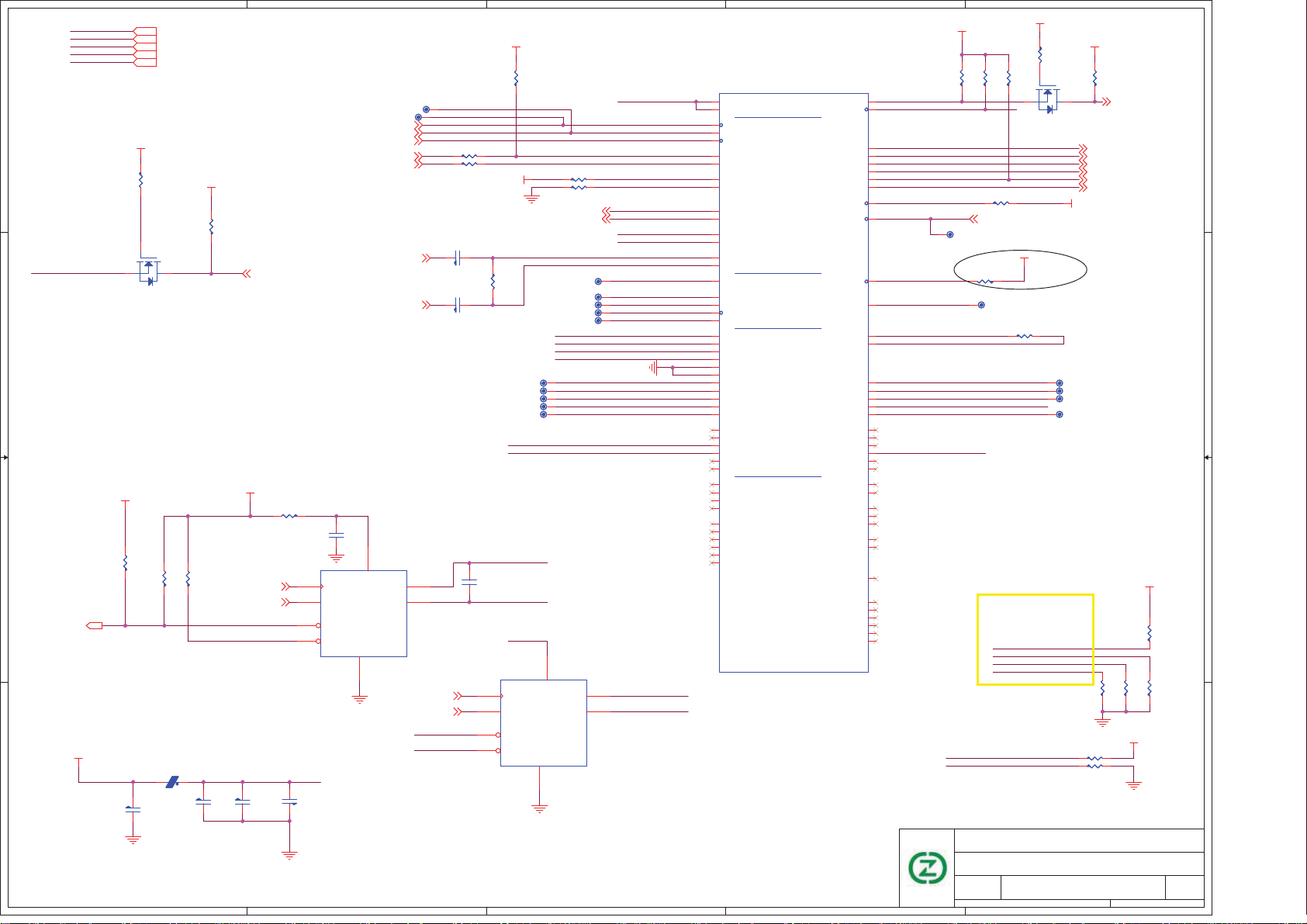

POWER RAIL

+V3.3AUX

+V5AUX

+V1.2AUX

+V1.8

+V0.9

+V5S

+V3.3S

+V2.5S

+V1.8S

+V1.5S

C C

+V1.2S

+Vcore

AC Mode Battery Mode

S0 S1 S3 S4 S5

ON ONONON ON

ON ON

ON

ON

ON

ONON ON

ONONON

ON

ON OFFON

OFF OFF OFFON ON

OFF OFF OFFON ON

ON

OFFON ON

S0 S1 S3 S4 S5

ON

ON ON ON

ON

OFFOFF

OFF

OFFOFF

OFFOFFOFFONON

OFFOFFOFFONON

OFFOFFOFFONON

OFFOFFOFFONON OFFOFFOFFONON

ON

ON OFFON

ON

ONONON

ONONON

ON

OFF OFF OFFON ON

OFF OFF OFFON ON

OFF OFF

OFF OFF

OFF OFF

OFFOFF

OFF

OFFON ON

OFFOFF

OFFOFFOFFONON

OFFOFFOFFONON

OFFOFFOFFONON

B B

A

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

T11 D

T11 D

T11 D

zw

zw

zw

of

of

of

343Wednesday, August 19, 2009

343Wednesday, August 19, 2009

343Wednesday, August 19, 2009

5

A

4

3

2

1

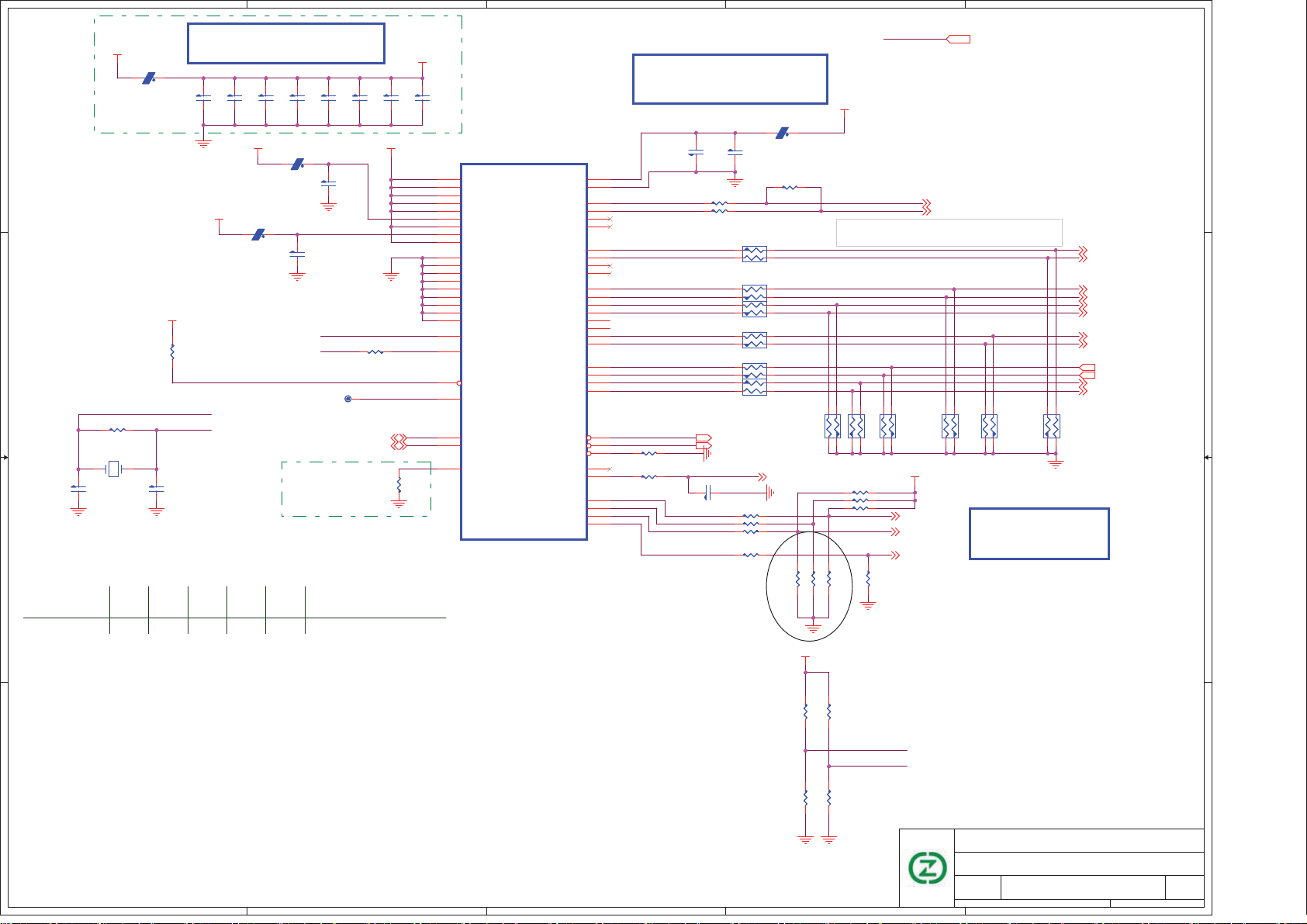

Board stack up description

Voltage Rails

D D

C C

+VDC

+VCC_core

+V1.05S

+V0.9S

+V1.5S

+V1.8

+V3.3AUX

+V3.3S

+V5AUX

+V5S

Primary DC system power supply(9V-12V)

Core/VTT voltage for processor

10V+V10

1.05V foe 910GML core/Hub interface

0.9V DDRII Termination voltage

1.5V for hublink and ICH4-M core and AGP VDDQ

1.8V power rail for DDRII

3.3V always on power rail

3.3V main power rail

5V for ICH4M's VCC5Refsus

5V main power rail

+Vcore:0.75V-1.1V

I2C SMB Address

Device

Clock Generator

SO-DIMM0

OZ8805LN

Thermal Diode G781

Address

1101 001x

1010 000x

0001 011x

1001 100x

Hex(W/R)

D2H/D3H

A0H/A1H

16H/17H

98H/99H

Bus

SMB_CLK/DATA

EC_I2C_CLK2/DATA2

EC_I2C_CLK/DATA

Master

SCH

EC

Power States

state

Full ON

S1M(Power On Suspend)

S3(Suspend to RAM)

S4(Suspend to DISK)

S5/Soft Off

With AC IN

G3

With Battery

signal

PM_SLPMODE

HIGH

LOW

LOW

LOW

PM_SLPRDY#

HIGH

HIGH

LOW

LOW

LOW

LOW

+V*AUX

ON

ON

ON

ON

ON

OFF

+V*

ON

ON

OFF

OFF

OFF

+V*S

ON

ON

OFF

OFF

OFF

OFF

CLOCKS

ON

LOW

OFF

OFF

OFF

OFF

Wake up Events

B B

PCB Layers

Top(Signal1)

Signal2

Ground

Signal3

Signal4

Ground

Power

Bottom(Signal5)

Trace Impedence:55ohm +/-15%

PCB Layer Difference signal Impedence list

USB signal difference impedence 90ohm

LVDS signal difference impedence 100ohm

DDRII signal difference impedence 85ohm

DDRII CLK signal difference impedence 70ohm

Wake Events

LID switch from EC

Power Button from EC

Keyboard from EC

USB device

State Supported(AC)

S3,S4 support

S3,S4,S5 support

No

No

[Option]:ns -- Component marked "ns" is not stuff

[Use State]:new --Component Marked "new" is new Materiel.

PCB Footprints

SOT23

1

3

5

4

SOT23_5

2

3

2ON1

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

T11 D

T11 D

T11 D

zw

zw

zw

of

of

of

443Wednesday, August 19, 2009

443Wednesday, August 19, 2009

443Wednesday, August 19, 2009

A

5

4

3

+V1.2S 7,11,12,14,16,17,26,31,33

2

1

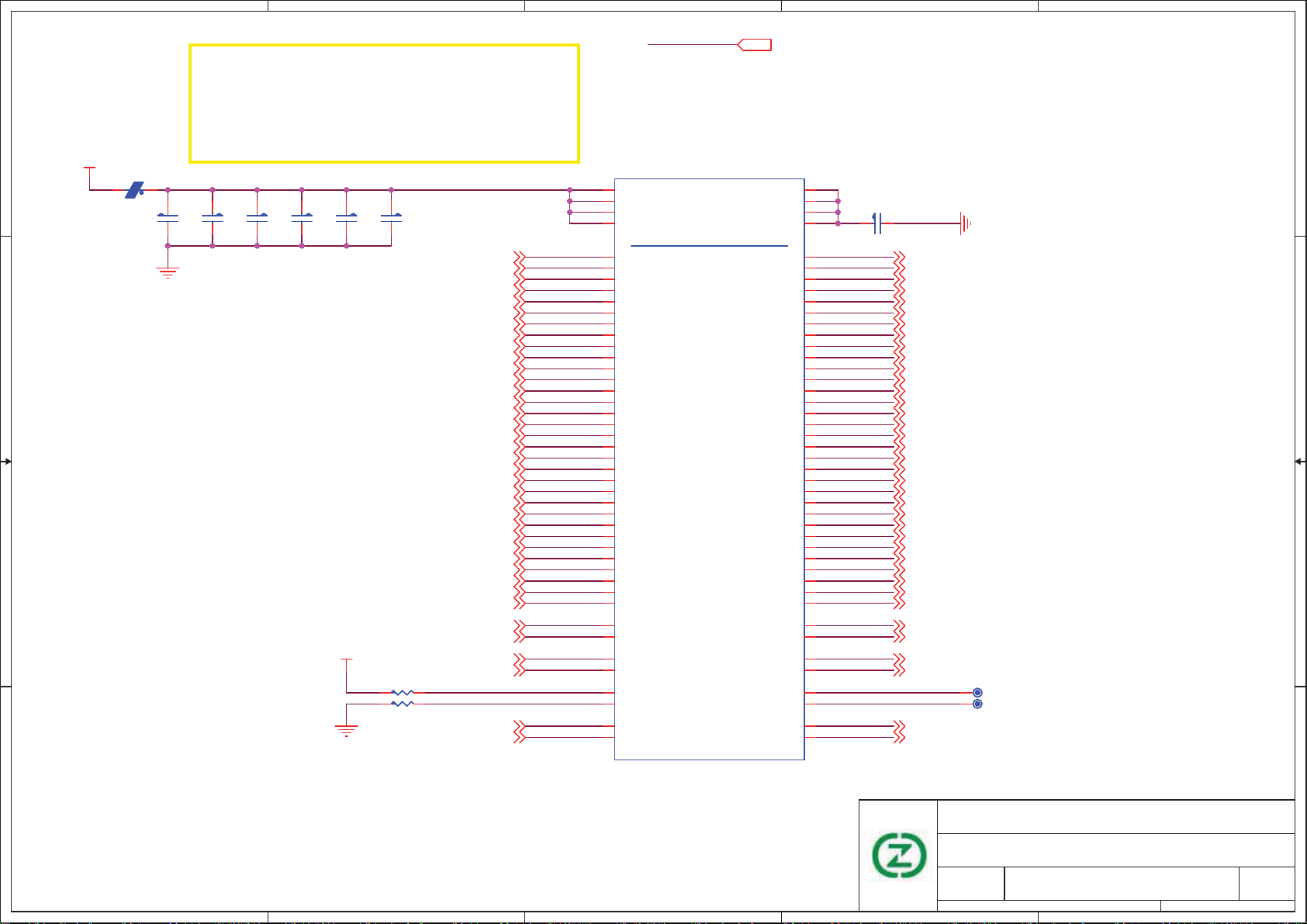

DESIGN NOTE:

VLDT must be routed as a pour or a trace at least 200 mils wide.

VLDT may be routed from the source to either ALx balls or Fx balls.

D D

+V1.2S

FB1 100ohm@100MHz,3AFB1 100ohm@100MHz,3A

C C

B B

Choose whichever makes routing simpler.

These six capacitors must be placed very near the selected balls.

The "other" set of balls must be decoupled with a 4.7uF cap.

C5

C5

C4

C4

C3

C1

C1

4.7uF/10V,X5R

4.7uF/10V,X5R

C3

C2

C2

0.22uF/10V,Y5V

0.22uF/10V,Y5V

4.7uF/10V,X5R

4.7uF/10V,X5R

180pF/25V,X7R

180pF/25V,X7R

0.22uF/10V,Y5V

0.22uF/10V,Y5V

+V1.2S

C6

C6

180pF/25V,X7R

180pF/25V,X7R

HT_CADIN15_P10

HT_CADIN15_N10

HT_CADIN14_P10

HT_CADIN14_N10

HT_CADIN13_P10

HT_CADIN13_N10

HT_CADIN12_P10

HT_CADIN12_N10

HT_CADIN11_P10

HT_CADIN11_N10

HT_CADIN10_P10

HT_CADIN10_N10

HT_CADIN9_P10

HT_CADIN9_N10

HT_CADIN8_P10

HT_CADIN8_N10

HT_CADIN7_P10

HT_CADIN7_N10

HT_CADIN6_P10

HT_CADIN6_N10

HT_CADIN5_P10

HT_CADIN5_N10

HT_CADIN4_P10

HT_CADIN4_N10

HT_CADIN3_P10

HT_CADIN3_N10

HT_CADIN2_P10

HT_CADIN2_N10

HT_CADIN1_P10

HT_CADIN1_N10

HT_CADIN0_P10

HT_CADIN0_N10

HT_CLKIN1_P10

HT_CLKIN1_N10

HT_CLKIN0_P10

HT_CLKIN0_N10

51R1 51R1

51R2 51R2

HT_CTLIN0_P10

HT_CTLIN0_N10

AL4

AL3

AL2

AL1

W7

W6

M8

M7

H4

H3

M2

M1

H2

H1

M3

M4

Y6

Y5

U6

U5

R7

R6

L6

L5

T3

T4

T2

T1

P3

P4

P2

P1

K3

K4

K2

K1

P6

P5

P8

P9

V2

V1

J6

J5

U1AU1A

VLDT_B4

VLDT_B3

VLDT_B2

VLDT_B1

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

VLDT_A4

VLDT_A3

VLDT_A2

VLDT_A1

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

F4

F3

F2

F1

Y9

Y8

AB6

AB5

AC7

AC6

AE6

AE5

AE9

AE8

AH3

AH4

AK3

AK4

AK1

AK2

Y1

Y2

Y4

Y3

AB1

AB2

AB4

AB3

AD4

AD3

AF1

AF2

AF4

AF3

AH1

AH2

AF6

AF5

AD1

AD2

AB8

AB9

V4

V3

C7 4.7uF/10V,X5RC7 4.7uF/10V,X5R

HT_CPU_CTLOUT1_PHT_CTLIN1_P

HT_CPU_CTLOUT1_NHT_CTLIN1_N

HT_CADOUT15_P 10

HT_CADOUT15_N 10

HT_CADOUT14_P 10

HT_CADOUT14_N 10

HT_CADOUT13_P 10

HT_CADOUT13_N 10

HT_CADOUT12_P 10

HT_CADOUT12_N 10

HT_CADOUT11_P 10

HT_CADOUT11_N 10

HT_CADOUT10_P 10

HT_CADOUT10_N 10

HT_CADOUT9_P 10

HT_CADOUT9_N 10

HT_CADOUT8_P 10

HT_CADOUT8_N 10

HT_CADOUT7_P 10

HT_CADOUT7_N 10

HT_CADOUT6_P 10

HT_CADOUT6_N 10

HT_CADOUT5_P 10

HT_CADOUT5_N 10

HT_CADOUT4_P 10

HT_CADOUT4_N 10

HT_CADOUT3_P 10

HT_CADOUT3_N 10

HT_CADOUT2_P 10

HT_CADOUT2_N 10

HT_CADOUT1_P 10

HT_CADOUT1_N 10

HT_CADOUT0_P 10

HT_CADOUT0_N 10

HT_CLKOUT1_P 10

HT_CLKOUT1_N 10

HT_CLKOUT0_P 10

HT_CLKOUT0_N 10

TP1TP1

TP2TP2

HT_CTLOUT0_P 10

HT_CTLOUT0_N 10

A A

Title

Title

Title

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

2

CZC Technology

CZC Technology

CZC Technology

<Title>

<Title>

<Title>

A4

A4

A4

zw

zw

zw

T11 D

T11 D

T11 D

543Wednesday, August 19, 2009

543Wednesday, August 19, 2009

543Wednesday, August 19, 2009

of

of

1

of

A

U1CU1C

AN13

RSVD1

AL14

RSVD2

AL16

RSVD3

AN17

RSVD4

AN12

RSVD5

AM12

RSVD6

AM16

RSVD7

4 4

3 3

2 2

1 1

AN16

AL18

AN19

AM24

AN24

AM18

AN18

AL22

AN23

AM25

AL26

AN28

AL28

AL24

AN25

AN27

AM28

AM29

AL30

AL32

AL33

AK28

AN29

AM31

AM32

E33

D31

B31

A31

F33

F31

C32

B32

C30

A29

B26

A26

B30

A30

A27

C26

A24

B24

C18

A18

A25

C24

C20

A19

C16

A16

B14

A13

B18

A17

C14

A14

K33

K31

G32

F32

L33

K32

H31

G33

H33

AN15

AN20

AK26

AN31

C33

C28

A20

D14

H32

AM14

AN14

AL20

AM20

AN26

AM26

AN30

AM30

D33

D32

B28

A28

A21

B20

B16

A15

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD54

RSVD55

RSVD56

RSVD57

RSVD58

RSVD59

RSVD60

RSVD61

RSVD62

RSVD63

RSVD64

RSVD65

RSVD66

RSVD67

RSVD68

RSVD69

RSVD70

RSVD71

RSVD72

RSVD73

RSVD74

RSVD75

RSVD76

RSVD77

RSVD78

RSVD79

RSVD80

RSVD81

J33

RSVD82

RSVD83

RSVD84

RSVD85

RSVD86

RSVD87

RSVD88

RSVD89

RSVD90

RSVD91

RSVD92

RSVD93

RSVD94

RSVD95

RSVD96

RSVD97

RSVD98

RSVD99

A

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_DM8

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_H8

MA_DQS_L8

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

AG11

AH11

AJ12

AJ14

AF11

AF12

AG12

AH12

AK14

AF15

AH19

AK20

AF14

AG14

AF17

AG19

AG20

AJ20

AF22

AK24

AF19

AF20

AJ23

AG23

AF23

AF25

AH27

AK30

AJ25

AG25

AJ26

AJ28

D28

G28

D26

E26

F30

E29

F27

H26

H25

D24

H22

E22

F26

G26

D22

G23

G22

G20

G15

F15

D20

F22

D16

E17

H15

H14

G12

H12

E15

E14

E11

F11

K30

J29

G29

F29

L28

L29

H29

H27

H30

AL12

AK16

AK22

AJ27

E27

E23

H19

G14

J27

J26

AJ11

AK12

AG15

AH15

AH22

AG22

AG26

AH26

E28

F28

E25

F25

G17

H17

E12

F12

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DQS7_P 9

MEM_MA_DQS7_N 9

MEM_MA_DQS6_P 9

MEM_MA_DQS6_N 9

MEM_MA_DQS5_P 9

MEM_MA_DQS5_N 9

MEM_MA_DQS4_P 9

MEM_MA_DQS4_N 9

MEM_MA_DQS3_P 9

MEM_MA_DQS3_N 9

MEM_MA_DQS2_P 9

MEM_MA_DQS2_N 9

MEM_MA_DQS1_P 9

MEM_MA_DQS1_N 9

MEM_MA_DQS0_P 9

MEM_MA_DQS0_N 9

B

MEM_MA_DATA[63..0] 9

MEM_MA_DM[7..0] 9

B

C

+V0.9

A12

VTT1

B12

VTT2

C12

VTT3

D12

VTT4

AK10

VTT5

AN10

VTT6

AL10

VTT7

AM10

VTT8

B11

CPU_M_VREF_SUS

M_ZN

M_ZP

MEM_MA0_CS_L19

MEM_MA0_CS_L09

MEM_MA_CKE19 MEM_MA1_ODT0 9

MEM_MA_CKE09

MEM_MA_ADD[15..0]9

MEM_MA_BANK29

MEM_MA_BANK19

MEM_MA_BANK09

MEM_MA_RAS#9

MEM_MA_CAS#9

MEM_MA_WE#9

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

+V1.8

LAYOUT NOTE: Keep

trace to resistors less

than 1.5" from CPU pin.

C

A11

B10

AG9

AH9

AH29

AE29

AH30

AF29

AK33

AF33

AJ32

AF31

N33

P32

M30

M28

P30

M29

AG28

P28

T30

AC28

P27

R26

R27

U28

V30

U27

Y30

AB29

W29

AC26

R29

AC29

AE28

AC27

AF30

AE27

R4

39.2,1%R439.2,1%

R5

39.2,1%R539.2,1%

VTT9

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA1_CS_L1

MA1_CS_L0

MA0_CS_L1

MA0_CS_L0

RSVD100

RSVD101

RSVD102

RSVD103

RSVD104

RSVD105

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

M_ZN

M_ZP

U1BU1B

MA1_CLK_H2

MA1_CLK_L2

MA1_CLK_H1

MA1_CLK_L1

MA1_CLK_H0

MA1_CLK_L0

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MA0_CLK_H0

MA0_CLK_L0

RSVD106

RSVD107

RSVD108

RSVD109

RSVD110

RSVD111

RSVD112

RSVD113

RSVD114

RSVD115

RSVD116

RSVD117

RSVD118

RSVD119

MA1_ODT0

MA0_ODT0

RSVD120

RSVD121

RSVD122

RSVD123

RSVD124

RSVD125

RSVD126

RSVD127

RSVD128

RSVD130

RSVD131

RSVD132

RSVD133

RSVD134

RSVD135

RSVD136

RSVD137

RSVD138

RSVD139

RSVD140

RSVD141

RSVD142

AH17

AG17

E20

E19

AB27

AB26

AK18

AJ17

D18

F19

Y28

Y27

AN21

AM21

A22

A23

AB33

AB32

AN22

AM22

C22

B22

AA32

AA33

AH31

AH33

AF27

AG29

P33

P31

AJ33

T32

T31

AD32

T33

V32

U33

V33

V31

W33

Y31

Y33

Y32

AC33

R33

AD33

AE33

AF32

AH32

AG33

D

+V1.8 7,8,9,28,32,33

+V0.9 8,9,26,32

LAYOUT NOTE: Place

close to CPU.

D

MEM_MA0_CLK2_P 9

MEM_MA0_CLK2_N 9

MEM_MA0_CLK1_P 9

MEM_MA0_CLK1_N 9

MEM_MA0_ODT0 9

DESIGN NOTE: Place close

to CPU within 1.5".

+V1.8

R3

15,1%R315,1%

C10

C10

R6

15,1%R615,1%

0.1uF/16V,X7R

0.1uF/16V,X7R

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

E

MEM_MA0_CLK2_P 9

C8

C8

1.5pF/50V,NPO

1.5pF/50V,NPO

MEM_MA0_CLK2_N 9

MEM_MA0_CLK1_P 9

C9

C9

1.5pF/50V,NPO

1.5pF/50V,NPO

MEM_MA0_CLK1_N 9

CPU_M_VREF_SUS

C11

C11

1000pF/50V,X7R

1000pF/50V,X7R

CZC Technology

CZC Technology

CZC Technology

R469 0

R469 0

T11 D

T11 D

T11 D

E

ns

ns

M_VREF 9,32

zw

zw

zw

of

643Wednesday, August 19, 2009

of

643Wednesday, August 19, 2009

of

643Wednesday, August 19, 2009

5

+V1.8 6,8,9,28,32,33

+V3.3S 9,11,12,13,15,16,17,18,19,20,21,24,25,26,27,28,31,33,34

+V3.3AUX 14,15,17,18,20,21,24,26,27,28,29,30,31,32,33

+V1.2S 5,11,12,14,16,17,26,31,33

+V2.5S 26,33

D D

+V1.8

R17

R17

10K

10K

CPU_PH_G

1

CPU_PROCHOT#_1P8V

C C

B B

PM_THRM_DN#11,30

+V2.5S

A A

2

+V3.3AUX

R32

R32

R24

R24

4.7K

4.7K

4.7K

4.7K

ns

ns

FB2 300ohm/100MHz,0.6AFB2 300ohm/100MHz,0.6A

C18

C18

10uF/6.3V,X5R

10uF/6.3V,X5R

5

+V3.3S

R19

R19

4.7K

4.7K

Q2

BSS138Q2BSS138

3

R25

R25

4.7K

4.7K

ns

ns

G781_PULLHIGH

C19

C19

4.7uF/10V,X5R

4.7uF/10V,X5R

+V3.3S

EC_SMB1_CLK26,27,29

EC_SMB1_DAT26,27,29

SOIC8_1P27_3P9

SOIC8_1P27_3P9

500mA

C20

C20

0.22uF/10V,Y5V

0.22uF/10V,Y5V

PROCHOT# 15,27

R23

R23

100

100

0.1uF/16V,X7R

0.1uF/16V,X7R

CPU_VDDA_RUN

C14

C14

8

7

6

4

C21

C21

3900pF/50V,X7R

3900pF/50V,X7R

12

SMBCLK

SMBDATA

ALERT#

THERM#

4

LDT_RST#14

SB_CPUPWRGD14

CPU_LDTSTOP#11,14

vdd

1

VCC

G781

G781

ADM1032AR

ADM1032AR

LM86CIM

LM86CIM

MAX6657MSA

MAX6657MSA

SOIC-8

SOIC-8

GND

5

4

TP5TP5

TP3TP3

CPU_SIC14

CPU_SID14

CPUCLK_P13

CPUCLK_N13

U2

U2

DXP

DXN

W83L771ASG

W83L771ASG

EC_SMB1_CLK26,27,29

EC_SMB1_DAT26,27,29

C12 3900pF/50V,X7RC12 3900pF/50V,X7R

C13 3900pF/50V,X7RC13 3900pF/50V,X7R

2

2200pF/25V,X7R

2200pF/25V,X7R

3

PM_THRM_DN#

G781_PULLHIGH

TSSOP8_P65_3P0

TSSOP8_P65_3P0

C15

C15

0R13ns0R13

0R16ns0R16

12

+V1.8

ns

ns

+V1.2S

CPU_VDD_RUN_FB_P34

CPU_VDD_RUN_FB_N34

R20

R20

169,1%

169,1%

TP13TP13

TP15TP15

TP17TP17

TP19TP19

TP20TP20

CPU_THERMDA

CPU_THERMDC

8

SMBCLK

7

SMBDATA

6

ALERT#

4

THERM#

R8

300R8300

CPU_SIC_R

CPU_SID_R

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

TP7TP7

TP8TP8

TP9TP9

TP11TP11

TP12TP12

CPU_TEST25_H_BYPASSCLK_P

CPU_TEST25_L_BYPASSCLK_N

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

CPU_THERMDC

CPU_THERMDA

vdd

U3

U3

1

DXP

VCC

DXN

G781

G781

ADM1032AR

ADM1032AR

LM86CIM

LM86CIM

MAX6657MSA

MAX6657MSA

SOIC-8

SOIC-8

GND

5

W83L771 TSSOP8

W83L771 TSSOP8

ns

ns

3

CPU_VDDA_RUN

44.2,1%R14 44.2,1%R14

44.2,1%R18 44.2,1%R18

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

2

3

3

CPU_HTREF1

CPU_HTREF0

CPU_THERMDA

CPU_THERMDC

AK6

AM2

AM6

AN4

AN5

V10

AM9

AK9

AH8

AN8

AK8

AL8

AM8

AN3

AH7

AL6

AM5

M31

M33

M32

W27

W26

AJ29

P26

M26

AJ30

AJ9

AJ5

AJ7

L32

A8

B8

V9

E2

E1

A6

A7

A9

B9

A5

B6

H8

J8

C8

D9

H7

C6

U1DU1D

VDDA2

VDDA1

RESET_L

PWROK

LDTSTOP_L

SIC

SID

HT_REF1

HT_REF0

VDD_FB_H

VDD_FB_L

VDDIO_FB_H

VDDIO_FB_L

CLKIN_H

CLKIN_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

RSVD143

RSVD144

RSVD145

RSVD146

RSVD147

RSVD148

RSVD149

RSVD150

RSVD151

RSVD152

2

THERMTRIP_L

PROCHOT_L

VID5

VID4

VID3

VID2

VID1

VID0

CPU_PRESENT_L

PSI_L

DBREQ_L

TDO

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD153

RSVD154

RSVD155

RSVD156

RSVD157

RSVD158

RSVD159

RSVD160

RSVD161

RSVD162

RSVD163

RSVD164

RSVD165

RSVD166

2

CPU_THERMTRIP#

AJ6

CPU_PROCHOT#_1P8V

AN6

CPU_VID5CPU_VID5

B2

CPU_VID4

C2

CPU_VID3

C1

CPU_VID2CPU_VID2

D2

CPU_VID1

D1

CPU_VID0CPU_VID0

D3

CPU_PRESENT#

AM3

E4

CPU_DBREQ#

AN9

CPU_TDO

AN7

CPU_TEST29_H_FBCLKOUT_P

E9

CPU_TEST29_L_FBCLKOUT_N

D10

CPU_TEST24_SCANCLK1

AH6

CPU_TEST23_TSTUPD

AG8

CPU_TEST22_SCANSHIFTEN

AN11

CPU_TEST21_SCANEN

F9

CPU_TEST20_SCANCLK2

AM7

G11

H11

AJ8

CPU_TEST26

AM4

D7

B5

L27

B25

G6

A10

B7

E8

G5

G7

AB31

AB30

AK31

AD31

AD30

AK32

1

+V3.3AUX

R7

10KR710K

1

T11 D

T11 D

T11 D

Q1

BSS138Q1BSS138

3

+V1.8

TP14TP14

TP16TP16

TP18TP18

TP21TP21

R12

R12

4.7K

4.7K

THERMTRIP# 15

CPU_VID5 34

CPU_VID4 34

CPU_VID3 34

CPU_VID2 34

CPU_VID1 34

CPU_VID0 34

R27

R27

300

300

510R30 510R30

510R31 510R31

1

+V1.8

R28

R28

300

300

+V1.8

zw

zw

zw

743Wednesday, August 19, 2009

743Wednesday, August 19, 2009

743Wednesday, August 19, 2009

R10

R10

300

300

R11

R11

300

300

+V1.8

+V1.8

R9

300R9300

2

R151KR15

1K

PSI_L 34

TP6TP6

+V1.8

300R21 300R21

TP10TP10

R22

R22

80.6,1%

80.6,1%

DESIGN NOTE: Resistors

required to fix Errata 133.

CPU_TEST26

CPU_TEST18_PLLTEST1

CPU_TEST19_PLLTEST0

CPU_TEST21_SCANEN

CPU_TEST25_H_BYPASSCLK_P

CPU_TEST25_L_BYPASSCLK_N

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

R26

R26

300

300

R29

R29

300

300

of

of

of

5

+VCC_CORE

D D

C C

B B

K10

K12

K14

K18

K20

K21

K23

K25

L11

L13

M10

M12

M25

N11

N24

N25

P15

P18

P20

P24

P25

A3

A4

B3

B4

C3

C4

D4

D5

D6

E5

E6

E7

F5

F6

F7

F8

G8

G9

H9

J9

J10

J12

J14

J18

J20

J21

J23

L7

L9

M5

N9

U1EU1E

VDDC#A3

VDDC#A4

VDDC#B3

VDDC#B4

VDDC#C3

VDDC#C4

VDDC#D4

VDDC#D5

VDDC#D6

VDDC#E5

VDDC#E6

VDDC#E7

VDDC#F5

VDDC#F6

VDDC#F7

VDDC#F8

VDDC#G8

VDDC#G9

VDDC#H9

VDDC#J9

VDDC#J10

VDDC#J12

VDDC#J14

VDDC#J18

VDDC#J20

VDDC#J21

VDDC#J23

VDDC#K10

VDDC#K12

VDDC#K14

VDDC#K18

VDDC#K20

VDDC#K21

VDDC#K23

VDDC#K25

VDDC#L7

VDDC#L9

VDDC#L11

VDDC#L13

VDDC#M5

VDDC#M10

VDDC#M12

VDDC#M25

VDDC#N9

VDDC#N11

VDDC#N24

VDDC#N25

VDDC#P15

VDDC#P18

VDDC#P20

VDDC#P24

VDDC#P25

VDDC#AA10

VDDC#AA12

VDDC#AA24

VDDC#AA25

VDDC#AB11

VDDC#AB13

VDDC#AC5

VDDC#AC10

VDDC#AC12

VDDC#AC24

VDDC#AC25

VDDC#AD9

VDDC#AD11

VDDC#AD12

VDDC#AD14

VDDC#AD18

VDDC#AD21

VDDC#AD25

VDDC#AE12

VDDC#AE14

VDDC#AE18

VDDC#AE21

VDDC#AE23

VDDC#V25

VDDC#V24

VDDC#Y19

VDDC#Y16

VDDC#Y14

VDDC#W20

VDDC#W18

VDDC#W15

VDDC#W5

VDDC#V19

VDDC#V16

VDDC#V14

VDDC#T20

VDDC#T18

VDDC#T15

VDDC#T10

VDDC#R19

VDDC#R16

VDDC#R14

VDDC#R5

+VCC_CORE

AA10

AA12

AA24

AA25

AB11

AB13

AC5

AC10

AC12

AC24

AC25

AD9

AD11

AD12

AD14

AD18

AD21

AD25

AE12

AE14

AE18

AE21

AE23

V25

V24

Y19

Y16

Y14

W20

W18

W15

W5

V19

V16

V14

T20

T18

T15

T10

R19

R16

R14

R5

LAYOUT NOTE: Bottom side decoupling.

+VCC_CORE

C30

C26

C26

C27

10uF/6.3V,X5R

10uF/6.3V,X5R

C38

C38

180pF/25V,X7R

180pF/25V,X7R

C59

C59

0.22uF/10V,Y5V

0.22uF/10V,Y5V

C27

C28

C28

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

+

+

C585

C585

220uF/2.5V,POSCAP

220uF/2.5V,POSCAP

CT7343_19

CT7343_19

ns

ns

C61

C61

C60

C60

0.22uF/10V,Y5V

0.22uF/10V,Y5V

0.22uF/10V,Y5V

0.22uF/10V,Y5V

C23

C23

C22

C22

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

+VCC_CORE

C36

C36

C35

C35

0.22uF/10V,Y5V

0.22uF/10V,Y5V

0.22uF/10V,Y5V

0.22uF/10V,Y5V

A A

+V1.8

C55

C55

C56

C56

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

C25

C25

C24

C24

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

C37

C37

0.01uF/25V,X7R

0.01uF/25V,X7R

C58

C58

C57

C57

4.7uF/10V,X5R

4.7uF/10V,X5R

4.7uF/10V,X5R

4.7uF/10V,X5R

5

C30

C29

C29

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

C123

C123

0.01uF/25V,X7R

0.01uF/25V,X7R

C63

C63

C62

C62

180pF/25V,X7R

180pF/25V,X7R

0.01uF/25V,X7R

0.01uF/25V,X7R

+V1.8

Y29

U29

R28

P29

W32

W30

W28

U30

N30

U32

R32

R30

N32

U26

Y26

M27

AG32

AG30

AF28

AE30

AE26

AC32

AC30

AE32

AB28

AA30

C64

C64

180pF/25V,X7R

180pF/25V,X7R

4

+VCC_CORE

VDDIO#Y29

VDDIO#U29

VDDIO#R28

VDDIO#P29

VDDIO#W32

VDDIO#W30

VDDIO#W28

VDDIO#U30

VDDIO#N30

VDDIO#U32

VDDIO#R32

VDDIO#R30

VDDIO#N32

VDDIO#U26

VDDIO#Y26

VDDIO#M27

VDDIO#AG32

VDDIO#AG30

VDDIO#AF28

VDDIO#AE30

VDDIO#AE26

VDDIO#AC32

VDDIO#AC30

VDDIO#AE32

VDDIO#AB28

VDDIO#AA30

C65

C65

180pF/25V,X7R

180pF/25V,X7R

4

3

+V1.8 6,7,9,28,32,33

+V0.9 6,9,26,32

+VCC_CORE 26,34

U1G

U1G

A32

U1FU1F

LAYOUT NOTE: Decoupling between CPU and DIMM.

Place close to CPU as possible.

C124

C124

180pF/25V,X7R

180pF/25V,X7R

+V0.9

C39

C39

4.7uF/10V,X5R

4.7uF/10V,X5R

C47

C47

4.7uF/10V,X5R

4.7uF/10V,X5R

AA1

AA2

AA4

AA9

AA11

AA22

AA23

AB10

AB12

AB21

AB22

AB23

AB24

AB25

AC11

AC1

AC2

AC4

AC8

AC9

AC13

AC21

AC22

AC23

AD10

AD13

AD16

AD20

AD22

AD23

AD24

AE1

AE2

AE4

AE7

AE10

AE11

AE13

AE16

AE20

AE22

AE24

AE25

AF7

AF8

AF9

AF26

AG1

AG2

AG4

AG6

AG7

AG27

AH5

AH14

AH20

AH23

AH25

AH28

+V1.8

C364

C364

180pF/25V,X7R

180pF/25V,X7R

C40

C40

4.7uF/10V,X5R

4.7uF/10V,X5R

C49

C49

C48

C48

0.22uF/10V,Y5V

0.22uF/10V,Y5V

4.7uF/10V,X5R

4.7uF/10V,X5R

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

AM2-BGA-27-27-812-01

AM2-BGA-27-27-812-01

C32

C32

C31

C31

4.7uF/10V,X5R

4.7uF/10V,X5R

4.7uF/10V,X5R

4.7uF/10V,X5R

C42

C42

C41

C41

0.22uF/10V,Y5V

0.22uF/10V,Y5V

0.22uF/10V,Y5V

0.22uF/10V,Y5V

C50

C50

0.22uF/10V,Y5V

0.22uF/10V,Y5V

3

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

VSS82

VSS81

VSS80

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

VSS73

VSS72

VSS71

VSS70

VSS69

VSS68

VSS67

VSS66

VSS65

VSS64

VSS63

VSS62

VSS61

C34

C34

C33

C33

0.22uF/10V,Y5V

0.22uF/10V,Y5V

0.22uF/10V,Y5V

0.22uF/10V,Y5V

C43

C43

1000pF/50V,X7R

1000pF/50V,X7R

C51

C51

C52

C52

1000pF/50V,X7R

1000pF/50V,X7R

1000pF/50V,X7R

1000pF/50V,X7R

G4

G2

G1

F23

F20

F14

E32

E30

D30

D29

D27

D25

D23

D21

D19

D17

D15

D13

D11

D8

C31

B33

B29

B27

B21

B19

B17

B15

B13

C10

AN32

AN2

AM33

AM27

AM23

AM19

AM17

AM15

AM13

AM11

AM1

AL31

AK29

AK27

AK25

AK23

AK21

AK19

AK17

AK15

AK13

AK11

AK7

AK5

AJ22

AJ19

AJ15

AJ4

AJ2

AJ1

C44

C44

1000pF/50V,X7R

1000pF/50V,X7R

C53

C53

180pF/25V,X7R

180pF/25V,X7R

CT1

CT1

220uF/10V,TAN

220uF/10V,TAN

ns

ns

C45

C45

C46

C46

180pF/25V,X7R

180pF/25V,X7R

180pF/25V,X7R

180pF/25V,X7R

C54

C54

180pF/25V,X7R

180pF/25V,X7R

U1H

U1H

G19

VSS121

G25

VSS123

G27

VSS124

G30

VSS125

H5

VSS126

H6

VSS127

H20

VSS128

H23

VSS129

H28

VSS130

J1

VSS131

J2

VSS132

J4

VSS133

J7

VSS134

J11

VSS135

J13

VSS136

J16

VSS137

J22

VSS138

J24

VSS139

J25

VSS140

J28

VSS141

J30

VSS142

J32

VSS143

K11

VSS144

K13

VSS145

K16

VSS146

A2

VSS147

K22

VSS148

K24

VSS149

K9

VSS150

L1

VSS151

L2

VSS152

L4

VSS153

L8

VSS154

L10

VSS155

L12

VSS156

L21

VSS157

L22

VSS158

L23

VSS159

L24

VSS160

L25

VSS161

L26

VSS162

L30

VSS163

M6

VSS164

M9

VSS165

M11

VSS166

M13

VSS167

M21

VSS168

M22

VSS169

M23

VSS170

M24

VSS171

N1

VSS172

N2

VSS173

N4

VSS174

N10

VSS175

N12

VSS176

N22

VSS177

N23

VSS178

P7

VSS179

P10

VSS180

P14

VSS181

P16

VSS182

P19

VSS183

AM2-BGA-27-27-812-01

AM2-BGA-27-27-812-01

2

R1

VSS184

R2

VSS185

R4

VSS186

R8

VSS187

R15

VSS188

R18

VSS189

R20

VSS190

T9

VSS191

T14

VSS192

T16

VSS193

T19

VSS194

T24

VSS195

T25

VSS196

V15

VSS197

V18

VSS198

V20

VSS199

U1

VSS200

U2

VSS201

U4

VSS202

U7

VSS203

U8

VSS204

W1

VSS205

W2

VSS206

W4

VSS207

W8

VSS208

W14

VSS209

W16

VSS210

W19

VSS211

Y7

VSS212

Y10

VSS213

Y15

VSS214

Y18

VSS215

Y20

VSS216

Y24

VSS217

Y25

VSS218

F17

VSS219

AB7

VSS220

AG5

VSS221

B23

VSS222

B1

VSS223

H1

H1

BOSS

BOSS

MH24_32X40X65T80B

MH24_32X40X65T80B

ns

ns

1

1

H3

H3

BOSS

BOSS

MH28X40X75

MH28X40X75

ns

ns

1

1

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

1

H2

H2

BOSS

BOSS

MH28X40X75

MH28X40X75

ns

ns

1

1

H4

H4

BOSS

BOSS

MH28X40X75

MH28X40X75

ns

ns

1

1

zw

zw

zw

T11 D

T11 D

T11 D

of

843Wednesday, August 19, 2009

of

843Wednesday, August 19, 2009

of

1

843Wednesday, August 19, 2009

5

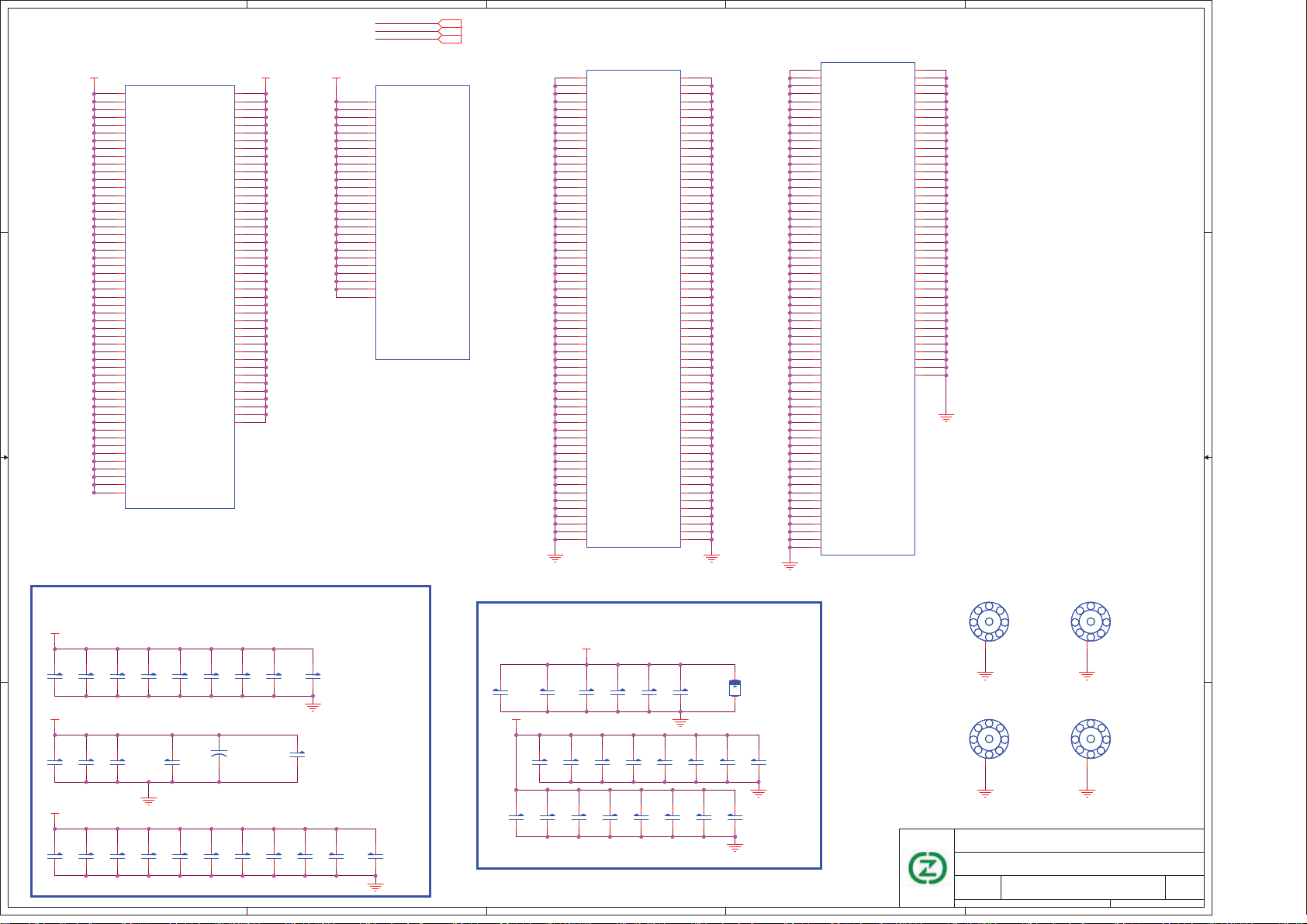

+V1.8

MEM_MA_ADD[15..0]6

D D

MEM_MA_BANK[2..0]6

MEM_MA_DM[7..0]6

C C

B B

+V3.3S

A A

MEM_MA_ADD[15..0]

MEM_MA_BANK[2..0]

MEM_MA_DM[7..0]

MEM_MA_DQS0_P6

MEM_MA_DQS1_P6

MEM_MA_DQS2_P6

MEM_MA_DQS3_P6

MEM_MA_DQS4_P6

MEM_MA_DQS5_P6

MEM_MA_DQS6_P6

MEM_MA_DQS7_P6

MEM_MA_DQS0_N6

MEM_MA_DQS1_N6

MEM_MA_DQS2_N6

MEM_MA_DQS3_N6

MEM_MA_DQS4_N6

MEM_MA_DQS5_N6

MEM_MA_DQS6_N6

MEM_MA_DQS7_N6

MEM_MA0_CLK1_P6

MEM_MA0_CLK1_N6

MEM_MA0_CLK2_P6

MEM_MA0_CLK2_N6

MEM_MA_CKE06

MEM_MA_CKE16

MEM_MA_RAS#6

MEM_MA_CAS#6

MEM_MA_WE#6

MEM_MA0_CS_L06

MEM_MA0_CS_L16

MEM_MA0_ODT06

MEM_MA1_ODT06

SDATA013,15

C93

C93

0.1uF/16V,X7R

0.1uF/16V,X7R

5

SCLK013,15

M_VREF_DDR

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

SDATA

SCLK

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10

90

A11

89

A12

116

A13

86

A14

84

A15

107

BA0

106

BA1

85

BA2

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS0

29

DQS1

49

DQS2

68

DQS3

129

DQS4

146

DQS5

167

DQS6

186

DQS7

30

CK0

32

CK0

164

CK1

166

CK1

79

CKE0

80

CKE1

108

RAS

113

CAS

109

WE

110

S0

115

S1

114

ODT0

119

ODT1

198

SA0

200

SA1

195

SDA

197

SCL

199

VDDspd

1

VREF

2

VSS0

3

VSS1

8

VSS2

9

VSS3

12

VSS4

15

VSS5

18

VSS6

21

VSS7

24

VSS8

27

VSS9

28

VSS10

33

VSS11

34

VSS12

39

VSS13

40

VSS14

41

VSS15

42

VSS16

47

VSS17

48

VSS18

53

VSS19

54

VSS20

59

DDR2 SO-DIMM SOCKET 1.8V, Vertical

DDR2 SO-DIMM SOCKET 1.8V, Vertical

DDR2S200H52_STD

DDR2S200H52_STD

103

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

4

111

104

112

117

118

J1

J1

5

DQ0

7

DQ1

VDD8

VDD7

VDD9

VDD10

SO-DIMM

SO-DIMM

VSS31

VSS30

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

127

122

121

VDD11

NC/TEST

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

132

128

4

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

GND0

GND1

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

50

69

83

120

163

201

202

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DATA[63..0]

3

MEM_MA_DATA[63..0] 6

MEM_MA_ADD[15..0]6

MEM_MA_BANK[2..0]6

+V1.8

R36

R36

49.9,1%

49.9,1%

C82

C82

R37

R37

49.9,1%

49.9,1%

0.1uF/16V,X7R

0.1uF/16V,X7R

3

MEM_MA_ADD[15..0]

MEM_MA_BANK[2..0]

MEM_MA_CAS#6

MEM_MA_WE#6

MEM_MA_RAS#6

MEM_MA_CKE16

MEM_MA_CKE06

MEM_MA0_CS_L16

MEM_MA0_CS_L06

MEM_MA0_ODT06

MEM_MA1_ODT06

C80

C80

0.1uF/16V,X7R

0.1uF/16V,X7R

M_VREF_DDR

C83

C83

0.01uF/25V,X7R

0.01uF/25V,X7R

C81

C81

0.1uF/16V,X7R

0.1uF/16V,X7R

R531 0 nsR531 0 ns

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_BANK2

MEM_MA_ADD5

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD10

MEM_MA_ADD0

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_ADD13

2

+V3.3S 7,11,12,13,15,16,17,18,19,20,21,24,25,26,27,28,31,33,34

+V1.8 6,7,8,28,32,33

+V0.9 6,8,26,32

+V0.9 +V0.9

RN1 47 x4RN1 47 x4

1 2

3 4

5 6

7 8

RN2 47 x4RN2 47 x4

1 2

3 4

5 6

7 8

RN3 47 x4RN3 47 x4

1 2

3 4

5 6

7 8

RN4 47 x4RN4 47 x4

1 2

3 4

5 6

7 8

RN5 47 x4RN5 47 x4

1 2

3 4

5 6

7 8

RN6 47 x4RN6 47 x4

1 2

3 4

5 6

7 8

R34 47,1%R34 47,1%

R35 47,1%R35 47,1%

RN7 47 x4RN7 47 x4

1 2

3 4

5 6

7 8

M_VREF 6,32

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CAS#

MEM_MA_WE#

MEM_MA_RAS#

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

2

Date: Sheet

1

C66 0.1uF/16V,X7RC66 0.1uF/16V,X7R

C67 0.1uF/16V,X7RC67 0.1uF/16V,X7R

C68 0.1uF/16V,X7RC68 0.1uF/16V,X7R

C69 0.1uF/16V,X7RC69 0.1uF/16V,X7R

C70 0.1uF/16V,X7RC70 0.1uF/16V,X7R

C71 0.1uF/16V,X7RC71 0.1uF/16V,X7R

C72 0.1uF/16V,X7RC72 0.1uF/16V,X7R

C73 0.1uF/16V,X7RC73 0.1uF/16V,X7R

C74 0.1uF/16V,X7RC74 0.1uF/16V,X7R

C75 0.1uF/16V,X7RC75 0.1uF/16V,X7R

C76 0.1uF/16V,X7RC76 0.1uF/16V,X7R

C77 0.1uF/16V,X7RC77 0.1uF/16V,X7R

C78 0.1uF/16V,X7RC78 0.1uF/16V,X7R

C79 0.1uF/16V,X7RC79 0.1uF/16V,X7R

C84 22pF/50V,NPOC84 22pF/50V,NPO

C85 22pF/50V,NPOC85 22pF/50V,NPO

C86 22pF/50V,NPOC86 22pF/50V,NPO

C87 22pF/50V,NPOC87 22pF/50V,NPO

C88 22pF/50V,NPOC88 22pF/50V,NPO

C89 22pF/50V,NPOC89 22pF/50V,NPO

C90 22pF/50V,NPOC90 22pF/50V,NPO

C91 22pF/50V,NPOC91 22pF/50V,NPO

C92 22pF/50V,NPOC92 22pF/50V,NPO

C94 22pF/50V,NPOC94 22pF/50V,NPO

C95 22pF/50V,NPOC95 22pF/50V,NPO

C96 22pF/50V,NPOC96 22pF/50V,NPO

C97 22pF/50V,NPOC97 22pF/50V,NPO

C98 22pF/50V,NPOC98 22pF/50V,NPO

C99 22pF/50V,NPOC99 22pF/50V,NPO

C100 22pF/50V,NPOC100 22pF/50V,NPO

CZC Technology

CZC Technology

CZC Technology

+V1.8

+V1.8

+V1.8

+V1.8

+V1.8

+V1.8

+V1.8

C101 22pF/50V,NPOC101 22pF/50V,NPO

C102 22pF/50V,NPOC102 22pF/50V,NPO

C103 22pF/50V,NPOC103 22pF/50V,NPO

C104 22pF/50V,NPOC104 22pF/50V,NPO

C105 22pF/50V,NPOC105 22pF/50V,NPO

C106 22pF/50V,NPOC106 22pF/50V,NPO

T11 D

T11 D

T11 D

1

+V1.8

zw

zw

zw

of

of

of

943Wednesday, August 19, 2009

943Wednesday, August 19, 2009

943Wednesday, August 19, 2009

5

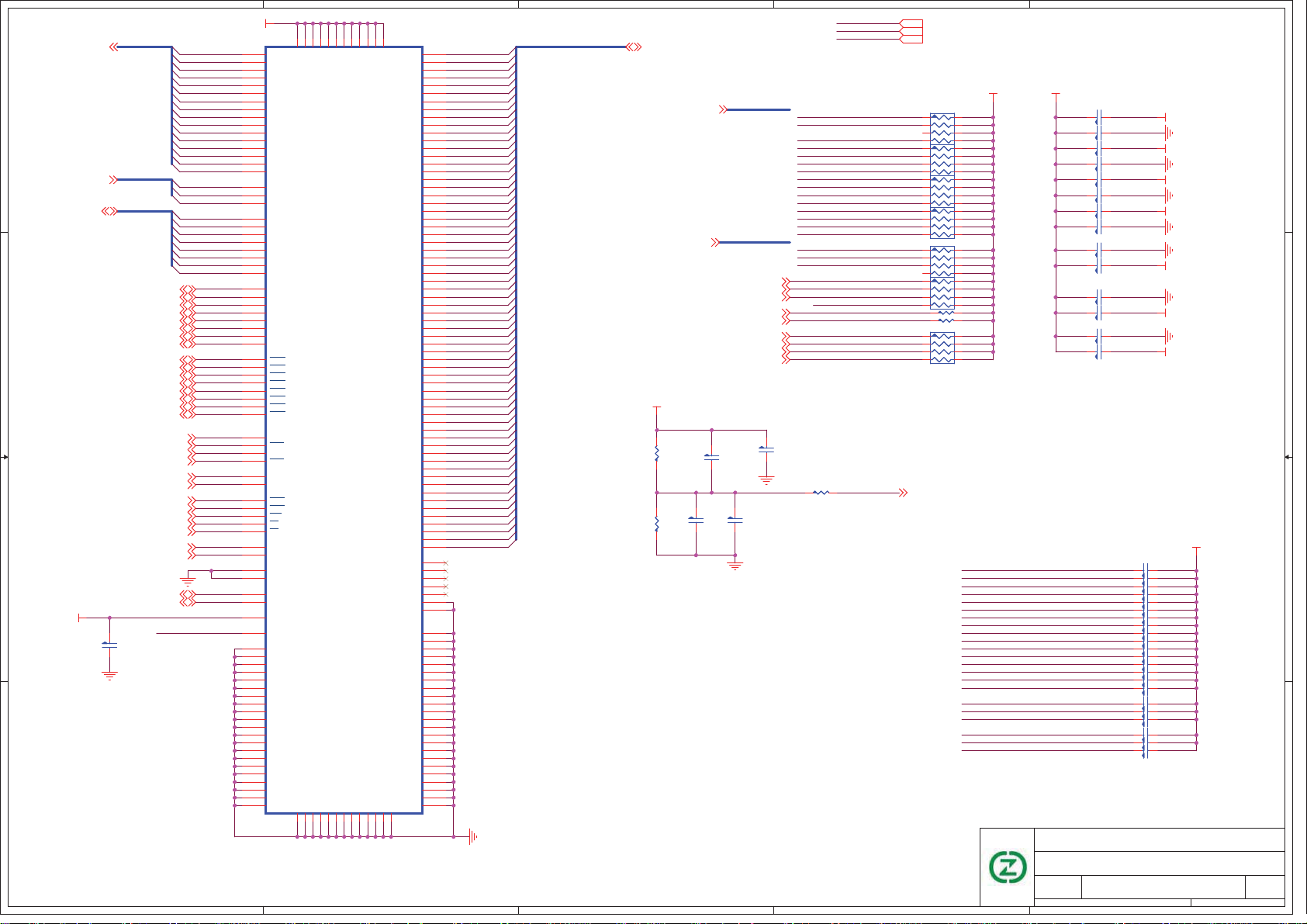

HT_CADOUT15_P5

HT_CADOUT15_N5

HT_CADOUT14_P5

HT_CADOUT14_N5

HT_CADOUT13_P5

HT_CADOUT13_N5

HT_CADOUT12_P5

D D

C C

HT_CADOUT12_N5

HT_CADOUT11_P5

HT_CADOUT11_N5

HT_CADOUT10_P5

HT_CADOUT10_N5

HT_CADOUT9_P5

HT_CADOUT9_N5

HT_CADOUT8_P5

HT_CADOUT8_N5

HT_CADOUT7_P5

HT_CADOUT7_N5

HT_CADOUT6_P5

HT_CADOUT6_N5

HT_CADOUT5_P5

HT_CADOUT5_N5

HT_CADOUT4_P5

HT_CADOUT4_N5

HT_CADOUT3_P5

HT_CADOUT3_N5

HT_CADOUT2_P5

HT_CADOUT2_N5

HT_CADOUT1_P5

HT_CADOUT1_N5

HT_CADOUT0_P5

HT_CADOUT0_N5

HT_CLKOUT1_P5

HT_CLKOUT1_N5

HT_CLKOUT0_P5

HT_CLKOUT0_N5

HT_CTLOUT0_P5

HT_CTLOUT0_N5

VDDAHT_PKG69012

49.9,1%R38 49.9,1%R38

HT_RXCALP

49.9,1%R40 49.9,1%R40

HT_RXCALN

W19

W20

AC21

AB22

AB20

AA20

AA19

AA25

AA24

AB23

AA23

AB24

AB25

AC24

AC25

W21

W22

W25

R19

R18

R21

R22

U22

U21

U18

U19

Y19

R25

U25

U24

V23

U23

V24

V25

Y24

P24

P25

A24

C24

T24

4

U4A

U4A

HT_RXCAD15P

HT_RXCAD15N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD0P

HT_RXCAD0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCTLP

HT_RXCTLN

HT_RXCALP

HT_RXCALN

RS690T(E)

RS690T(E)

PART 1 OF 6

PART 1 OF 6

HT CPU I/F

HT CPU I/F

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

P21

P22

P18

P19

M22

M21

M18

M19

L18

L19

G22

G21

J20

J21

F21

F22

N24

N25

L25

M24

K25

K24

J23

K23

G25

H24

F25

F24

E23

F23

E24

E25

L21

L22

J24

J25

N23

P23

C25

D24

HT_TXCALP

HT_TXCALN

3

HT_CADIN15_P 5

HT_CADIN15_N 5

HT_CADIN14_P 5

HT_CADIN14_N 5

HT_CADIN13_P 5

HT_CADIN13_N 5

HT_CADIN12_P 5

HT_CADIN12_N 5

HT_CADIN11_P 5

HT_CADIN11_N 5

HT_CADIN10_P 5

HT_CADIN10_N 5

HT_CADIN9_P 5

HT_CADIN9_N 5

HT_CADIN8_P 5

HT_CADIN8_N 5

HT_CADIN7_P 5

HT_CADIN7_N 5

HT_CADIN6_P 5

HT_CADIN6_N 5

HT_CADIN5_P 5

HT_CADIN5_N 5

HT_CADIN4_P 5

HT_CADIN4_N 5

HT_CADIN3_P 5

HT_CADIN3_N 5

HT_CADIN2_P 5

HT_CADIN2_N 5

HT_CADIN1_P 5

HT_CADIN1_N 5

HT_CADIN0_P 5

HT_CADIN0_N 5

HT_CLKIN1_P 5

HT_CLKIN1_N 5

HT_CLKIN0_P 5

HT_CLKIN0_N 5

HT_CTLIN0_P 5

HT_CTLIN0_N 5

R39

R39

100

100

2

LAYOUT NOTE: To simplify routing, PCIe

lanes may be freely swapped between:

- Ethernet

- 2 PCIe x1 slots

1

U4B

U4B

G5

GFX_RX0P

G4

GFX_RX0N

J8

GFX_RX1P

J7

GFX_RX1N

J4

GFX_RX2P

J5

GFX_RX2N

L8

GFX_RX3P

L7

GFX_RX3N

L4

GFX_RX4P

L5

GFX_RX4N

M8

B B

A_RX2_P14

A_RX2_N14

A_RX3_P14

A_RX3_N14

PCIE_RXP2_EXPRESS21

PCIE_RXN2_EXPRESS21

PCIE_RXP3_LAN24

PCIE_RXN3_LAN24

PCIE_RXP0_SLOT20

PCIE_RXN0_SLOT20

A_RX0_P14

A_RX0_N14

A_RX1_P14

A A

5

A_RX1_N14

GFX_RX5P

M7

GFX_RX5N

M4

GFX_RX6P

M5

GFX_RX6N

P8

GFX_RX7P

P7

GFX_RX7N

Y4

SB_RX2P(GPP_RX0P)

Y5

SB_RX2N(GPP_RX0N)

W4

SB_RX3P(GPP_RX1P)

W5

SB_RX3N(GPP_RX1N)

P4

GPP_RX2P

P5

GPP_RX2N

R4

GPP_RX3P

R5

GPP_RX3N

R7

GPP_RX0P(NC)

R8

GPP_RX0N(NC)

U4

GPP_RX1P(NC)

U5

GPP_RX1N(NC)

AB7

SB_RX0P

AB6

SB_RX0N

V9

SB_RX1P

W9

SB_RX1N

AC4

NC(PCE_ISET)

AD4

NC(PCE_TXISET)

RS690T(E)

RS690T(E)

4

PART 2 OF 6

PART 2 OF 6

SB_TX2P(GPP_TX0P)

SB_TX2N(GPP_TX0N)

SB_TX3P(GPP_TX1P)

PCIE I/F GFX

PCIE I/F GFX

SB_TX3N(GPP_TX1N)

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

PCE_CALRP(PCE_PCAL)

PCE_CALRN(PCE_NCAL)

GPP_TX0P(NC)

GPP_TX0N(NC)

GPP_TX1P(NC)

GPP_TX1N(NC)

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

J1

TXOUT_L2C_N

H2

TXOUT_L1C_P

K2

TXOUT_L1C_N

K1

TXOUT_L0C_P

K3

TXOUT_L0C_N

L3

TXOUT_CLKC_P

L1

TXOUT_CLKC_N

L2

N2

N1

P2

P1

P3

R3

R1

R2

AA1

AA2

Y2

Y3

U2

U1

V2

V1

V3

W3

W1

W2

AC1

AC2

AB1

AB2

AE4

AE3

A_C_TX2P

A_C_TX2N

A_C_TX3P

A_C_TX3N

A_C_TX0P

A_C_TX0N

A_C_TX1P

A_C_TX1N

TXOUT_L2C_P

C107 0.1uF/16V,X7R HDMIC107 0.1uF/16V,X7R HDMI

C108 0.1uF/16V,X7R HDMIC108 0.1uF/16V,X7R HDMI

C109 0.1uF/16V,X7R HDMIC109 0.1uF/16V,X7R HDMI

C110 0.1uF/16V,X7R HDMIC110 0.1uF/16V,X7R HDMI

C111 0.1uF/16V,X7R HDMIC111 0.1uF/16V,X7R HDMI

C112 0.1uF/16V,X7R HDMIC112 0.1uF/16V,X7R HDMI

C113 0.1uF/16V,X7R HDMIC113 0.1uF/16V,X7R HDMI

C114 0.1uF/16V,X7R HDMIC114 0.1uF/16V,X7R HDMI

C115 0.1uF/16V,X7RC115 0.1uF/16V,X7R

C116 0.1uF/16V,X7RC116 0.1uF/16V,X7R

C117 0.1uF/16V,X7RC117 0.1uF/16V,X7R

C118 0.1uF/16V,X7RC118 0.1uF/16V,X7R

C119 0.1uF/16V,X7RC119 0.1uF/16V,X7R

C120 0.1uF/16V,X7RC120 0.1uF/16V,X7R

C121 0.1uF/16V,X7RC121 0.1uF/16V,X7R

C122 0.1uF/16V,X7RC122 0.1uF/16V,X7R

C125 0.1uF/16V,X7RC125 0.1uF/16V,X7R

C126 0.1uF/16V,X7RC126 0.1uF/16V,X7R

C127 0.1uF/16V,X7RC127 0.1uF/16V,X7R

C128 0.1uF/16V,X7RC128 0.1uF/16V,X7R

C129 0.1uF/16V,X7RC129 0.1uF/16V,X7R

C130 0.1uF/16V,X7RC130 0.1uF/16V,X7R

562,1%R41 562,1%R41

2K,1%R42 2K,1%R42

3

TXOUT_L2_P 19

TXOUT_L2_N 19

TXOUT_L1_P 19

TXOUT_L1_N 19

TXOUT_L0_P 19

TXOUT_L0_N 19

TMDS_CLK_P 19

TMDS_CLK_N 19

A_TX2_P 14

A_TX2_N 14

A_TX3_P 14

A_TX3_N 14

PCIE_TXP2_EXPRESS 21

PCIE_TXN2_EXPRESS 21

PCIE_TXP3_LAN 24

PCIE_TXN3_LAN 24

PCIE_TXP0_SLOT 20

PCIE_TXN0_SLOT 20

A_TX0_P 14

A_TX0_N 14

A_TX1_P 14

A_TX1_N 14

VDDA12_PKG690 12

?GFX_TX3P, GFX_TX3N (Clock+, Clock-)

?GFX_TX2P, GFX_TX2N (Blue Data0+, Data0-)

?GFX_TX1P, GFX_TX1N (Green Data1+, Data1-)

?GFX_TX0P, GFX_TX0N (Red Data2+, Data2-)

2

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

T11 D

T11 D

T11 D

1

zw

zw

zw

of

of

of

10 43Wednesday, August 19, 2009

10 43Wednesday, August 19, 2009

10 43Wednesday, August 19, 2009

5

+V3.3S

FB3 300ohm/100MHz,0.6AFB3 300ohm/100MHz,0.6A

+V1.8S

PLLVDD

HTPVDD

C138

C138

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

2

R123

R123

R57

R57

4.7K

4.7K

4.7K

4.7K

AVDDQ

PLLVDD1P2

+V1.8S

R49

R49

10K

10K

1

R124

R124

4.7K

4.7K

DAC_SDAT

DAC_SCL

I2C_CLK

DDC_DATA

STRP_DATA

R18

G18

B18

Q3

BSS138Q3BSS138

3

I2C_DATA

RESISTORS

CLOSE TO NB

R43

R43

150

150

+V1.2S

FB10 100ohm/100MHz,2AFB10 100ohm/100MHz,2A

+V3.3S

R50

R50

4.7K

4.7K

NB_LDTSTOP#

R44

R44

150

150

+V1.8S

R45

R45

150

150

C139

C139

4.7uF/10V,X5R

4.7uF/10V,X5R

HTREFCLK13

SUS_STAT#15,18

NB_OSC13

NBSRC_CLK_P13

NBSRC_CLK_N13

SBLINK_CLK_P13

SBLINK_CLK_N13

I2C_CLK18,19

I2C_DATA18

+V3.3S

FB4 300ohm/100MHz,0.6AFB4 300ohm/100MHz,0.6A

C132

C132

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

D D

FB5 300ohm/100MHz,0.6AFB5 300ohm/100MHz,0.6A

C135

C135

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

FB6 300ohm/100MHz,0.6AFB6 300ohm/100MHz,0.6A

C134

C134

1uF/10V,X5R

1uF/10V,X5R

+V1.2S

FB8 300ohm/100MHz,0.6AFB8 300ohm/100MHz,0.6A

C C

CPU_LDTSTOP#7,14

+V3.3S

R55

R55

R54

B B

R54

10K

10K

4.7K

4.7K

R56

R56

4.7K

4.7K

DFT_GPIO1 DFT_GPIO[4:2] DFT_GPIO5DFT_GPIO0

Pin straps are used to configure

PCIE GPP mode:

PULL HIGH

(internally

pulled high)

PULL

A A

LOW

Use hardware

default values

DEFAULT DEFAULT

I2C master loads

strap values from

EEPROM if

connected

5

Memory side port

not available

Memory side port

available

DEFAULT

111: Register defined

(register default to Config E)

DEFAULT

Others not used in this design Use the memory data bus

DAC_SCL18

DAC_SDAT18

VDDPLL_690

C140

C140

1uF/10V,X5R

1uF/10V,X5R

TMDS_HPD19

DDC_DATA19

R59

R59

4.7K

4.7K

4

ALLOW_LDTSTOP14

I2C_DATA

4

VCC3P3V_ANA690

C131

C131

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

C133

C133

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

AVDDQ

VSYNC#18

HSYNC#18

33R47 33R47

33R48 33R48

PLLVDD

HTPVDD

NB_RST#14

VLDT_PWRGD15,18,26

4.7KR52 4.7KR52

0R53 0R53

PLLVDD1P2

TP35TP35

TMDS_HPD

DDC_DATA

TESTMODE

Enable debug bus via the

memory IO pads

Use default values

to output the debug bus

DAC_SCLR

DAC_SDAR

NB_LDTSTOP#

10KR51 10KR51

OSCIN

Thermal_P

Thermal_N

STRP_DATA

3

+V1.8S 12,14,17,26,33

+V3.3S 7,9,12,13,15,16,17,18,19,20,21,24,25,26,27,28,31,33,34

+V1.2S 5,7,12,14,16,17,26,31,33

U4C

U4C

TXCLK_LP

TXCLK_LN

LPVDD

LPVSS

LVSSR1

LVSSR3

LVSSR5

LVSSR6

LVSSR7

LVSSR8

LVSSR12

LVSSR13

+V3.3S

EC_SMB2_CLK27,29

EC_SMB2_DAT27,29

G781_PULLHIGH

B14

B15

B13

A13

H14

G14

D17

E17

A15

B16

C17

C18

B17

A17

A18

B18

LCDCLK1+

E15

LCDCLK1-

D15

TXCLK_UP

H15

TXCLK_UN

G15

D14

E14

LVDDR1P8D

A12

B12

LVDDR3P3A

C12

C13

A16

A14

D12

C19

C15

C16

F14

F15

E12

G12

F12

DFT_GPIO0

D6

LOAD_ROM#

D7

DFT_GPIO2

C8

DFT_GPIO3

C7

DFT_GPIO4

B8

DFT_GPIO5

A8

R185 ns

R185 ns

100

100

0.1uF/16V,X7R

0.1uF/16V,X7R

TSSOP8_P65_3P0

TSSOP8_P65_3P0

TP22TP22

TP23TP23

C141

C141

C142

C142

0.1uF/16V,X7R

0.1uF/16V,X7R

10uF/6.3V,X5R

10uF/6.3V,X5R

12

C314

C314

ns

ns

8

SMBCLK

7

SMBDATA

6

ALERT#

4

THERM#

ns

ns

B22

AVDD1

C22

AVDD2

G17

AVSSN1

H17

AVSSN2

A20

AVDDDI

B20

AVSSDI

A21

AVDDQ

A22

AVSSQ

C21

C_R

C20

Y_G

D19

COMP_B

E19

RED

F19

GREEN

G19

BLUE

C6

DACVSYNC

A5

715,1%R46 715,1%R46

33R58 33R58

DACHSYNC

B21

RSET

B6

DACSCL

A6

DACSDA

A10

PLLVDD18(PLLVDD)

B10

PLLVSS

B24

HTPVDD

B25

HTPVSS

E7

VDDPLL_1(VDDA12)

F7

VDDPLL_2(VDDA12)

F9

VSSPLL_1(VSSA12)

G9

VSSPLL_2(VSSA12)

C10

SYSRESET#

C11

POWERGOOD

C5

LDTSTOP#

B5

ALLOW_LDTSTOP

C23

HTTSTCLK

B23

HTREFCLK

C2

TVCLKIN

B11

OSCIN

A11

PLLVDD12(OSCOUT)

F2

GFX_CLKP

E1

GFX_CLKN

G1

SB_CLKP

G2

SB_CLKN

B2

BMREQb

A2

I2C_CLK

B4

I2C_DATA

AD5

THERMALDIODE_P

AE5

THERMALDIODE_N

C14

TMDS_HPD

B3

DDC_DATA

C3

TESTMODE

A3

STRP_DATA

RS690T(E)

RS690T(E)

PM_THRM_DN#7,30

PART 3 OF 6

PART 3 OF 6

CRT/TVOUT

CRT/TVOUT

LVDDR33_1(LVDDR18A_1)

LVDDR33_2(LVDDR18A_2)

PLL PWR

PLL PWR

PM

PM

CLOCKs

CLOCKs

MIS.

MIS.

R182

R182

4.7K

4.7K

ns

ns

3

R183

R183

4.7K

4.7K

ns

ns

TXOUT_L0P

TXOUT_L0N

TXOUT_L1P

TXOUT_L1N

TXOUT_L2P

TXOUT_L2N

TXOUT_L3P

TXOUT_L3N

TXOUT_U0P

TXOUT_U0N

TXOUT_U1P

TXOUT_U1N

TXOUT_U2P

TXOUT_U2N

TXOUT_U3P

TXOUT_U3N

TXCLK_UP

TXCLK_UN

LVDDR18D_1

LVDDR18D_2

LVDS_DIGON

LVDS_BLON

LVDS_BLEN

DFT_GPIO0

DFT_GPIO1

DFT_GPIO2

DFT_GPIO3

DFT_GPIO4

DFT_GPIO5

LCD0+ 18

LCD0- 18

LCD1+ 18

LCD1- 18

LCD2+ 18

LCD2- 18

LCD3+

LCD3-

LCDCLK1+ 18

LCDCLK1- 18

LVDS_DIGON 18

LVDS_BLON 18

LVDS_BLEN 18

R4773KR477

R476

R476

3K

3K

3K

ns

ns

1

DXP

VCC

DXN

G781

G781

ADM1032AR

ADM1032AR

LM86CIM

LM86CIM

MAX6657MSA

MAX6657MSA

SOIC-8

SOIC-8

GND

5

W83L771 TSSOP8

W83L771 TSSOP8

2

C136

C136

0.1uF/16V,X7R

0.1uF/16V,X7R

C143

C143

0.1uF/16V,X7R

0.1uF/16V,X7R

Ϣ

LOAD_ROM#

U25

U25

2

3

2

+V1.8S

FB7 300ohm/100MHz,0.6AFB7 300ohm/100MHz,0.6A

C137

C137

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

FB9 300ohm/100MHz,0.6AFB9 300ohm/100MHz,0.6A

FB11 300ohm/100MHz,0.6AFB11 300ohm/100MHz,0.6A

C144

C144

2.2uF/6.3V,X7R

2.2uF/6.3V,X7R

DESIGN NOTE:The following debug

points should be provided.

LDT_PWRGD

ⳌϢDŽ

DFT_GPIO0I2C_CLK

DFT_GPIO2

DFT_GPIO3

DFT_GPIO4

DFT_GPIO5

12

C313

C313

2200pF/25V,X7R

2200pF/25V,X7R

ns

ns

1

+V1.8S

+V3.3S

TP36TP36

TP37TP37

TP39TP39

TP41TP41

TP42TP42

TP43TP43

Thermal_P

Thermal_N

CZC Technology

CZC Technology

CZC Technology

Title

Title

Title

<Title>

<Title>

<Title>

Size Project Name Rev

Size Project Name Rev

Size Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

ࡴϱ

M690E_H

M690E_H

Cu Boss for MiniPCIE 2*3mm

Cu Boss for MiniPCIE 2*3mm

T11 D

T11 D

T11 D

1

zw

zw

zw

of

of

of

11 43Wednesday, August 19, 2009

11 43Wednesday, August 19, 2009

11 43Wednesday, August 19, 2009

5

G3

AD1

AE1

G6

M3

VSSA2P9VSSA5F3VSSA7A1VSSA8H1VSSA9

VSSA6

VSSA4

VSSA3

VSSA1

D D

PAR 5 OF 6

PAR 5 OF 6

VSS1

VSS2

VSS3

VSS4E9VSS5

VSS6

VSS7

F11

A25

Y23

P11

D23

R24

G11

+V1.2S

100ohm@100MHz,3A

C C

+V1.2S

B B

+V1.2S

A A

+V1.8S

100ohm@100MHz,3A

FB14 100ohm/100MHz,2AFB14 100ohm/100MHz,2A

+V1.8S

FB15 300ohm/100MHz,0.6AFB15 300ohm/100MHz,0.6A

+V3.3S

FB17 100ohm/100MHz,2AFB17 100ohm/100MHz,2A

FB18 100ohm/100MHz,2AFB18 100ohm/100MHz,2A

FB19 100ohm/100MHz,2AFB19 100ohm/100MHz,2A

Y7

AA3

VSSA10J2VSSA11H3VSSA13J6VSSA15F1VSSA16L6VSSA17M2VSSA18M6VSSA19J3VSSA20P6VSSA21T1VSSA22N3VSSA24R6VSSA25T2VSSA26T3VSSA27U3VSSA28U6VSSA30Y1VSSA29

VSSA14

VSSA12

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

J22

J12

L12

L14

L20

L23

G23

M15

AC18

FB68

FB68

FB0805

FB0805

C147

C147

10uF/6.3V,X5R

10uF/6.3V,X5R

+V1.2S

C153

C153

0.1uF/16V,X7R

0.1uF/16V,X7R

0.1uF/16V,X7R

0.1uF/16V,X7R

C162

C162

0.1uF/16V,X7R

0.1uF/16V,X7R

0.1uF/16V,X7R

0.1uF/16V,X7R

C167

C167

C166

C166

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

C173

C173

1uF/10V,X5R

1uF/10V,X5R

C183

C183

C184

C184

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

C189

C189

C190

C190

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

5

VSS17

VSS18

VSS19

VSS20

VSS21

M11

M20

M23

M25

10uF/6.3V,X5R

10uF/6.3V,X5R

C154

C154

0.1uF/16V,X7R

0.1uF/16V,X7R

C158

C158

0.1uF/16V,X7R

0.1uF/16V,X7R

800mA

C168

C168

1uF/10V,X5R

1uF/10V,X5R

C174

C174

1uF/10V,X5R

1uF/10V,X5R

C185

C185

1uF/10V,X5R

1uF/10V,X5R

C191

C191

1uF/10V,X5R

1uF/10V,X5R

R9

VSS22

N12

N14

C148

C148

C159

C159

0.1uF/16V,X7R

0.1uF/16V,X7R

C169

C169