PRELIMINARY

Features

WAN and LAN ATM physi cal layer devic e

•

Provides complete physi cal layer t ransport of A TM cells

•

at:

—STS−3c/ STM−1 rate of 155.52 MHz

—STS−1 rate of 51.84 MHz

Compliant with ATM Forum User Netw or k Inter face 3. 1

•

specification

UTOPIA ATM inte rface

•

ATM cell processing including:

•

—HEC generation/verification

—Cell scrambli ng / d es c r ambling

—Rate adaption/idle cell filtering

—Local Flow Control

—Cell alignm ent

SONET frame processing including:

•

—Compliant with Bellcore GR−253, I.432,

T1.105, and G.709 for Jitter Tolerance and Jit ter

Generation

—Frame generation/recovery

—SO N ET scrambling/descrambling

—Frequency justification/pointer processing

Complete line interface including:

•

—C lock and data recovery

—Transmit timing derived from receiver or byte-rate

source

—SO NET com pliant PLL

—100K PECL compatible I/O

Alarm indications including:

•

—Loss Of Signal

—Out Of Frame, Loss Of Frame

CY7C955

AX™ ATM-SONET/SDH Transceiver

— Line Far E n d Recei ve Failure

—Line Alarm Indication Signal

— B1 Parity Error

—Loss Of Cell Alignment

—Loss O f Recei ve Data

Controller interface for internal int errupt and

•

configuration registers including:

—Error monitoring

—Status indication

—Device configuration

0.65µ Low Power CMOS

•

• 128-pin PQFP

Functional Description

The Cypress Semiconductor CY7C955 is a Transceiver chip

designed to carry ATM cells across SONET/SDH systems .

On the transmit side, ATM cells coming from the Utopia interface are bei ng mappe d into SONET/ SDH frames and then se rialized for transmission over fiber or twisted pair (through an

optical module or an equalizer chip).

On the receive side, serial SONET/SDH datastreams coming

from an optical module or an equalizer chip are being recovered by the intergrated clock and data recovery phase-locked

loop, framed, processed, and presented as parallel ATM cells

on the Receive Utopia Interface.

The CY7C955 can be use d in a Network Interface Card (NIC)

design to connect the segmentation and Reassembly (SAR)

chip to the optical modules or equalizer chi p.

The CY7C955 can also be used in work group or enterprise

switches to connect the I/O FIFOs of the switch fabric to the

optical module or equalizer in the interface boards.

The applications of the CY7C955 include adapters, switches,

routers, hubs , and proprietary systems.

T ABLE OF CONTENTS

Features 1

Functional Description 1

Pin Descriptions 2

Pin Configuratio n 7

Description 8

Transmit Section 8

Receive Section 10

Controller Interface (CI) 12

Loopback Oper ati on 16

SONET Overhead Description 17

CY7C955 Register Map 18

Electrical Characteristics 60

Capacitance 61

AC Test Loads and Waveforms 61

Switching Characteristics 61

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

November 29, 1999

PRELIMINARY

CY7C955

T ABLE OF CONTENTS (continued)

Switching Wavef o rm s 63

Functional Timing Diagram 69

Interfa ce Termination and Biasing Schemes 73

Filter Pin Configurat ion 75

Ordering Info rmatio n 76

Package Diagram 77

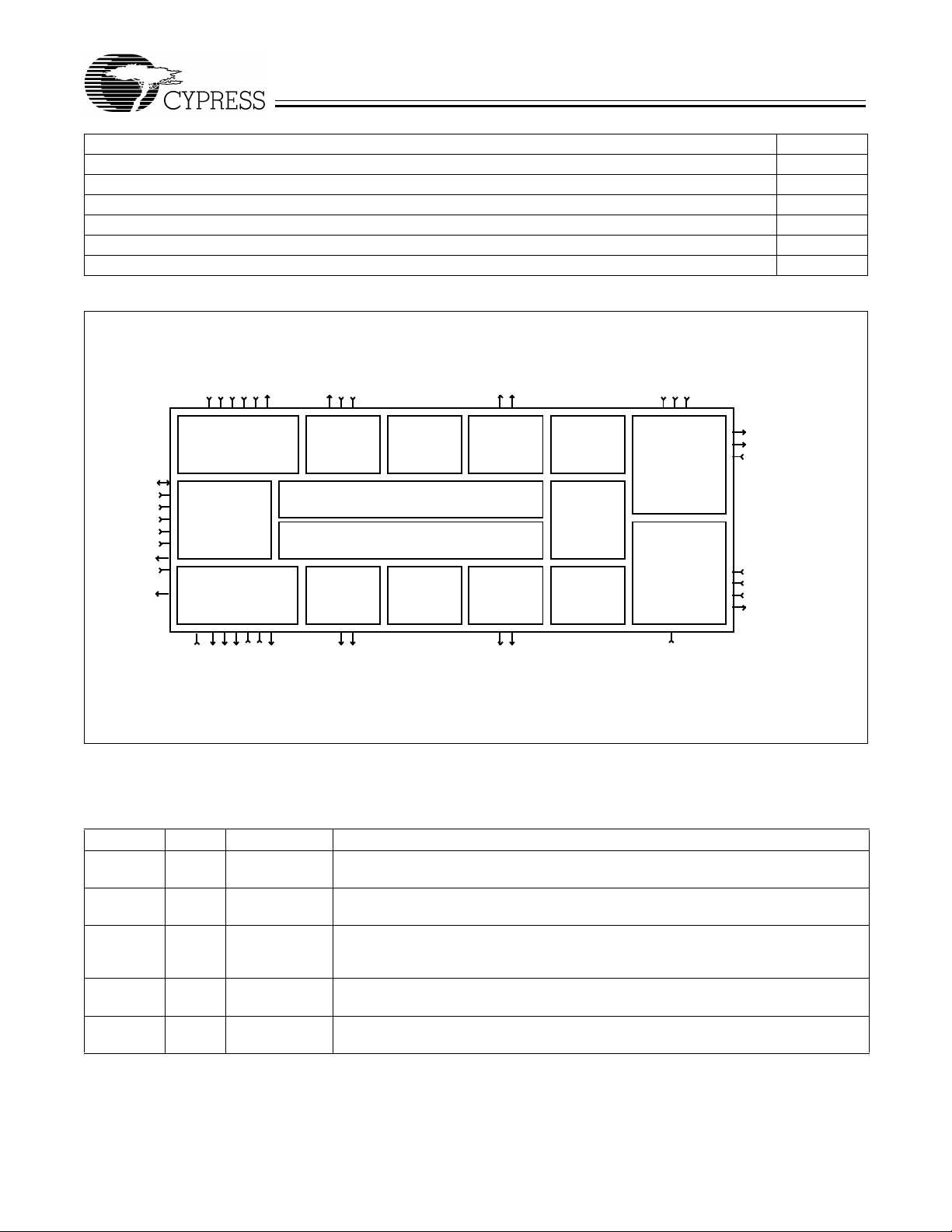

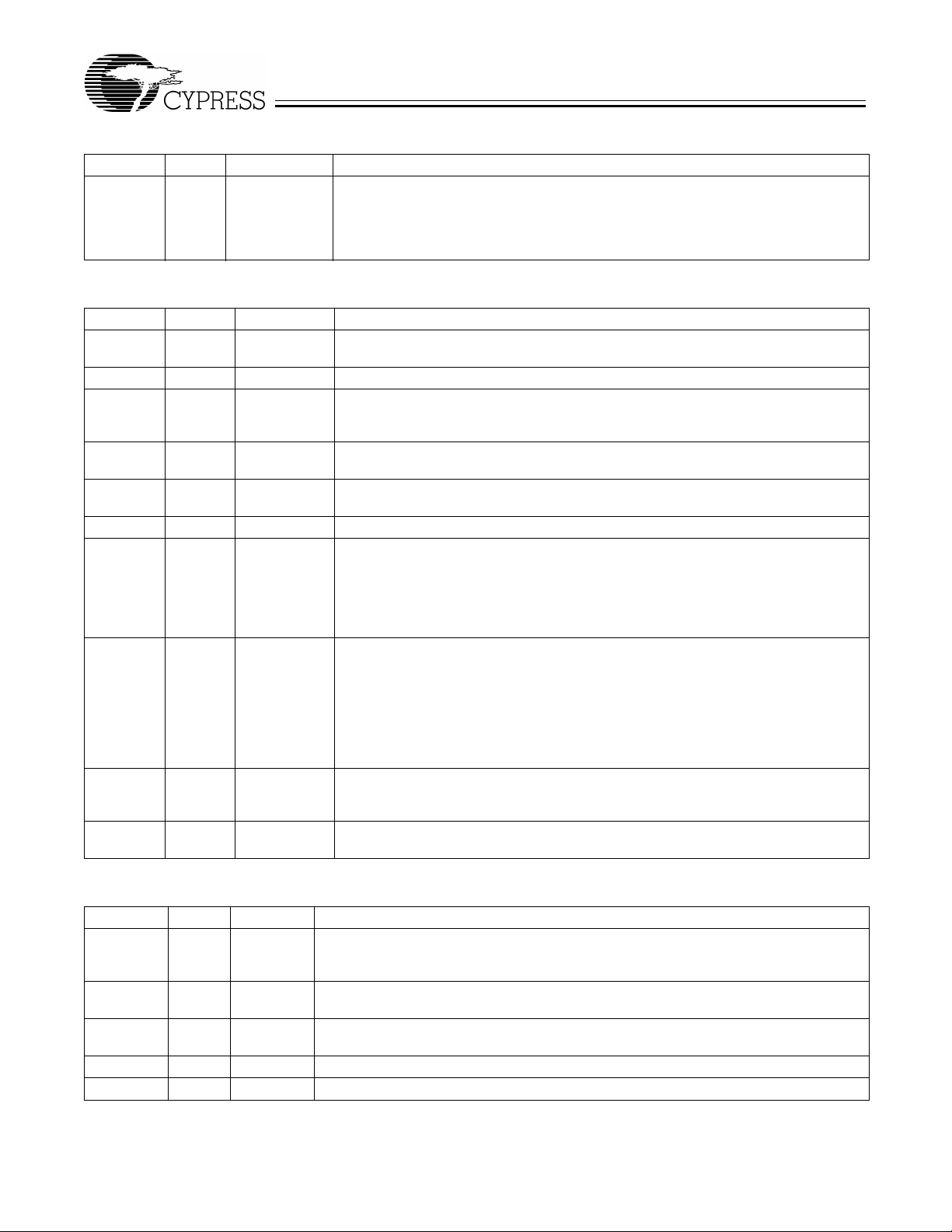

RATE1

TBYP

RATE0

Transmit

Clock

Transmit

Buffer

SONET/SDH

Clock

Recovery

RBYP

TXD±

TXC±

TRCLK±

ALOS±

RRCLK±

RXD±

RXDO±

7C955−1

D[7:0]

A[7:0]

ALE

RDB

WRB

CSB

INTB

RSTB

RALM

TDAT[7:0]

TSOC

TFCLK

TXPRTY

UTOPIA I/F

Transmit FIF O

4 Cell by 8 bit

Controller

Interface

UTOPIA I/F

Receive FIFO

4 Cell by 8 bit

TSEN

RSOC

RXPRTY

RDAT[7:0]

RFCLK

TWRENB

TCA

RRDENB

TCP

XOFF

TGFC

Transmit Transmit Transmit TransmitTransmit

ATM Cell

Processor

Configuration and Status

Register File

Error Monitoring

Receive Receive Receive ReceiveReceive

Processor

RCA

RCP

RGFC

TFPO

TCLK

Path

Overhead Overhead Overhead

PathATM Cell

Processor Processor Processor

Line Section

ProcessorProcessorProcessor

Rate

Selection

SectionLine

OverheadOverheadOverhead

RFP

RCLK

Multiplier &

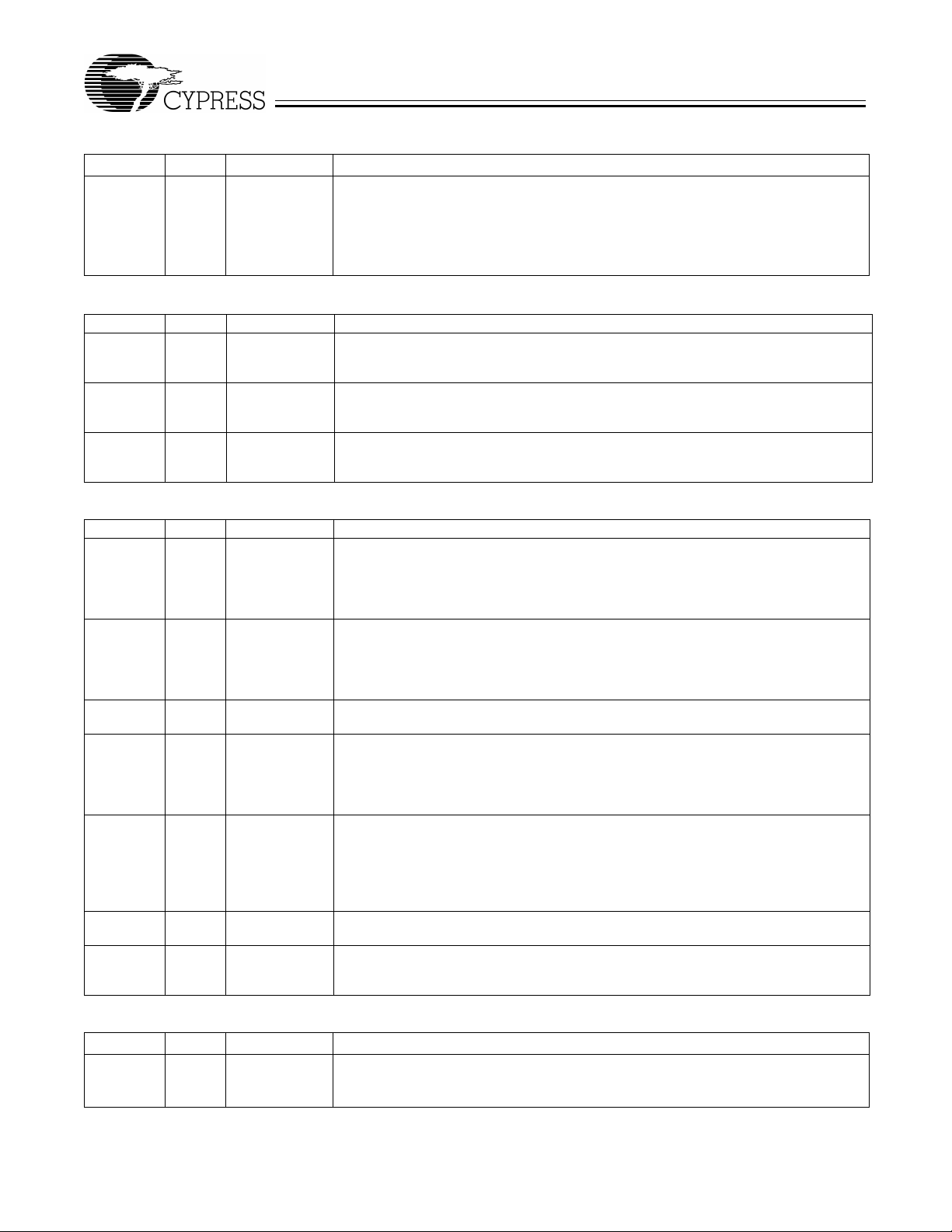

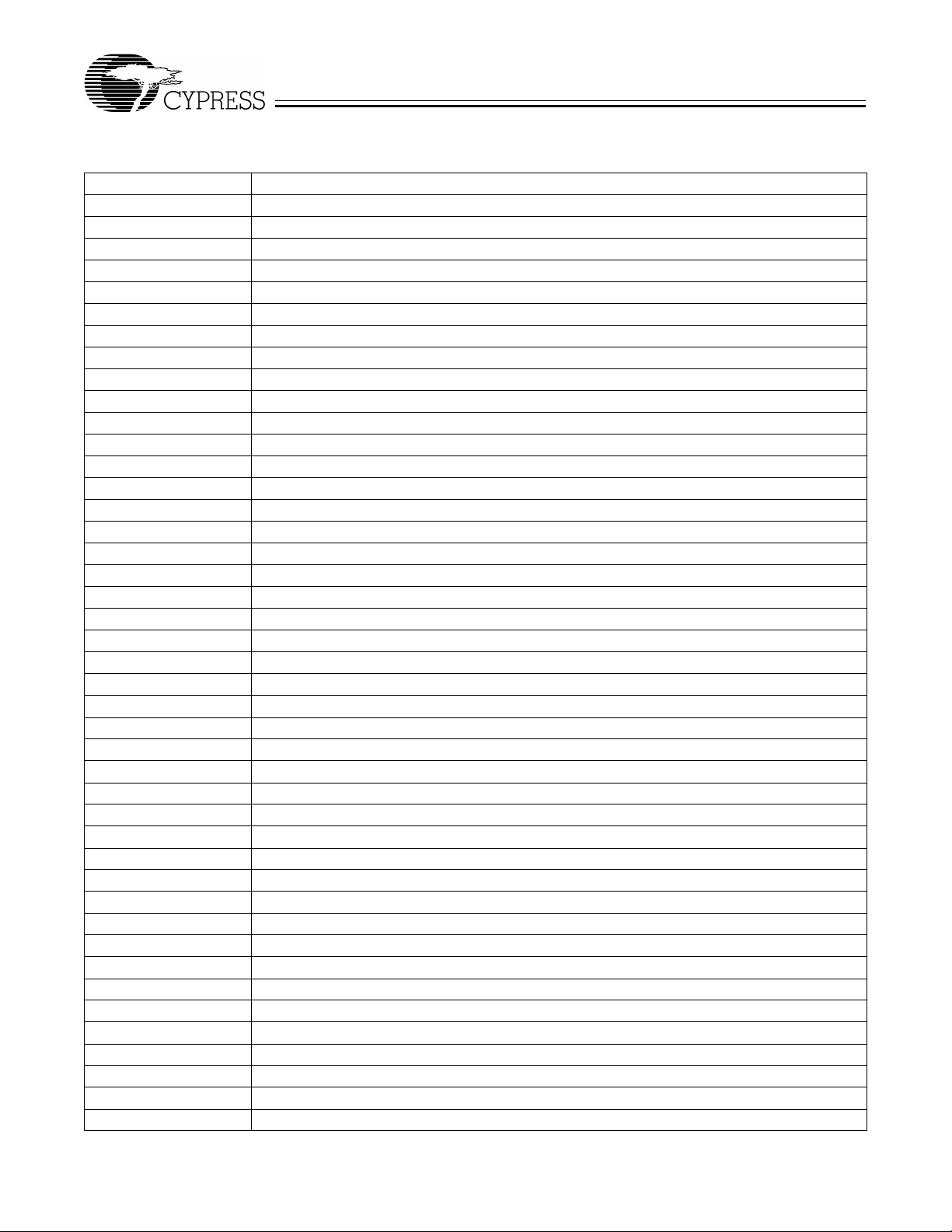

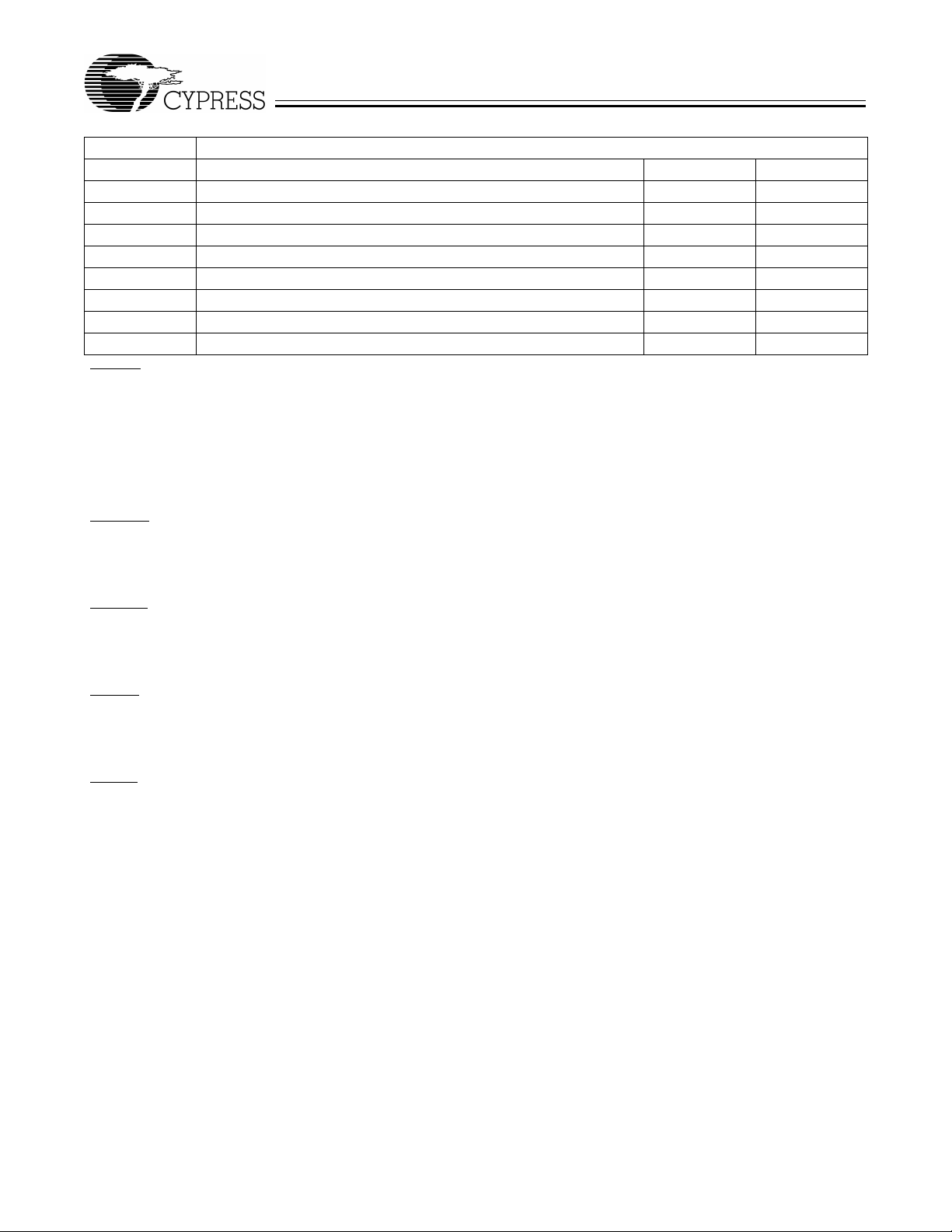

Pin Descriptions

CY7C955 ATM-SONET/SDH Transceiver

Transmit Utopia Interface

Name Pin I/O Description

TDAT[7:0] 87−94 Input T ra nsmit Utopi a data: Byte-wid e data driv en from the ATM to PHY layer. TD AT[ 7] is the

MSB.

TPRTY 95 Input Transmit Utopia Data Parity: Data parity calculated over TDAT[7:0]. Odd parity is as-

sumed unless the TXPTYP bit (Reg–63, bit 7) is set to even parity

TSOC 96 Input Transmi t Utop ia St art of Cell: Assert TSOC HIGH when TDAT[7:0] contains the first

byte of an ATM cell. If TSOC is asserted sooner than 53 writ es after the pr eviou s SOC,

an error condition will be generated. This inpu t i s opti onal after the first TSOC pulse.

TFCLK 84 Input T ransmit Utopia Clock: Data transfer clock . Data is transferred to the AX on t he rising

edge of TFCLK when TWRENB is asserted (LOW).

TWRENB 85 Input T ransmit Ut opia Data Enable: Enab les the TFCLK input f or data transf er to the AX. This

signal is active LOW.

2

PRELIMINARY

Transmit Utopia Interface (continued)

Name Pin I/O Description

TCA 86 Output T ra nsmit Utopia Cell Av ailab le: An a ctive state on this si gnal in dicates t hat the T r ansmit

FIFO can acce pt at least N more cel ls ( 53 oc tets) of dat a where N and the act iv e st ate

of the signal (HIGH or LOW) are programmable through the config uration registers

(Reg−63H an d Reg−01H) . I n a s peci al case , i f Reg –63H bit2−3 is set to 00, Reg −01H,

bit 3 is set to 0, and TCALEVEL0 (Reg–63H, bit 1) set to 0. TCA will behave as an

active HIGH FULL indic ator.

Transmit ATM Interface

Name Pin I/O Description

XOFF 50 Input Transmi t Idle Cell: A HIGH state on this pin will force the ATM Cell Processor to send

TGFC 52 Input T r ansmi t Generic Flow Control : Thi s bit serial i nput pr ov ides t he abil ity to overwrite the

TCP 51 Ou tput Tr ansmit Sta rt Of GFC: This indicates th at the firs t bit of the GFC f or the ne x t cell read

Transmit Clock Generator

Name Pin I/O Description

TRCLK± 9−10 Differenti al In T ransmi t Input Cloc k: Accepts ei ther a diff erenti al PECL, or a TTL or a CMO S byte rate

TXC± 13−14 Differential Out Transmit Output Clock: Provides clock output for the transmit data. TXD± is updated

TXD± 15−16 Differential Out Transmit Data Output: Accepts NRZ encoded output data. This signal is updated on

TBYP 2 Input T ra nsmi t Cloc k Byp ass: When this input is held HI GH t he trans mit f requency mul tip lier

RATE0

RATE1

TCLK 54 Output Transmit Byte Reference: Byt e rate reference clock derived from the t ransmit line bit

TFPO 53 Output Tr ansmit Frame Reference. This signal is an 8-kHz frame rate reference that goes

97−98 Input RATE: When the RATE0 input i s HIGH the Transmit frequency generator and the Re-

an IDLE cell e ven i f there are cel ls to s end in th e Tr ans mit FIFO. XOFF is an async hronous input and has an integrated pull down resistor.

four bits of the ATM cell header GFC field. These bi ts may be optionally written during

the four TCLK cl ock periods following the assertion of the TCP output.

from the Transm it FIFO is expected on the TGFC pin during the next rising edge of

TCLK.

reference connected to TRCLK− with TRCLK+ grounded for the Transmit frequency

multiplier PLL. Optiona lly, this input can accept also the bit rat e reference when TBYP

is true (held HIGH). In th is mode the Transmit frequency multipl ier is b ypassed and the

bit rate clock is used directly for transmit side clocking.

on the falling edge of this signal. In the default setting, TXC is disabled if RATE0 is

HIGH and a 51.84-MHz cloc k if RA TE0 is LO W. XORTXC (Reg−04H, bit 6) ca n be used

to inve rt the default setting such tha t TXC is a 155.52- MHz clock i f RATE0 is HIG H and

is disabled w hen RATE0 is LOW.

the falling edge of TXC±.

is disabl ed and TRCLK± input is used dir ectly f or transmit s ide clocki ng. When t his input

is held LOW the transm it fre quenc y multi pli er mult ipli es the TRCLK± input b y 8, 24, or

8/3 (depending on the TREFSEL (Reg−06H, bit 0) setting to pr ovide the internal bit

rate clock .

ceive cl ock recov ery are selecte d to operate a t the STS−3c/STM−1 r ate of 155.52 MHz.

When the RATE0 pin is LO W, the Transmit frequency gener ator and the Rec eiv e c lock

recovery ar e s electe d to op er ate at the STS−1 rate of 51.8 4 MHz. RATE1 is for fact ory

testing use only and shoul d be ti ed HIGH. Both RATE0 and RATE1 have integrated

pull-up resistors.

rate.

HIGH during the transmission of the first A1 byte of the SONET/SDH frame . TFPO is

updated by the rising edge of TCLK.

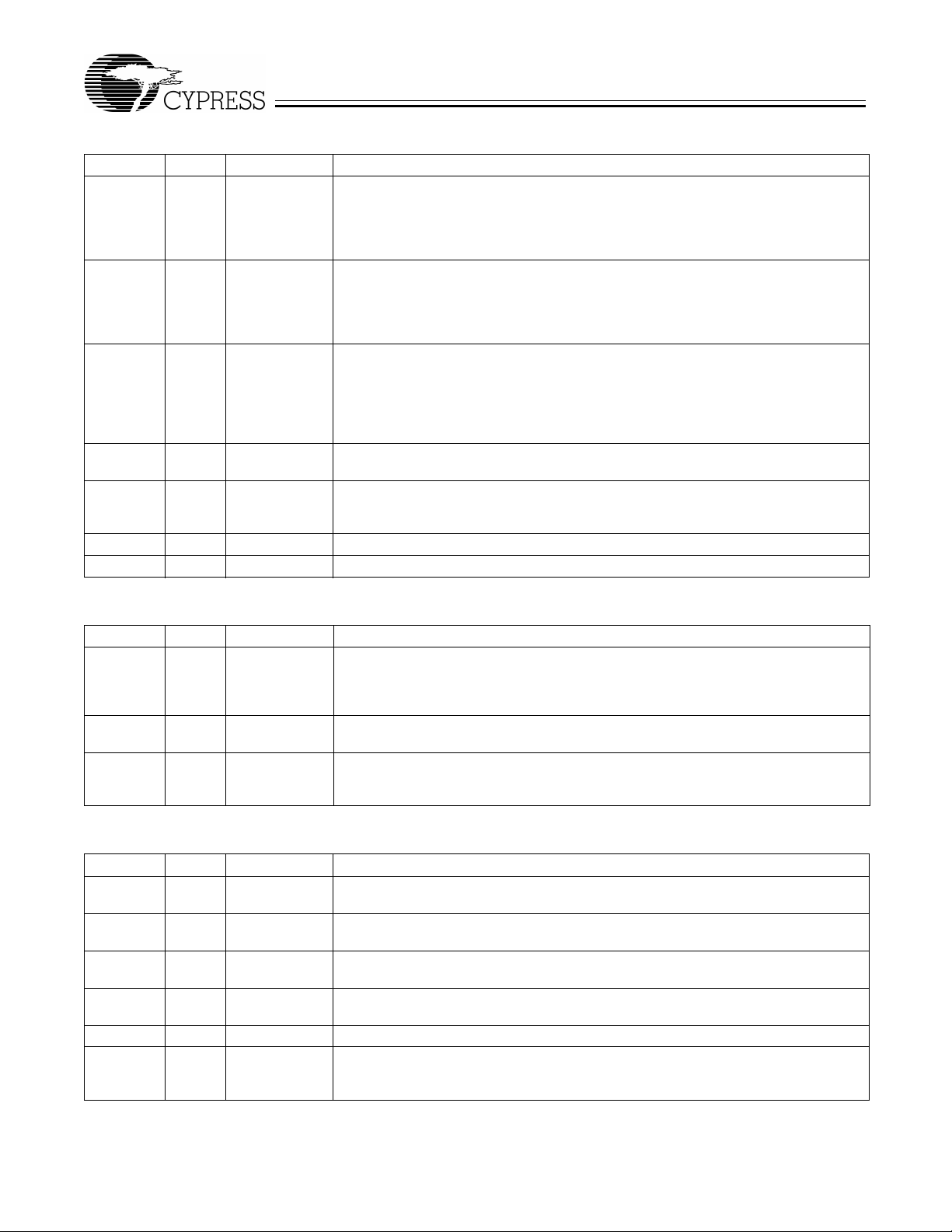

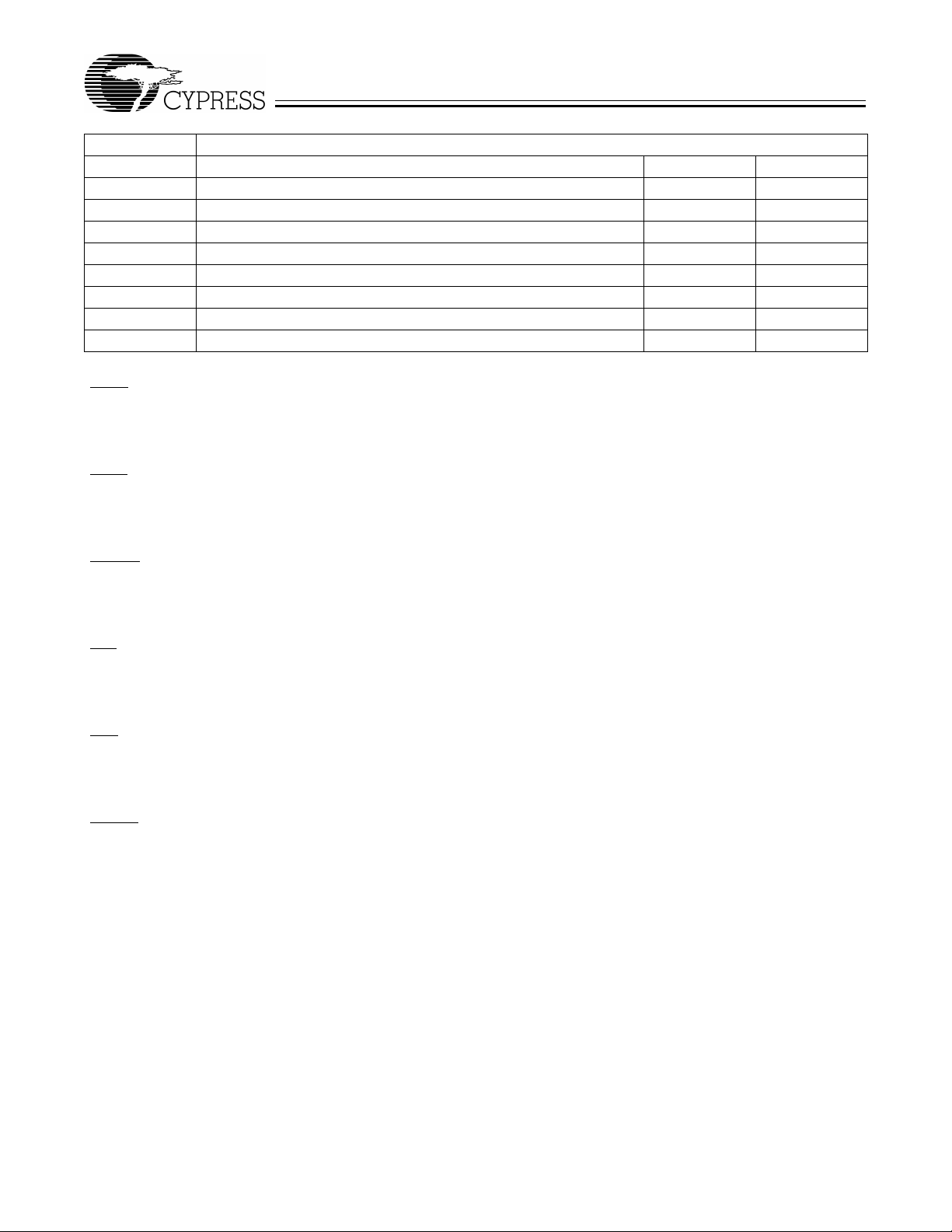

CY7C955

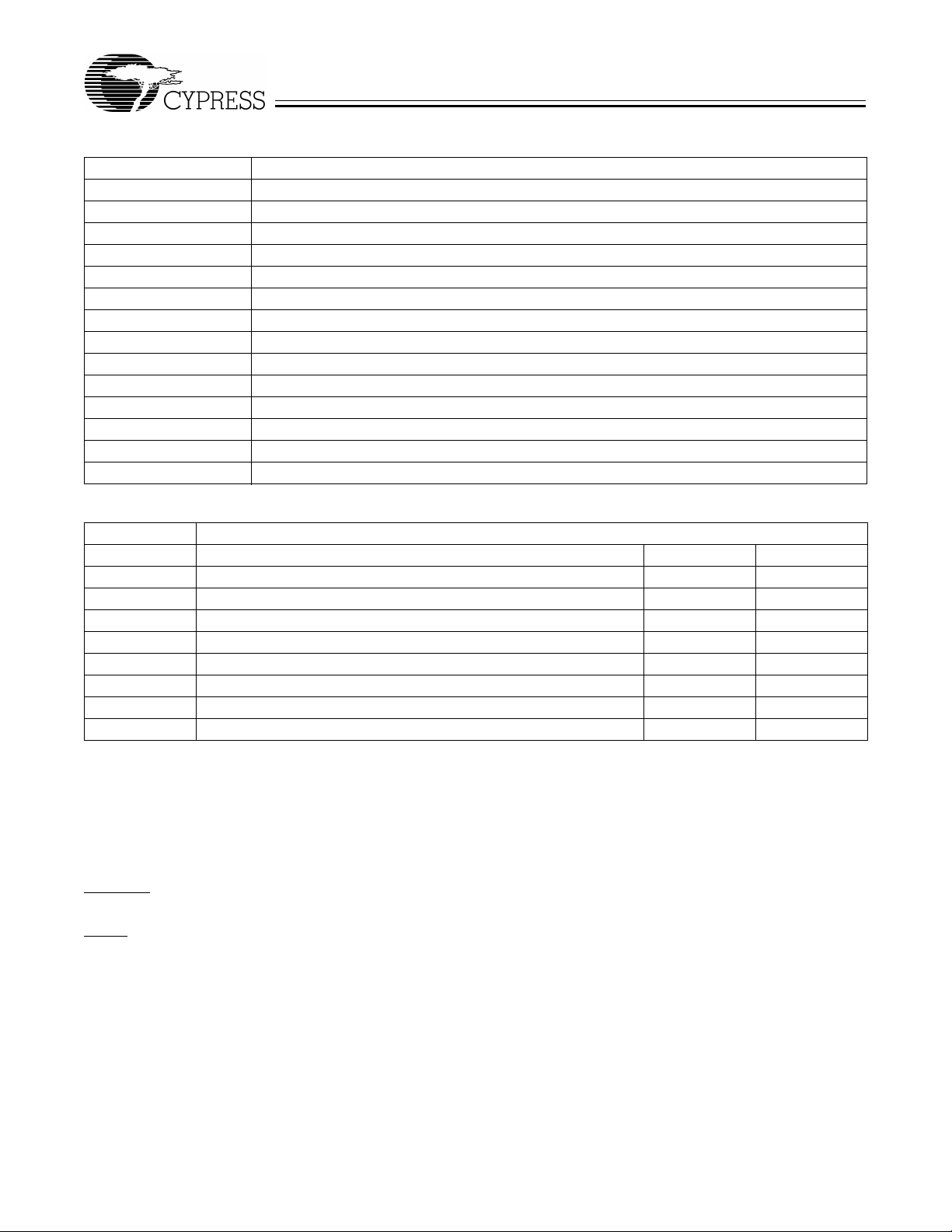

Recei ve C l o ck R e covery

Name Pin I/O Description

RXD± 25−26 Differential In Receiv e Input Data: These line receiver inputs are connected to an internal Receive

PLL that recovers the embedded cloc k and data information. The incoming data rate

can be within one of two fre quency ranges depending on the state of the RATE0 pin.

3

PRELIMINARY

Recei ve C l o ck R e covery (continued)

Name Pin I/O Description

RXDO± 22−23 Differential Out Receive Output Data: These diff erential outputs represent the retimed v ersion of the

input data stream (RXD±) in normal mode and the buffe red v ersi on of the input datas tream (RXD±) in bypass mode. This output pair can be used as inputs to decision

feedback equalizers to correct for baseline wander. RXDO can be turned off to save

power by setting RXDOD (Reg−04H, bit 7) to 1.

RRCLK± 33−34 Differential In Receive Clock : These inpu ts are used t o clock in the diff ere ntial data ( RXD±) when the

Receive clock recov e ry block is by passed (RBYP=HI GH). If RBYP is LO W , RRCLK is

multiplied b y 8, 24, or 8/ 3 d epending on the set ting of RREFSEL ( Reg−07H, bit 0) and

use as a refer ence for the Receiv er PLL. Ref er to the s ection on “Interface T ermin ation

and Bias of Schemes” for connection examples to these pins.

RBYP 41 Input Receive Clock Bypass: When this input is HIGH the Receiver clock recovery block is

bypassed. In this mode the devi ce does not recover clock and data from the Receive

input data stream (RXD±) b ut i nstea d uses t he RRCLK± in puts t o cloc k t he d iff ere ntial

data into the devic e. When th is input is LOW the Receiver cl ock reco very bloc k reco vers

the clock and data fr om the input d ata stream. I n this mode a byte-rat e clock i s expecte d

on the RRCLK± inputs.

RCLK 57 Output Receive Byte Reference: Provides a byte-rate reference derived from the recov ered

bit- rate Receiv e clock. RALM, RCP, and RGFC are aligned with this clock.

RFP 58 Output Receive Frame Reference: This output provides a frame-rate reference clock aligned

to the SONET/SDH frame alignment bytes. RFP will pulse HIGH for one RCLK cycle

eve ry 125 seconds even at OOF and LOF situations.

LF+ 42 Input NC. This pin is for factory testing only.

LF–, LFO 43, 44 Input These are the PLL filter pins. Connect a 0.47-µF capacitor across LF– and LFO.

CY7C955

Receive ATM Interface

Name Pin I/O Description

RGFC 59 Output Receive Generic Flow Control: Thi s output provides the four bits of the current ATM

cell header GFC l ocati ons at ea ch suc cessive RCLK pulse. The RCP output indi cates

the first GFC bi t l ocat ion. This out put i s f orced LO W if the ATM Cell Processor has l ost

cell delineat ion.

RALM 63 Output Receive Interrupt: Thi s active HIGH signal is aligned with the RCLK b yte-rate cloc k and

signals the presence of LAIS, PAIS, LOS, LOF, LOP, or LCD.

RCP 60 Output Receive Start Of GFC: This output indicates the first bit of the G FC presented on the

RGFC output. This output goes HIGH for 1 RCLK cycle 6 byte times after the corre-

sponding cell is written into the Receive FIFO.

Receive Utopia Interface

Name Pin No I/O Description

RDAT[7:0] 70−71

74−79

RPRTY 82 Output Receive Utopia Data Parity: Data parity calculated ov er RDAT[7:0]. Odd parity is as-

RSOC 83 Output Rece ive Utopi a Start of Cell : Asserted HIGH when RD AT[7:0] contains the fi rst byte of

RFCLK 67 Input Receive Ut opia Cloc k: Data transf er cl ock. Data is transf erred from the AX on the rising

RRDENB 68 Input Receive Utopia Enable: Enab les the RFCLK input for dat a tr ansfers from the AX.

RCA 69 Output Receive Utopi a Cell Available: An active signal indicates that the Recei ve FIFO con-

Output Receiv e Utopia Data: Byte-wid e data driv en from th e PHY to ATM layer . RD AT[7] is the

MSB

sumed unless the TXPRTY bit is set to even parity by Reg−50H, bit 6.

an ATM cell.

edge of RFCLK when RRDENB is asserted (LOW).

tains at least 1 or 4 more bytes of data. RCA is controlled by RCAINV (Reg−01H, bit

2) and RCALEVEL0 (Reg−59H, bit 2).

4

PRELIMINARY

Receive Utopia Interface (continued)

Name Pin No I/O Description

TSEN 66 Input Receive Output Enab le: This output oper ates in conjuncti on with the RRDENB output.

When TSEN is HIGH and RRDENB i s HIGH the Receive UTOPIA data b us (RDAT[7:0],

RPRTY, and RSOC) is three-stated. When TSEN is HIGH and RRDENB is LOW the

data bus is driven with the requested data. When TSEN is LOW the data bus will not

three-state.

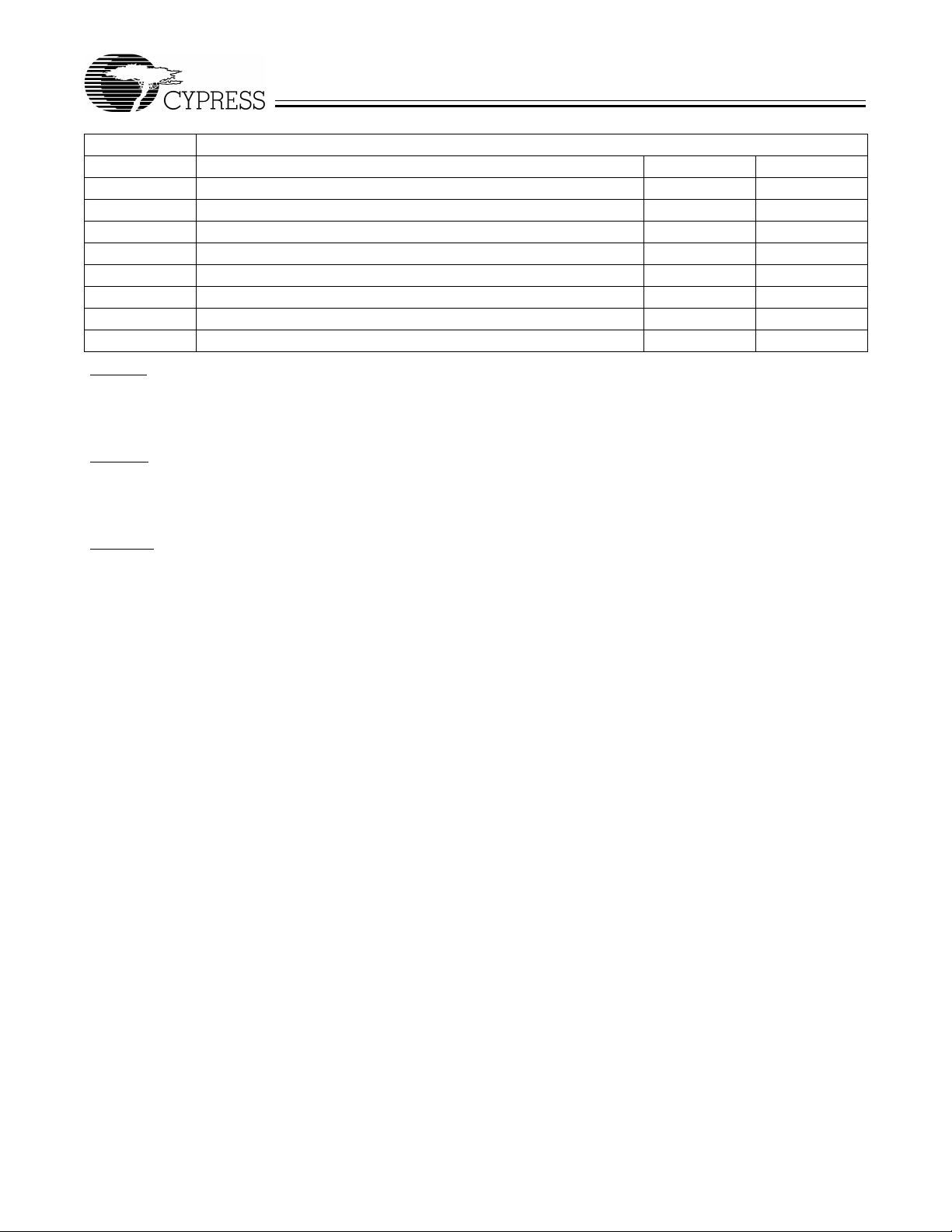

Controller Interface

Name Pin No I/O Description

D[7:0] 110−112

115−118

A[7:0] 119−126 Input Address[7:0]: Address bus used to select the internal register f or reading or writing.

ALE 127 Input Address Latch Enable: When this in put is LO W the addr ess is l atched f rom the A[7: 0]

RDB 105 Input Read: This activ e LOW signal is us ed to read the internal regi ster. The AX dri ves D[7:0]

WRB 104 Input Write: This active LOW signal is used to write the internal regi sters. Data is latche d

CSB 100 Input Select: This activ e LOW device select has to be enabled duri ng regi ster accesses.

INTB 108 Output Interrupt: This active LOW open drain output transitions LOW when an unmasked

ALOS± 27−28 D iffer e n tia l In Carrier Detect: This diff erential input co ntrols t he recov ery functio n of the Receiv e PLL

RSTB 101 Input Reset : Thi s active LOW signal provide s a device reset. This line can be pulled LOW

VCLK 99 Input Factory test pin. Must be LOW for normal operation. VCLK has an i ntegrated pul l-down

I/O Data[7:0]: Bidirectional data bus used to transfer data to and from the internal config-

uration, status, and error monitori ng registers.

inputs. When this input is HIGH, the input is transpar ent. ALE has an integr ated pullup resistor.

when RDB and CSB are both LOW.

into the specified address register on the rising edge of WRB when CSB is LOW.

interrupt source i s active. This output transiti ons HIGH when the appropriate register

has been read. This inter rupt sig nals the most crit ical error s tates of th e de vice inc luding Loss of P oint er , Line Al arm Indicat ion Signal (LAIS) , Line Far End Receive F ailur e

(LFERF), Loss of Fr ame (LOF), Out of Fram e (OOF), Loss of Signal (LOS), and many

others.

and can be driven by th e carri er detect output from opti cal modules or from external

transition detection circuitry. When this input is at a Logic Low, the input data stream

(RXD±) is recovered normally by the Recei v e Cloc k Recov ery PLL. When this input is

at a Logic Hi gh, t he Recei v e PLL n o l onger aligns t o RXD±, but in ste ad alig ns with the

RRCLK * 8 frequency and the LOS alarm register (RDOOLV) will be set. Besides

differential PECL, the ALOS− input can be set to accept single ended PECL input if

ALOS+ is tied to GND . ALOS− has to be decoupled.

to put the CY7C95 5 into the po wer -down mode . RSTB has an i nteg rated pull -up resistor.

resistor.

CY7C955

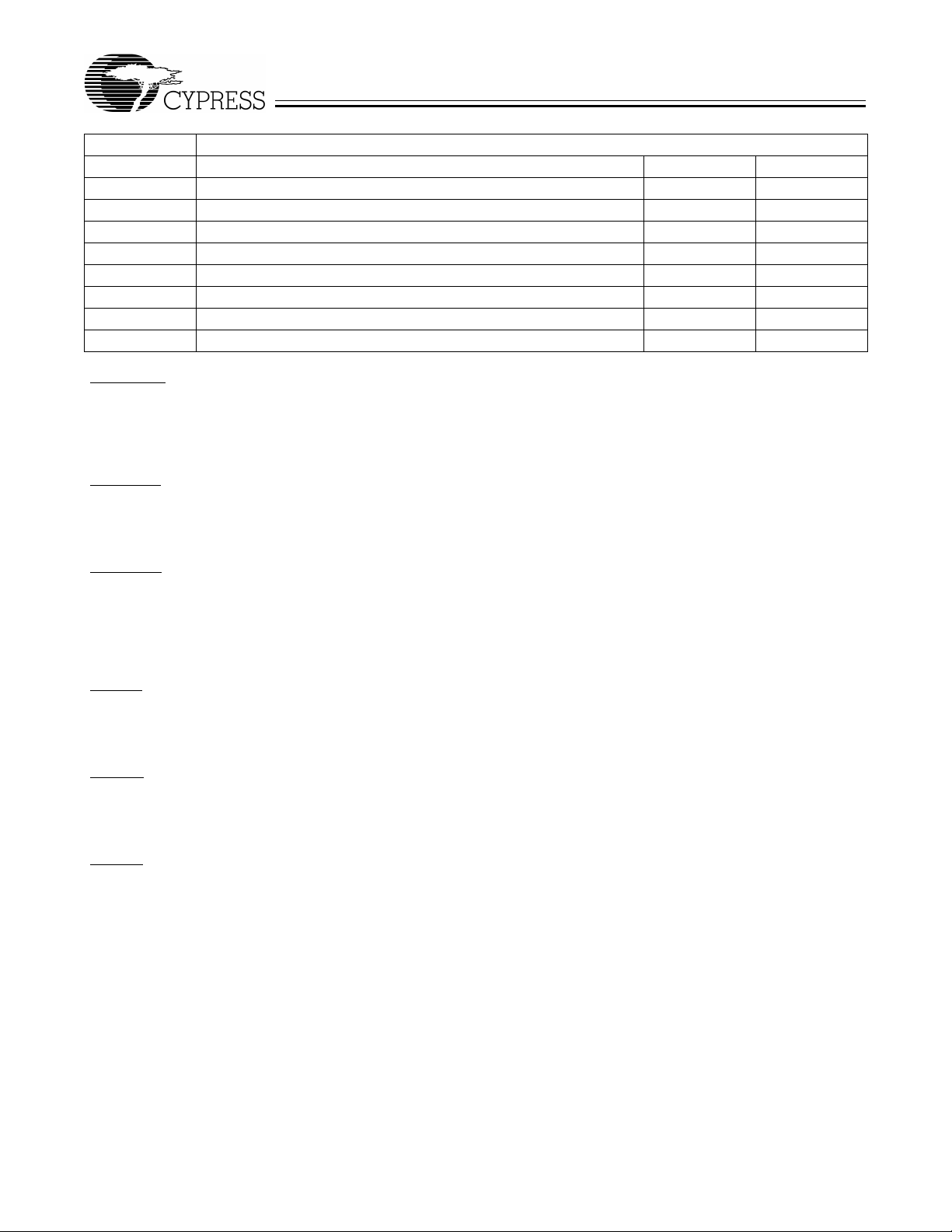

Transmit Power

Name Pin No I/O Description

TXVDD 12 Power The Transmit Pad Power supplies the TXD± outputs. TXVDD is physically isolated from

TAVD1 4 Power The power pin for the transmit clock synthesizer reference circuitry. TAVD1 should be

TAVD2 6 Power The power pin for the transmit clock synthesizer oscillator. TAVD2 should be connected

TAVD3 8 Power The power pin for the transmit PECL inputs. TAVD3 should be connect ed to anal og +5V.

TVDDO 18 Power Power for TXC± and RXDO±.

the other de vice po wer pins and should be wel l regulated +5 V DC and noise- free for good

performance when dri ving category 5 unshielded twist pair cabling.

connected to anal og +5V.

to analog +5V.

5

PRELIMINARY

CY7C955

Receive Power

Name Pin No I/O Description

RAVD1 30 Power The power pin for receiv e cloc k and data reco very block reference ci rcuitry . RA VD1 should

be connected to analog +5V.

RAVD2 36 Power The power pin f or receive clock and data recovery block active loop filter and oscillator.

RAVD2 should be connected to analog +5V.

RAVD3 24 Power The power pin for the RXD± and ALOS± PECL inputs. RAVD3 should be connected to

analog +5V.

RAVD4 32 Power The power pin for the RRCLK± PECL inputs. RAVD4 should be connected to an al og +5V.

Core Power

Name Pin No I/O Description

V

V

DDI

DDO

20, 61,

107

55, 73,

81, 114

Power The core power pins should be connected to a well decoupled +5V DC in common with

V

.

DDO

Power The pad ring power pins should be connected to a well decoupled +5V DC in common

with V

DDI

.

Ground

Name Pin No I/O Description

TAVS1 5 Ground The ground pin for the transmit clock synthes izer reference circuitry. TAVS1 should be

connected to anal og GND.

TAVS2 7 Ground The ground pin for t he transmit clock synthesizer oscillat or. TAVS2 should be connec ted

to analog GND.

TAVS3 11 Ground The ground pin for the transmit PECL input s. TAVS3 shou ld be connected t o analog GND .

TXV

SS

17 Ground The transmit pad ground is the return path for the TXC± and TXD± outputs. TXVSS is

physically isolated fro m the other device ground pins and should be noise-fr ee for good

performance when dri ving category 5 unshielded twisted pair cabling.

RAVS1 31 Ground The ground pin f or receive clock an d data recovery bl ock reference ci rcuitry. RAVS1 shoul d

be connected to analog GND.

RAVS2 37 Ground The ground pin fo r receive cloc k and data recovery bl ock active l oop filter and oscillator.

RAVS2 should be connected to analog GND.

RAVS3 29 Ground The ground pin f or the RRCLK± PECL inputs. RA VS3 shoul d be connected to analog GND .

RAVS4 35 Ground The ground pin for the RSD± and ALOS± PECL inputs. RAVS4 should be connected to

analog GND.

RVSSO 21 Ground This pin is grounded for TXC± and RXDO±.

V

SSI

19, 62,

Ground The core ground (V

) pins should be connected to GND in common with V

SSI

SSO

.

106,48

V

SSO

56, 72,

Ground The pad ring ground (V

) pins should be connected to GND in common with V

SSO

SSI

.

80, 113,

49

V

SS

1, 38,

39, 46,

Ground These pins must be connected to GND for correct operati on.

47, 64,

65, 102,

103,

128

ATP1,

ATP2,

40, 3, 46I/O These Analog Test Points (ATPx) are for factory testing use only. These pins have to be

tied to GND for correct chip operation.

ATP3

6

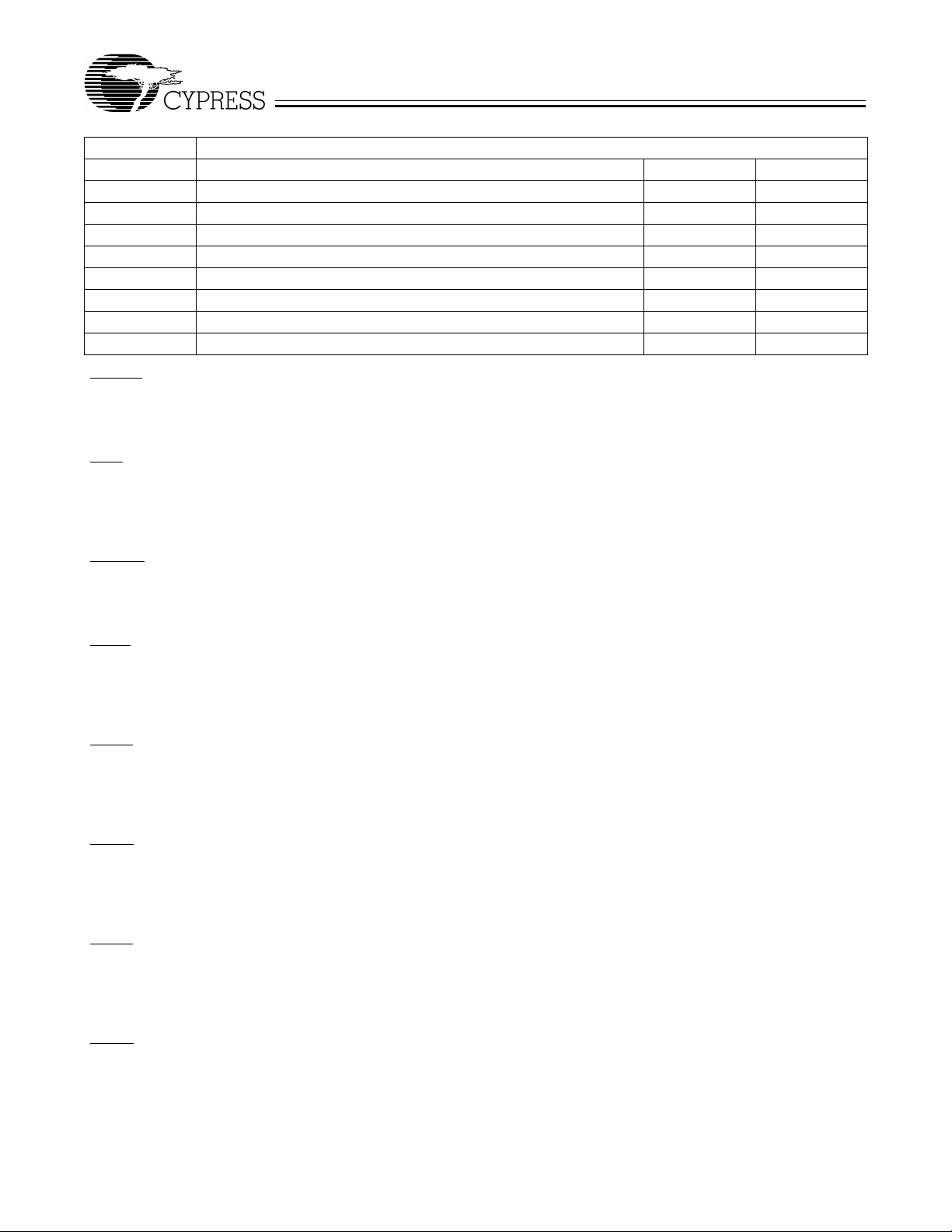

Pin Configuration

PRELIMINARY

128-pin PQFP

CY7C955

Top Vi ew

VSS

TBYP

ATP 2

TAVD1

TAVS1

TAVD2

TAVS2

TAVD3

TRCLK–

TRCLK+

TAVS3

TXV

TXC+

TXC–

TXD+

TXD–

TXV

TVDDO

VSSI

VDDI

RVSS

RXDO+

RXDO–

RAVD3

RXD–

RXD+

ALOS–

ALOS+

RAVS3

RAVD1

RAVS1

RAVD4

RRCLK–

RRCLK+

RAVS4

RAVD2

RAVS2

VSS

VSS

ALE

1284312744126451254612447123481224912150120511195211853117541165511556114

1

2

3

4

5

6

7

8

9

10

11

DD

SS

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

394142

40

A[4]

A[5]

A[6]

A[7]

A[0]

D[6]

D[7]

A[1]

A[2]

A[3]

VSSO

VDDO

D[4]

D[5]

113

CY7C955

AX

ATM

SONET / SD H

TRANSCEIVER

D[3]

112

D[2]

111

D[1]

110

57

D[0]

109

58

INTB

108

59

VDDI

VSSI

10795106

60

61

WRB

RDB

10594104

62

639664

VSS

103

102

101

100

99

98

97

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

VSS

RSTB

CSB

VSS

RATE[0]

RATE[1]

TSOC

TPRTY

TDAT[7]

TDAT[6]

TDAT[5]

TDAT[4]

TDAT[3]

TDAT[2]

TDAT[1]

TDAT[0]

TCA

TWRENB

TFCLK

RSOC

RPRTY

VDDO

VSSO

RDAT[7]

RDAT[6]

RDAT[5]

RDAT[4]

RDAT[3]

RDAT[2]

VDDO

VSSO

RDAT[1]

RDAT[0]

RCA

RRDENB

RFCLK

TSEN

VSS

VSS

ATP 1

LFO

LF

VSS

VSS

RBYP

ATP3

TCP

VSSI

XOFF

VSSO

TCLK

TFPO

TGFC

VDDO

VSSO

RCP

RFP

RCLK

RGFC

VDDI

VSS

VSSI

RALM

−

LF+

7C955−2

7

PRELIMINARY

CY7C955

Description

Transmit Section

T ransmit Utopia Interface (TUI)

The transmit interface provides a simple access from the external environment to the ATM Transceiver. The operation of

this interface is compliant with the Utopia interface specification. The interface provides a 9-bit by 4-cell FIFO to decouple

the system interface from the ATM physical layer timing. 9-bit

words are c loc ke d i nto t he de vi ce thr ough a clo c ked FI FO s ystem interface. These 9 bits include an 8-bit data word along

with a Start Of Cell (SOC) indication. The interface also provides full and almost full indications (TCA). Maximum cl ock

rate for this interface is 33 MHz.

T ransmit ATM Cell Pr ocessor (TACP)

The ATM cell processor provides HEC generation, idle/unassigned cell header modificat ion, pa yload scr ambli ng, and GFC

insertion.

HEC Generator

The Header Error Check (HEC) code is contained i n the last

byte of the ATM cell header and is capable of single error correction and multiple error detecti on. When optionally generated, the Transmit ATM Cell Processor calc ulates a CRC−8 ov er

the first four bytes of the ATM cell header using the pol ynomi al

8

x

+ x2+ x + 1. The coset x6 + x4 + x2 + 1 is added (modulo 2)

to the residue of thi s funct ion. The HEC is calc ulated in accordance with ANSI T1.624−1993 and CCITT Reco mmendation

I.432. This HEC sequ ence i s plac ed in th e 5th b yte of the ATM

cell header.

Idle/Unassigned Cell Header Modification

Idle (Unassigned) cells are sent by the ATM cell processor

whenev er a complete cell is not contained within the Transmit

FIFO. This transforms the non-continuous cell input stream

into a continuous stream of assigned and unassigned cells.

The ATM cell processor provides the ability to overwrite the

Generic Flow Control (GFC), the Payload Type Indication

(PTI), and the Cell Loss Priority (CLP) fields of Idle (Unassigned) cells with the values contained in the corresponding

configura tion registe rs. VPI and VCI are set to zero in I dle (Unassigned) cells.

Payload Scrambler

The 48 bytes of the ATM payload are scrambled using a parallel implem entation of the polynomial x

CCITT Recommendation I.432. The scrambler can be optionally deselec ted.

GFC Insertion

The transmit ted GFC field of an ATM cell can be derived fr om

different sources. For assigned cells, the default is from pins

TDAT[7:0]. For Idle (Unassigned) cells, the default is from

GFC[3:0] (Reg−61H, bit 7−bit 4). However, if any bit of

TGFCE[3:0] (Reg−67H, bit 7−bit4) is set, the corresponding

transmitted G FC location will instead be taken from the serial

TGFC (pin 52) input following the functional timing specifications described in the section on Transmit GFC Serial Link

Interface.

43

+ 1 as described in

Transmit SONET Path Overhead Processor (TPOP)

The SONET path ov erhe ad proces sor provi des pa y load poi nter alignment (H1, H2), path overhead insertion, and insertion

of the Synchron ous Payload Env elope (SPE). ATM cells (bot h

assigned and unassi gned ) are in serted into the SPE f or trans mission in the SONET frame

SONET Overhead Insertion

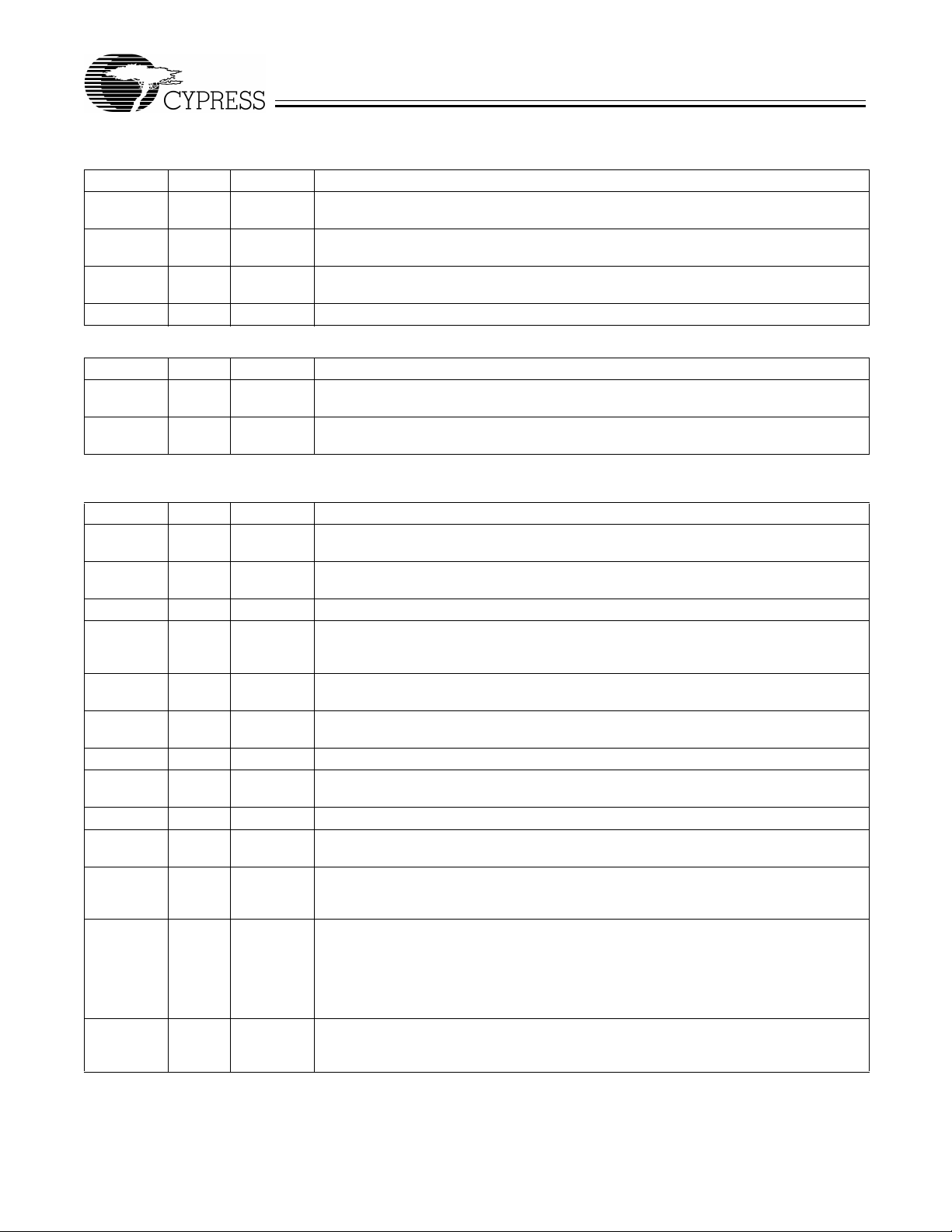

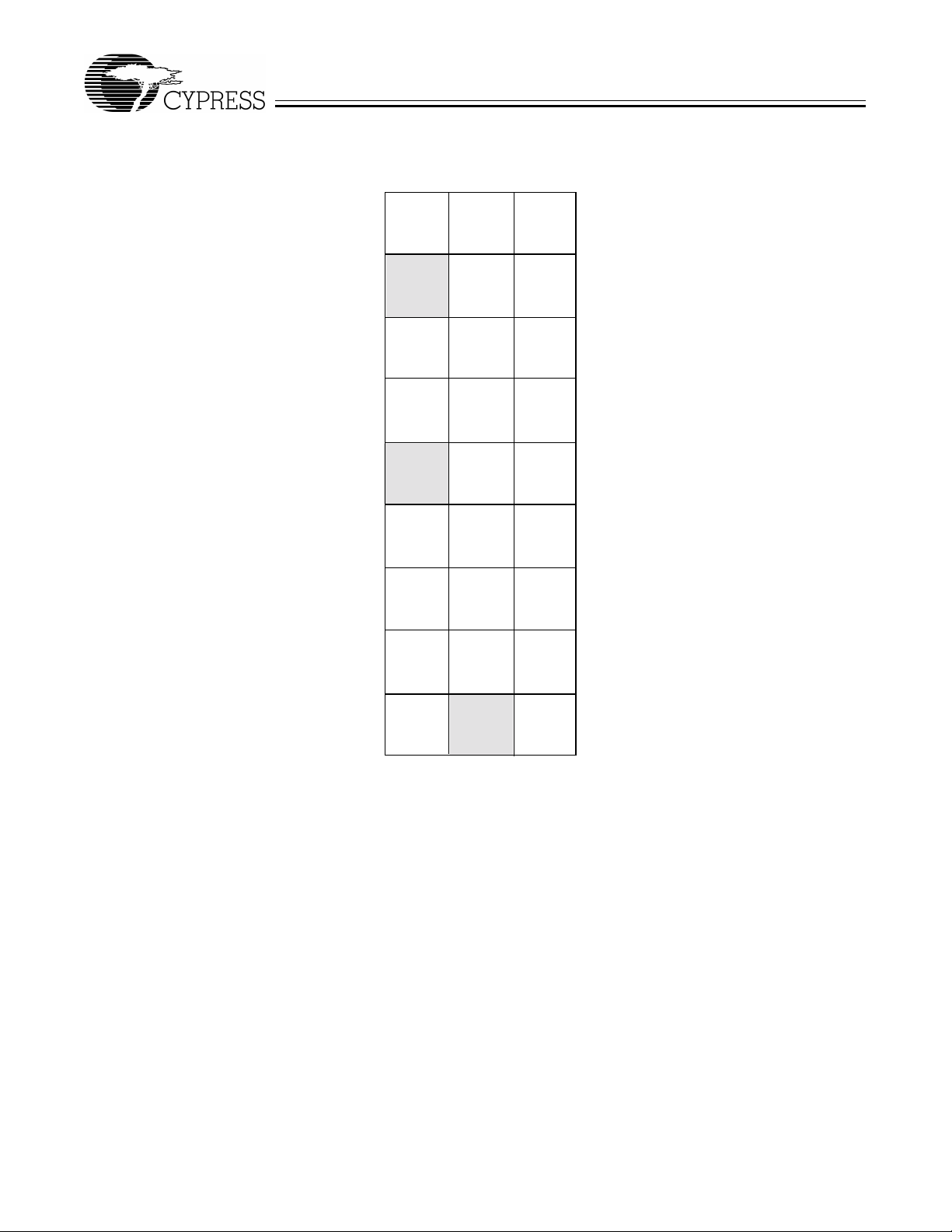

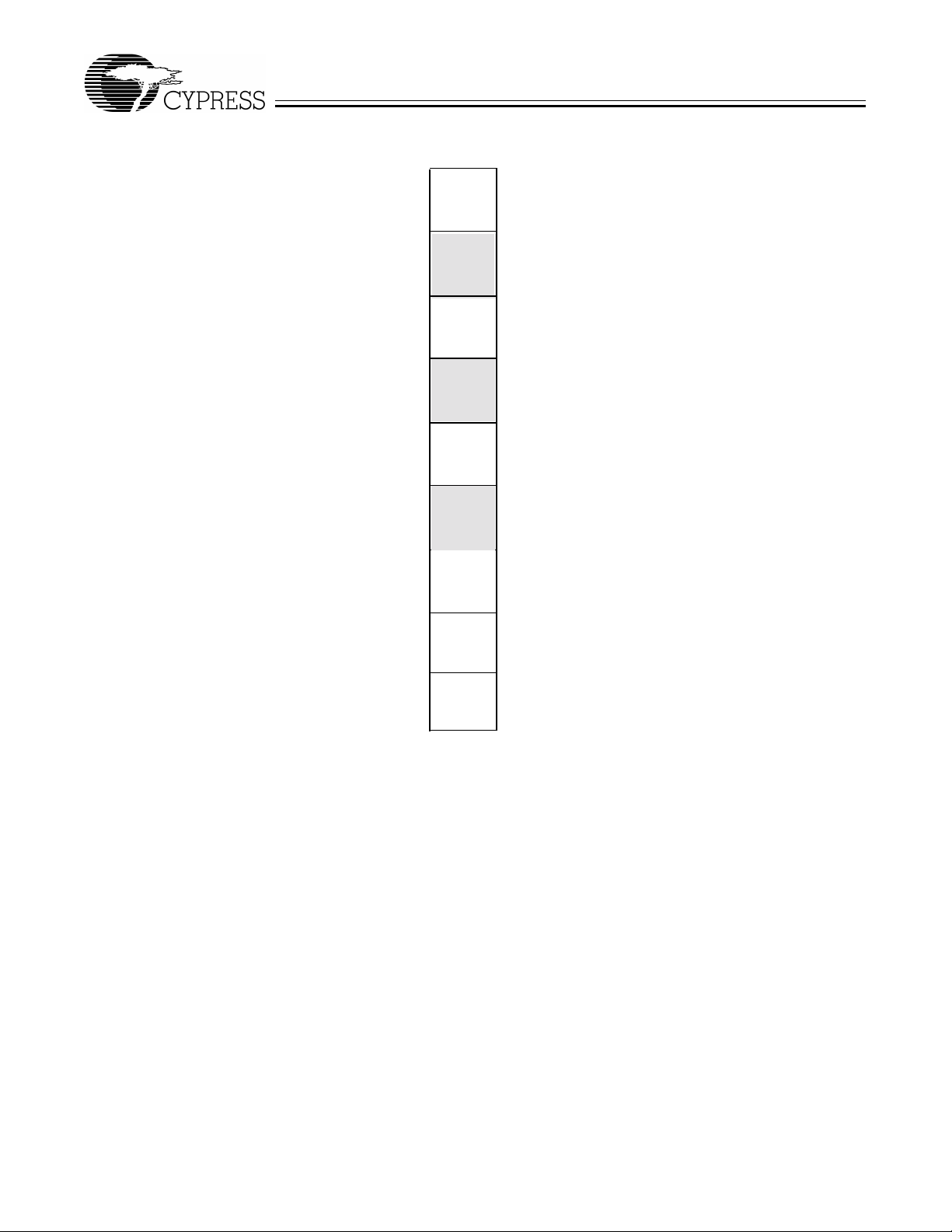

The SONET/SDH STS−3c/STM−1 frame st ructur e is sho wn in

Figure 1 and the SONET STS−1 frame structure is shown in

Figure 2. The SONET fram e occurs once every 125 µs and is

transmitted beginning with the A1 bytes, followed by the A2

bytes, C1 by tes, 261 by tes (87 bytes for S TS−1) of the Synchronous Payload Envelope (SPE), B1 bytes, etc., until the

entire frame is tr ansmitted.

The TPOP generates the H1 and H2 bytes that indicate the

beginning of the SPE and the H4 byte that indicates the ATM

cell offset within the SPE. The default initial value for H1 and

H2 pointer is 522, meaning that the first byte of the SPE (J1)

corresponding to a frame actually starts after the C1 byte of

the next frame.

In the def ault case des cribed abov e, a 6h i s present i n the New

Data Flag (NDF) portion of the first H1 (bits 0−4), a 2h is

present in bits 5−7 and a 0Ah is present in the first H2 byte.

The remaining H1 b ytes f or STS−3c/STM−1 are s et to 93h and

the remaining H2 b ytes ar e set t o FF h which i s the c onca tenation indication for the J1 pointer. The Pointer Action by te, H3,

is set to 00h. During Path AIS all of the H1 and H2 bits are set

to 1.

The STS path trace J1 is set to all zero s. The path BIP−8 (B3)

byte provides path error monitoring. This function calculates

the bit-inte rleav ed parity- 8 code usin g ev en parity o ve r the pre vious SPE before scrambling and is inserted into the current

B3 byte before scrambling. Bit-interleaved parity-8 forces the

number of 1s in the xth bit of every byte in the previous SPE

plus the xth bit of the B3 by te in t he curre nt SPE to be an even

number.

The path signal level indicator, C2, defaults to 13h.

The path status, G1, has several functions. Bits 1 through 4

are used to indicat e Far End Block Errors (FEBE) derived by

counting the nu mber of BIP−8 error s occurred in t he last fr ame

received. Valid codes are 0 through 8. If more than 8 errors

have a ccum ulated since the last, frame the maxim um value is

sent with the curr ent fr ame , the F EBE counter is decr emented

by 8, and the remaining errors are sent with the next frame.

FEBE may be inserted through register control for diagnostic

purposes. Bits 1 through 4 can also be used to transmit Far

End Receive Failures by setting these bits to 9 (1001). This

error indicat es to the far en d that cell deli neation has been lost .

Bit 5 can be used to generate a yellow alarm condition. The

default v alue for this bit is 0 (no alarm).

The multi-frame indicator, H4, is used to ind icate the first ATM

cell and may take on values of 00 to 34h.

The remaining bytes, F2, Z3, Z4, and Z5, are not used by the

SONET path processing and ar e set to 00h upon transmiss ion.

When operating in STS−1 mode, SPE columns 30 and 5 9 can

be configured as fixed stuff columns.

8

PRELIMINARY

.

A1

A1 A1 A2 A2 A2 C1 C1 C1

CY7C955

B1

E1 F1

Section

D1 D2 D3

H1

H1 H1 H2 H2 H2 H3 H3 H3

B2

B2 B2 K2

K1

D4 D5 D6

Line

D7 D8 D9

D10 D11 D12

Z1 Z1 Z1 Z2 Z2

9Bytes

Z2

E2

Figure 1. STS−3c/STM−1 Framing Form at

Payload

J1

B3

C2

G1

F2

H4

Z3

Z4

Z5

Path

Payload

HD1 HD2 HD3 HD4 HEC PAYLOAD

Bytes

261

7C955−3

Bytes

9

A1

B1

D1 D2 D3

H1

B2

D4 D5 D6

Line Section

D7 D8 D9

D10D11 D12

Z1 Z2

A2 C1

E1 F1

H2 H3

K1

E2

3Bytes

K2

Payload

J1

B3

C2

G1

F2

H4

Z3

Z4

Z5

Path

Payload

HD1 HD2 HD3 HD4 HEC PAYLOAD

87

Bytes

Bytes

9

7C955−4

Figure 2. STS−1 Framing Format

9

PRELIMINARY

CY7C955

T ransmit SONET Line Overhead Processor (TLOP)

The Transmit SONET line overhead processor (TLOP) provides B IP−8/24 generation and line level alarms.

The BIP−8/24 code is calculated as if the STS−3c frame was

composed of three STS−1s. The f irst B2 byte is calcu lated over

the firs t STS−1 frame, the second B2 byte over the second

STS−1 frame a nd the thir d B2 b yte ov er the t hird STS−1 frame.

Each B2 bit is calc ulated ov er t he line and SPE portions of th e

previou s frame befor e scramb ling using ev en parity and inserted into the current fram e befor e scrambl ing. For STS−1 RATE,

a BIP−8 is calculated over the entire SPE and line overhead

and placed in B2.

The Line Alarm Indicat ion Signal (LAIS), is as serted by changing all bits of the SONET f rame into 1 bef ore scramb ling . LAIS

generation is controlled by a register setting ( R eg−14H, bit 0).

The Line Far End Receive Failure (LFERF), also called Line

RDI, is indicated by pl acing a 110 pattern in bits 6,7, and 8 of

the first K2 byte. LFERF can be asserted under register

(Reg−20H, bit 0) control.

The Line Fa r End Block Err ors (LFEBE) are loca ted in the third

Z2 byte and indicate the number of B2 errors in the previous

frame interval . Legal v alues f or th is by te are 00 h throug h 18h.

All bytes of the line data com munication channel (D4−D12)

and all other unu sed bytes are encoded to 00h.

T ransmit SONET Section Overhead Processor (TSOP)

The Transmit SONET Line Overhead Processor (TSOP) provides A1,A2 framing pattern generation, section BIP−8 (B1)

insertion, secti on level alarm insertion, and fram e scrambling.

The A1 and A2 bytes pro vide a fr aming pattern fo r frame ali gnment. All A1 bytes are coded to F6h and all A2 bytes are coded

to 28h. These bytes are not scrambl ed upon transmission.

The STS−1 identification byt es, C1, are used for framing and

de-interleav ing purposes and are coded the order in their appearance in the STS−3c frame. The first C1 byte is coded to

01h, the second to 02h, and the t hird to 03h.

The section BIP−8 (B1) is the byte-interleaved par ity-8 calculated over all byt es of the previ ous fram e after scramb l ing and

inserted into the current frame before scrambling.

The bytes of the se ction dat a commun ication cha nnel , D1−D3

and the remaining unused bytes are set to 00h.

The frame is scr ambl ed prior to tr an smissi on with the gener a ting polynomial x

scrambled. The scrambler runs continuously through the

frame and reset s at the beginning of the next transmission

frame. The scrambler may be optionally disabled.

T ransmit Clock Generator (TCG)

The TCG accepts a byte-rate transmit clock from TRCLK that

operates at either 19.44 MHz for STS−3c/STM−1 RATE or at

6.48 MHz for STS−1 RATE. The Transmit PLL multiplies this

byte-rate reference by eight to produce the bit-rate clock used

by the parallel-to-serial converter. Optionally a bit-rate source

can be taken from an external source (TBYP = 1) or from the

Receive Clock Recovery block when in loop-time mode

(LOOPT = 1). In loop-time mode the recovered clock is used

to provide timing to the transmitte r.

7

+ x6 + 1. The A1, A2, and C1 bytes are not

Parallel to Serial Converter (PSC)

The PSC converts the parallel data from t he TSOP to serial

data. The bit rate cloc k is derived from the Transmit Cloc k Generator. The serialized data and aligned output clock are presented to the Transmit Output Mult iplexer.

Transmit Output Multiplexer (TOM)

The TOM selects between the serialized output data stream

and associated clock provided by the PSC and the recovered

data and clock from the Receive Clock Recovery block for

transmissi on based on the state of the local loop back enable

(LLE) register (Reg−05H, bit 2). When LLE = 1 the recovered

data and recovered clock is sel ected for ou tput on th e tra nsmi t

data lines (TXD±) and the transmit clock lines (TXC±). The

output signal is 100K compatible differential Positive-referenced ECL (PECL) signal capable of driving any copper or

fiber based media with impedances as LOW as 50Ω.

Receiv e Section

Receive Clock Recovery (RCR)

The RCR provides clock and data recovery from an incoming

differential PECL data stream. Clock and data are recovered

from the incoming differential PECL data stream without the

need for external buffering and AC-coupling. The built-in line

receiver inputs have a wide common-mode range (2.5−5V)

and the ability t o recei v e signal s wit h as littl e as 200 m V diff er ential volt age. They are compat ible with all PE CL signals. They

are compatib le with a ll PECL signal s driv en by optical modul es

or twisted-pair equalizers. The Receive PLL uses the RRCLK

as a byte-rate reference. This input is multiplied by 8 and is

used to impro ve PL L lock time and to provid e a center frequency for operat ion in the absence of input data stream transit ions.

The receiver can recover clock and data in two different frequency ranges depending on the state of the RATE0 pin. To

insure accurate data and clock recovery, the received data

stream must be within 1000 ppm of RRCLK * 8 (The PLL will

declare Out Of Lock if the data rate is different from REFCLK

x 8 by more than 2000 ppm. The PLL will remain Out Of Lock

until the data rate pulls back to within 700 ppm of REFCLK x

8 frequency). The standards, however, specify that the

RRCLK*8 frequency accurac y be within 20−100 ppm. The wid er frequency toler ance r a nge of the CY7C955 i s a n adv ant age

that allows for higher frequenc y tol eranc e in be nch tes ting setups.

A Loss of Signal (ROOLV = 1) is declare d when no transitions

have been detect ed on the incoming data st ream for more than

512 bit-times. LOS is cleared whe n two valid framing patterns

(A1, A2) have been found and the intervening data does not

contain a period that vio lat es the minimum transit ions limit.

Serial to Paral lel Conversion (SPC)

The SPC conv erts bit serial data to byt e s erial dat a fro m ei ther

the recov er ed recei ved dat a or t he trans mit dat a fr om t he PSC

depending on the state of the DLE register (Reg−05H, bit 1).

When DLE =1 transmit data is used for serial to parallel conversion. The SPC also provides SONET framing by scanning

the incoming data for the SONET framing pattern A1,A2. For

STS−1 RATE the framer looks for the pattern F628h and for

STS−3 RATE the framer looks for the pattern

F6F6F6282828h. Out of Frame (OOF) is declared when four

consecutive frames contain a framing error. OOF clears when

two frames cont ain valid framing characters. Loss of Frame

10

PRELIMINARY

CY7C955

(LOF) is decl ared when the OOF c ondition fail s to clear withi n

3 ms. L OF clears after 3 m s of frames with valid framing characters.

Receive SONET Section Overhead Processor (RSOP)

The RSOP provides descrambling, SONET section alarm indication, and error monitoring.

The data is descrambled using the generating polynomial 1 +

6

x

+ x7. The A1, A2, and C1 bytes are not descrambled. The

scrambling process may be disabled under register control.

The BIP−8 v alue calculated ov er the pre vious scrambl ed frame

is compared wi th the B1 b yte of the current fr ame section ove rhead after descrambling. If the two values do not match, the

B1PAR output is taken HIGH. Up to 64,000 errors can be detected per second (8000 frames/second * 8 bit-errors

(max)/frame). Errors are recorded in a 16-bit saturating

counter that ca n be read through the controller int erface.

Receive SONET Line Overhead Processor (RLOP)

The RLOP provides SONET line alarm indications and error

monitoring.

A Line Alarm Indication Signal (LAIS) is asserted when a 111

pattern is detected for five consecutive frames in bits 6,7, and

8 of the first K2 byte of the Automatic Protection Switching

channel. LAIS i s removed when anyt hing other than a 111 pa ttern is received for five consecutive frames.

A Line Fa r End Receive Failure (LFERF) or Line RDI is indicated with a 110 patte rn is detected for five consecut ive frames

in bits 6,7, and 8 of the first K2 b yte. LFERF is removed when

anything other than a 110 pattern is received for five consecutive fram es.

The BIP−24 (BIP−8 for STS−1 RATE) value calculate d ove r the

previou s line overhe ad and SPE is compar ed with the B2 by tes

of current frame. Up to 192,000 errors can be detected per

second (3 channels/frame * 8 errors (max)/channel * 8000

frames/second). Errors are recorded in a 20-bit saturating

counter that ca n be read through the controller int erface.

Far End Block Errors (FEBE) are detected by examining the

value i n t he t h ird Z2 byt e. T hi s val ue (0 −18h) is added to the

count in an 18-bit saturatin g counter that can be rea d thr ough

the controller interface.

Receive SONET Path Overhead Processor (RPOP)

The RPOP provides pointer interpretation, SPE extraction,

SONET path alarm indications, and error monitoring.

The pa yload locat ion i s d etermined b y e xami ning t he val ues in

the H1 and H2 b y tes of the l ine o ver hea d which i ndicat e the J 1

byte of the SPE. The RPOP can process a J1 byte located

anywhere in the SPE. Loss of P ointer ( LOP) is set when a vali d

pointer value has not been found within eight consecutive

frames. Thi s register bit is cleared when a val id pointer is foun d

for three consecutive frames. Path Alarm Indication Signal

(PAIS) (Reg30H, bit 3) is set when the H1 and H2 bytes are

set to all ones for 3 consecutive frames. This register bit is

cleared when a valid pointer is found for three consecutive

frames. PAIS does not cause LOP to be s et. The SPE locat ion

is provided to the Receive ATM Cell Processor for cell extraction.

The BIP−8 value calculated over the previ ous SPE is compared with the B3 byt e of the current path overhead. Up to

65,535 errors can be detected per second. Err ors are recorded

in a 16-bit saturating counter that can be read through the

controller interface.

Path F ar En d Block Errors (PFEBE) a re detect ed by e xamining

the value in bits 1 through 4 of G1. This value (0−8h) is added

to the count in a 16-bit saturating counter that can be read

through the controller interface.

Path Far End Receive Failures (PFERF) are detected by examining the value in bits 1 through 4 of G1. If this value is 9h

for two consecutive frames, PFERF is set. This register bit is

cleared when anything other than 9h appears for two consec utive frames.

Path Remote Defect Indication (Path RDI) is detected by examining bit 5 of G1. If thi s val ue is 1 h f or 5 consec utiv e fr ames ,

PYEL is set. This register bit is cleared when a 0 appears in

bit 5 for 5 consecutive frames.

Receive ATM Cell Processor (RA CP)

The RACP block provides cell delineation, HEC checking and

correcting, cell filtering for idle/unassigned cells, cell payload

descrambling, status indicat ions, and error monitori ng.

Cell delineati on is per formed b y comparing t he HEC seque nce

calculated over the first four bytes of the SPE to the fifth byte.

If these values match, cell boundary has been determined. If

not, the calculati on advances one b yte further into the pa yload

(bytes 2−5) and the check is performed again. The HEC sequence is a CRC−8 calculated o ver the first 4 octet s of the A TM

cell header using the polynomial x

+ x4 + x2 + 1 is added (modulo 2) to the residue before comparison with the receiv ed seque nce. Thi s is t he HUNT state of

the cell deli neat ion pr ocess. When a v ali d match has occ urred

the process enters the PRESYNC state. When 7 consecutive

matches occur the process enters the SYNC state. If 6 consecutive incorrect HEC matches are detected the process

moves back to the HUNT state. The average time for cell delineation is 93µs for STS−1 and 31µs for ST S −3C.

The HEC sequence is used not only to check for cell alignment, but also to insure that integrity of the ATM header. The

HEC is used to correct single bit errors and to detect multiple

bit errors. This feature can be disabl ed. The register file contains two satur ating 8-bi t coun ter s f or HEC er rors; one for cells

with single bit errors and another for multiple-bit errors. Cells

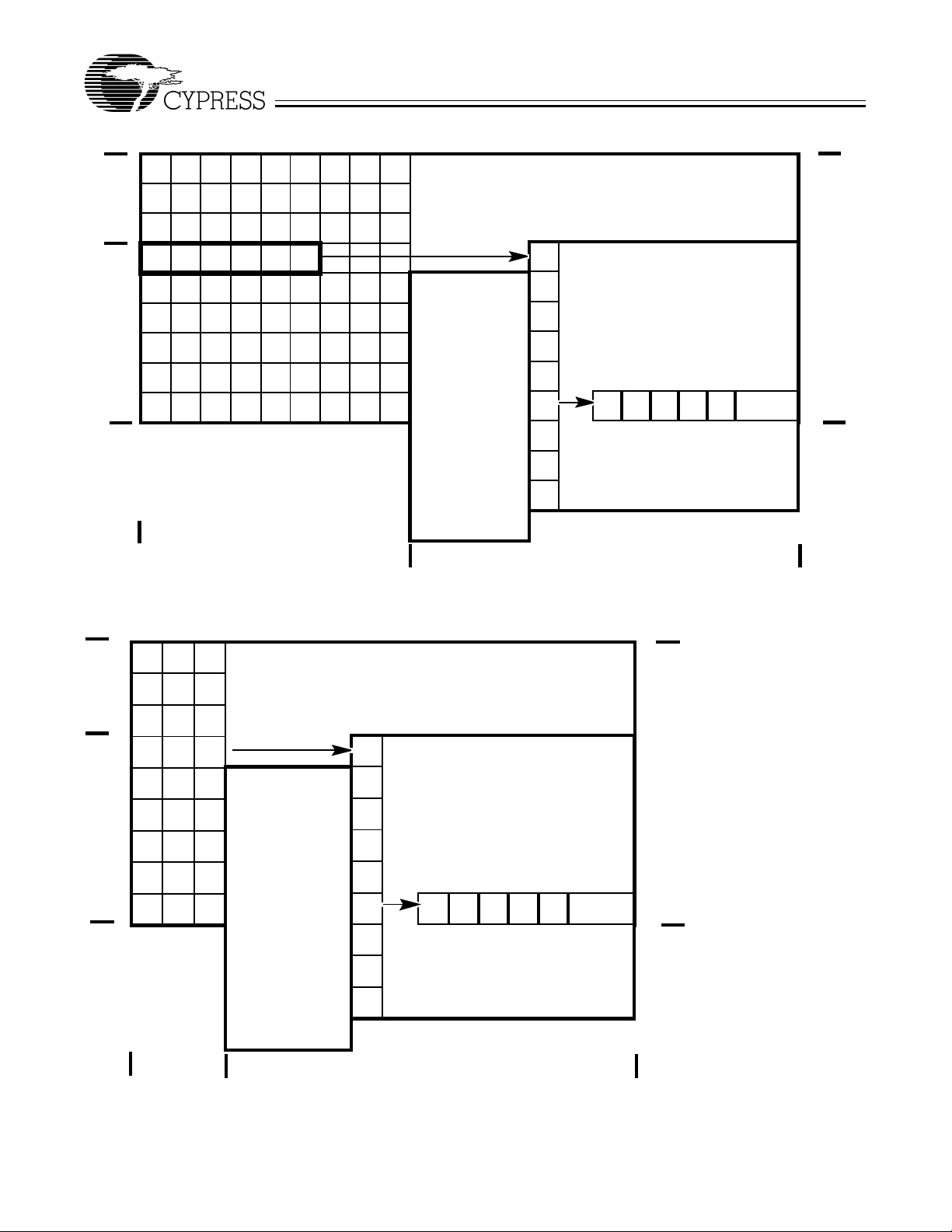

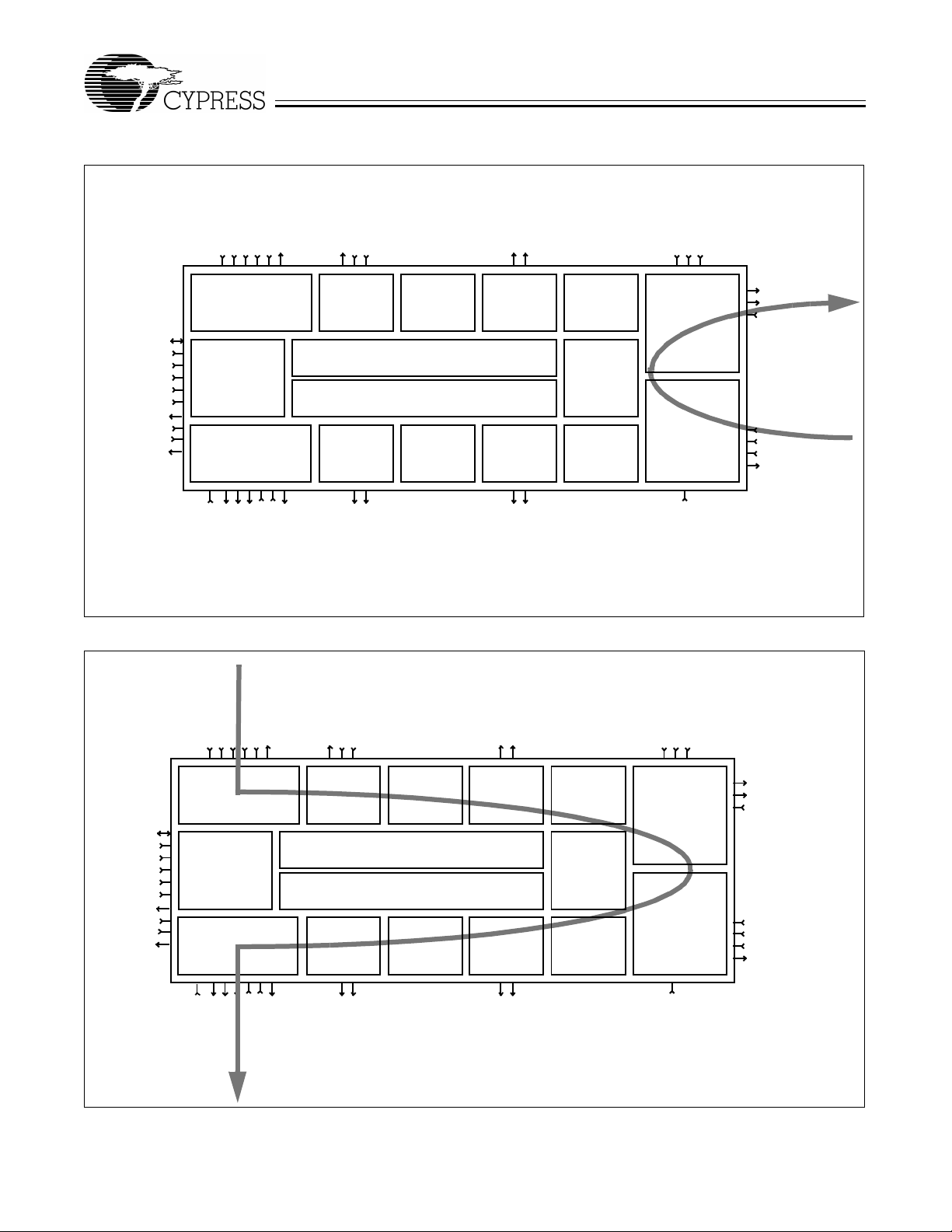

with multiple bit errors are optionally discarded. Figure 3

shows the state di agram for HEC.

The RACP optionally discards Idle/Unassigned cells. These

cells contain a VPI/VCI address of 0h. Also, a Header Mask

and Header Match register are provi ded to allow cells with a

particular header characteristic in GFC, PTI and CLP to be

filtered.

The payload of valid cells are descrambled using the polyno-

43

mial x

+1. The cell headers are not descrambled since they

8

+ x2 + x + 1. The coset x

6

11

PRELIMINARY

were not scr ambl ed upon tr ansmission. The descr ambli ng feature can be disabled.

ATMDELINEATION

SYNC

STATE

ApparentMulti-Bit Error

(Drop Cell)

No Errors

Detected

PassCell

DELTA

consecutive HECs

(From PRESYNCstate)

CORRECTION

MODE

SingleBit Error

(CorrectError

and PassCell)

No ErrorsDetected

(PassCell)

Figure 3. HEC Verification State Diagram

DETECTION

MODE

Errors

Detected

(Drop

Cell)

CY7C955

ALPHA

consecutive

HECs (From

HUNT state)

7C955−5

Receive Utopia Interface (RUI)

The RUI provides a simple access from the external environment to the ATM T r anscei v er. The operation of this interfa ce is

compliant with the Utopia interface specification that is being

standardized by the ATM Forum. The interface provides a 10

bit by 4 cell FIFO to decouple the system interface from the

ATM physical layer timing. Ten bit words are clocked out from

the device through a clocked FIFO style interface. These 10

bits include an 8-bit data word along with an parity bit

(RXPRTY) and a Start Of Cell ( SO C) indication. T he interface

also provides a cell available (RCA) indication and a read enable (RRDENB) cont rol. RCA allo ws the FIFO to i ndicate empty and almost empty conditions and RRDENB allows the

downstream circuit to pause the reading process in case the

downstream can not accep t anymore r ead. If the Rec eiv e FIFO

overflows, FIFO reset will occur and up to 4 cells may be lost

because of t he operation.

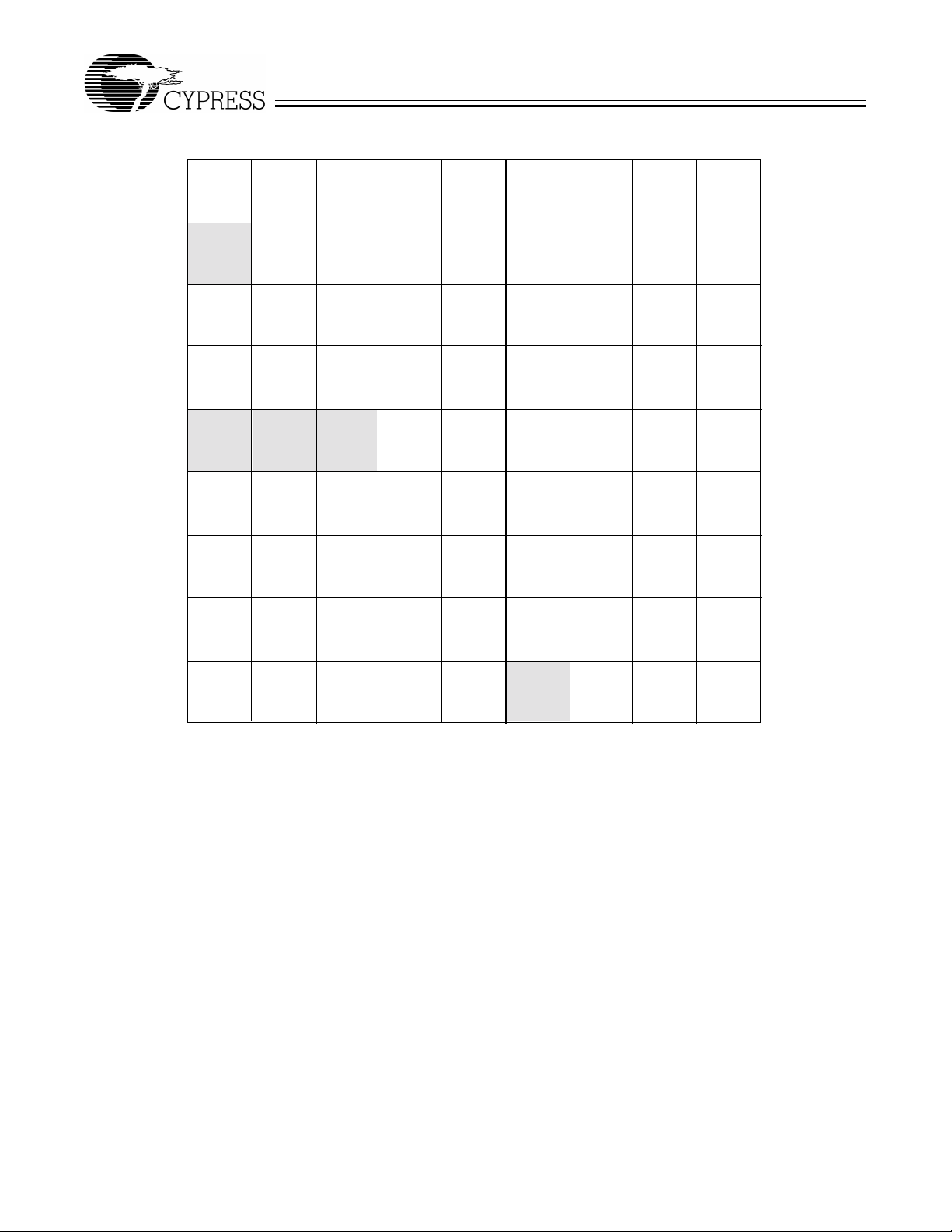

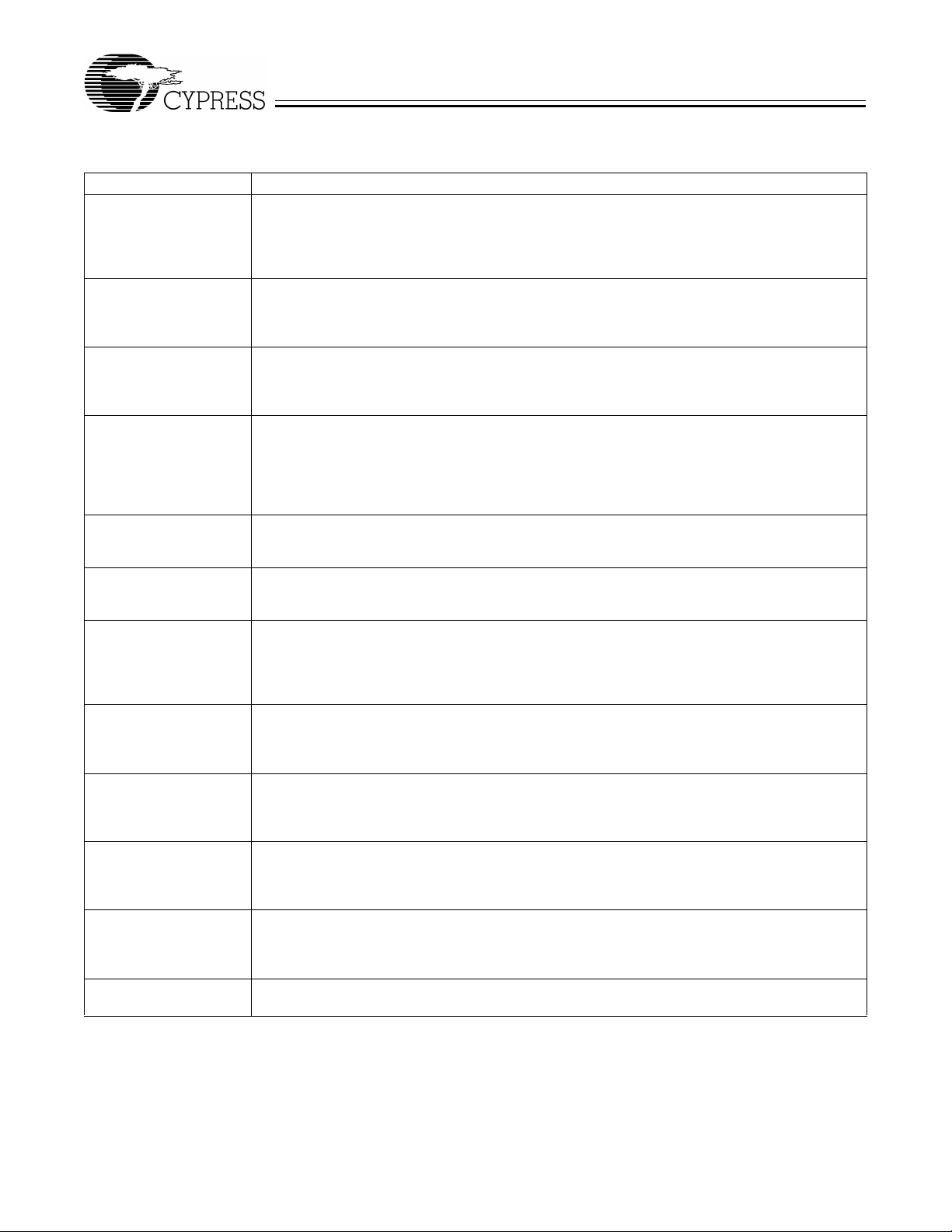

Controller

Interface

SONET/SDH

Overhead Processing

Fiber or Copper

Media Interface

Fiber or Copper

Media Interface

Receive Serial Data

Carrier Detect

Buffered TransmitData

Byte Rate

Oscillator

Clock a nd Data

Recovery and

Receive

Equalization

Frequency

Multiplication &

Transmit

Buffering

Controller Interface (CI)

The CI interface provides external access to the internal register file, device resetting and ext ernal input for the carrier detect signal. The ALOS input allows an external carrier detect

from an optical module to cause an interrupt to the controller.

The INTB and RALM pins can be configured to interrupt the

external con trol ler whe ne ver an y of se v er al di ff er ent err or con ditions occur. RALM signals the most important error conditions such as LOS, LOF, line AIS, path AIS, LCD, and LOP.

INTB may indicate all possible errors depending on the state

of the mask regi ster s . INTB pr o vides n otif ication of the in divid ual processing block that generated the error condition. The

error register contained in each block will determine the e xact

cau se of the in terrupt.

Packet

Reassembly

or

ATM Switch

Core

Packet

Segmentation

or

ATM Switch

Core

ATM Cell

Processing

Receive Parallel Data

Receive Start of Cell

Receive Parity

Read Strobe

Parallel Data

Transmit

TransmitStart of Cell

TransmitParity

WriteStrobe

CY7C955ATM−SONET/SDHTransceiver(AX)

Figure 4. SONET/SDH and ATM Interface

12

7C955−6

PRELIMINARY

CY7C955

F6

A1

NOTE

B1

00

D1

62

H1

[NOTE

B2

00

D4

00

D7

00

D10

H

F6

A1

1

00

00

93

H

H

H

H

H1

1]

[NOTE

B2

H

00

H

H

00

H

00

H

H

H

H

1]

F6

A1

00

00

93

H1

[NOTE

B2

00

00

00

28

H

A2

H

00

E1

H

00

D2

H

0A

H2

1]

00

H

K1

00

H

D5

00

H

D8

H

00

D11

28

H

A2

00

H

28

H

A2

00

H

H

01

H

H

C1

00

02

C1

00

H

03

H

H

C1

00

H

H

F1

00

H

H

00

H

00

00

H

00

H

H

D3

FF

H

H2

00

H

FF

H

H2

00

H

00

H

H

H3

00

00

H3

00

H

H

00

H

H

H3

00

H

K2

00

H

H

00

00

H

00

H

00

H

H

D6

00

H

H

00

H

00

00

H

00

H

H

D9

00

H

H

00

H

00

00

H

00

H

H

D12

00

H

Z1

Note:

1. B1, B2, Z2, G1, H4, and B3 are variables.

Figure 5. Default Values for the Transmitted Section and Line STS−3C/STM−1 Overhead

00

Z1

H

00

Z1

[NOTE

Z2

1]

00

E2

00

H

Z2

00

H

H

Z2

00

H

00

H

H

7C955−7

13

PRELIMINARY

CY7C955

F6

H

A1

NOTE 1

B1

00

H

D1

62

H

H1

NOTE

B2

00

D4

00

D7

00

D10

F6

A2

00

H

E1

00

D2

0A

H2

1

00

K1

H

00

D5

H

00

D8

00

H

D11

00

H

H

C1

00

H

F1

00

H

H

D3

H

00

H

H3

00

H

H

K2

00

H

H

D6

00

H

H

D9

00

H

H

D12

NOTE

Z2

1

00

H

E2

7C955−8

00

H

Z1

Figure 6. Default Values for the Transmitted Section and Line STS−1 Overhead

14

PRELIMINARY

00

J1

NOTE

B3

13

C2

NOTE

G1

00

F2

NOTE

H4

CY7C955

H

1

H

1

H

1

00

H

Z3

00

H

Z4

00

H

Z5

7C955−9

Figure 7. Default Values for the Transmitted Path Overhead

15

Loopback Operatio n

TDAT[7:0]

TXPRTY

PRELIMINARY

TSOC

TFCLK

TWRENB

TCA

TCP

XOFF

TGFC

TFPO

TCLK

TBYP

RATE0

RATE1

CY7C955

D[7:0]

A[7:0]

ALE

RDB

WRB

CSB

INTB

RSTB

VCLK

RALM

UTOPIA I/F

Transmit FIFO

4 Cell by 8 bit

Controller

Interface

UTOPIA I/F

Receive FIFO

4 Cell by 8 bit

TSEN

RSOC

RXPRTY

RDAT[7:0]

TDAT[7:0]

TSOC

TFCLK

TXPRTY

TWRENB

Transmit Transmit Transmit TransmitTransmit

ATM Cell

Processor

Configuration and Status

Register File

Error Monitoring

Receive Receive Receive ReceiveReceive

Processor

RCA

RFCLK

RRDENB

RCP

RGFC

Path

Overhead Overhead Overhead

PathATM Cell

Processor Processor Processor

Line Section

ProcessorProcessorProcessor

Rate

Selection

SectionLine

OverheadOverheadOverhead

RFP

RCLK

Transmit

Clock

Multiplier &

Transmit

Buffer

SONET/SDH

Clock

Recovery

RBYP

High Speed Line Loopback

RATE1

TBYP

TCA

TCP

XOFF

TGFC

TFPO

TCLK

RATE0

TXD±

TXC±

TRCLK±

ALOS±

RRCLK±

RXD±

RXDO±

7C955−10

D[7:0]

A[7:0]

ALE

RDB

WRB

CSB

INTB

RSTB

VCLK

RALM

UTOPIA I/F

Transmit FIF O

4 Cell by 8 bit

Controller

Interface

UTOPIA I/F

Receive FIFO

4 Cell by 8 bit

TSEN

RSOC

RXPRTY

RDAT[7:0]

Transmit Transmit Transmit TransmitTransmit

ATM Cell

Processo

Configuration an d S ta t us

Regis ter Fil e

Error Monitoring

Receive Receive Receive ReceiveReceive

Processor

RCA

RFCLK

RRDENB

RCP

RGFC

Path

Overhead Overhead Overhead

r

PathATM Cell

Processor Processor Processor

Line Section

RFP

RCLK

ProcessorProcessorProcessor

Rate

Selection

SectionLine

OverheadOverheadOverhead

Transmit

Clock

Multip lier &

Transmit

Buffer

SONET/SDH

Clock

Recovery

RBYP

Diagnostic Loopback

TXD±

TXC±

TRCLK±

ALOS±

RRCLK±

RXD±

RXDO±

7C955−11

16

PRELIMINARY

CY7C955

SONET Overhead Description

Signal Values Description

A1, A2 The frame ali gnment b yt es mark the begi nning of a SONET frame . The y are t ransm itted e very 125

C1 This is t he ident ificat ion b yt e f or th e STS d ata st ream. Transmit Side: In OC−1, C1 is tr ansm itted as

B1 This is the se ction bit i nterleave p arity byt e. T r ansmit Side: B1 is calcul ated using the BIP−8 algorithm

H1, H2 These are the poi nter val ue b yte. These b yt es ar e use d to l ocate the beginni ng of th e Synchro nous

H3 This is the pointer action byte. Transmit Side: H3 will be all zeroes. Receive Side: Synchronous

B2 This is the line bit interleaved parity bytes, it is used to monitor line errors. Transmit Side: B2 is

K2 This is the identity line lay er maint enance signal . Transmit Side: Bits 6, 7, and 8 of thi s byte ar e ‘110’

Z2 This is the growt h byte. It is us ed to prov ide far end bloc k error f unction usef ul for remote perf ormance

B3 This is the interleaved parity byte. Transmit Side: B3 is calcul ated over all bits of the SPE of the

C2 This is the path signal label byte for indicating the contents of the SONET payload. Transmit Side:

G1 This is the path status byte. Transmit Side: P ath remote def ect Indication (P ath RDI) together with

H4 This is the cell offset byte. Transmit Side: Thi s byte i ndicates the of fset in bytes bet ween the H4 b yte

µs in both OC−1 and OC3c speeds. Transmit Sid e: In OC−1, A1(F6

into the t ransmitted stream at the beginning of every frame. These bytes are not scrambled by the

frame synchronous SONET scrambler. Receive Side: The receiv er will search for and frame onto

the incoming A1, A2 bytes.

OH. In OC −3c, the sequence C1, C1, C1 of every fr ame is transmitted as 01

bytes are not scrambled by the fr ame-synchronous SONET scrambler. Receive side: The receiver

will ignore C1.

described in I.432. It i s inserted into the SONET data st ream bef ore the f rame syn chronous SONET

scrambl er. Receive Side: Received B1 error events are accumulated in the SBE [15:0] (Reg−12H

and Reg−13H).

Pa yload Env elope (SPE) in the SONET/SDH frame. T r ansmit si de: H1, H2 contains th e normal new

data flag (0110 ) to gether with 522 (decimal) as th e fi xed pointer value field. The concatenation

indication byte is also inserted (H1* = 93, H2* = FF). Receive Side: H1 and H2 are used to locat e

the beginni ng of the SPE. If a v alid po inter canno t be fou nd, CY7C955 will i ndicate a Los s of Po inter

State. Path AIS is detected by an all-ones pattern in H1 and H2 bytes.

Payload Data will be stuffed in the H3 byte if a negat ive stuff e vent occurs. This byte is ignored

otherwise.

calculat ed over all bits of the line overhead and the SPE cap acity of the previous frame before the

frame is being scrambled. The B2 byte itself is then placed in t he current frame before scramble.

before scramb ling when Line Remote Def ect I ndicatio n is true. Th e whole of K2 is an all -one pattern

before scrambling if Lin e AIS is inserted. Recei ve Side: Bits 6, 7, and 8 of the K2 byte are being

exami ned to determine the presence of AIS, and RDI si gnals. Access to APs registers will be

av ail a ble in future revisions .

monitoring. Transmit Side: The number of B2 errors detected in the last frame is inserted. Z2 is a

number from 0−24 indi cati ng 0 −24 errors . Recei ve Si de: A le gal (0 −24) Z2 num ber will be add ed to

the line FEBE counter.

previo us frame before s crambling and is pl aced in the current f rame befo re scramb ling. This provides

path error moni toring capability for the link. Receive Side: The val ue in B3 is accum ulated in a

register.

It’s fixed value is 13H. This indicates the payload is ATM. Receive Side: The receive si de expects

C2 to be 13H. If the data is not 13H f or 3 consecutive frames, an interrupt (if enabled) will be

generated.

the number of B3 erro rs in the last frame are inserted into G1 before scrambling f or transmission.

G1 is a number from 0−8, indicating 0−8 errors. Receive side: A legal G1 value (0−8) will be ac cumulated in the FEBE counter. Path remote defect indication is also detected through this byte.

and the first cell byte after H4. Receive Side: H4 byte is ignored.

) and A2 (28H) are inserted

H

, 02H, 03H. These

H

17

PRELIMINARY

CY7C95 5 R eg i ster Map

Address Register

Reg−00H Master Reset/Type/Identify Register

Reg−01H Master Configu ration Register

Reg−02H Master Inter rupt Register

Reg−04H Master Clock Monitor Register

Reg−05H Master Control Regis ter

Reg−06H Transmit Clock Synthesis Control Register

Reg−07H Receive Clock Synthesis Control Register

Reg−10H Receive Section Overhead Processor Control Regi ster

Reg−11H Receive Section Overhead Processor Status Register

Reg−12H LSB of the Receive Section Overhead Processor Status BIP-8 Counter

Reg−13H MSB of the Receive Sec ti on O verhead Processor Status BIP-8 Counter

Reg−14H Transmit Section Overhead Processor Control Register

Reg−15H Transmit Section Overhead Processor Control Error Insertion Register

Reg−18H Receive Line Overhead Processor Control and Status Register

Reg−19H Receive Line Overhead Processor Interrupt Enable and Status Register

Reg−1AH Line B I P −8/24 Register

Reg−1BH Line B I P −8/24 Register

Reg−1CH Line BIP−8/24 Register

Reg−1DH Line Far-End Block Error Register

Reg−1EH Line Far-End Block Error Register

Reg−1FH Line Far-End Block Error Register

Reg−20H Transmit Line Overhead Processor Register

Reg−21H Transmit Line Overhead Processor Error Insertion Register

Reg−30H Receive Path Overhead Processor Interrupt Regis ter

Reg−31H Receive Path Overhead Processor Register

Reg−33H Receive Path Overhead Processor Interrupt Enable Register

Reg−37H Receive Path Signal Label Register

Reg−38H Path BIP−8 (B3) Register

Reg−39H Path BIP−8 (B3) Register

Reg−3AH Pat h Far-End Block Error Register

Reg−3BH Pat h Far-End Block Error Register

Reg−3CH Path Far-End Block Error Register

Reg−40H Transmit Path Overhead Processor Error Insertion Register

Reg−41H Transmit Path Overhead Processor Pointer Control Register

Reg−45H Transmit Path Overhead Processor Arbitrary Payload Pointer Register

Reg−46H Transmit Path Overhead Processor Arbitrary Payload Pointer Register

Reg−48H Transmit Path Overhead Processor Path Signal Label Register

Reg−49H Transmit Path Overhead Processor Arbitrary Path Status Register

Reg−50H Receive ATM Cell Processor Control and Status Register

Reg−51H Receive ATM Cell Processor Interrupt Register

Reg−52H Receive ATM Cell Processor Match Header Pattern Register

Reg−53H Receive ATM Cell Processor Match Header Mask Register

Reg−54H Receive ATM Cell Processor Correctable HCS Error Count Register

CY7C955

18

PRELIMINARY

CY7C955

CY7C95 5 R eg i ster Map

Address Register

Reg−55H Receive ATM Cell Processor Uncorrectable HCS Error Coun t Regi ster

Reg−56H Receive ATM Cell Processor Receive Cell Counter Register

Reg−57H Receive ATM Cell Processor Receive Cell Counter Register

Reg−58H Receive ATM Cell Processor Receive Cell Counter Register

Reg−59H Receive ATM Cell Processor Receive Configuration Register

Reg−60H Transmit ATM Cell Processor Control and Status Register

Reg−61H Transmit ATM Cell Processor Unassigned Cell Header Register

Reg−62H Transmit ATM Cell Processor Unassigned Cell Payload Register

Reg−63H Transmit ATM Cell Processor FIFO Control Register

Reg−64H Transmit ATM Cell Processor Transmit Cell Counter Register

Reg−65H Transmit ATM Cell Processor Transmit Cell Counter Register

Reg−66H Transmit ATM Cell Processor Transmit Cell Counter Register

Reg−67H Transmit ATM Cell Processor Transmit Configuration Register

Reg−80H CY7C955 Test Control Register

REG−00H Master Reset / Type / Identity Register

BIT POSITION NAME READ/WRITE DEFAULT

7 RESET R/W 0

6 TYPE[2] R 0

5 TYPE[1] R 1

4 TYPE[0] R 1

3 ID[3] R 1

2 ID[2] R 1

1 ID[1] R 1

0 ID[0] R 1

(continued)

RESET

This is the master reset bit. Toggling this register has the same effect as toggling the RSTB pin, except that RSTB will reset all

registers to their default values, while writing a 1 to this register will only reset all other registers (but not itself) to their default

values. Leaving a 1 in this register puts the AX in power-down mode.

0: Normal mode.

1: Reset / Power Down Mode.

TYPE[2:0]

These bits differentiate the AX with other Cypress products.

ID[3:0]

These bits show th e revision number of the CY7C955.

19

PRELIMINARY

REG − 01H Master Configuration Register

BIT POSITION NAME READ/WRITE DEFAULT

7 Unused

6 AUTOFEBE R/W 1

5 AUTOLRDI R/W 1

4 AUTOPRDI R/W 1

3 TCAINV R/W 0

2 RCAINV R/W 0

1 RXDINV R/W 0

0 Unused

AUTOFEBE

This bit contro ls whet her Far End Block Error (FEBE) is t ransm it ted when l ine or path BIP err or is being de tected on the rec eiv e

data stream.

0: Do not generate line or path FEBE error in response to incoming li ne or path BIP error.

1: Generate line or path FEBE error in response to incoming line or pat h BIP error.

AUTOLRDI

This bit controls whether Li ne Remote Defect Indication (LRDI) is transmitted when an incoming alarm is being det ected.

0: Do not insert line RDI when line AIS , Loss of Frame (LOF) or Loss of Signal (LOS) is being detecte d.

1: Insert line RDI when line AIS, Los s of Frame (LOF) or Loss of Signal (LOS) is being detect ed.

AUTOPRDI

This bit controls whether STS Path Rem ote Def ect Indica tion (PRDI ) is transm it ted when an incomi ng alarm is being detected.

0: Do not insert STS path RDI when Loss of Signal (LO S), Loss of P oi nter (LOP), STS pat h AIS, Los s of F r ame (LOF), l ine

AIS, or Loss of Cell Delineation (LCD) is being detected.

1: Insert STS path RDI when Loss of Signal (LO S), Los s of Pointer (LOP), STS path AIS, Loss of Frame (LOF), line AIS, or

Loss of Cell Delineat ion (LCD) is being detected.

TCAINV

This bit controls the polarity of TCA.

0: TCA is active HIGH.

1: TCA is active LOW.

RCAINV

This bit controls the polarity of RCA.

0: RCA is active HIGH.

1: RCA is active LOW.

RXDINV

This bi t con tr o ls the in te r p r e ta tion of the differ ent ia l p ai r R X D.

0: Logical 1 is represe nted by RXD+ HIGH and RXD− LOW.

1: Logical 0 is represe nted by RXD+ HIGH and RXD− LOW.

CY7C955

20

PRELIMINARY

REG − 02H Master I nterrupt Register

BIT POSITION NAME READ/WRITE DEFAULT

7 TROOLI R

6 LCDI R

5 RDOOLI R

4 TACPI R

3 RACPI R

2 RPOPI R

1 RLOPI R

0 RSOPI R

TROOLI

This is the Transmit Reference Out Of Lock Interrupt. This bi t re sets when Reg−02H is being read.

1: TROOLV (Reg−06H, bit 3) has changed state since Reg−02H was last read.

0: TROOLV (Reg−06H, bit 3) has not changed state si nce Reg−02H was last read.

LCDI

This is the Loss of Cel l Delineation Int errupt. It has to be enab led by bit 7 of Reg−05H. This bit resets when Reg−02H is being

read.

1: Loss of cell delineation is entered or e xited since Reg−02H was last re ad.

0: There is no change in the loss of cell delineation state.

RDOOLI

This is the Receive Data Out Of Lock Interrupt. This bi t resets when Reg−02H is being read.

1: RDOOLV (Reg−07H, bit 3) has changed state since Reg−02H was last read.

0: RDOOLV (Reg−07H, bit 3) has not changed state since Reg−02H wa s last read.

TACPI

This is the Transmit ATM Cell Processor Interrupt. This bit resets when Reg−02H is being read. This register is a logical O R of

all the Transmit ATM Cell Processor (TACP) interrupts Reg−60H and 63H.

1: FOVRI, TSOCI, or TXPRTYI is HIGH.

0: FOVRI , TSOCI, and TXPRTYI are all LOW.

RACPI

This is the Receive ATM Cell Processor Interrupt. This bit r esets when Reg−02H is being read. This registe r i s a logical OR of

all the Receive ATM Cell Processo r (RACP) interrupts of Reg−51H.

1: OOCDI, CHCSI, or UHCSI is HIGH.

0: OOCDI, CHCSI, and UHCSI are all LOW.

RPOPI

This is the Receive Path Overhead Processor Interrupt. This bit resets when Reg−02H is being read. This register is a logical

OR of all the Receive Path Overhead Processor (RPOP) interrupts of Reg−31H.

1: PSLI, LOPI, PAISI, PRDII, BIPEI, or FEBEI is HIGH.

0: PSLI, LOPI, PAISI, PRDII, BIPEI, and FEBEI are all LOW.

RLOPI

This is the Receive Line Overhead Processor Interrupt. This bit resets when Reg−02H is being read. This register is a logical

OR of all the Receive Line Overhead Processor (RLOP) interrupts of Reg−19H.

1: FEB E I, B IP EI, LAISI, or R D II is HI GH .

0: FEBEI, BIPEI, LAISI, and RDII are all LOW.

RSOPI

This is the Receiv e Section Ov erhead Processor Inter rupt. This bit resets when Reg−02H is being read. Thi s register i s a logical

OR or all the Receive Secti on Overhead Processor (RSOP) interrupts or Reg−11H.

1: BIPEI, LOSI, LOFI, or OOFI is HIGH.

0: BIPEI, LOSI, LOFI, and OOFI are all LO W.

CY7C955

21

PRELIMINARY

REG − 04H Master Clock Monitor Register

BIT POSITION NAME READ/WRITE DEFAULT

7 RXDOD R/W 0

6 XORTXC R/W 0

5 Unused

4 Unused

3 RRCLKA R

2 TRCLKA R

1 RCLKA R

0 TCLKA R

RXDOD

This bit is used to turn off the RXDO output in case it is not needed. Thi s helps save power and reduce power supply noise.

1: RXDO output is disabled.

0: RXDO is the retimed buffered output of RXDXORTXC.

XORTXC is used to invert the defaul t-on status of the TXC output.

1: TXC is disabled if RATE0 is LOW, and TXC is a 155.52-MHz clock if RATE0 is HIGH.

0: TXC is a 51.84-MHz clock if RATE0 is LOW, and TXC is disabled if RATE0 is HIGH.

RRCLKA

This bit can be read to check for RRCLK transitions ; when HIGH, thi s bit stays HIGH until Reg −04H is being read.

1: RRCLK+ has a LOW to HIGH transiti on since this register was last read.

0: RRCLK+ has no LOW to HIGH transitions since this regis ter was last read.

TRCLKA

This bit can be read to check for TRCLK transitions ; when HI GH, thi s bit stays HIGH until Reg−04H is being read.

1: TRCLK+ has a LOW to HIGH transition since this register was last read.

0: TRCLK+ has no LOW to HIGH transitions since this register was last read.

RCLKA

This bit can be read to check for RCLK transitions; when HIGH, thi s bit stays HIGH until Reg −04H is being read.

1: RCLK has a LOW to HIGH transit ion since this regist er was last read.

0: RCLK has no LOW to HIGH transitions since this register was last read.

TCLKA

This bit can be read to check for TCLK transitions; when HIGH, this bit stays HIGH unti l Reg−04H is being read.

1: TRCLK+ has a LOW to HIGH transition since this register was last read.

0: TRCLK+ has no LOW to HIGH transitions since this register was last read.

CY7C955

22

PRELIMINARY

REG − 05H Master Control Register

BIT POSITION NAME READ/WRITE DEFAULT

7 LCDE R/W 0

6 LCDV R

5 FIXPTR R/W 1

4 Unused

3 Unused

2 LLE R/W 0

1 DLE R/W 0

0 LOOPT R/W 0

LCDE

This bit enables a change in the Loss of Cell Delineation state to generate an interrupt on pin INTB.

0: INTB will not be affected by a transition in LCDV (Reg−05H, bit 6).

1: INTB will go LOW when there is a transition in LCDV (Reg−05H, bit 6).

LCDV

This bit shows the present loss of cell del ineation state of the Receive ATM Cell overhead Processo r (RACP).

0: RACP is in SYNC state f or l onger than 4 ms.

1: RACP is out of cell delineation for more than 4 ms and there are no detected LOS, LOP, Path AIS, and Line AIS.

FIXPTR

This bit controls the operation of the transmit payload pointer adjustment function.

0: The setting in Reg−41H can con trol the payload point er adjustment operat ions.

1: The transmit payload pointer is fixed at 522.

LLE

This bit controls the li ne loop-back path of the CY7C955; DLE and LLE cannot be both set to 1.

0: Normal operation.

1: RXD+ and RXD− are connected to TXD+ and TXD− internally.

DLE

This bit controls the diagnostic loop-back path of the CY7C955; DLE and LLE cannot be both set to 1.

0: Normal operation.

1: The transmitted data steam is being looped bac k to the received data stream.

LOOPT

This bit enables loop timing.

0: The transmit ted data stream derives its cloc k from TRCLK. The cloc k to use depends on the setting of TREFSEL

(Reg−06H, bit 0) and on the level of pins TBYP and RATE0.

1: The transmitted dat a stream derives its clock from RRCLK if the clock and data recovery function of the receiver is not

active and f rom RXD if the cl ock and data recovery function is activ e. Again, the clock to use in RRCLK depends on

the setting of RREFSEL (Reg−07H), RBYP, and RATE0.

CY7C955

23

PRELIMINARY

REG − 06H Transmit Clock Synthesis Contr ol Regi ster

BIT POSITION NAME READ/WRITE DEFAULT

7 Unused

6 Unused

5 Unused

4 Unused

3 TROOLV R

2 Unused

1 TROOLE R/W 0

0 TREFSEL R/W 0

TROOLV

This bit is the Transmit Reference Out Of Lock Status register.

0: The divided-do wn synthesized tr ansmit clock is within 2930 ppm of TRCLK or RRCLK (in loop ti ming mode).

1: The divided-do w n synthesized transmit clock is not with in 2930 ppm of TRCLK or RRCLK (in loop timing mode).

TROOLE

This bit is the Transmit Reference Out Of Lock Interrupt Enable register.

0: INTB, the interrupt pin, will not be aff ected by transmit out of lock.

1: INTB, the interrupt pin, will pull LOW when there is a state change of TROOLV.

TREFSEL

This bit is the Transmit Reference Select. This bit is ignored in transmit bypass mode (TBYP = 1).

0: TRCLK expects a 19.44-MHz reference clock. If RATE0 is HIGH (155.52 Mbps, STS−3c/STM−1), the transmit PLL will

multiply the TRCLK frequency by 8 times. If RATE0 is LOW (51.84 Mbps, STS−1), the transmit PLL will multiply the

TRCLK frequency by 8/ 3 times to clock the transmitter .

1: TRCLK expects a 6.48-MHz reference clock. If RATE0 is HIGH (155.52 Mbps, STS−3c/STM−1), the transmit PLL will

multiply the TRCLK frequency by 24 times. If RATE0 is LOW (51.84 Mbps, STS−1), the t ransm it P LL will multi ply the

TRCLK frequency by 8 tim es to clock the transmit ter.

CY7C955

24

PRELIMINARY

REG − 07H Recei ve Clock Synthesis Control Regi ster

BIT POSITION NAME READ/WRITE DEFAULT

7 Unused

6 Unused

5 Unused

4 Unused

3 RROOLV R

2 Unused

1 RROOLE R/W 0

0 RREFSEL R/W 0

RROOLV

This bit is the Receive Reference Out Of Lock Status register.

0: The divided-down reco vered clock is within 2930 ppm of RRCLK, and there is at least one tran sition on RXD during

the last 80 bit-periods.

1: The divided-down recovered clock is not within 2930 ppm of RRCLK, or there are no trans it ions on RXD within the last

80 bit-periods.

RROOLE

This bit is the Receive Reference Out Of Lock Interrupt Enabl e regi ster.

0: INTB, the interrupt pin, will not be aff ected by receiv er out of lock.

1: INTB, the interrupt pin, will go LOW when there is a state change of RROOLV.

RREFSEL

This bit is the Receiver Reference Select. This bit is ignored in receiver bypass mode (RBYP = 1).

0: RRCLK expects a 19.44-MHz reference clock. If RATE0 is HIGH (155.52 Mbps, STS−3c/STM−1), the recovered clock

is divided down 8 times before comparing with RRCLK. If RATE0 is LOW (51.84 Mbps, STS−1), the recovered clock is

divided down 3/8 times before comparing with RRCLK.

1: RRCLK expects a 6.480-MHz reference clock. If RATE0 is HIGH (155.52 Mbps, STS−3c/STM−1), the recovered clock

is divided down 24 times before comparing wit h RRCLK. If RATE0 is LOW (51.84 Mbps , STS−1), the recovered clock is

divided down 8 times before comparing with RRCLK.

CY7C955

25

PRELIMINARY

REG − 10H Recei ve Section Overhead Processor Cont rol Register

BIT POSITION NAME READ/WRITE DEFAULT

7 Unused

6 DDS R/W 0

5 FOOF W 0

4 Unused

3 BIPEE R/W 0

2 LOSE R/W 0

1 LOFE R/W 0

0 OOFE R/W 0

DDS

This bit controls whether SONET descrambling is done on the receive data stream.

0: Descramb li ng is performed.

1: Descramb li ng is not performed.

FOOF

This bit can be used to manually put the Receive Secti on Overhead Processor out of frame.

0: No action.

1: The Receive Section Overhead Proce ssor will detect an out of frame alarm at the next frame boundary.

BIPEE

This bit controls whether a section BIP−8 error (B1) gener ates an interrupt.

0: The interrupt pin, INTB, is not affected by section BIP−8 errors .

1: The interrupt pin, INTB, will go LOW upon receivi ng a section BIP−8 error.

LOSE

This bit controls whether a Loss of Signal alarm generates an interrupt.

0: The interrupt pin, INTB, is not affected by the loss of signal alarm.

1: The interrupt pin, INTB, will go LOW upon receiving a loss of signal alarm.

LOFE

This bit controls whether a Loss of Frame al arm generates an interrupt.

0: The interrupt pin, INTB, is not affected by the lo ss of frame alarm.

1: The interrupt pin, INTB, will go LOW upon receivi ng a loss of frame alarm.

OOFE

This bit controls whether an Out of Frame alarm generates an interrupt.

0: The interrupt pin, INTB, is not affected by the out of frame alarm.

1: The interrupt pin, INTB, will go LOW upon receiving an out of frame alarm.

CY7C955

26

PRELIMINARY

REG − 11H Recei ve Section Overhead Processor Sta tus Register

BIT POSITION NAME READ/WRITE DEFAULT

7 Unused

6 BIPEI R

5 LOSI R

4 LOFI R

3 OOFI R

2 LOSV R

1 LOFV R

0 OOFV R

BIPEI

This is the section BIP −8 interrupt bit. This bit resets when Reg−11H is being read.

0: No section BIP−8 error is det ected since Reg−11H was last read .

1: Section BIP−8 error is det ected since Reg−11H was last read.

LOSI

This is the Loss of Signal (LOS) interrupt bit. This bit resets when Reg−11H is being read.

0: No change in the LOS status.

1: There is a change in the LOS status since Reg−11H was last read.

LOFI

This is the Loss of Frame (LOF) interrupt bit. This bit resets when Reg−11H is being read.

0: No change in the LOF status .

1: There is a change in the LOF status since Reg−11H was last read.

OOFI

This is the Out of Frame (OOF) interrupt bit. This bit resets when Reg−11H is being read.

0: No change in the OOF status.

1: There is a change in the OOF status since Reg−11H was last read.

LOSV

This bit shows the Loss of Signal (LOS) status of the CY7C955.

0: The Receive Section Overhead Processor is not in a loss of signal st ate.

1: The Receive Section Overhead Processor is in a loss of signal state.

LOFV

This bit shows the Loss of Frame (LOF) status of the CY7C955.

0: The Receive Section Overhead Processor is not in a Loss of Frame state.

1: The Receive Section Overhead Processor is in a Loss of Frame state. LOF is declared when OOF has lasted for more