Datasheet CY7C1316V18-200BZC, CY7C1316V18-167BZC, CY7C1320V18-300BZC, CY7C1320V18-250BZC, CY7C1320V18-200BZC Datasheet (Cypress Semiconductor)

...

PRELIMINARY

18-Mb DDR-II SRAM Two-word

Burst Architecture

CY7C1316V18

CY7C1318V18

CY7C1320V18

Cypress Semiconductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

Document #: 38-05177 Rev. *A Revised July 31, 2002

Features

• 18-Mb density (2M x 8, 1M x 18, 512K x 36)

—Supports concurrent transactions

• 250-MHz clock for high vandwidth

• Two-word burst for reducing address bus frequency

• Double Data Rate (DDR) interfaces (data t ransferred at

500 MHz) @ 250 MHz

• Two input cloc ks (K and K

) for precise DDR timing

—SRAM uses rising edges only

• Two output clocks (C and C

) accounts for clock skew

and flight time mismatches

• Echo clocks (CQ and CQ

) simplify data ca pture in high

speed systems

• Synchronous internally self-timed writes

• 1.8V core power supply with HSTL inputs and outputs

• Variable drive HSTL output buffers

• Expanded HSTL output voltage (1.4V–V

DD

)

• 13x15 mm 1.0-mm pit ch fBGA p ackage, 1 65 ball (1 1x1 5

matrix)

•JTAG interface

• On-chip Delay Lock Loop (DLL)

Configurations

CY7C1316V18 – 2M x 8

CY7C1318V18 – 1M x 18

CY7C1320V18 – 512K x 36

Functional Description

The CY7C1316V18/CY7C1318V18/CY7C1320V18 are 1.8V

Synchronous Pipelined SRAM equipped with DDR-II (Double

Data Rate) architecture. The DDR-II consists of an SRAM core

with advanced synchronous peripheral circuitry and a 1-bit

burst counter. Addresses for Read and Write are latched on

alternate rising edges of the input (K) clo ck.Write data is regi stered on the rising edges of both K and K

. Read data is d riven

on the rising edges of C and C

if provided, or on the rising ed ge

of K and K

if C/C are not provided. Each address location is

associated with two 8-bit words in the case of CY7C1316V18

that burst sequentially into or out of the device. The burst

counter always starts with a “0” internally in the case of

CY7C1316V18. On CY7C1318V18 and CY7C1320V18, the

burst counter takes in the least significant bit of the external

address and bursts two 18-bit words in the case of

CY7C1318V18 and two 36-bit words in the case of

CY7C1320V18 sequentially into or out of the device.

Asynchronous inputs include impedance match (ZQ).

Synchronous dat a outpu ts (Q, shari ng the sa me phy sica l pins

as the data in puts D) are ti ghtly matched to th e two output echo

clocks CQ/CQ

, eliminat ing the nee d for separ ately ca pturing

data from each individual DDR SRAM in the system d esign.

Output data cl ocks (C/C

) enable maximum system clocking

and data synchr onization flexibili ty.

All synchronous inp ut s pa ss thro ugh inp ut regis ters c ont rolled

by the K or K

input clocks. All data o utputs pa ss through output

registers controlled by the C or C

input clocks. Writes are

conducted with on-chip synchronous self-timed writ e circuitry.

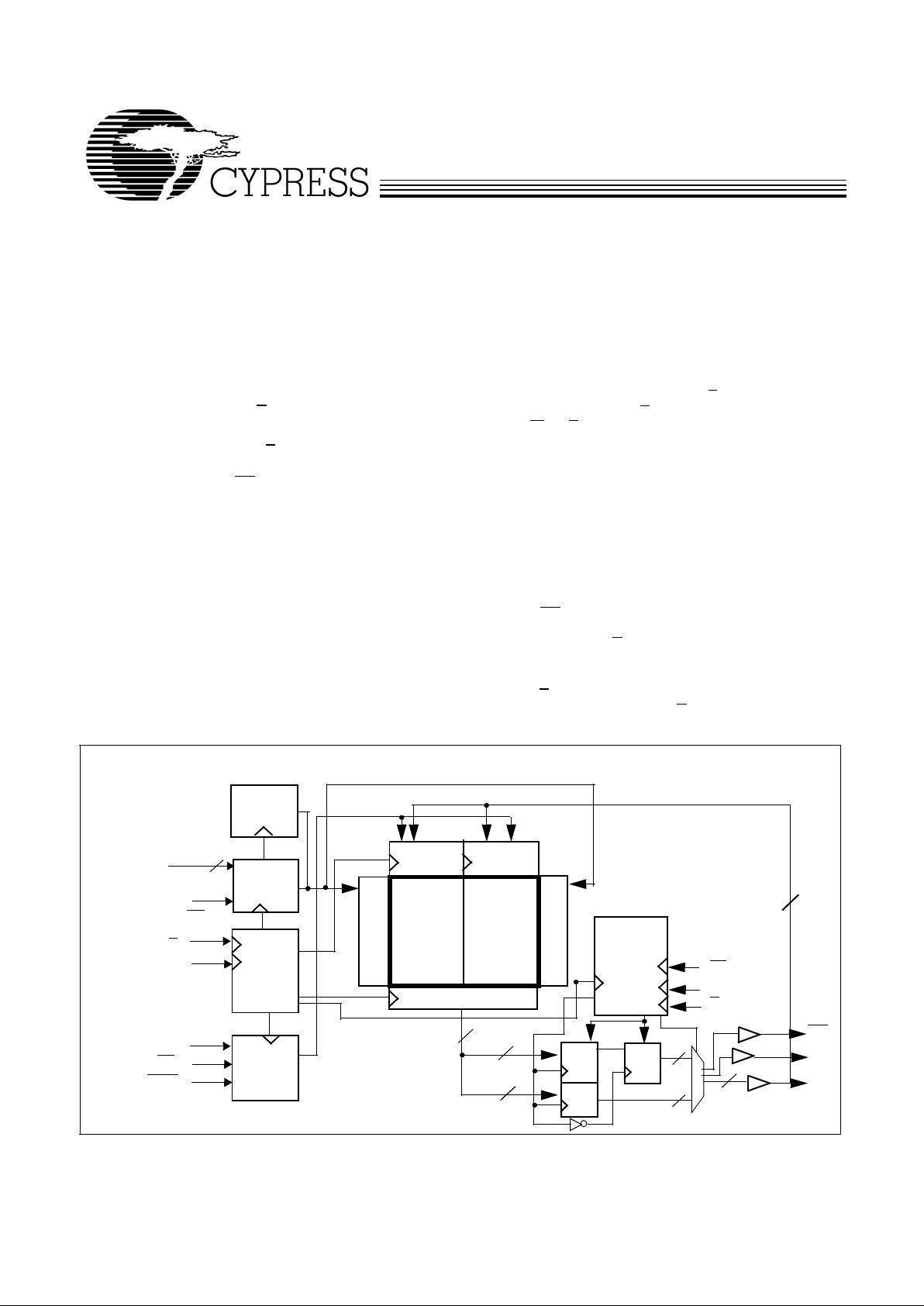

Logic Block Diagram (CY7C1316V18)

CLK

A

(19:0)

Gen.

K

K

Control

Logic

Address

Register

Read Add. Decode

Read Data Reg.

R/W

DQ

[7:0]

Output

Logic

Reg.

Reg.

Reg.

8

8

16

8

BWS

[1:0]

V

REF

Write Add. Decode

8

C

C

8

LD

Control

Burst

Logic

20

1M x 8 Array

1M x 8 Array

Write

Reg

Write

Reg

CQ

CQ

R/W

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 2 of 24

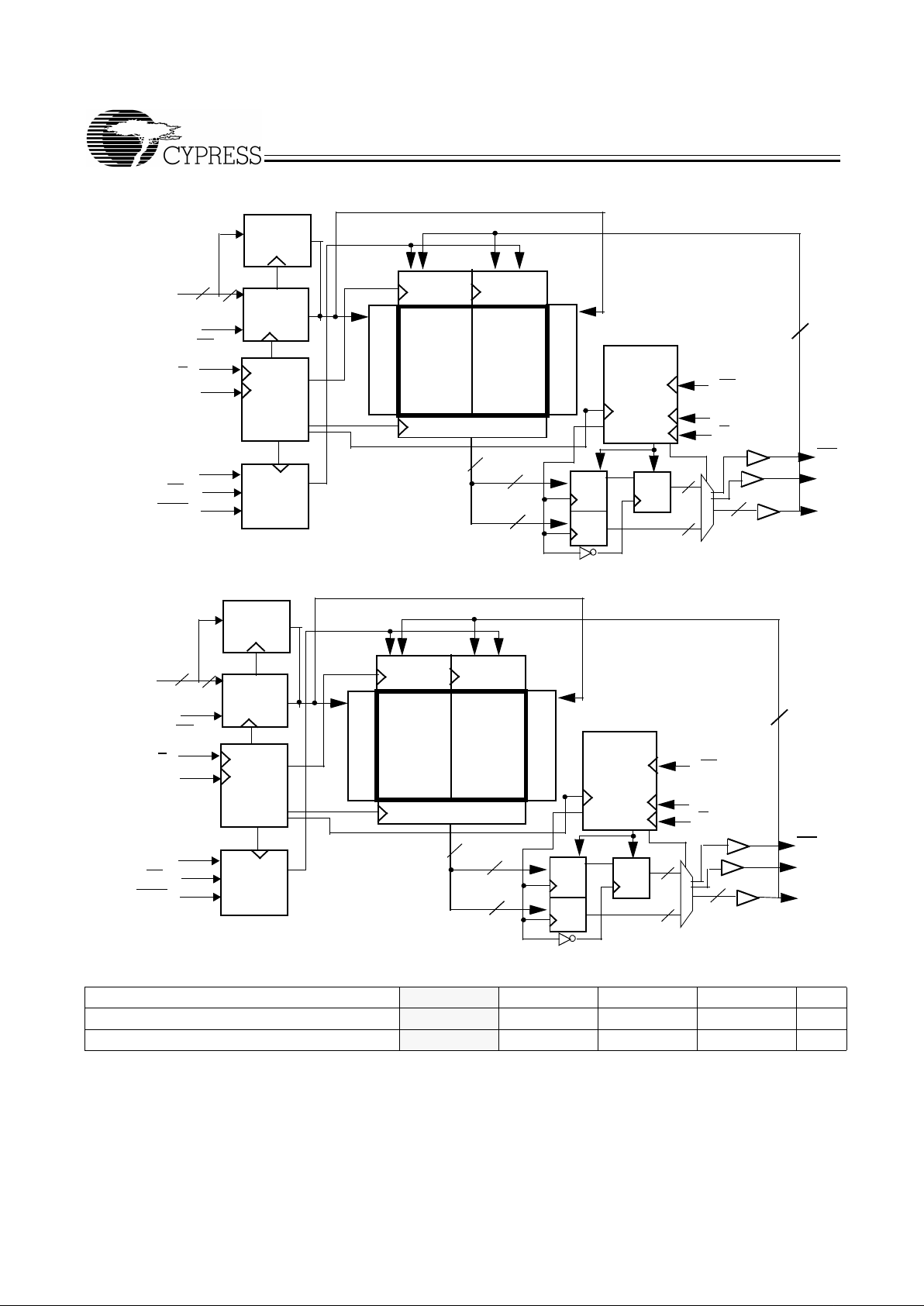

Logic Block Diagram (CY7C1318V18)

CLK

A

(19:0)

Gen.

K

K

Control

Logic

Address

Register

Read Add. Decode

Read Data Reg.

R/W

DQ

[17:0]

Output

Logic

Reg.

Reg.

Reg.

18

18

36

18

BWS

[1:0]

V

REF

Write Add. Decode

18

20

C

C

18

LD

Control

Burst

Logic

A

(0)

A

(19:1)

19

512K x 18 Array

512K x 18 Array

Write

Reg

Write

Reg

CQ

CQ

R/W

Logic Block Diagram (CY7C1320V18)

CLK

A

(18:0)

Gen.

K

K

Control

Logic

Address

Register

Read Add. Decode

Read Data Reg.

R/W

DQ

[35:0]

Output

Logic

Reg.

Reg.

Reg.

72

36

144

36

BWS

[3:0]

V

REF

Write Add. Decode

72

19

C

C

36

LD

Control

Burst

Logic

A

(0)

A

(18:1)

18

256K x 36 Array

256K x 36 Array

Write

Reg

Write

Reg

CQ

CQ

36

R/W

Selection Guide

[1]

300 MHz 250 MHz 200 MHz 167 MHz Unit

Maximum Operating Frequency 300 250 200 167 MHz

Maximum Operating Current TBD TBD TBD TBD mA

Note:

1. Shaded cells indicate advanced information.

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 3 of 24

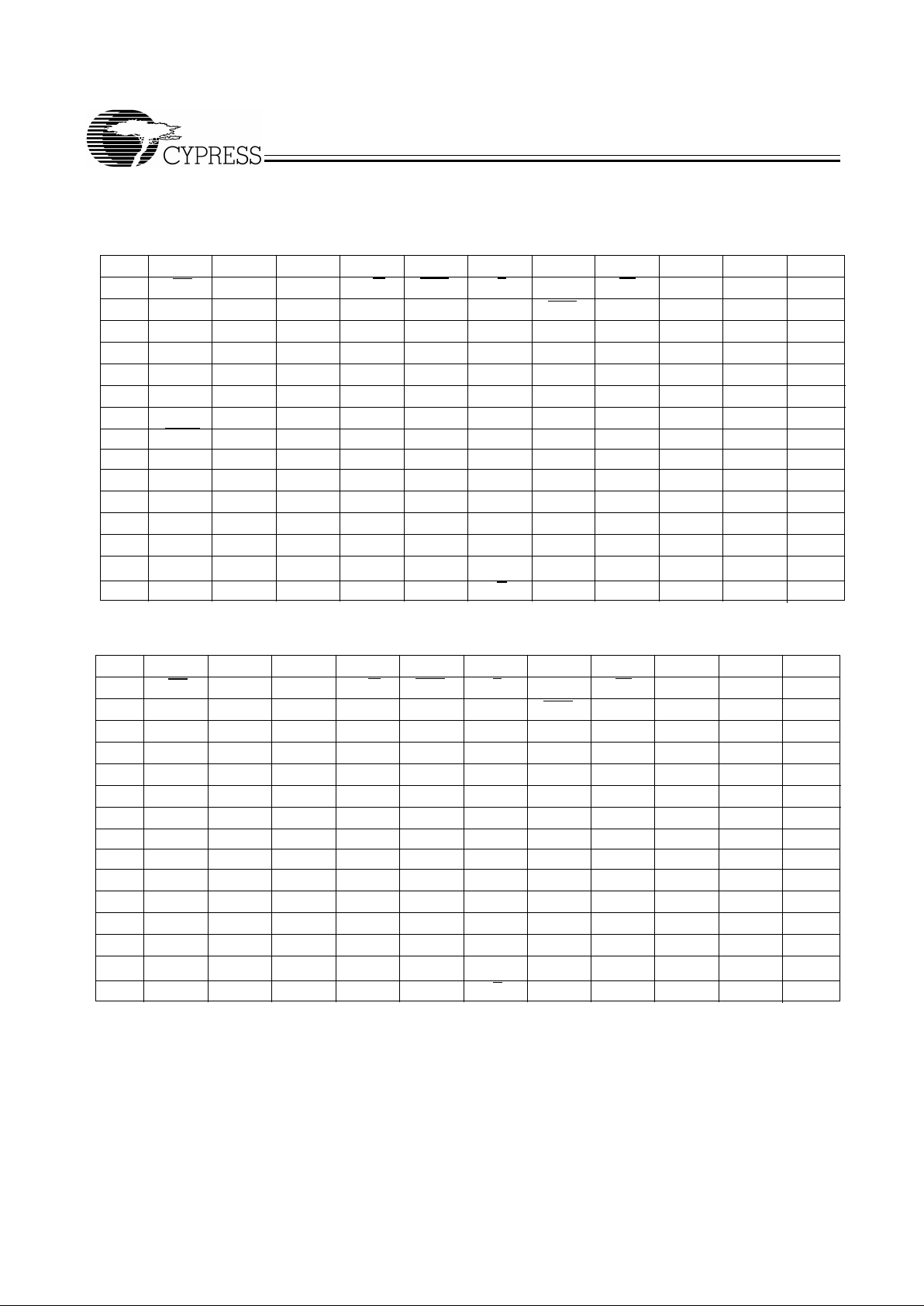

Pin Configurations

CY7C1316V18 (2M x 8) - 11 x 15 FBGA

2345671

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

A

CQ

NC

NC

NC

NC

DOFF

NC

V

SS

/72M A BWS

1

KR/W

NC

NC NC

NC

NC

NC

TDO

NC

NC

NC

NC

NC

NC

TCK

NC

NC

A NC K BWS

0

V

SS

AAA

NC V

SS

V

SS

V

SS

V

SS

V

DD

A

V

SS

V

SS

V

SS

V

DD

DQ4

NC

V

DDQ

NC

NC

NC

NC

DQ7

A

V

DDQ

V

SS

V

DDQ

V

DD

V

DD

DQ5 V

DDQ

V

DD

V

DDQ

V

DD

V

DDQ

V

DD

V

SS

V

DD

V

DDQ

V

DDQ

V

SS

V

SS

V

SS

V

SS

A

AC

V

SS

A

A

A

NC V

SS

NC V

SS

NC

NC

V

REF

V

SS

V

DD

V

SS

V

SS

A

V

SS

C

NC

DQ6

NC

NC

NC

V

DD

A

891011

NC

AV

SS

/36MLD

CQ

A NC NC DQ3

V

SS

NC NC NC

NC

V

SS

NC

DQ2

NC

NC

NC

V

REF

NC

NC

V

DDQ

NC

V

DDQ

NC NC

V

DDQ

V

DDQ

V

DDQ

NCV

DDQ

NC

DQ1

NC

V

DDQ

V

DDQ

NC

V

SS

NC NC

NC

TDITMS

V

SS

A

NC

A

NC

NC

NC

ZQ

NC

DQ0

NC

NC

NC

NC

A

CY7C1318V18 (1M x 18) - 11 x 15 FBGA

234 5671

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

A

CQ

NC

NC

NC

NC

DOFF

NC

V

SS

/72M A BWS

1

KR/W

NC

DQ9

NC

NC

NC

NC

TDO

NC

NC

NC

NC

NC

NC

TCK

NC

NC

A NC

K

BWS

0

V

SS

AA0A

DQ10 V

SS

V

SS

V

SS

V

SS

V

DD

A

V

SS

V

SS

V

SS

V

DD

DQ11

NC

V

DDQ

NC

DQ14

NC

DQ16

DQ17

A

V

DDQ

V

SS

V

DDQ

V

DD

V

DD

DQ13 V

DDQ

V

DD

V

DDQ

V

DD

V

DDQ

V

DD

V

SS

V

DD

V

DDQ

V

DDQ

V

SS

V

SS

V

SS

V

SS

A

AC

V

SS

A

A

A

NC V

SS

NC V

SS

DQ12

NC

V

REF

V

SS

V

DD

V

SS

V

SS

A

V

SS

C

NC

DQ15

NC

NC

NC

V

DD

A

891011

DQ0

AV

SS

/36MLD

CQ

A NC

NC

DQ8

V

SS

NC DQ7 NC

NC

V

SS

NC

DQ6

NC

NC

NC

V

REF

NC

DQ3

V

DDQ

NC

V

DDQ

NC DQ5

V

DDQ

V

DDQ

V

DDQ

NCV

DDQ

NC

DQ4

NC

V

DDQ

V

DDQ

NC

V

SS

NC NC

NC

TDITMS

V

SS

A

NC

A

NC

NC

NC

ZQ

NC

DQ2

NC

DQ1

NC

NC

A

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 4 of 24

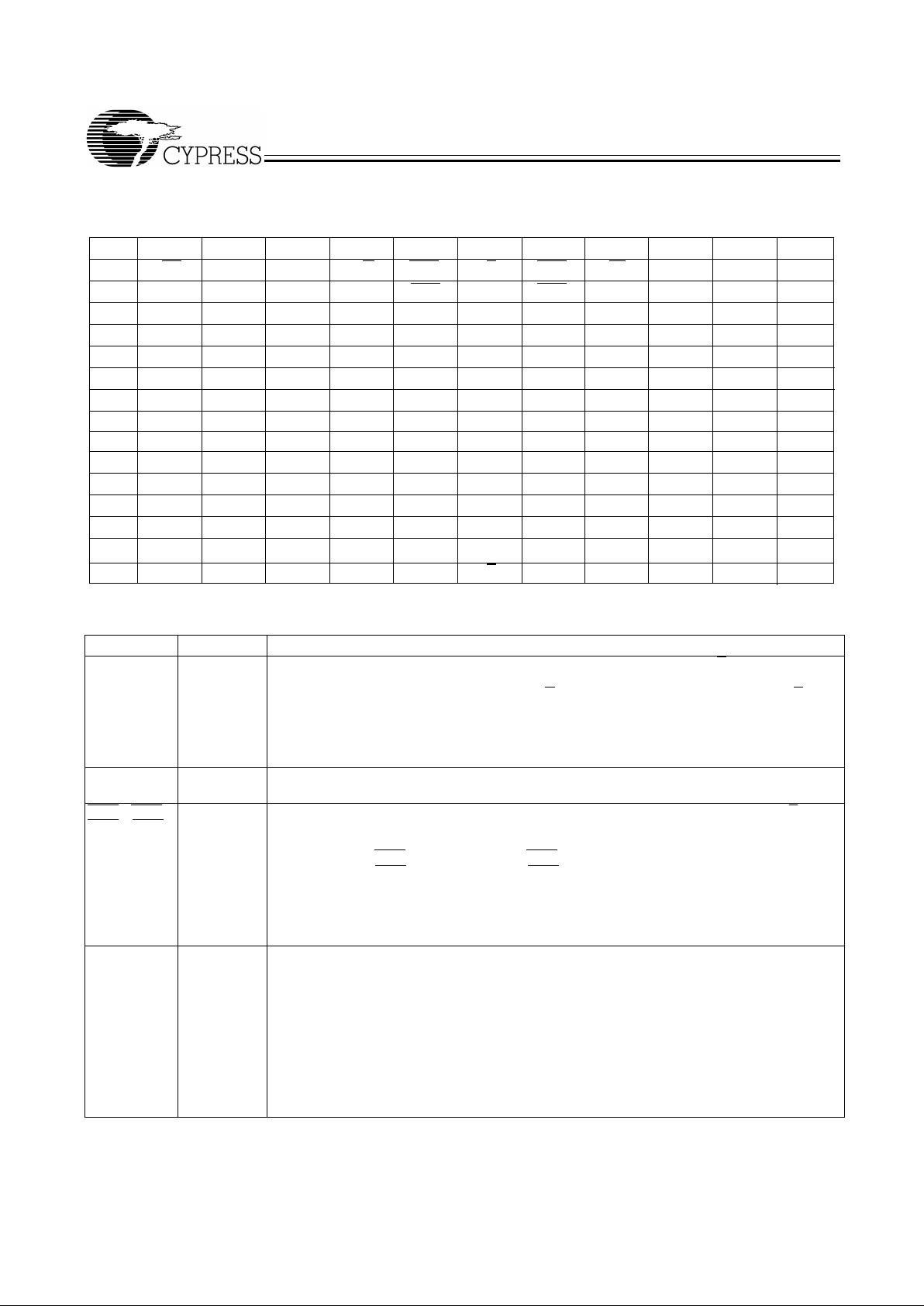

Pin Configurations (continued)

CY7C1320V18 (512K x 36) - 11 x 15 FBGA

2345671

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

A

CQ

NC

NC

NC

NC

DOFF

NC

V

SS

/144M NC/36M BWS

2

KR/W BWS

1

DQ27

DQ18

NC

NC

NC

TDO

NC

NC

DQ31

NC

NC

NC

TCK

NC

DQ28

A BWS

3

K

BWS

0

V

SS

AA0A

DQ19 V

SS

V

SS

V

SS

V

SS

V

DD

A

V

SS

V

SS

V

SS

V

DD

DQ20

DQ21

V

DDQ

DQ32

DQ23

DQ34

DQ25

DQ26

A

V

DDQ

V

SS

V

DDQ

V

DD

V

DD

DQ22 V

DDQ

V

DD

V

DDQ

V

DD

V

DDQ

V

DD

V

SS

V

DD

V

DDQ

V

DDQ

V

SS

V

SS

V

SS

V

SS

A

AC

V

SS

A

A

A

DQ29 V

SS

NC V

SS

DQ30

NC

V

REF

V

SS

V

DD

V

SS

V

SS

A

V

SS

C

NC

DQ33

NC

DQ35

DQ24

V

DD

A

891011

DQ0

AV

SS

/72MLD CQ

A NC

NC

DQ8

V

SS

NC DQ17 DQ7

NC

V

SS

NC

DQ6

DQ14

NC

NC

V

REF

NC

DQ3

V

DDQ

NC

V

DDQ

NC DQ5

V

DDQ

V

DDQ

V

DDQ

DQ4V

DDQ

NC

DQ13

NC

V

DDQ

V

DDQ

NC

V

SS

NC DQ1

NC

TDITMS

V

SS

A

NC

A

DQ16

DQ15

NC

ZQ

DQ12

DQ2

DQ10

DQ11

DQ9

NC

A

Pin Definitions

Pin Name I/O Pin Description

DQ

[x:0]

Input/OutputSynchronous

Data input/Output signals. In puts are sampled o n the rising edge of K and K clocks du ring valid

write operations. These pins driv e out the req uested dat a during a Read operatio n. Valid data is

driven out on the rising edge of both the C an d C

clocks during Read operations or K an d K when

in single clock mode. When the Read port is deselected, Q

[x:0]

are automatically three-stated.

CY7C1316V18 − DQ

[7:0]

CY7C1318V18 − DQ

[17:0]

CY7C1320V18− DQ

[35:0]

LD Input-

Synchronous

Synchronous load. This input is brought LOW when a bus cycle sequ ence is to be defin ed. This

definition includes address and read/writ e directio n. All transact ions opera te on a burs t of 2 data.

BWS0, BWS1,

BWS2, BWS

3

Input-

Synchronous

Byte Write Select 0, 1, 2, and 3 − active LOW. Sampl ed on the rising e dge of the K and K cl ocks

during write operations. Used to select which byte is written into the device during the current

portion of the write operations. Bytes not written remain unaltered.

CY7C1311V18 − BWS

0

controls D

[3:0]

and BWS1 controls D

[7:4]

.

CY7C1313V18 − BWS0 controls D

[8:0]

and BWS1 controls D

[17:9].

CY7C1315V18 − BWS0 controls D

[8:0]

, BWS1 controls D

[17:9]

, BWS2 controls D

[26:18]

and BWS3

controls D

[35:27]

.

All the byte writes are sampled on the same edge as the data. Deselecting a Byte Write Select

will cause the corresponding byte of data to be ignored and not written into the device.

A, A0 Input-

Synchronous

Address inputs. These address inputs are multiplexed for both Read and Write operations.

Internally, the device is organized as 2M x 8 (2 arrays each of 1M x 8) for CY7C131 6V1 8, 1M x

18 (2 arrays each of 512 K x 18 ) for CY 7C1 318 V18 a nd 5 12K x 36 (2 a rray s ea ch of 25 6K x 36 )

for CY7C1320V18.

CY7C1316V18 – Since the least significant bit of the address internally is a “0,” only 20 external

address inputs are needed to access the entire memory array.

CY7C1318V18 – A0 is the input to the burs t cou nter. These are incre me nted in a linear fas hi on

internally. 20 address inputs are nee ded to acces s the entire me mo ry array.

CY7C1320V18 – A0 is the input to the burs t cou nter. These are incre me nted in a linear fas hi on

internally. 19 address input s are nee ded to ac c ess th e en tire mem ory arra y. All the dres s inputs

are ignored when the appropriate port is deselected.

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 5 of 24

R/W Input-

Synchronous

Synchronous Read/Write Inpu t. When LD is LOW , this input designates the access type (READ

when R/W

is HIGH, WRITE when R/W is low) for l oaded address . R/W must meet the set-up a nd

hold times around edge of K.

C Input-

Clock

Positive Output Clock Input. C is used in conjunction with C to clock out the Read data from

the device. C and C

can be used together to deskew the flight times of various devices on the

board back to the controller. See application example for further details.

C Input-

Clock

Negative Output Clock Input. C is used in conjunction with C to clock out the Read data from

the device. C and C

can be used together to deskew the flight times of various devices on the

board back to the controller. See application example for further details.

K Input-

Clock

Positive Input Clock Input. The rising edge of K is used to capture synchronous inputs to the

device and to drive out data through Q

[x:0]

when in single clock m ode . All ac c ess es are in iti ate d

on the rising edge of K.

K Input-

Clock

Negative Input Clock Input. K i s used to capture sync hronous data being pre sented to the device

and to drive out data through Q

[x:0]

when in single clock mode.

CQ Echo Clock CQ is referenced with respect to C. This is a free running clock and is synchronized to the

output clock of the QDR

TM

-II. In the single clock mode, CQ is generated with respect to K. The

timings for the echo clocks are shown in the AC timing table.

CQ Echo Clock CQ is referenced with respect to C. This is a free running clock and is synchronized to the

output clock of the QDR

TM

-II. In the single clock mode, CQ is generated with respect to K. The

timings for the echo clocks are shown in the AC timing table.

ZQ Input Output Impedance Matching Input. This input is used to tune the device ou tputs t o the sys tem

data bus impedance. Q

[x:0]

output impedance are set to 0.2 x RQ, where RQ is a resistor

connected between ZQ and ground. Alternatel y , this pi n can be connected directly to V

DD

, which

enables the minimum impedance mode. This pin cannot be connected directly to GND or left

unconnected.

DOFF Input DLL Turn Off. Connecting this pin to ground will turn off the DLL inside the device. The timings

in the DLL turned off operation will be different from those listed in this data sheet. More details

on this operation can be found in the application note, “DLL Operation in the QDR

TM

-II.”

TDO Output TDO for JTAG.

TCK Input TCK pin for JTAG.

TDI Input TDI pin for JTAG.

TMS Input TMS pin for JTAG.

NC Input No connects. Can be tied to any voltage level.

NC/36M Input Address expansion for 36M. This is not connected to the die.

NC/72M Input Address expansion for 72M. This is not connected to the die an d so can be tied to any volt age

level.

VSS/72M Input Address expansion for 72M. This must be tied LOW on the 18M SRAM.

VSS/144M Input Address expansion for 144M. This must be tied LOW on the 18M SRAM.

VSS/288M Input Address expansion for 288M. This must be tied LOW on the 18M SRAM.

V

REF

Input-

Reference

Reference V oltage Input. S tatic input used to set the reference level for HSTL inputs and Outputs

as well as A/C measurement points.

V

DD

Power Supply Power supply inputs to the core of the device. Should be connected to 1.8V power supply.

V

SS

Ground Ground for the device. Should be connected to ground of the system.

V

DDQ

Power Supply Power supply inputs for the outp uts of the device. Should be co nnected to 1.5V power sup ply .

Pin Definitions (continued)

Pin Name I/O Pin Description

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 6 of 24

Introduction

Functional Overview

The CY7C1316V18/CY7C1318V18/CY7C1320V18 are

synchronous pipelined Burst SRAMs equipped with a DDR

interface.

Accesses are initiated on the Positive Input Clock (K). All

synchronous input ti ming is refe renced from the rising edge of

the input clocks (K and K

) and all output timing is referenced

to the output clocks (C/C

or K/K when in single clock mode).

All synchronous data inputs (D

[x:0]

) pass through input

registers controlled by the input clocks (K and K

). All

synchronous data outputs (Q

[x:0]

) pass through output

registers control led by the rising edge of the output c locks (C/C

or K/K when in single-clock mode).

All synchronous control (R/W, LD, BWS

[0:X]

) inputs pass

through input registers controlled by the rising edge of the

input clock (K ).

The following descriptions take CY7C1318V18 as an

example. However, the same is true for the other DDR-II

SRAMs, CY7C1316V18 and CY7C1320V18.

These chips utilize a Delay Lock Loop (DLL) that is designed

to function betwee n 80 MH z and the specifie d maximum clock

frequency . The DLL may be disabled by applying gro und to the

DOFF

pin.

Read Operations

Accesses are completed in a burst of two sequential 18-bit

data words. Read operations are in itiated by assertin g R/W

HIGH and LD LOW at the rising edge of the Positive Input

Clock (K). The address presented to Address inputs is stored

in the Read address registe r and the least s ignificant bit of the

address is presented to the burst counter. The burst counter

increments th e add res s in a lin ea r fashion. Following the next

K clock rise the corresponding 18-bit word of data from this

address location is driven onto the Q

[17:0]

using C as the output

timing reference. On the subs equent rising edge o f C th e next

18-bit data wo rd from the address loca tion gen erated by th e

burst counter is driven onto the Q

[17:0]

. The requested dat a will

be valid 0.35 ns from the rising edge of the output clock (C or

C

, 250-MHz device). In order to maintain the internal logic,

each read access must be allowed to complete. Read

accesses can be initiated on every rising edge of the Positive

Input Clock (K).

When the read port is dese lected, the CY7C1318V18 wil l fi rst

complete the pend ing read transa ctions. Synchrono us internal

circuitry will autom atically th ree-stat e the o utputs fol lowing the

next rising edge of the Positive Output Clock (C). This will

allow for a seamless transition between devices without the

insertion of wait states in a depth expanded memory.

Write Operations

Write operations are initiated by asserting R/W

LOW and LD

LOW at the rising edge of the Positive Input Clock (K). The

address presented to Address inputs is stored in the Write

address register and the least significant bit of the address is

presented to the burst counter. The burst counter increments

the address in a linear fashion. On the following K clock rise

the data presented to D

[17:0]

is latched and stored into the

18-bit Write Da ta regi ster provi ded BWS

[1:0]

are both asserted

active. On the subsequent rising edge of the Negative Input

Clock (K

) the information presented to D

[17:0]

is also stored

into the Write Data Register provided BWS

[1:0]

are both

asserted active. The 36 bits of data are then written into the

memory array at the specified location. Write accesses can be

initiated on every rising edge of the Positive Input Clock (K).

Doing so will pipeline the data flow such that 18 bits of data

can be transferred into the device on every rising edge of the

input clocks (K and K

).

When deselected, the write port will ignore all inputs after the

pending Write operations have been completed.

Byte Write Operations

Byte Write op erati on s a re sup po rted by the CY7C1318V18. A

write operation is initi ated as describ ed in the Write Operation

section above. The bytes that are written are determined by

BWS

0

and BWS1 which are sampled with each set of 18-bit

data word. Asserting the appropriate Byte Write Select input

during the data portion of a write will allow the data being

presented to be latched and written into the device.

Deasserting the By te Write S elect input during the data porti on

of a write will allow the data stored in the device for that byte

to remain unaltered. This feature can be used to simplify

Read/Modify/Write operations to a Byte Write operation.

Single Clock Mode

The CY7C1318V18 can be used with a single clock that

controls bot h the i nput and out put r egister s. In this m ode th e

device will re cogni ze on ly a si ngl e pair of input cloc ks (K an d

K

) that control both the input and output registers. This

operation is identical to the operation if the device had zero

skew between the K/K

and C/C clocks. All tim ing parame ter s

remain the same in this mode. To use this mode of operation,

the user must tie C and C

HIGH at power- on . Th is fu n ct ion is

a strap option and not alterable during device operation.

DDR Operation

The CY7C1318V18 enables high performance operation

through high clock frequencies (achieved through pipelining)

and double data rate mode of operation. The CY7C1318V18

requires a single No O peration (NOP) cycl e when transitioning

from a Read to a Write cycle. At higher frequencies, some

applications may require a second NOP cycle to avoid

contention.

If a Read occurs after a Write cycle, address and data for the

Write are stored in registers. The write information must be

stored because the SRAM c an not perform the last wo rd Write

to the array without conflicting with the Read. The data stays

in this register until the next Write cycle occurs. On the first

Write cycle af ter the READ (s), the st ored dat a from the earl ier

Write will be written into the SRAM array. This is called a

Posted Write.

If a Read is performed o n th e sa me address on which a Writ e

is performed in the previous cycle, the SRAM reads out the

most current data. The SRAM does this by bypassing the

memory array and reading the data from the registers.

Depth Expansion

Depth expansion requires replicating the LD

control signal for

each bank. All other control signals can be common between

banks as appropriate.

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 7 of 24

Programmable Impedance

An external resistor, RQ, must be connected between the ZQ

pin on the SRAM and V

SS

to allow the SRAM to adjust its

output driver impedance. The value of RQ must be 5X the

value of the inten ded line impe dance driven by the SRAM, The

allowable range of RQ to guaran tee impedanc e matchi ng with

a tolerance of ±10% is between 175Ω and 350Ω

, with

V

DDQ

= 1.5V. The output impedance is adjusted every 1024

cycles to adjust for drifts in supply voltage and temperature.

Echo Clocks

Echo clocks are provided on the DDR-II to simplify data

capture on high-speed systems. Two echo clocks are

generated by the DDR-II. CQ is referenced with respect to C

and CQ

is referenced with respect to C. These are

free-running clocks and are synchronized to the output clock

of the DDR-II. In the single clock mode, CQ is generated with

respect to K and CQ

is generated with respect to K. The

timings for the echo clocks are shown in the AC Timing table.

Application Example

[2]

DQ

Add.

K/K

C/C

R/W

Add.

K/K

C/C

R/W

18

72

SRAM #1

SRAM #4

V

TERM

= V

REF

CLK/CLK (output)

DQ

LD

Add.

R/W

CLK/CLK (input)

18

2

R = 50Ω

VT = V

REF

R = 50Ω

DQ

Memory

Controller

20

20

2

LD

LD

Truth Table

[3, 4,5, 6, 7, 8]

Operation K LD R/W DQ DQ

Write Cycle:

Load address; input write data on consecutive K and K

rising

edges.

L-H L L D(A1)at K(t + 1) ↑ D(A2) at K

(t + 1) ↑

Read Cycle:

Load address; wait one cycle; read data on consecutive C

and

C rising edg es.

L-H L H Q(A1) at C

(t + 1)↑ Q(A2) at C(t + 2) ↑

NOP: No Operation L-H H X High-Z High-Z

Standby: Clock Stopped Stopped X X Previous State Previous State

Notes:

2. The above application shows 4 of CY7C1318V18 being used. This holds true for CY7C1316V18 and CY7C1320V18 as well.

3. X = “Don’t Care,” H = Logic HIGH, L = Logic LOW,

↑represents rising edge.

4. Device will power-up deselected and the outputs in a three-state condition.

5. On CY7C1318V18 and CY7C1320V18, “A1” represents address location latched by the devices when transaction was initiated and A2 represents the addresses

sequence in the burst. On CY7C1316V18, “A1” represents A + ‘0’ and A2 represents A + ‘1.’

6. “t” represents the cycle at which a read/write operation is started. t+1 and t + 2 are the first and second clock cycles succeeding the “t” clock cycle.

7. Data inputs are registered at K and K

rising edges. Data outputs are delivered on C and C rising edges, except when in single clock mode.

8. It is recommended that K = K

and C = C = HIGH when clock is stopped. This is not essential, but permits most rapid restart by overcoming transmission line

charging symmetrically.

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 8 of 24

Burst Address Table (CY7C1318V18 and

CY7C1320V18)

First Address (External) Second Address (Internal)

X..X0 X..X1

X..X1 X..X0

Write Cycle Descriptions

(CY7C1316V18 and CY7C1318V18)

[3, 9]

BWS0BWS1KK Comments

LLL-H– During the Data portion of a Write sequence :

CY7C1316V18 − both nibbles (D

[7:0]

) are written into the device,

CY7C1318V18 − both bytes (D

[17:0]

) are written into the device.

LL– L-H During the Data portion of a Write sequence :

CY7C1316V18 − both nibbles (D

[7:0]

) are written into the device,

CY7C1318V18 − both bytes (D

[17:0]

) are written into the device.

LHL-H– During the Data portion of a Write sequence :

CY7C1316V18 − only the lo wer nibb le (D

[3:0]

) is written into th e device. D

[7:4]

will remain unalt ered,

CY7C1318V18 − only the lower byte (D

[8:0]

) is written into the device. D

[17:9]

will remain unaltered.

LH– L-H During the Data portion of a Write sequence :

CY7C1316V18 − only the lo wer nibb le (D

[3:0]

) is written into th e device. D

[7:4]

will remain unalt ered,

CY7C1318V18 − only the lower byte (D

[8:0]

) is written into the device. D

[17:9]

will remain unaltered.

HLL-H– During the Data portion of a Write sequence :

CY7C1316V18 − only th e upper nibbl e (D

[7:4]

) is written into the de vice. D

[3:0]

will remain unalt ered,

CY7C1318V18 − only the upper byte (D

[17:9]

) is written into the device. D

[8:0]

will remain unaltered.

HL– L-H During the Data portion of a Write sequence :

CY7C1316V18 − only th e upper nibbl e (D

[7:4]

) is written into the de vice. D

[3:0]

will remain unalt ered,

CY7C1318V18 − only the upper byte (D

[17:9]

) is written into the device. D

[8:0]

will remain unaltered.

HHL-H– No data is written into the devices during this portion of a write operation.

HH– L-H No data is written into the devices during this portion of a write operation.

Write Cycle Descriptions

(CY7C1320V18)

[3, 9]

BWS

0

BWS

1

BWS

2

BWS

3

KK Comments

LLLLL-H– During the Data portion o f a Write sequen ce,

all four bytes (D

[35:0]

) are written into the

device.

LLLL– L-H During the Data portion o f a Write sequen ce,

all four bytes (D

[35:0]

) are written into the

device.

LHHHL-H– During the Data po rtion of a Wri te sequence,

only the lower byte (D

[8:0]

) is written into the

device. D

[35:9]

will remain unaltered.

LHHH– L-H During the Dat a portion of a Write sequence ,

only the lower byte (D

[8:0]

) is written into the

device. D

[35:9]

will remain unaltered.

HLHHL-H– During the Data portion of a W rite sequence,

only the byte (D

[17:9]

) is written into the

device. D

[8:0]

and D

[35:18]

will remain

unaltered.

Note:

9. Assumes a Write cycle was initiated per the Write Port Cycle Description Truth T able. BWS

0

, BWS1 in the case of CY7C1316V18 and CY7C1318V18 and also

BWS

2

, BWS3 in the case of CY7C1320V18 can be altered on different portions of a write cycle, as long as the set-up and hold requirements are achieved.

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 9 of 24

HLHH– L-H During the Data portion of a Wri te sequence,

only the byte (D

[17:9]

) is written into the

device. D

[8:0]

and D

[35:18]

will remain

unaltered.

HHLHL-H– During the Data po rtion of a Wri te sequence,

only the byte (D

[26:18]

) is written into the

device. D

[17:0]

and D

[35:27]

will remain

unaltered.

HHLH– L-H During the Data portion of a Write sequence ,

only the byte (D

[26:18]

) is written into the

device. D

[17:0]

and D

[35:27]

will remain

unaltered.

H H H L L-H During the Data portion of a Wri te sequence,

only the byte (D

[35:27]

) is written into the

device. D

[26:0]

will remain unaltered.

HHHL– L-H During the Data portion o f a Write seq uence,

only the byte (D

[35:27]

) is written into the

device. D

[26:0]

will remain unaltered.

HHHHL-H– No data is writte n into t he d evice du ring this

portion of a write operation.

HHHH– L-H No data is written into the d evice during this

portion of a write operation.

Write Cycle Descriptions

(CY7C1320V18) (continued)

[3, 9]

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 10 of 24

Maximum Ratings

(Above which the us efu l l ife ma y be impaired. For user gui delines, not tested.)

Storage Temperature .................................–65°C to +150°C

Ambient Temperature with

Power Applied.............................................–55°C to +125°C

Supply Voltage on V

DD

Relative to GND........–0.5V to +2.9V

DC Voltage Applied to Outputs

in High-Z State

[12]

...............................–0.5V to V

DDQ

+ 0.5V

DC Input Voltage

[12]

............................–0.5V to V

DDQ

+ 0.5V

Current into Outputs (LOW).........................................20 mA

Static Discharge Voltage........................................... >2001V

(per MIL-STD-883, Method 3015)

Latch-up Current..................................................... >200 mA

Operating Range

Range

Ambient

Temperature

[10]

V

DD

V

DDQ

Com’l 0°C to +70°C 1.8 ± 100 mV 1.4V to V

DD

Electrical Characteristics Over the Operating Rang e

[1, 11]

Parameter Description Test Conditions Min. Typ. Max. Unit

V

DD

Power Supply Voltage 1.7 1.8 1.9 V

V

DDQ

I/O Supply Voltage 1.4 1.5 V

DD

V

V

OH

Output HIGH Voltage I

OH

= −2.0 mA, Nominal Impedance V

DDQ

– 0.2 V

DDQ

– 0.2 V

DDQ

V

V

OL

Output LOW Voltage IOL = 2.0 mA, Nominal Impedance V

SS

V

SS

0.2 V

V

IH

Input HIGH Voltage

[12]

V

REF

+ 0.1 V

REF

+ 0.1 V

DDQ

+ 0.3 V

V

IL

Input LOW Voltage

[12]

–0.3 V

REF

– 0.1 V

REF

– 0.1 V

I

X

Input Load Current GND ≤ VI ≤ V

DDQ

–5 –5 5 µA

I

OZ

Output Leakage

Current

GND ≤ VI ≤ V

DDQ,

Output Disabled –5 –5 5 µA

V

REF

Input Reference

Voltage

[13]

Typical Value = 0.75V 0.68 0.75 0.95 V

I

DD

VDD Operating Supply

x8, x18

V

DD

= Max., I

OUT

= 0 mA,

f = f

MAX

= 1/t

CYC

167 MHz TBD mA

200 MHz TBD mA

250 MHz TBD mA

300 MHz TBD mA

I

DD

VDD Operating Supply

x36

V

DD

= Max., I

OUT

= 0 mA,

f = f

MAX

= 1/t

CYC

167 MHz TBD mA

200 MHz TBD mA

250 MHz TBD mA

300 MHz TBD mA

I

SB1

Automatic

Power-down

Current, x8, x18

Max. VDD, Both Ports

Deselected, VIN ≥ VIH or

V

IN

≤ VIL f = f

MAX

= 1/t

CYC

,

Inputs S tatic

167 MHz TBD mA

200 MHz TBD mA

250 MHz TBD mA

300 MHz TBD mA

I

SB1

Automatic

Power-down

Current, x36

Max. VDD, Both Ports

Deselected, VIN ≥ VIH or

V

IN

≤ VIL f = f

MAX

= 1/t

CYC,

Inputs S tatic

167 MHz TBD mA

200 MHz TBD mA

250 MHz TBD mA

300 MHz TBD mA

Notes:

10. Ambient temperature = T

A

. This is the case temperature.

11. All voltage referenced to ground.

12. Oversho ot: V

IH

(AC) < VDD + 0.5V for t < t

TCYC

/2; undershoot VIL(AC) < − 0.5V for t < t

TCYC

/2; power-up: V

IH

< 1.8V and V

DD

< 1.8V and V

DDQ

< 1.4V for

t < 200 ms.

13. V

REF

Min. = 0.68V or 0.46V

DDQ

, whichever is larger, V

REF

Max. = 0.95V or 0.54V

DDQ

, whichever is smaller.

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 11 of 24

Switching Characteristics Over the Operating Range

[1, 14]

Parameter Description

300 250 200 167

UnitMin. Max. Min. Max. Min. Max. Min. Max.

t

CYC

K Clock and C Clock Cycle Time 3.3 4.0 4.0 5.0 5.0 6.0 6.0 7.5 ns

t

KH

Input Clock (K/K and C/C) HIGH 1.32 – 1.6 – 2.0 – 2.4 – ns

t

KL

Input Clock (K/K and C/C) LOW 1.32 – 1.6 – 2.0 – 2.4 – ns

t

KHKH

K/K Clock Rise to K/K Clock Rise and C/C to

C/C

Rise (rising edge to rising edge)

1.49 1.82 1.8 – 2.2 – 2.7 – ns

t

KHCH

K/K Clock Rise to C/C Clock Rise (rising edge

to rising edge)

0.0 1.45 0.0 1.8 0.0 2.3 0.0 2.8 ns

Set-up Times

t

SA

Address Set-up to K Clock Rise 0.4 – 0.5 – 0.6 – 0.7 ns

t

SC

Control Set-up to Clock (K) Rise (R/W, LD,

BWS

0

, BWS1, BWS2, BWS3)

0.4 – 0.5 – 0.6 – 0.7 – ns

t

SD

D

[x:0]

Set-up to Clock (K and K) Rise 0.3 – 0.4 – 0.5 – 0.6 – ns

Hold Times

t

HA

Address Hold after Clock (K) Rise 0.4 – 0.5 – 0.6 – 0.7 ns

t

HC

Control Hold after Clock (K) Rise (R/W, LD,

BWS

0

, BWS1, BWS2, BWS3)

0.4 – 0.5 – 0.6 – 0.7 – ns

t

HD

D

[x:0]

Hold after Clock (K and K) Rise 0.3 – 0.4 – 0.5 – 0.6 – ns

Output Times

t

CO

C/C Clock Rise (or K/K in single clock mode)

to Data Valid

[14]

– 0.29 – 0.35 – 0.38 – 0.40 ns

t

DOH

Data Output Hold after Output C/ C Clock Rise

(Active to Active)

–0.29 ––0.35 ––0.38 ––0.40 – ns

t

CCQO

C/C Clock Rise to Echo Clock Valid – 0.27 – 0.33 – 0.36 – 0.38 ns

t

CQOH

Echo Clock Hold after C/C Clock Rise –0.27 – –0.27 – –0.36 – –0.38 – ns

t

CQD

Echo Clock High to Data Change –0.27 0.29 –0.33 0.35 –0.36 0.38 –0.38 0.40 ns

t

CLZ

Clock (C) Rise to Low-Z

[15, 16]

–0.29 – –0.35 – –0.38 – –0.4 – ns

t

CHZ

Clock (C) Rise to High-Z (Active to High-Z)

[15,

16]

– 0.29 – 0.35 – 0.38 – 0.4 ns

DLL Timing

t

KC

Clock Phase Jitter – 0.08 – 0.10 – 0.13 0.15 ns

t

KC lock

DLL Lock Time (K, C) 1024 - 1024 – 1024 – 1024 – cycles

Capacitance

[17]

Parameter Description Test Conditions Max. Unit

CIN Input Capacitance TA = 25°C, f = 1 MHz,

VDD = 1.8V

V

DDQ

= 1.5V

TBD pF

C

CLK

Clock Input Capacita nc e TBD pF

C

O

Output Capacitance TBD pF

Notes:

14. Unless otherwise noted, test conditions assume signal transition time of 2V/ns, timing reference levels of 0.75V, V

REF

= 0.75V, RQ = 250Ω, V

DDQ

= 1.5V,

input pulse levels of 0.25V to 1.25V, and output loading of the specified I

OL/IOH

and load capacitance shown in (a) of AC Test Loads.

15. t

CHZ

, t

CLZ

, are specified with a load capacitance of 5 pF as in (b) of AC Test Loads. Transition is measured ± 100 mV from steady-state voltage.

16. At any given voltage and temperature t

CHZ

is less than t

CLZ

and t

CHZ

less than tCO.

17. Tested initially and after any design or process change that may affect these parameters.

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 12 of 24

AC Test Loads and Waveforms

1.25V

0.25V

R = 50Ω

5pF

INCLUDING

JIG AND

SCOPE

ALL INPUT PULSES

Device

R

L

= 50Ω

Z

0

= 50Ω

V

REF

= 0.75V

V

REF

= 0.75V

[14]

0.75V

Under

Test

0.75V

Device

Under

Test

OUTPUT

0.75V

V

REF

V

REF

OUTPUT

ZQ

ZQ

(a)

RQ =

250Ω

(b)

RQ =

250Ω

Slew Rate = 2V / ns

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 13 of 24

Switching Waveforms

Note:

18. Device originally deselected.

K

= DON’T CARE

= UNDEFINED

ead/Deselect Sequence

K

A

R/W

A

B

t

KL

t

CYC

t

SA

t

HA

t

KH

t

KHKH

t

KHKH

LD

C

Read

Read

Read

Deselect

Deselect

Deselect

DQ

Q(A)

Q(A+1)

Q(B)

Q(B+1)

Q(C)

Q(C+1)

t

CHZ

t

DOH

C

C

t

CO

t

CLZ

CQ

CQ

t

CQOH

t

CQD

t

KHCH

t

KHCH

t

CO

t

CCQO

t

CQOH

t

CCQO

t

KL

t

KL

t

KH

t

KH

t

KHKH

t

CQD

t

KH

t

SC

t

KL

t

HC

[18]

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 14 of 24

Notes:

19. C and C

reference to Data Outputs and do not affect Write operations.

20. BWS

x

LOW = Valid, Byte writes allowed, see Byte write table for details.

Switching Waveforms

K

= DON’T CARE

= UNDEFINED

Write/Deselect Sequence

K

A

Data In

R/W

A

D(A)

D(A+1)

D(B)

D(B+1)

B

t

KH

t

KL

t

CYC

t

SA

t

HC

t

SC

t

HD

t

SD

BWS

x

t

SC

t

HC

t

KL

D(C)

D(C+1)

t

HC

t

HA

LD

C

Write

Write

Write

Deselect

Deselect

Deselect

t

KH

t

SC

[19, 20]

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 15 of 24

Switching Waveforms

K

LD

= DON’T CARE

= UNDEFINED

Read/Write/Deselect Sequence

K

A

R/W

DQ

[x:0] Q(A)

Q(A+1)

Q(B)

Q(B+1)

D(B) D(B+1)

A

A

C

C

CQ

CQ

Read

NOP/Deselect

B

B

Write

Read

Deselect

Deselect

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 16 of 24

IEEE 1149.1 Serial Boundary Scan (JTAG)

The DDR-II incorporates a serial boundary scan test access

port (TAP) in the FBGA package. This port operates in accordance with IEEE S tandard 1 149 .1-1900, but does not ha ve the

set of functions required for full 1149.1 compliance. These

functions from the IEEE specification are excluded because

their inclusion places an added delay in the critic al spee d path

of the SRAM. Note that the TAP controller functions in a

manner that does not conflict with the operation of other

devices using 1149.1 fully co mpli ant TAPs. The TAP operates

using JEDEC standard 1.8V I/O logic levels.

Disabling the JTAG Feature

It is possible to operate the SRAM without using the JTAG

feature. To disable the TAP c on trol ler, TCK must be tied LOW

(V

SS

) to prevent clocking of the d evice. TDI and TMS a re internally pulled up and m ay be unconnected . They may alternately

be connected to V

DD

through a pull-up resistor. TDO should

be left unconnected. Upon power-up, the device will come up

in a reset state which w ill not interfere with th e operation of the

device.

Test Access Port–Test Clock

The test clock is used only with the TAP controller. All inputs

are captured on the rising edge of TCK. All outputs are d riv en

from the falling edge of TCK.

Test Mode Select

The TMS input is used to give c ommands to the T AP con troller

and is sampled on the rising edge of TCK. It is allowable to

leave this pin unconnected if the TAP is not used. The pin is

pulled up internally, resulting in a logic HIGH level.

Test Data-In (TDI)

The TDI pin is used to serially input information into the

registers and can be connected to the input of any of the

registers. The regis ter between TDI and TDO is chose n by the

instruction that is loaded into the TAP instruction register. For

information on loading the instruction register, see the TAP

Controller State Diagram. TDI is internally pulled up and can

be unconnected if the TAP is unused in an application. TDI is

connected to the most significant bit (MSB) on any register.

Test Data-Out (TDO)

The TDO output pin i s u se d to serially clock data-o ut from the

registers. The output is active depending upon the current

state of the TAP state machine (see Instruction codes). The

output changes on the fall ing edg e of TCK. TDO is connec ted

to the least significant bit (LSB) of any register.

Performing a TAP Reset

A Reset is performed by fo rcing TMS HIGH (V

DD

) for five rising

edges of TCK. This RESET does not affect the operation of

the SRAM and may be performed while the SRAM is

operating. At power-up, the TAP is reset internally to ensure

that TDO comes up in a high-Z state.

TAP Registers

Registers are connected between the TDI and TDO pins and

allow data to be scanned into and out of the SRAM test

circuitry. Only one register can be selected at a time through

the instruction registe rs. Data is serially loaded into the TDI pin

on the rising edge of TCK. Data is output on the TDO pin on

the falling edge of TCK.

Instruction Register

Three-bit instructi ons can be serially loaded into the ins truction

register. This register is loaded when it is placed between the

TDI and TDO pins as s hown in T AP Controller Blo ck Diagra m.

Upon power-up, the instruction register is loaded with the

IDCODE instruction. It is also loaded with the IDCODE

instruction if the controller is placed in a reset state as

described in the previous section.

When the TAP controller is in the Capture IR state, the two

least significant bits are loaded with a binary “01” pattern to

allow for fault isolation of the board level serial test path.

Bypass Register

To save time when serially shifting data through registers, it is

sometimes advantageous to skip certain chips. The bypass

register is a si ngle-bit register th at can be placed between TD I

and TDO pins. This allows data to be shifted through the

SRAM with minimal delay. The bypass register is set LOW

(V

SS

) when the BYPASS instruction is executed.

Boundary Scan Register

The boundary scan register is connected to all the input and

output pins on the SRAM. Several no connect (NC) pins are

also included in the scan register to reserve pins for higher

density devices.

The boundary scan register is loaded with the contents of the

RAM Input and Output ring when the TAP controller is in the

Capture-DR state and is then placed between the TDI and

TDO pins when the controller is moved to the Shift-DR state.

The EXTEST, SAMPLE/PRELOAD and SAMPLE Z instructions can be used to capture the contents of the Input and

Output ring.

The Boundary Scan Order tables show the order in which the

bits are connecte d. Each bit corres ponds to one of the bump s

on the SRAM package. The MSB of the register is connected

to TDI, and the LSB is connected to TDO.

Identification (ID) Register

The ID register is loaded with a vendor-specific, 32-bit code

during the Capture-DR state when the IDCODE command is

loaded in the instruction register. The IDCODE is hardwired

into the SRAM and can be sh ifted out w hen the TAP controller

is in the Shift-DR state. The ID regi ster has a vendor code and

other information described in the Identification Register

Definitions table.

TAP Instruction Set

Eight different instructions are possible with the three-bit

instruction register. All combinations are listed in the

Instruction Code table. Three of these instructions are listed

as RESERVED and sho uld not be use d. The other five in structions are described in detail below.

The TAP controller used in this SRAM is not f ull y c om pl ian t to

the 1 149.1 con vention becau se some of th e mandatory 1 149.1

instructions are not fully implemented. The TAP controller

cannot be used to load address, data, or control signals into

the SRAM and cannot preload the Input or Output buffers . The

SRAM does not implemen t the 1149.1 comman ds EXTEST or

INTEST or the PRELOAD portion of SAMPLE/PRELOAD;

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 17 of 24

rather it performs a ca ptu r e o f the In put and O utpu t ri ng w h en

these instructions are executed.

Instructions are loaded into the TAP controller during the

Shift-IR state when the instruction register is placed between

TDI and TDO. During this state, instructions are shifted

through the instruction reg ister through the TDI and TDO pins.

To execute the instruction once it is shifted in, the TAP

controller needs to be moved into the Update-IR state.

EXTEST

EXTEST is a mandatory 1149.1 instruction that is to be

executed whenever the instruction register is loaded with all

0s. EXTEST is not implemented in the TAP controller, and

therefore this device is not compliant to the 1149.1 standard.

The TAP controller does recognize an all-0 instruction. When

an EXTEST inst ruction is loade d into th e instruc tion regi ster,

the SRAM responds as if a SAMPLE/PRELOAD instruction

has been loaded.

IDCODE

The IDCODE instruc tion causes a vendor-specific, 32-bit code

to be loaded into the instruction register. It also places the

instruction register be twee n the TDI and TDO p ins and allows

the IDCODE to be shifted out of the device when the TAP

controller enters the Shift-DR state. The IDCODE instruction

is loaded into the instruction register upon power-up or

whenever the TAP controller is given a test logic reset state.

SAMPLE Z

The SAMPLE Z instru ction ca uses the b oundary s can regis ter

to be connected between the TDI and TDO pins when the T AP

controller is in a Shift-DR state.

SAMPLE/PRELOAD

SAMPLE/PRELOAD is a 1149.1 mandatory instruction. The

PRELOAD portion of this instruction is not implemented, so

the TAP controller is not fully 1149.1-compliant.

When the SAMPLE/PRELOAD instruction is loaded into the

instruction register and the T AP contro ller is in the Capture-DR

state, a snapshot of data on the inputs and output pins is

captured in the boundary scan register.

The user must be a ware that the TAP controller clock can only

operate at a frequency up to 10 MHz, while the SRAM clock

operates more than an order of magnitude faster. Because

there is a large difference in the clock frequencies, it is

possible that during the Capture-DR state, an input or output

will undergo a transition. The TAP may then try to capture a

signal while in tran si tio n (m et as t a ble state). This will no t ha rm

the device, but there is no guarantee as to the value that will

be captured. Repeatable results may not be possible.

To guarantee that the boundary scan register will capture the

correct value of a signal, the SRAM signal must be stabilized

long enough to meet the TAP controller’s capture set-up plus

hold times (t

CS

and tCH). The SRAM clock inputs might not be

captured correctly if there is no way in a design to stop (or

slow) the clock du ring a SAMPLE/PRELOAD instruc tion. If this

is an issue, it is still possible to capture all other signals and

simply ignore the value of the K, K

, C, and C captured in the

boundary scan register.

Once the data is captured, it is pos sible to s hift out th e data b y

putting the TAP into the Shift-DR state. This places the

boundary scan register between the TDI and TDO pins.

Note that s ince the PRELOAD part of the command is not

implemented, putting the TAP into the Update to the

Update-DR state while performing a SAMPLE/PRELOAD

instruction will have the same effect as the Pause-DR

command.

Bypass

When the BYPASS instruction is loaded in the instruction

register and the TAP is placed in a Shift-DR state, the bypass

register is placed between the TDI and TDO pins. The

advantage of the BYPASS instruction is that it shortens the

boundary scan path when multiple devices are connected

together on a board.

Reserved

These instructions are not implemented but are reserved for

future use. Do not use these instructions.

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 18 of 24

TAP Controller State Diagram

[21]

Note:

21. The 0/1 next to each state represents the value at TMS at the rising edge of TCK.

TEST-LOGIC

RESET

TEST-LOGIC/

IDLE

SELECT

DR-SCAN

CAPTURE-DR

SHIFT-DR

EXIT1-DR

PAUSE-DR

EXIT2-DR

UPDATE-DR

SELECT

IR-SCAN

CAPTURE-IR

SHIFT-IR

EXIT1-IR

PAUSE-IR

EXIT2-IR

UPDATE-IR

1

0

1

1

0

1

0

1

0

0

0

1

1

1

0

1

0

1

0

0

0

1

0

1

1

0

1

0

0

1

1

0

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 19 of 24

TAP Controller Block Diagram

0

012..

29

3031

Boundary Scan Register

Identification Register

012..

.

.106

012

Instruction Register

Bypass Register

Selection

Circuitry

Selection

Circuitry

TAP Controller

TDI

TDO

TCK

TMS

TAP Electrical Characteristics Over the Operating Range

[11, 12 , 22]

Parameter Description Test Conditions Min. Max. Unit

V

OH1

Output HIGH Voltage I

OH

= −2.0 mA VDD − 0.45 V

V

OH2

Output HIGH Voltage I

OH

= −100 µA VDD − 0.2 V

V

OL1

Output LOW Voltage IOL = 2.0 mA 0.45 V

V

OL2

Output LOW Voltage IOL = 100 µA 0.2 V

V

IH

Input HIGH Voltage 0.65V

DD

V

DD

+ 0.3 V

V

IL

Input LOW Voltage –0.3 0.35V

DD

V

I

X

Input and OutputLoad Current GND ≤ VI ≤ V

DD

−5 5 µA

TAP AC Switching Characteristics Over the Operating Range

[23, 24]

Parameter Description Min. M ax. Unit

t

TCYC

TCK Clock Cycle Time 100 ns

t

TF

TCK Clock Frequency 10 MHz

t

TH

TCK Clock HIGH 40 ns

t

TL

TCK Clock LOW 40 ns

Notes:

22. These characteristics pertain to the TAP inputs (TMS, TCK, TDI and TDO). Parallel load levels are specified in the Electrical Characteristics Table.

23. t

CS

and tCH refer to the set-up and hold time requirements of latching data from the boundary scan register.

24. Test conditions are specified using the load in TAP AC test conditions. t

R/tF

= 1 ns.

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 20 of 24

Set-up Times

t

TMSS

TMS Set-up to TCK Clock Rise 10 ns

t

TDIS

TDI set-up to TCK Clock Rise 10 ns

t

CS

Capture Set-up to TCK Rise 10 ns

Hold Times

t

TMSH

TMS Hold after TCK Clock Rise 10 ns

t

TDIH

TDI Hold after Clock Rise 10 ns

t

CH

Capture Hold after Clock Rise 10 ns

Output Times

t

TDOV

TCK Clock LOW to TDO Valid 20 ns

t

TDOX

TCK Clock LOW to TDO Invalid 0 ns

TAP Timing and Test Conditions

[24]

TAP AC Switching Characteristics Over the Operating Range

[23, 24]

Parameter Description Min. M ax. Unit

(a)

TDO

CL= 20 pF

Z

0

= 50Ω

GND

0.9V

50Ω

1.8V

0V

ALL INPUT PULSES

0.9V

Test Clock

Test Mode Select

TCK

TMS

Test Data-In

TDI

Test Data-Out

t

TCYC

t

TMSH

t

TL

t

TH

t

TMSS

t

TDIS

t

TDIH

t

TDOV

t

TDOX

TDO

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 21 of 24

Identification Register Definitions

Instruction Field

Value

DescriptionCY7C1316V18 CY7C1318V18 CY7C1320V18

Revision Number (31:29) 000 000 000 Version number.

Cypress Device ID (28:12) 11010100010000101 11010100010010101 11010100010100101 Defines the type of SRAM.

Cypress JEDEC ID (11:1) 00000110100 00000110100 00000110100 Allows unique identification of

SRAM vendor.

ID Register Presence (0) 1 1 1 Indicate the presence of an ID

register.

Scan Register Sizes

Register Name Bit Size

Instruction 3

Bypass 1

ID 32

Boundary Scan 107

Instruction Codes

Instruction Code Description

EXTEST 000 Captures the Input/Output ring c ontents. Places th e boundary scan regis ter between the TDI and

TDO. This instruct ion is n ot 1149.1 compliant. The EXTEST comma nd impl emented by the se

devices will NOT place the output buffers into a high-Z condition. If the output buffers

need to be in high-Z condition, this can be accomplished by deselecting the Read port.

IDCODE 001 Loads the ID register with the vendor ID code and places the register between TDI and TDO.

This operation does not affect SRAM operation.

SAMPLE Z 010 Captures the Input/Output contents. Pl ac es the bo und ary s can reg is ter betwe en TDI and TDO.

The SAMPLE Z command implemente d by these devices will place the output buffers in to

a high-Z condition.

RESERVED 011 Do Not Use: This instruction is reserved for future use.

SAMPLE/PRELOAD 100 Captures the Input/Output ring contents. Places the boundary scan register between TDI and

TDO. Does not affect the SRAM operation. This instruction does not implement 1149.1 preload

function and is therefore not 1149.1 compliant.

RESERVED 101 Do Not Use: This instruction is reserved for future use.

RESERVED 110 Do Not Use: This instruction is reserved for future use.

BYPASS 111 Places the bypass register between TDI and TDO. This operation does not affect SRAM

operation.

Boundary Scan Order

Bit # Bump ID

0 6R

1 6P

2 6N

3 7P

4 7N

5 7R

6 8R

7 8P

8 9R

9 11P

10 10P

11 10N

12 9P

13 10M

14 11N

15 9M

16 9N

17 11L

18 11M

19 9L

20 10L

21 11K

Boundary Scan Order (continued)

Bit # Bump ID

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 22 of 24

22 10K

23 9J

24 9K

25 10J

26 11J

27 11H

28 10G

29 9G

30 11F

31 11G

32 9F

33 10F

34 11E

35 10E

36 10D

37 9E

38 10C

39 11D

40 9C

41 9D

42 11B

43 11C

44 9B

45 10B

46 11A

47 10A

48 9A

49 8B

50 7C

51 6C

52 8A

53 7A

54 7B

55 6B

56 6A

57 5B

58 5A

59 4A

60 5C

61 4B

62 3A

63 2A

64 1A

65 2B

Boundary Scan Order (continued)

Bit # Bump ID

66 3B

67 1C

68 1B

69 3D

70 3C

71 1D

72 2C

73 3E

74 2D

75 2E

76 1E

77 2F

78 3F

79 1G

80 1F

81 3G

82 2G

83 1J

84 2J

85 3K

86 3J

87 2K

88 1K

89 2L

90 3L

91 1M

92 1L

93 3N

94 3M

95 1N

96 2M

97 3P

98 2N

99 2P

100 1P

101 3R

102 4R

103 4P

104 5P

105 5N

106 5R

Boundary Scan Order (continued)

Bit # Bump ID

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 23 of 24

© Cypress Semiconductor Corporation, 2002. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than cir cuitry embodied i n a Cypress Sem iconductor product . Nor does it convey or imply any license un der patent or other righ ts. Cypre ss Semiconductor doe s not authori ze

its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

Ordering Information

[1]

Speed

(MHz) Ordering Code

Package

Name Package Type

Operating

Range

300 CY7C1316V18-300BZC BB165A 13 x 15 mm FBGA Commercial

CY7C1318V18-300BZC

CY7C1320V18-300BZC

250 CY7C1316V18-250BZC BB165A 13 x 15 mm FBGA Commercial

CY7C1318V18-250BZC

CY7C1320V18-250BZC

200 CY7C1316V18-200BZC BB165A 13 x 15 mm FBGA Commercial

CY7C1318V18-200BZC

CY7C1320V18-200BZC

167 CY7C1316V18-167BZC BB165A 13 x 15 mm FBGA Commercial

CY7C1318V18-167BZC

CY7C1320V18-167BZC

Package Diagram

QDR RAMs and Quad Data Rate RAMs comprise a new family of products developed by Cypress, Hitachi, IDT , Micron, NEC and

Samsung technology.

165-Ball FBGA (13 x 15 x 1.2 mm) BB165A

51-85122-*B

PRELIMINARY

CY7C1316V18

CY7C1318V18

CY7C1320V18

Document #: 38-05177 Rev. *A Page 24 of 24

Document Title: CY7C1316V18/CY7C1318V18/CY7C1320V18 18-Mb DDR-II SRAM Two-word Burst Architecture

Document Number: 38-05177

REV. ECN NO.

ISSUE

DATE

ORIG. OF

CHANGE DESCRIPTION OF CHANGE

** 110856 11/09/01 SKX New Data Sheet

*A 115919 08/02/02 RCS Changed Status to Preliminary

Shaded 300-MHz Bin

Updated JTAG Scan Order

Loading...

Loading...