Cypress Semiconductor CY7C038-20AI, CY7C038-20AC, CY7C038-15AI, CY7C028-20AI, CY7C028-20AC Datasheet

...

PRELIMINARY

32K/64K x 16/18

Dual-Port Static RAM

CY7C027/028

CY7C037/038

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

November 23

,

1998

5

1

Features

• T rue Dual-Ported memory cells which allow si m ultaneous access of the same memory locat ion

• 32K x 16 organization (CY7C027)

• 64K x 16 organization (CY7C028)

• 32K x 18 organization (CY7C037)

• 64K x 18 organization (CY7C038)

• 0.35-micron CMOS for optimum speed/power

• High-speed access: 12

[1]

/15/20 ns

• Low operat i n g power

—

Active: I

CC

= 180 mA (typical)

—Standby: I

SB3

= 0.05 mA (typical)

• Fully asynchronous operation

• Automatic power-down

• Expandabl e data bus to 32/36 bits or more using Master/Slave chip sel ect when using more than one device

• On-chip arbitration logic

• Semaphores inc luded to permit software handshak ing

between ports

•INT flags f or port-to-port communication

• Separate upper-byte and lower-byte cont rol

• Dual Chip Enables

• Pin select for Master or Slave

• Commercial and industrial temperature ranges

• Available in 100-pin TQFP

• Pin-compatible and functionally equivalent to IDT7027

Notes:

1. See page 6 for Load Conditions.

2. I/O

8

–I/O15 for x16 devices; I/O9–I/O17 for x18 devices.

3. I/O

0

–I/O7 for x16 devices; I/O0–I/O8 for x18 dev ices.

4. A

0–A14

for 32K; A0–A15 for 64K devices.

5. BUSY

is an output in master mode and an input in slave mode.

R/W

L

CE

0L

CE

1L

OE

L

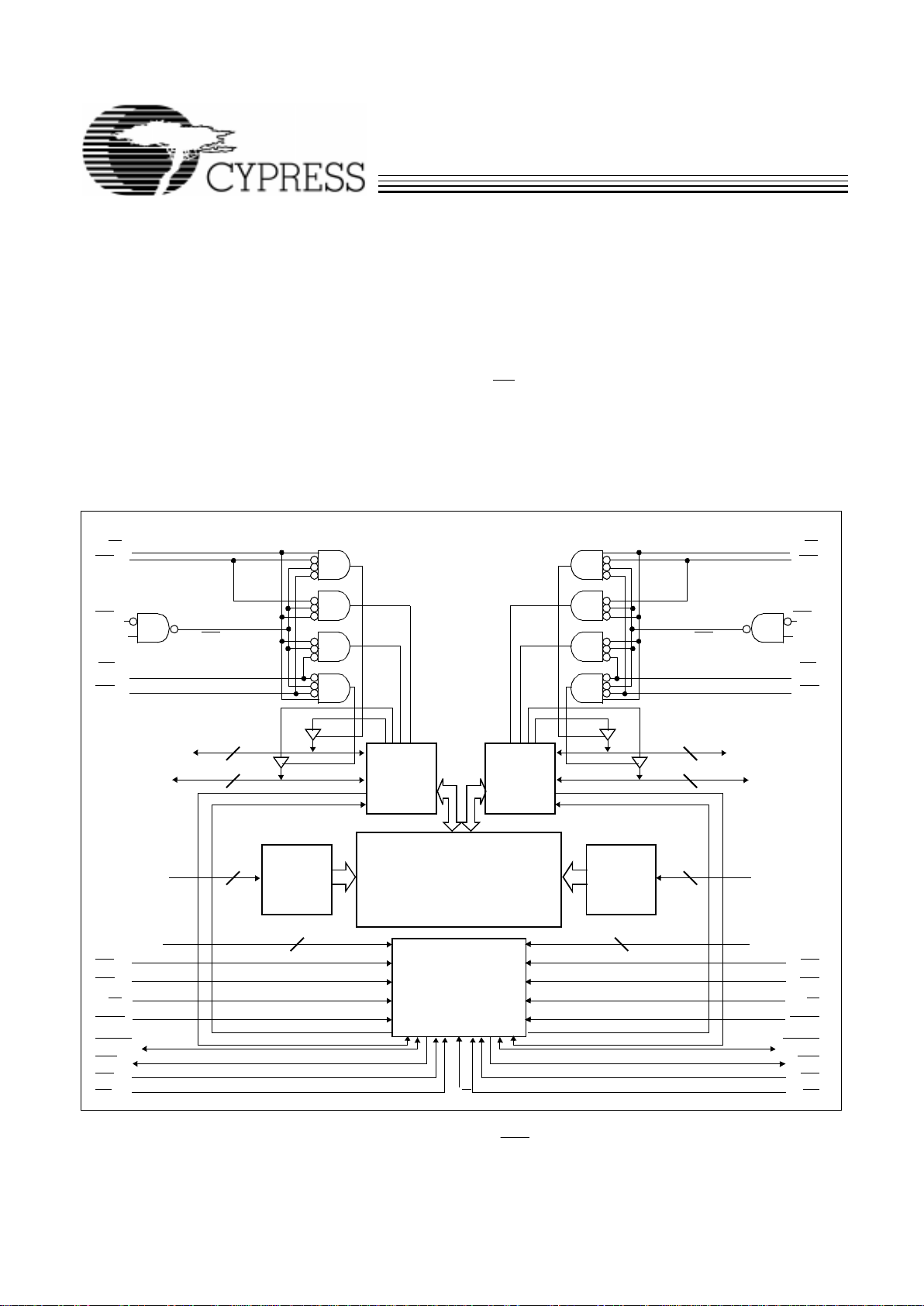

I/O

8/9L

–I/O

15/17L

I/O

Control

Address

Decode

A

0L–A14/15L

CE

L

OE

L

R/W

L

BUSY

L

I/O

Control

CE

L

Interrupt

Semaphore

Arbitration

SEM

L

INT

L

M/S

UB

L

LB

L

I/O0L–I/O

7/8L

R/W

R

CE

0R

CE

1R

OE

R

I/O

8/9L

–I/O

15/17R

CE

R

UB

R

LB

R

I/O0L–I/O

7/8R

UB

L

LB

L

Logic Block Diagram

A0L–A

14/15L

True Dual-Ported

RAM Array

A0R–A

14/15R

CE

R

OE

R

R/W

R

BUSY

R

SEM

R

INT

R

UB

R

LB

R

Address

Decode

A

0R–A14/15R

[2]

[2]

[3]

[3]

[4]

[4]

[5]

[5]

[4] [4]

15/16

8/9

8/9

15/16

8/9

8/9

15/16 15/16

For the most recent information, visit the Cypress web site at www.cypress.com

CY7C027/028

CY7C037/038

PRELIMINARY

2

Functional Description

The CY7C027/028 and CY7C037/038 are low-power CMOS

32K, 64K x 16/18 dual-port static RAMs. Various arbitration

schemes are included on the devices to handle situations

when multipl e proces sors acc ess t he sam e piece of data. Two

ports are provided , pe rmitting i ndep endent, asynchr onous access for reads and writes to any location in m emory. The devices can be utilized as standalone 16/18-bit dual-port static

RAMs or multip le devi ces can b e combined in o rder to funct ion

as a 32/36-bit or wider master/slave dual-port static RAM. An

M/S

pin is provided for implementing 32/36-bit or wider memory applications without the need for separate master and

slave devices or additional discrete logic. Application areas

include interprocessor/multiprocessor designs, communications status buffering, and dual-port video/graphics memory.

Each port has independent control pins: dual chip enables

(CE

0

and CE1), read or write enable (R/W), and output enable

(OE

). Two flags are provided on each port (BUSY and INT). BUSY

signals that the port is tryi ng to access the same location currently

being accessed by the ot her port. Th e interrupt flag (INT

) permits

communication between ports or systems by means of a mail box.

The semaphores are used to pass a flag, or token, from one port to

the other to indicate that a shared resource is in use. The semaphore

logic is comprised of eight shared latches. Only one side can control

the latch (semaphore) at any time. Control of a semaphore indicates

that a shared resource is in use. An automatic power-down feature is

controlled independently on each port by the chip enable pins.

The CY7C027/028 and CY7C03 7/0 38 are a v ail abl e in 100 -pin

Thin Quad Plastic Flatpack (TQFP) packages.

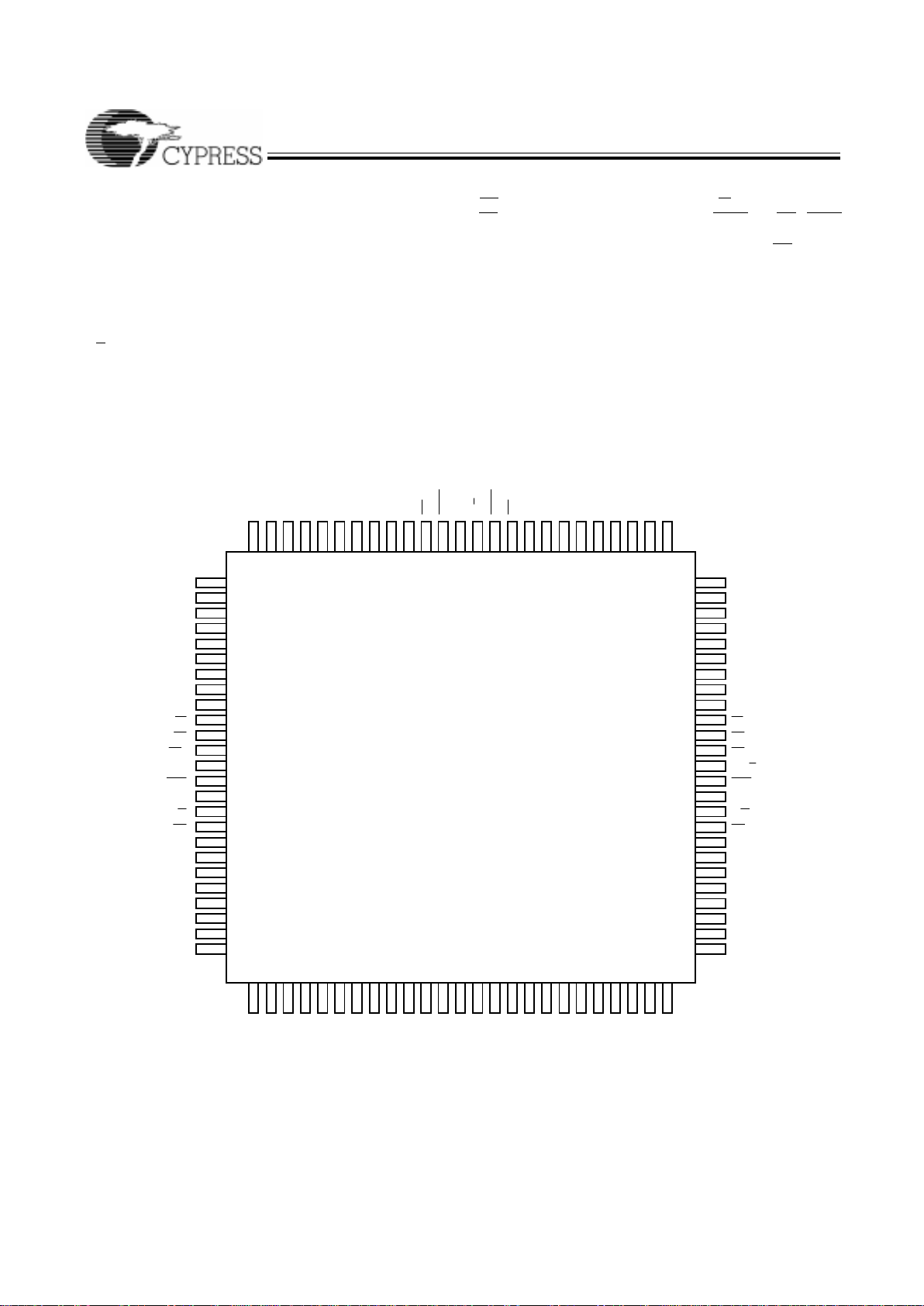

Pin Configurations

100- Pin TQ FP (Top View)

Note:

6. This pin is NC for CY7C027.

1

3

2

92 91 90 848587 868889 83 82 81 7678 77798093949596979899100

59

60

61

67

66

64

65

63

62

68

69

70

75

73

74

72

71

A9R

A10R

A11R

A12R

A13R

A14R

UBR

NC

LBR

CE1R

SEMR

OER

GND

NC

A15R

GND

R/WR

GND

I/O15R

I/O14R

I/O13R

I/O12R

I/O11R

I/O10R

CE0R

58

57

56

55

54

53

52

51

CY7C02 7 (32K x 16)

A9L

A10L

A11L

A12L

A13L

A14L

UBL

NC

LBL

CE1L

SEML

OEL

GND

NC

A15L

VCC

R/WL

GND

I/O15L

I/O14L

I/O13L

I/O12L

I/O11L

I/O10L

CE0L

17

16

15

9

10

12

11

13

14

8

7

6

4

5

18

19

20

21

22

23

24

25

A8L

A7L

A6L

A5L

A4L

A3L

INTL

A1L

NC

GND

M/S

A0R

A1R

A0L

A2L

BUSYR

INTR

A2R

A3R

A4R

A5R

A6R

A7R

A8R

BUSYL

34 35 36 424139 403837 43 44 45 5048 494746

NC

I/O9R

I/O8R

I/O7R

VCC

I/O6R

I/01R

I/O4R

I/O2R

GND

I/O0L

I/O2L

I/O3L

I/O3R

I/O5R

I/O1L

GND

I/O4L

I/O5L

I/O6L

I/O7L

VCC

I/O8L

I/O9L

I/O0R

3332313029282726

CY7C02 8 (64K x 16)

[Note 6]

[Note 6]

CY7C027/028

CY7C037/038

PRELIMINARY

3

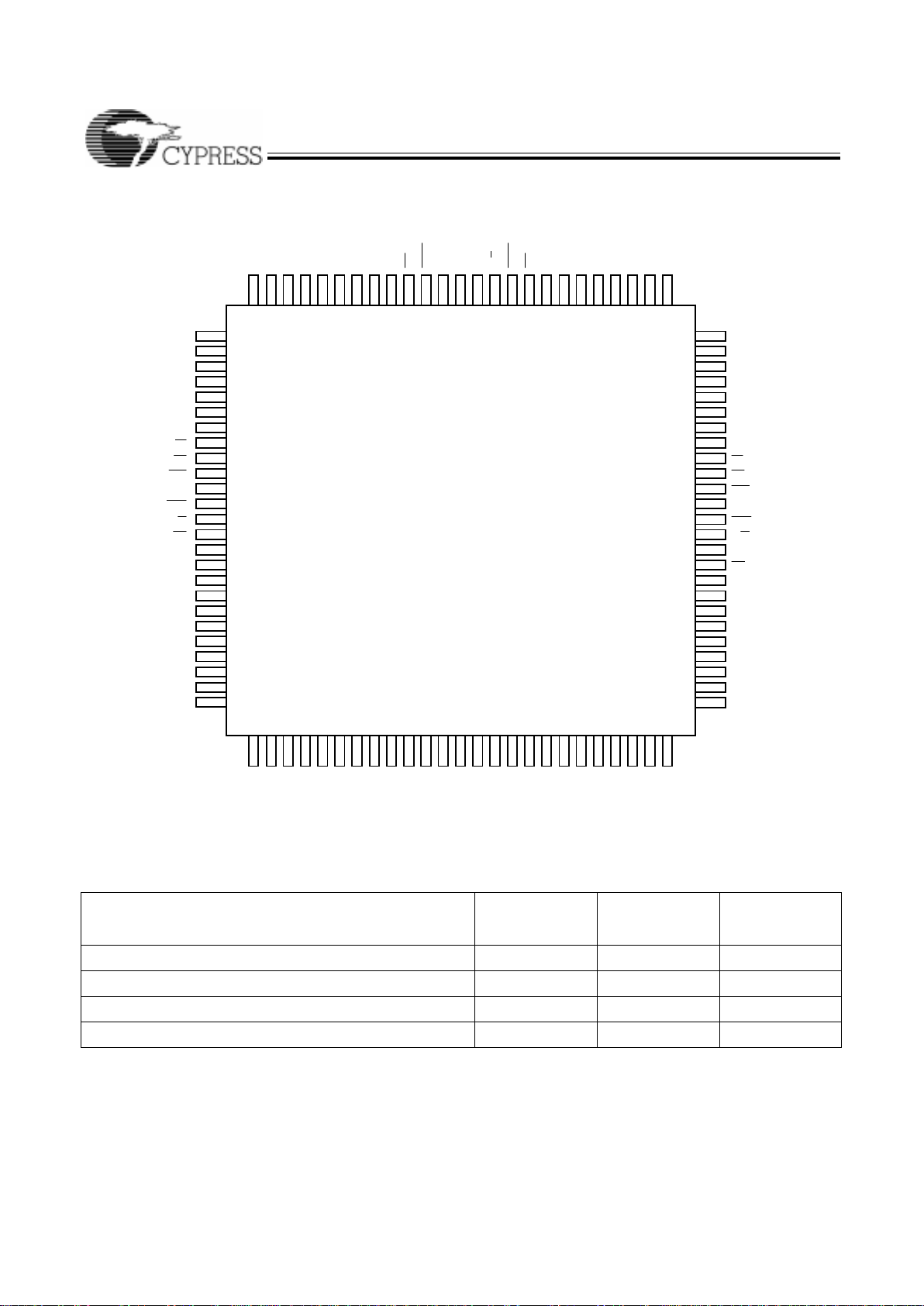

Pin Configurations

(continued)

100- Pin TQ FP (Top View)

Note:

7. This pin is NC for CY7C037.

Selection Guide

CY7C027/028

CY7C037/038

-12

[1]

CY7C027/028

CY7C037/038

-15

CY7C027/028

CY7C037/038

-20

Maximum Access Time (ns) 12 15 20

Typical Operating Current (mA) 195 190 180

Typical Standby Current for I

SB1

(mA) (Both ports TTL lev el) 55 50 45

Typical Standby Curren t for I

SB3

(mA) (Both ports CMOS level) 0.05 0.05 0.05

1

3

2

92 91 90 848587 868889 83 82 81 7678 77798093949596979899100

59

60

61

67

66

64

65

63

62

68

69

70

75

73

74

72

71

A8R

A9R

A10R

A11R

A12R

A13R

CE0R

A15R

UBR

SEMR

R/WR

GND

I/O17R

LBR

A14R

GND

OER

GND

I/O16R

I/O15R

I/O14R

I/O13R

I/O12R

I/O11R

CE1R

58

57

56

55

54

53

52

51

CY7C03 7 (32K x 18)

A9L

A10L

A11L

A12L

A13L

A14L

CE1L

LBL

CE0L

R/WL

OEL

I/O17L

I/O16L

UBL

A15L

VCC

GND

GND

I/O15L

I/O14L

I/O13L

I/O12L

I/O11L

I/O10L

SEML

17

16

15

9

10

12

11

13

14

8

7

6

4

5

18

19

20

21

22

23

24

25

A8L

A7L

A6L

A5L

A4L

A3L

BUSYL

A1L

INTL

GND

VCC

INTR

A0R

A0L

A2L

M/S

BUSYR

A1R

A2R

A3R

A4R

A5R

A6R

A7R

GND

34 35 36 424139 403837 43 44 45 5048 494746

I/O10R

I/O9R

I/O8R

I/O7R

VCC

I/O6R

I/01R

I/O4R

I/O2R

GND

I/O0L

I/O2L

I/O3L

I/O3R

I/O5R

I/O1L

GND

I/O4L

I/O5L

I/O6L

I/O7L

VCC

I/O8L

I/O9L

I/O0R

3332313029282726

CY7C03 8 (64K x 18)

[Note 7]

[Note 7]

CY7C027/028

CY7C037/038

PRELIMINARY

4

Maximum Ratings

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperat ure ............ ................. ....–65

°

C to +150°C

Ambient Temperature wit h

Power Applied.............................................–55

°

C to +125°C

Supply Voltage to Ground Potential...............–0. 3V to +7.0V

DC V oltage Applied to Outputs

in High Z State............................................ –0.5V to +7.0DC

Input Voltage

[8]

............................................... –0.5V to +7.0V

Output Current into Outputs (LOW)............................. 20 mA

Static Discharge Voltage ....................... ................... >1100V

Latch-Up Current............................. ................. ...... >200 mA

Note:

8. Pulse width < 20 ns.

Pin Definitions

Left Port Right Port Description

CE0L, CE

1L

CE0R, CE

1R

Chip Enable (CE is LOW when CE0 ≤ VIL and CE1 ≥ VIH)

R/W

L

R/W

R

Read/Write Enable

OE

L

OE

R

Output Enable

A0L–A

15L

A0R–A

15R

Address (A0–A14 for 32K ; A0–A15 for 64K devices)

I/O0L–I/O

17L

I/O0R–I/O

17R

Data Bus Input/Output (I/O0–I/O15 for x16 devices; I/O0–I/O17 for x18)

SEML SEM

R

Semaphore Enable

UB

L

UB

R

Upper Byte Select (I/ O8–I/O15 for x1 6 de v ices; I/O9–I/O17 for x18 devi ces)

LB

L

LB

R

Lower Byte Select (I/ O0–I/O7 for x16 devices; I/O0–I/O8 for x18 devices)

INT

L

INT

R

Interrupt Flag

BUSY

L

BUSY

R

Busy Flag

M/S Master or Slave Select

V

CC

Power

GND Ground

NC No Connect

Operating Range

Range

Ambient

Temperature

V

CC

Commercial 0°C to +70°C 5V ± 10%

Industrial –40°C to +85°C 5V ± 10%

Shaded area contains advance information.

CY7C027/028

CY7C037/038

PRELIMINARY

5

Shaded area contains advance information.

Note:

9. f

MAX

= 1/tRC = All inputs c ycling at f = 1/tRC (except output enab le) . f = 0 mea ns no add ress or contr ol li nes change . T his appl ies only to i nputs at C MOS le v el s tandb y I

SB3

.

Electrical Characteristics

Over the Ope rating Range

Symbol Parameter

CY7C027/028

CY7C037/038

Units

-12

[1]

-15 -20

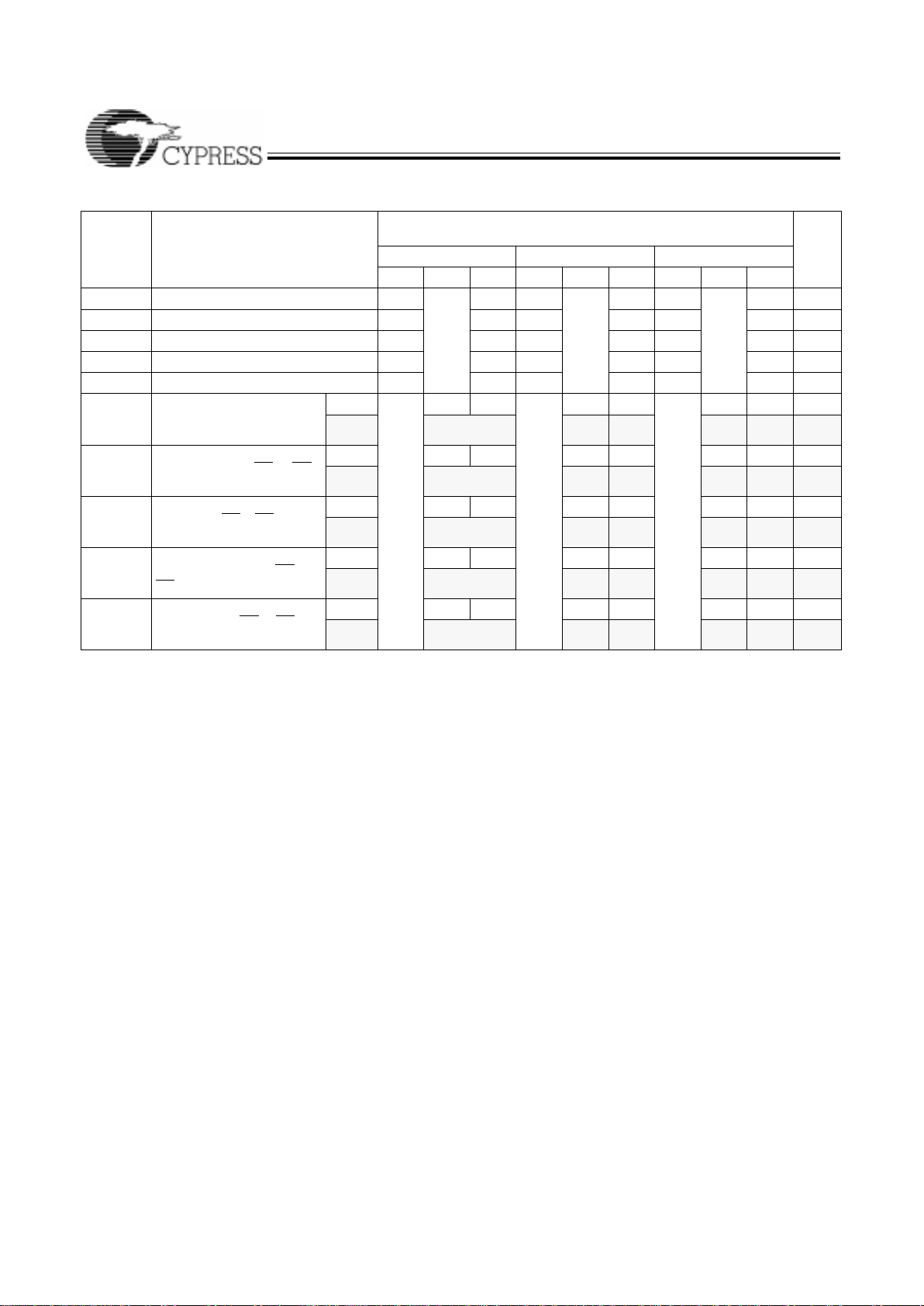

Min Typ Max Min Typ Max Min Typ Max

V

OH

Output HIGH Voltage (VCC=5V) 2.4 2.4 2.4 V

V

OL

Output LOW Voltage 0.4 0.4 0.4 V

V

IH

Input HIGH Voltage 2. 2 2.2 2.2 V

V

IL

Input LOW Voltage 0.8 0.8 0.8 V

I

OZ

Output Leakage Current –10 10 –10 10 –10 10 µA

I

CC

Operating Curr ent

(V

CC

=Max, I

OUT

=0 mA)

Outputs Disabled

Com’l. 195 325 190 280 180 265 mA

Indust. 215 305 305 290 mA

I

SB1

Standby Current (Both

Ports TTL Le vel) CE

L

& CER

≥ V

IH

, f=f

MAX

Com’l. 55 75 50 70 45 65 mA

Indust. 65 95 60 80 mA

I

SB2

Standby Current (One Port

TTL Lev el) CE

L

| CER ≥ VIH,

f=f

MAX

Com’l. 125 205 120 180 110 160 mA

Indust. 135 205 125 175 mA

I

SB3

Standby Current (Both

Ports CMOS Level) CE

L

&

CE

R

≥ V

CC

– 0.2V, f=0

Com’l. 0.05 0.25 0.05 0.25 0.05 0.25 mA

Indust. 0.05 0.25 0.05 0.25 mA

I

SB4

Standby Current (One Port

CMOS Level) CE

L

| CER ≥

V

IH

, f=f

MAX

[9]

Com’l. 115 185 110 160 100 140 mA

Indust. 125 175 115 155 mA

CY7C027/028

CY7C037/038

PRELIMINARY

6

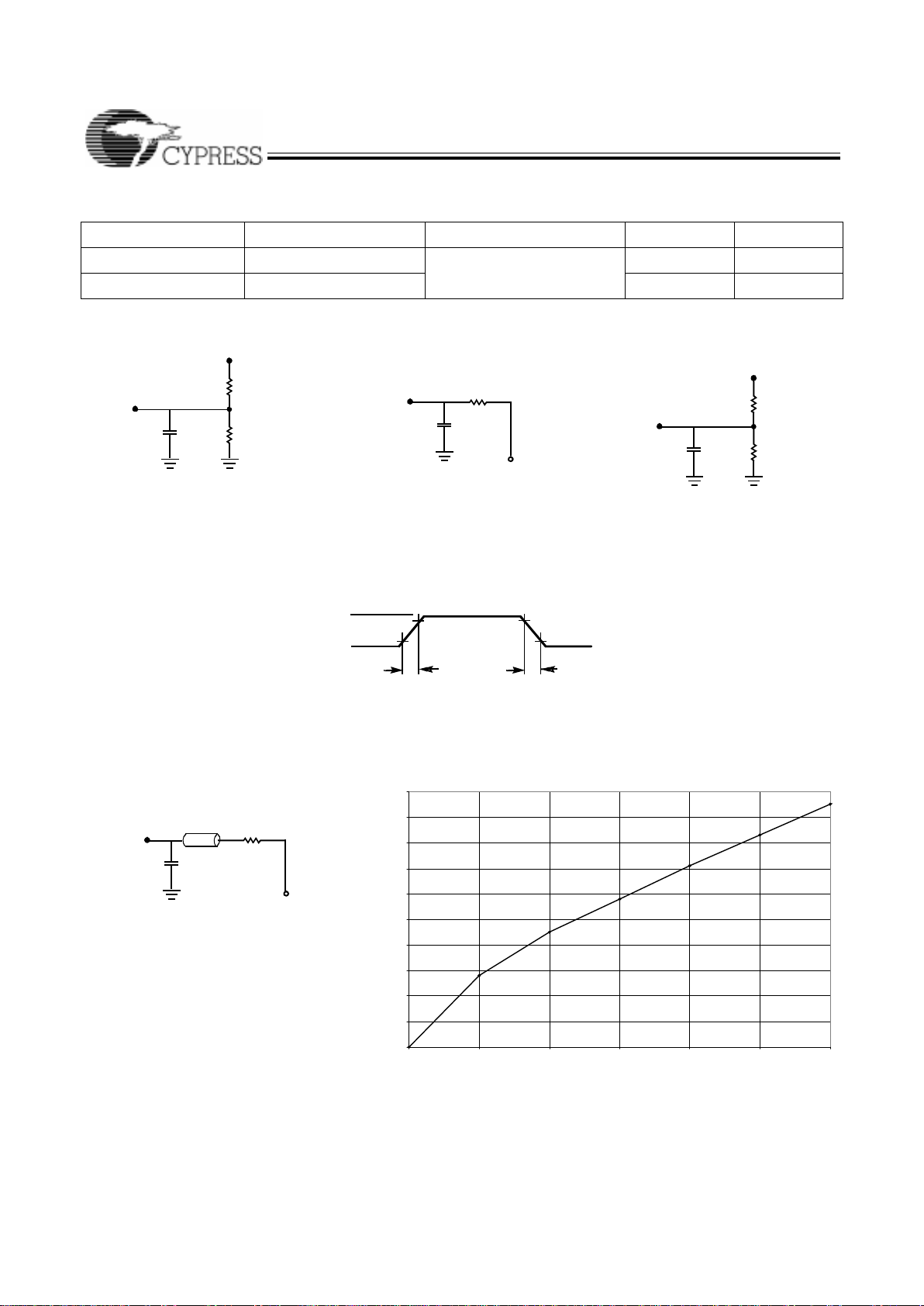

AC Test Loads (Applicable to -12 only)

[11]

Notes:

10. Tested initially and after any design or process changes that may affect these parameters.

11. Test Conditions: C = 0 pF.

Capacitance

[10]

Parameter Description Test Conditions Max. Unit

C

IN

Input Capacitance TA = 25°C, f = 1 MHz,

V

CC

= 5.0V

10 pF

C

OUT

Output Capacitance 10 pF

AC Test Loads and Waveforms

3.0V

GND

90%

90%

10%

3ns

3

ns

10%

ALL INPUT PULSES

(a) Normal Load( Load 1)

R1= 893

Ω

5V

OUTPUT

R2= 347

Ω

C= 30

pF

V

TH

=1.4V

OUTPUT

C=

30 pF

(b) Thévenin Equivalent (Load 1)

(c)Three-State Delay(Load 2)

R1= 893

Ω

R2= 347

Ω

5V

OUTPUT

C= 5pF

R

TH

=250

Ω

≤

≤

(Used for t

CKLZ

, t

OLZ

, & t

OHZ

including scope and jig)

VTH=1.4V

OUTPUT

C

(a) Load 1 (-12 only)

R = 50

Ω

(b) Load Derating Curve

Capacitance

(pF)

∆

(ns) for al l -12 access times

0.00

0.10

0.20

0.30

0.40

0.50

0.60

0.70

0.80

0.90

1.00

0 5 10 15 20 25 30

Z0 = 50

Ω

Loading...

Loading...