Cypress Semiconductor CY62138VLL-70BAIT, CY62138VLL-70BAI, CY62138VL-70BAI, CY62136VLL-70ZI, CY62136VLL-70BAIT Datasheet

...

256K x 8 Static RAM

CY62138V MoBL™

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

January 20, 2000

Features

• Low volt age range:

—2.7–3.6V

• Ultra-low active power

• Low st a ndby powe r

• Easy memory e xpansion with CS

1

/CS2 and OE feature s

• TTL-compatible inputs and outputs

• Autom atic power-dow n wh en deselected

• CMOS for optimum speed/power

Functional Description

The CY62138V is a high-performance CMOS static RAM organized as 262,144 words by 8 bits. This device features advanced circuit design to provide ultra-low active current. This

is ideal for providing More Battery Life™ (MoBL™) in portable

applications such as cellular telephones. The device also has

an automatic power-down feature that reduces power con-

sumption by 99% when addresses are not toggl ing. The devi ce

can be put into standby mode when deselected (CS

1

HIGH or

CS

2

LOW).

Writing to the device is accomplished by taking Chip Enable

One (CS

1

) and Write Enable (WE) inputs LOW and Chip En-

able Two (CS

2

) HIGH. Data on the eight I/O pins (I/O0 through

I/O

7

) is then written into the location specified on the address

pins (A

0

through A17).

Reading from the device is accomplished by taking Chip Enable One (CS

1

) and Output Enable (OE) LOW whil e forcing

Write Enable (WE

) and Chip Enable Two (CS2) HIGH. Under

these conditions, the contents of the memory location specified by the address pins will appear on the I/O pins.

The eight input/output pins (I/O

0

through I/O7) are placed in a

high-impedance state when the device is deselected (CS

1

HIGH or CS2 LOW), the outputs are disabled (OE HIGH), or

during a write oper ation ( CS

1

LOW , CS2 HIGH, and W E LOW) .

The CY62138V is available in a 36-ball FBGA.

More Battery Life and MoBL are trademarks of Cypress Semiconductor Corporation.

14

15

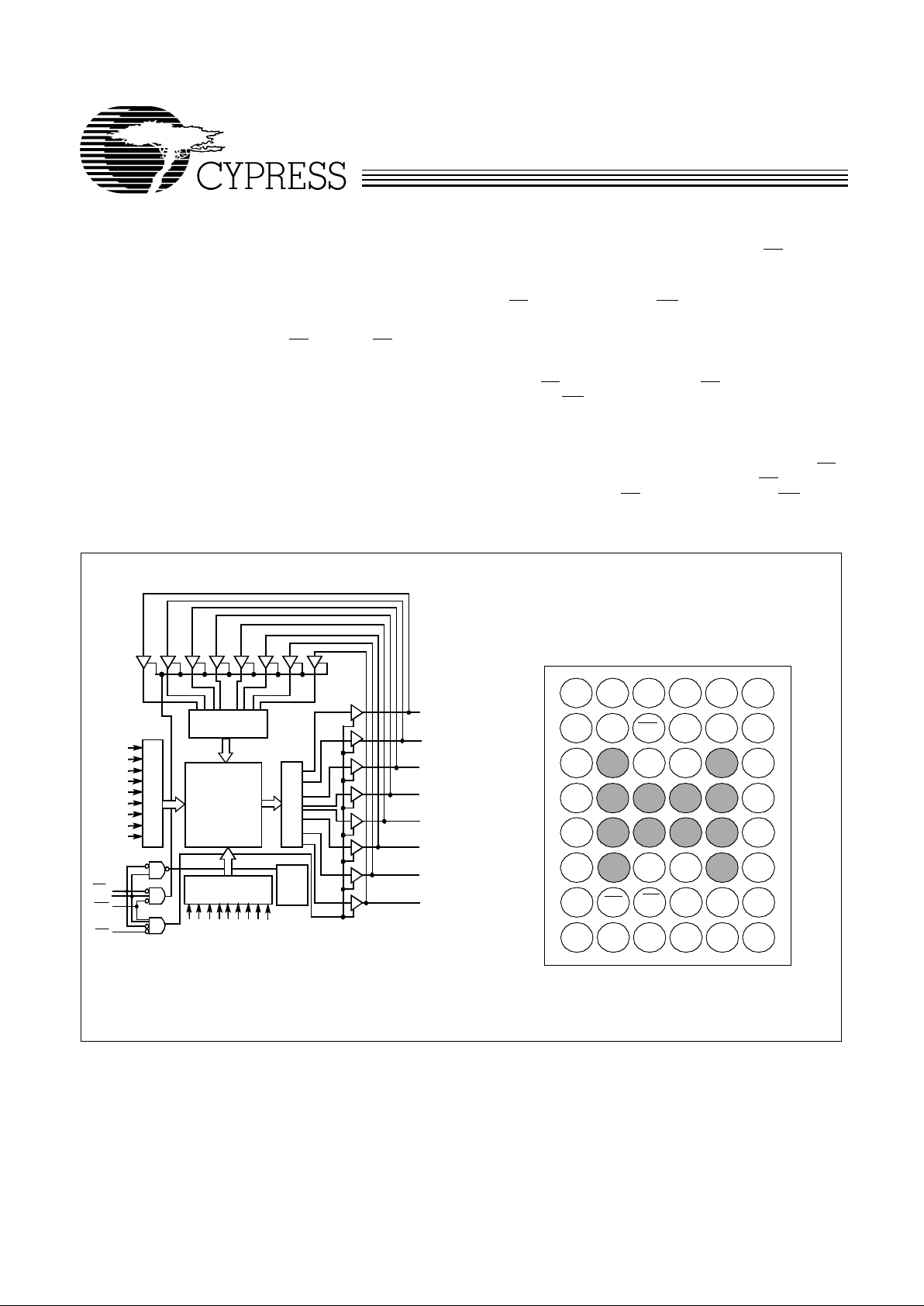

Logic Block Diagram

Pin Configuration

A

1

A

2

A

3

A

4

A

5

A

6

A

7

A

8

COLUMN

DECODER

ROW DECODER

SENSE AMPS

Data in Drivers

POWER

DOWN

WE

OE

I/O

0

CS

2

I/O

1

I/O

2

I/O

3

256K x 8

ARRAY

I/O

7

I/O

6

I/O

5

I/O

4

A

0

A

11

A13A

12

A

A

10

CS

1

A

A

16

A

9

62138V-1

17

A

A

V

CC

A

13

A

12

A

5

CS

2

WE

A

7

I/O

4

I/O

5

A

4

NC

I/O

6

I/O

7

V

SS

A

11

A

10

A

V

SS

I/O

0

A

A

8

A

6

A

3

A

V

CC

I/O

1

I/O

2

I/O

3

A

17

NC

A

16

CS

OE

A

9

A

14

62138V–2

365

4

D

E

B

A

C

F

G

H

TOP View

FBGA

12

1

15

0

1

2

CY62138V MoBL™

2

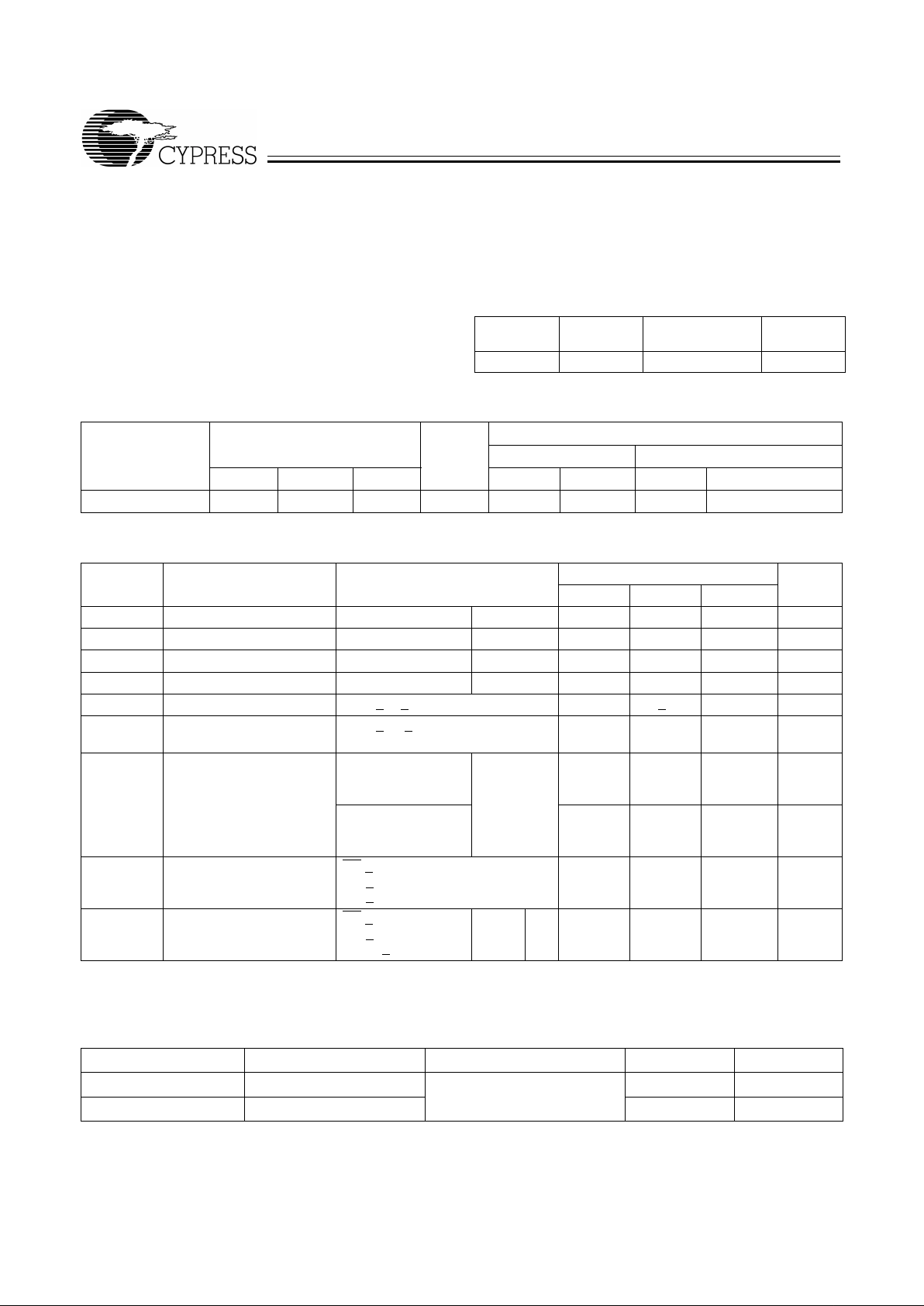

Maximum Ratings

(Above which the useful lif e m ay be impaired. For user guidelines, not tested.)

Storage Temperature .....................................−65°C to +15 0 °C

Ambient Temperature with

Po wer Applied..................................................−55°C to +125°C

Supply Voltage to Ground Potential..................−0.5V to +4.6V

DC V oltage Applied to Outputs

in High Z State

[1]

....................................... −0.5V to V

CC

+ 0.5V

DC Input Voltage

[1]

.................................... −0.5V to V

CC

+ 0.5V

Output Current into Outputs (LOW)............................. 20 mA

Static Discharge Voltage .......................................... >2001V

(per MIL-STD-883, Method 3015)

Latch-Up Current............. .. ............ .. ....................... >200 mA

Operating Range

Device Range

Ambient

Temperature V

CC

CY62138V Industrial

−40°C to +85°C

2.7V to 3.6V

Product Portfolio

VCC Range

Speed

Power Dissipation (Industrial)

Operating (Icc) Standby (I

SB2

)

Product V

CC(min)VCC(typ)

[2]

V

CC(max)

Typ.

[2]

Maximum Typ.

[2]

Maximum

CY62138V 2.7V 3.0V 3.6V 70 ns 7 mA 15 m A 1 µA 15 µA

Electrical Characteristics

Over the Operating Range

CY62138V

Parameter Description Test Conditions Min. Typ.

[2]

Max. Unit

V

OH

Outp ut HIGH Voltage IOH = −1.0 mA VCC = 2.7V 2.4 V

V

OL

Output LOW Voltage IOL = 2.1 mA VCC = 2.7V 0.4 V

V

IH

Input HIGH Voltage VCC = 3.6V 2.2 VCC + 0.5V V

V

IL

Input LOW Voltage VCC = 2.7V

−0.5

0.8 V

I

IX

Input Load Current GND < VI < V

CC

−1

+1 +1

µA

I

OZ

Output Leakage Current GND < VO < VCC, Output

Disabled

−1

+1 +1

µA

I

CC

VCC Operating Supply

Curr ent

I

OUT

= 0 mA,

f = f

MAX

= 1/t

RC,

CMOS Levels

VCC = 3.6V 7 15 mA

I

OUT

= 0 mA,

f = 1 MHz,

CMOS Levels

1 2 mA

I

SB1

Auto matic CE

Power-Down Current—

CMOS Inputs

CE > VCC − 0.3V,

V

IN

> VCC − 0.3V or

V

IN

< 0.3V, f = f

MAX

100

µA

I

SB2

Auto matic CE

Power-Down Current—

CMOS Inputs

CE > V

CC

−0.3V

V

IN

> V

CC

−0.3V

or V

IN

< 0.3V, f = 0

VCC =

3.6V

LL 1 15

µA

Notes:

1. V

IL

(min) = –2.0V for pulse durations less than 20 ns.

2. Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at V

CC

= VCC Typ, TA = 25°C.

Capacitance

[3]

Parameter Description Test Conditions Max. Unit

C

IN

Input Capacitance TA = 25°C, f = 1 MHz,

V

CC

= V

CC(typ)

6 pF

C

OUT

Output Capacitance 8 pF

Note:

3. Tested initially and after any design or process changes that may affect these parameters.

CY62138V MoBL™

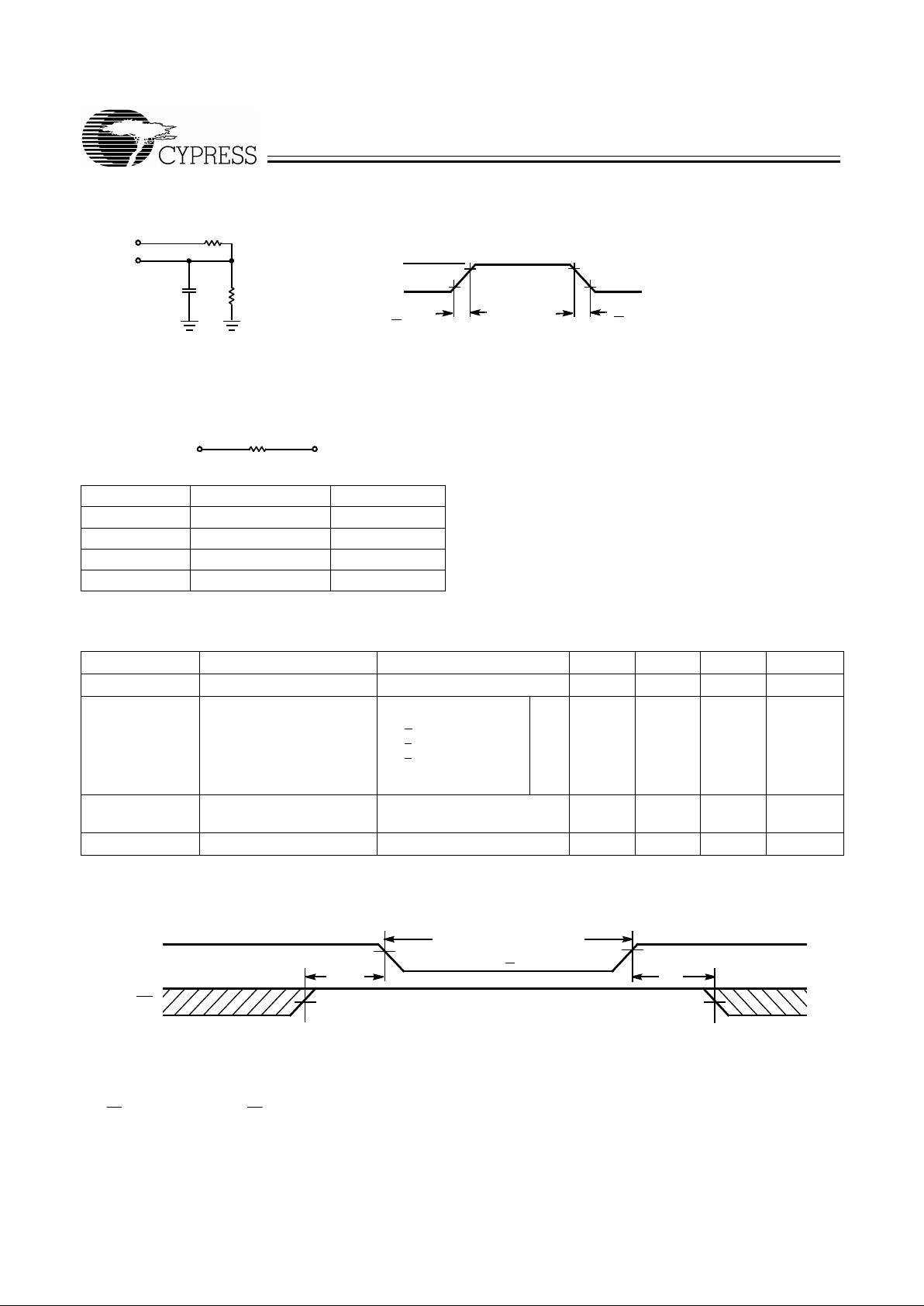

3

Notes:

4. T est conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V , input pulse lev els of 0 to V

CC

typ., and output loading of the specified

I

OL/IOH

and 30-pF load c apacitance.

5. CE

is the combination of both CS1 and CS2.

AC Test Loads and Waveforms

Parameters 3.0V Unit

R1 1105 Ohms

R2 1550 Ohms

R

TH

645 Ohms

V

TH

1.75 Volts

VCC Typ

V

CC

OUTPUT

R2

30 pF

INCLUDING

JIG AND

SCOPE

GND

90%

10%

90%

10%

<5ns

<5ns

OUTPUT V

Equivalent to: THÉ VENINEQUIVALENT

ALL INPUT PULSES

62138V–3

RTH

R1

62138V–4

Data Rete n ti o n C h ar acteristics

(Over the Operating Range)

Parameter Description Conditions

[4]

Min. Typ.

[2]

Max. Uni t

V

DR

VCC for Data Retention 1.0 3.6 V

I

CCDR

Data Retention Current V

CC

= 1.0V

CE >

VCC − 0.3V ,

V

IN

> VCC − 0.3V or

V

IN

< 0.3V

No input may exceed

V

CC

+0.3V

LL 0.1 5

µA

t

CDR

[3]

Chip Deselect to Data

Retention Time

0 ns

t

R

Operation Recovery Time 100

µs

Data Retention Waveform

[5]

62128V–5

V

CC(min.)

V

CC(min.)

t

CDR

VDR> 1.0V

DATA RETENTION MODE

t

R

CE

V

CC

Loading...

Loading...