Desktop/Notebook Frequency Generator

W48S87-72

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

August 4, 2000 rev. *A

Features

• Maximized EMI suppression usi ng Cypress’s Spread

Spectrum technology

• ±0. 5 % Spread S pectru m cl o ck i n g

• Equivalent to the W 48S67-72 wit h Spread Spect rum f or

Tilamook, MMO, and Deschutes processors

• Generates system clocks for CPU , I OAPIC, SDRAM,

PCI, USB plus 14.318-MHz (REF0:1)

• Serial data inte rface (SDA T A, SCLOCK inputs ) provides

additional CPU/PCI clock fr equency selections, individual output clock disabling and other functions

• MODE input pin selects optional power management

input control pins (reconfigures pins 26 and 27)

• T wo fixed outputs separately selectabl e as 24-MHz or

48-MHz (default = 48-MHz)

•V

DDQ3

= 3.3V±5%, V

DDQ2

= 2.5V±5%

• Uses exte rnal 14.318-MHz crystal

• Available in 48-pin SSOP (300 mils)

•

10Ω CPU output impedance

Note:

1. Additional frequency selections provided by serial data interface; refer to

Tabl e 5

on page 8.

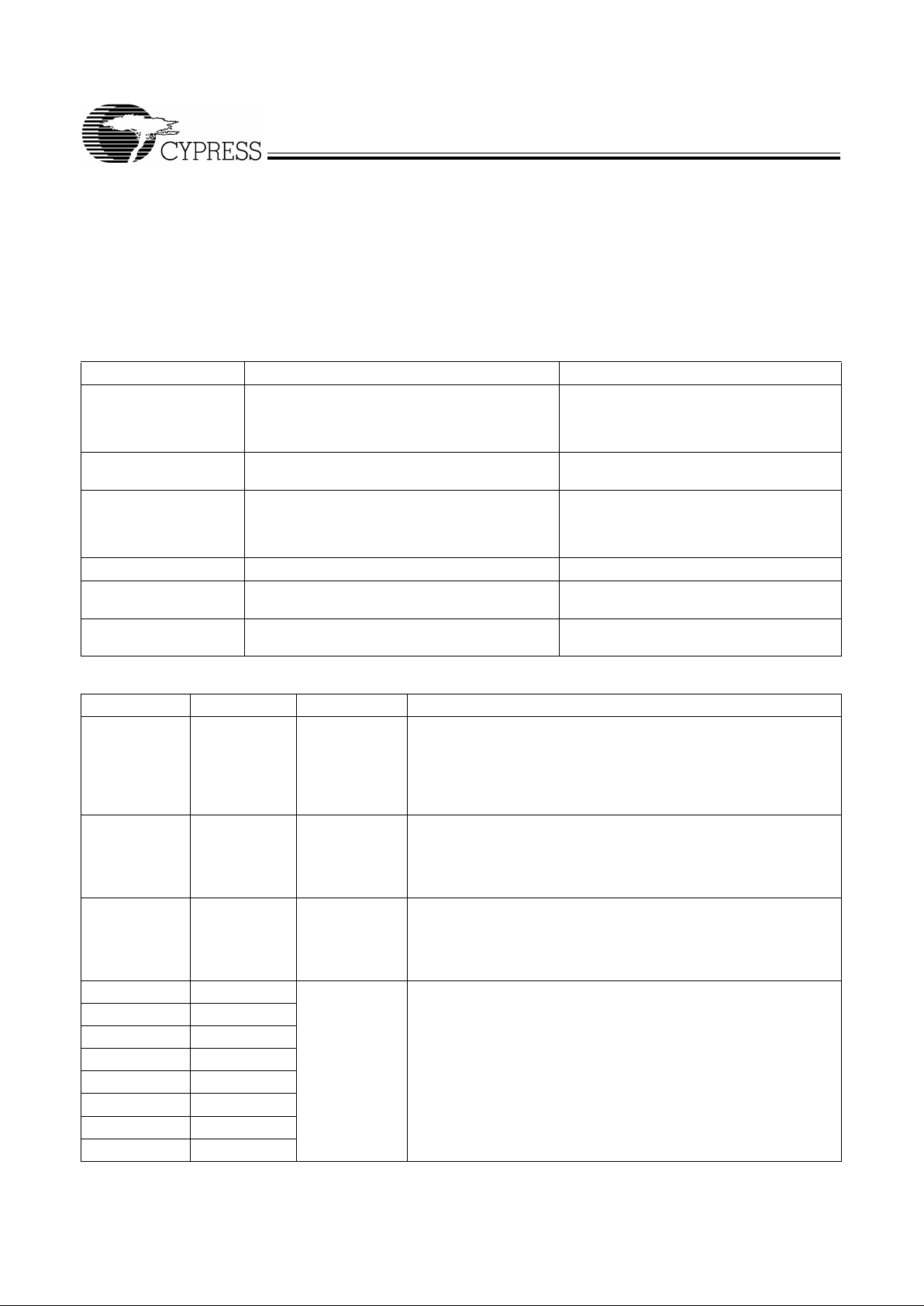

T able 1. Pin Selectable Frequency

[1]

60/66_SEL

CPU, SDRAM

Clocks (MHz)

PCI Clocks

(MHz)

06030

1 66.8 33.4

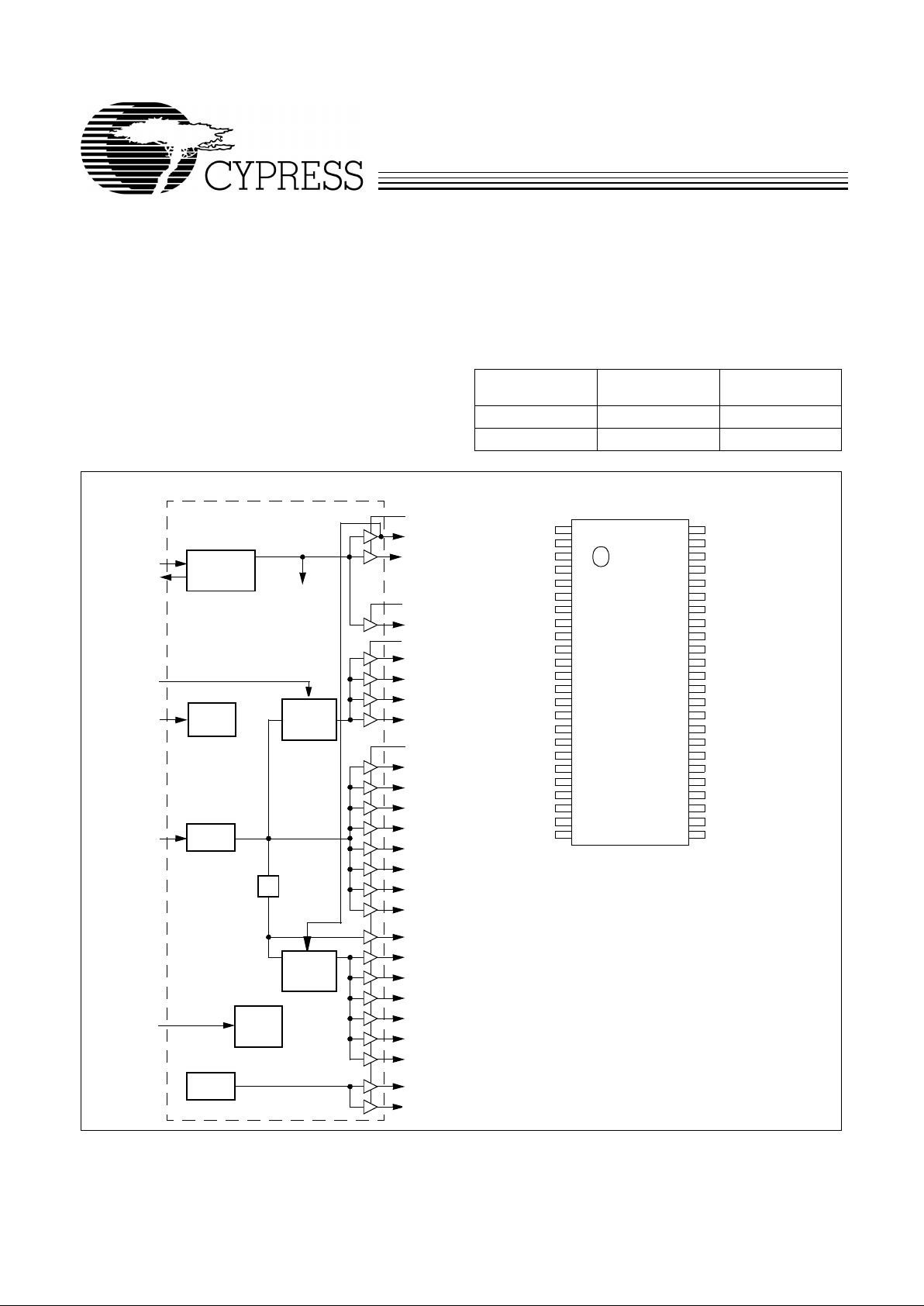

Block Diagram

Pin Configuration

VDDQ3

REF0

VDDQ2

IOAPIC

CPU0

CPU1

CPU2

CPU3

SDRAM0

SDRAM1

SDRAM2

SDRAM3

SDRAM4

SDRAM5

SDRAM6

SDRAM7

PCI_F

PCI0

XTAL

PLL Ref Freq

PLL 1

60/66_SEL

MODE

X2

X1

REF1

VDDQ3

Stop

Output

Control

Stop

Output

Control

PCI1

PWR_DWN#

Power

Down

Control

PCI2

PCI3

PCI4

PCI5

48/24MHZ

48/24MHZ

PLL2

÷2

OSC

I/O

Control

VDDQ2

CPU_STOP#

REF1

REF0

GND

X1

X2

MODE

VDDQ3

PCI_F

PCI0

GND

PCI1

PCI2

PCI3

PCI4

VDDQ3

PCI5

GND

60/66_SEL

SDATA

SCLOCK

VDDQ3

48/24MHZ

48/24MHZ

GND

W48S87-72

VDDQ3

CPU2.5#

VDDQ2

IOAPIC

PWR_DWN#

GND

CPU0

CPU1

VDDQ2

CPU2

CPU3

GND

SDRAM0

SDRAM1

VDDQ3

SDRAM2

SDRAM3

GND

SDRAM4

SDRAM5

VDDQ3

SDRAM6/CPU_STOP#

SDRAM7/PCI_STOP#

VDDQ3

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

W48S87-72

2

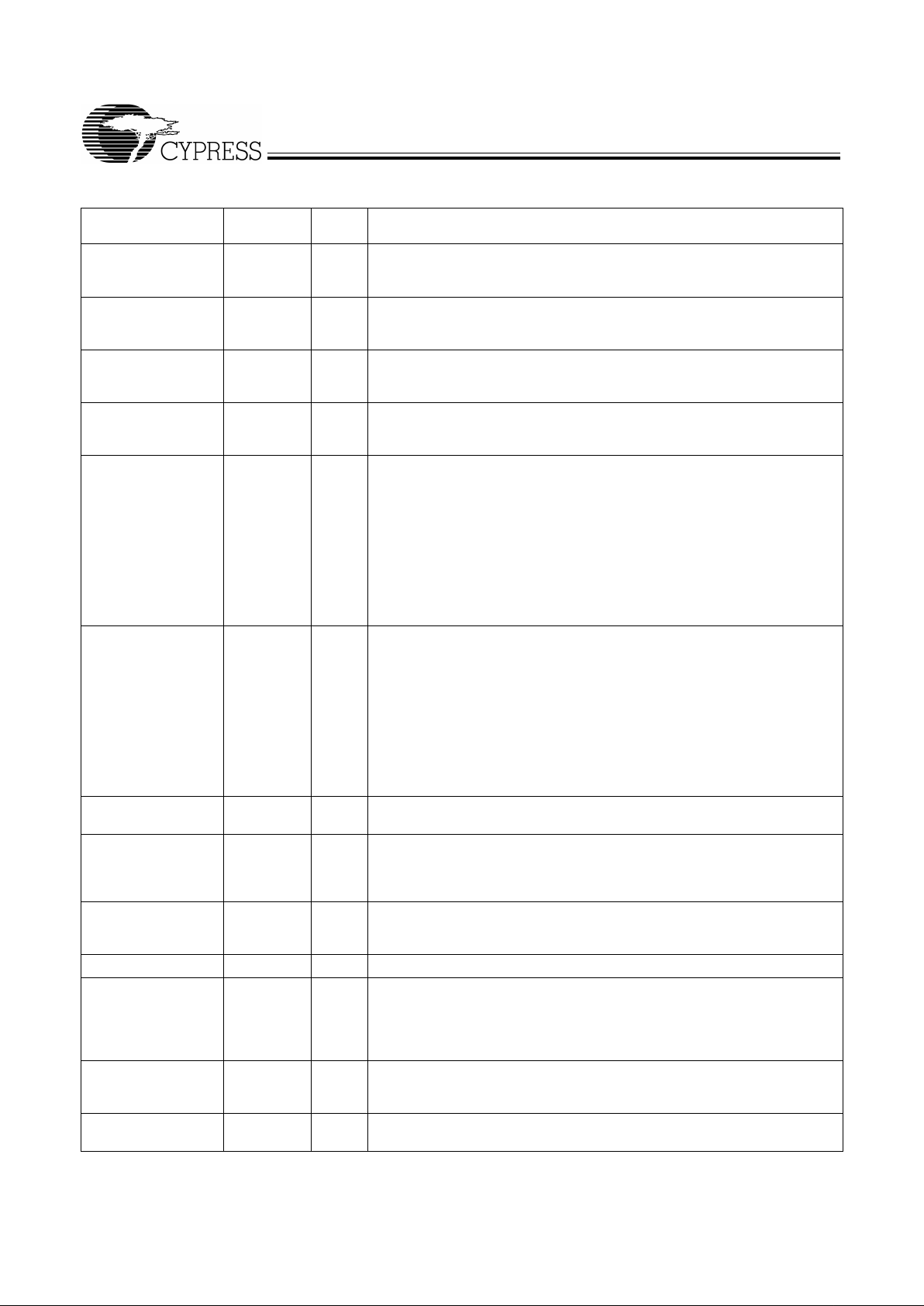

Pin Definitions

Pin Name

Pin

No.

Pin

Type Pin Description

CPU0:3 42, 41, 39, 38O

CPU Outputs 0 through 3:

These four CPU outp uts are controlled by the

CPU_STOP# co ntrol pin. Out put volt age swi ng is controll ed by vol tage appli ed

to VDDQ2.

PCI0:5 9, 11, 12,

13, 14, 16

O

PCI Bus Outputs 0 through 5:

These six PCI outputs are controlled by the

PCI_STO P# control pin. Output voltage swing is controlled by voltage applied

to VDDQ3.

PCI_F 8 O

Free Running PCI Output:

Unlike PCI0:5 out puts, t his output is not controll ed

by the PCI_STOP# control pin. Output voltage swing is controlled b y voltage

applied to VDDQ3.

SDRAM0:5 36, 35, 33,

32, 30, 29

O

SDRAM Clock Outputs 0 through 5:

These six SDRAM clock output s run

synchronous to the CPU clock outputs. Output voltage swing is controlled by

voltage applied to VDDQ3.

SDRAM6/

CPU_STOP#

27 I/O

SDRAM Clock Output 6 or CPU Clock Output Stop Control :

This pin has

dual functions, selectable by the MODE input pin. When MODE = 0, this pin

becomes the CPU_STOP# inpu t. When MODE = 1, thi s pin becomes SDRAM

clock output 6.

Regarding use as a CPU_STOP# input: When brought LOW, clock outputs

CPU0:3 are stopped LOW after completing a ful l cl ock cycle (2–3 CPU clock

latency). When brought HIGH, clock outputs CPU0:3 are st arted beginning with

a full clock cycle (2–3 CPU clock latenc y).

Regarding use as a SDRAM cloc k: Output voltag e swing is controlled b y voltage

applied to VDDQ3.

SDRAM7/

PCI_STOP#

26 I/O

SDRAM Clock Output 7 or PCI Clock Output Stop Control:

This pin has

dual functions, selectable by the MODE input pin. When MODE = 0, this pin

becomes the PCI_STOP# input. When MO DE = 1, this pin becomes SDRAM

clock output 7.

PCI_STO P# input: When br ought LOW , clock out puts PCI0:5 are st opped LOW

after completing a full clock cycl e. When brought HIGH, cloc k outputs PCI0:5

are started beginning with a full cloc k cycle . Clock latency provides one PCI_F

rising edge of PCI cloc k followi ng PCI_STOP# state change.

Regarding use as a SDRAM cloc k: Output voltag e swing is controlled b y voltage

applied to VDDQ3.

IOAPIC 45 O

I/O APIC Clock Output:

Provides 14.3 18-MHz fixed frequency. The output

voltage swing is controlled by VDDQ2.

48/24MHz 22, 23 O

48-MHz / 24-MHz O utpu t:

Fixed cloc k outputs that def ault to 48 MHz f ollo wing

device po w er-up. Either or both can be cha nged to 24 MH z through use of the

serial data interface (Byte 0, bits 2 and 3). Output voltage s wing is controlled

by voltage applied to VDDQ3

REF0:1 2, 1 O

Fixed 14.318- MHz Outputs 0 through 1:

Used for various system applications. Output voltage swing is controlled by voltage applied to VDDQ3. REF0

is stronger than REF1 and should be used for driving ISA slo ts.

CPU_2.5# 47 I Set to logic 0 for V

DDQ2

= 2.5V (0 to 2.5V CPU output swing).

60/66_SEL 18 I

60- or 66-MHz Input Sel ection:

Selects power -up default CPU cloc k frequency

as shown in Table 1 on page 1 (also determines SDRAM and PCI clock frequency selecti ons). Can be used to change CPU clock frequen cy while de vice

is in operation if serial data port bits 0–2 of Byte 7 are logic 1 (defa ult powerup condition).

X1 4 I

Crystal Connection or External Reference Frequency Input:

This pin has

dual functions. It can be used as an ext ernal 14. 318-MHz crystal connection

or as an external reference frequency input.

X2 5 I

Crystal Connect ion:

An input conn ect ion f or an e xt ernal 14. 318-M Hz crystal .

If using an e xternal reference, this pin must be left unconnec ted.

W48S87-72

3

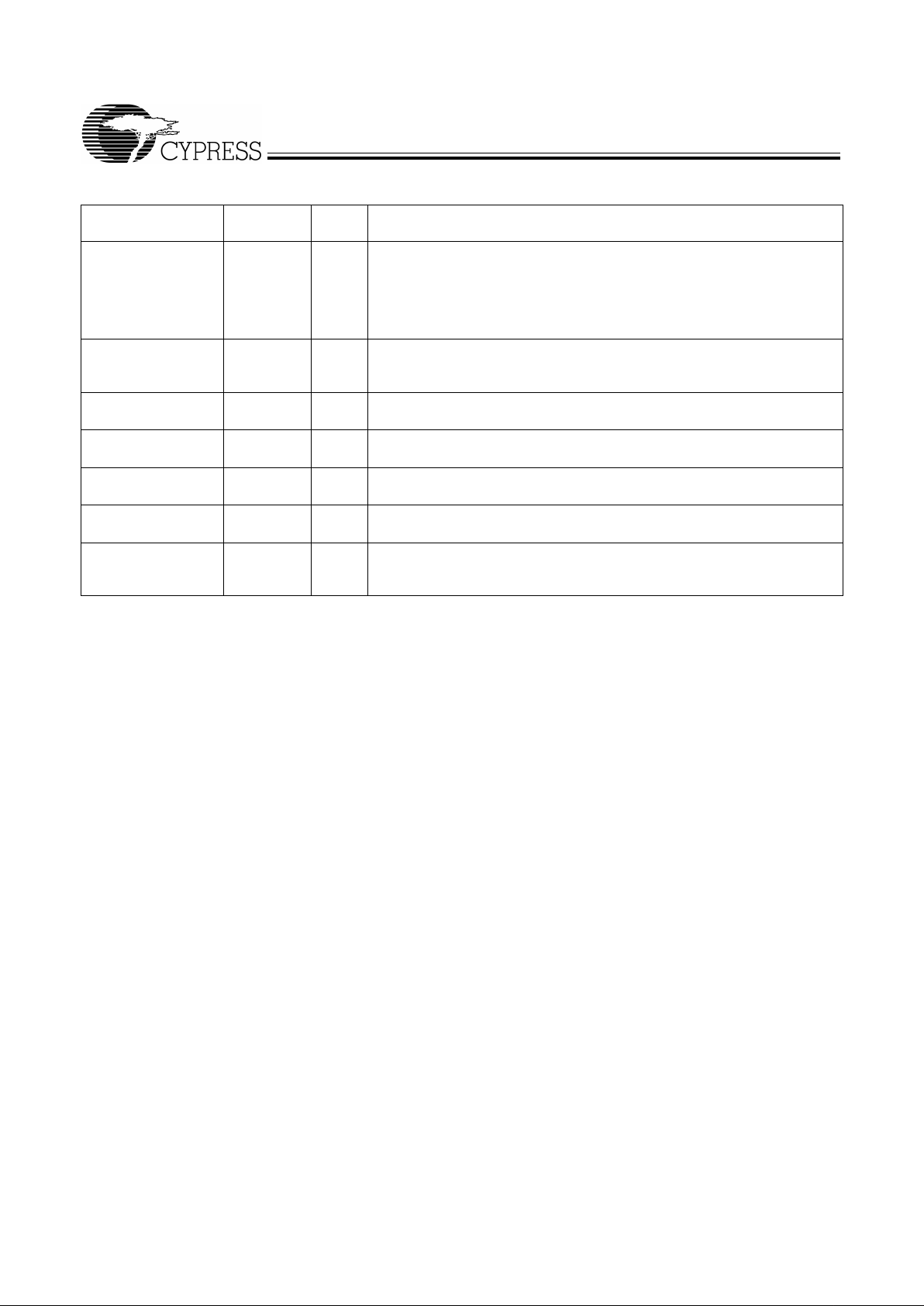

PWR_DWN# 44 I

Power-Down Con tro l:

When this input is LOW, the device goes into a lowpower standby condition. All outputs are activel y held LOW while in power down. CPU, SDRAM, and PCI clock out puts are stopped LOW after completing

a full clock cycle (2–4 CPU clock cycle l atency). When brought HIGH, CPU,

SDRAM, and PCI out puts start with a full clock cycle at full oper ating f requency

(3 ms maximum latency).

MODE 6 I

Mode Control:

This input selects the function of dev ice pin 26

(SDRAM7/PCI_ST OP#) and pin 27 (SDRAM6/CPU_ST OP#). Refer to des cription fo r those pins.

SDATA 19 I/O

Serial Data Input:

Data input for Serial Data Interface. Refer to Serial Data

Interface section that follows.

SCLOCK 20 I

Serial Clock Input:

Clock input for Serial Data Interface. Refer to Serial Data

Interface section that follows.

VDDQ3 7, 15, 21, 25

28, 34, 48

P

Po wer Connectio n:

Pow er supply f or PCI0:5, REF0:1, and 48/24MHz output

buffers. Connected to 3.3V supply.

VDDQ2 46, 40 P

Po wer Connection:

Power supply for IOAPIC0, CPU0:3 output buffer. Con-

nected to 2.5V supply.

GND 3 , 1 0 , 17,

24, 31, 37,

43

G

Ground Connection :

Connect all ground pin s to the comm on system gr ound

plane.

Pin Definitions

(continued)

Pin Name

Pin

No.

Pin

Type Pin Description

W48S87-72

4

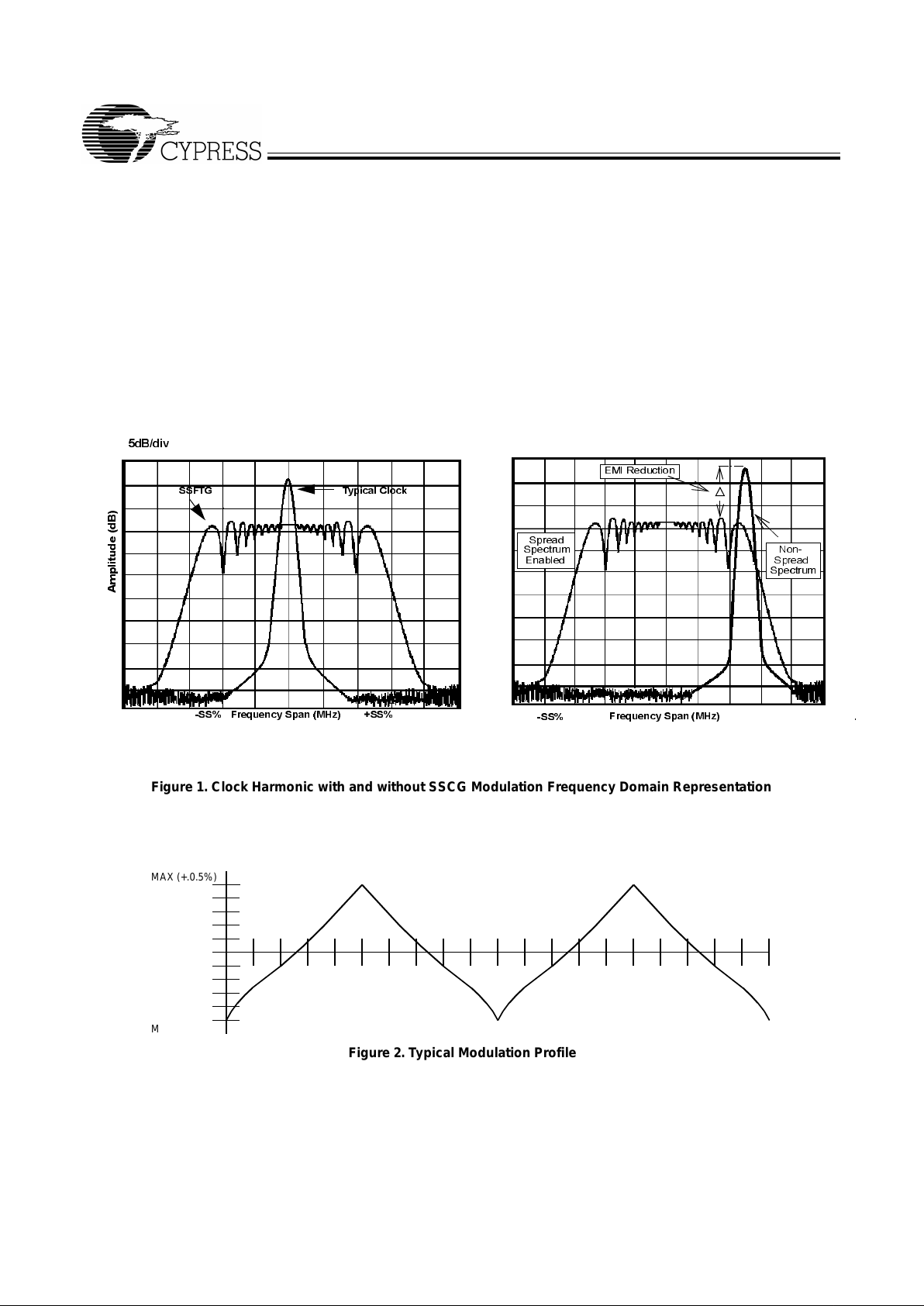

Spread Sp ectrum Ge n er ator

The device generates a clock that is frequency modulated in

order to increase the bandwidth that it occu pies. By increas ing

the bandwidth of the fundamental and its harmonics, the amplitudes of the radiated electromagnetic emissions are reduced. This effect is depicted in Figure 1.

As depicted in Figure 1, a harmonic of a modulated clock has

a much lower amplitude than that of an unmodulated signal.

The reduction in am plitude is dependen t on the harmonic number and the frequency deviation or spread. The equation for

the reductio n is

dB = 6.5 + 9*log

10

(P) + 9*log10(F)

Where P is the percent age of de v iati on and F is the freq uency

in MHz where the reduction is measured.

The output clock is modulated with a waveform depicted in

Figure 2. This waveform, as discussed in “Spread Spectrum

Clock Gener ation f or the Redu ct ion of Radiat ed Emiss ions” by

Bush, Fessler, and Hardin produces the maximum reduction

in the amplitude of radiated electromagnetic emissions. The

deviati on select ed f or thi s chip is ±0. 5% of the center frequen cy. Figure 2 details the Cypress spreading pattern. Cypress

does offer options with more spread and greater EMI reduction. Contact your local Sales representative for details on

these devices.

Spread Spectrum clocking is activated or deactivated by selecting the appropriate v al ues fo r bits 1–0 in data byte 0 of the

I

2

C data stream. Refer to Ta ble 4 for more details.

66)7* 7\SLFDO &ORFN

)UHTXHQF\ 6SDQ 0+]66 66

$PSOLWXGH G%

G%GLY

6SUHDG

6

S

HFWUXP

(QDEOHG

(0, 5HGXFWLRQ

6SHFWUXP

)UHTXHQF\ 6SDQ 0+]

1RQ

6

S

UHDG

66

Figure 1. Clock Harmonic wit h and without SSCG Modulation Frequency Domain Represent ation

Figure 2. Typical Modulation Profil e

MAX (+.0.5%)

MIN. (–0.5%)

10%

20%

30%

40%

50%

60%

70%

80%

90%

100%

10%

20%

30%

40%

50%

60%

70%

80%

90%

100%

FREQUENCY

W48S87-72

5

Serial Data Interface

The W48S87-72 features a two-pin, serial data interface that

can be used to configure internal register settings that control

particular device functions. Upon power-up, the W48S87-72

initiali zes wit h defau lt regist er setti ngs, t heref ore the use of this

serial data interface is optional. The serial interface is writeonly (to the clock chip) and is the dedicated function of de vice

pins SDATA and SCLOCK. In motherboard applications,

SDATA and SCLOCK are typically driven by two logic outputs

of the chipset. Clock device register changes are normally

made upon system init iali zati on, if any are r equire d. The int erface can also be us ed during system oper ation f or power management functions. Ta ble 2 summarizes the control functions

of the serial data interface.

Operation

Data is written to the W48S87-72 in ten bytes of eight bits

each. Bytes are written in the ord er shown in Table 3 .

Table 2. Serial Data Interface Control Functions Summary

Control Function Description Common Application

Clock Output Disa ble Any indivi dual clock output(s) can be disabled. Dis-

abled outputs are actively held LOW.

Unused outputs are disabled to reduce EMI

and system power. Examples are clock outputs to unused SDRAM DIMM socket or PCI

slot.

48-/24-MHz Cloc k Output

Frequency Selection

48-/24-MHz clock outputs can be set to 48 MHz or

24 MHz.

Provides flexibility in Super I/O and USB device selectio n.

CPU Clock Frequency

Selection

Provides CPU/PCI fr equency selections be yond the

60- and 66.6-MHz selections that are provided by

the SEL60/66 input pin. F req uency is changed i n a

smooth and controlled fashion.

For alternate CPU devices, and power management options. Smooth frequency transition allows CPU fr equency ch ange un der nor-

mal system operati on.

Output Three-state Puts all clock outputs into a high-impedance state. Production PCB testing.

Test Mode All clock outputs toggle in relation with X1 input ,

internal PLL is bypassed. Refer to Table 4.

Production PCB testing.

(Reserved) Reserved fu nction for future device re vision or pro-

duction device testing.

No user application . Regist er bit must be wri t-

ten as 0.

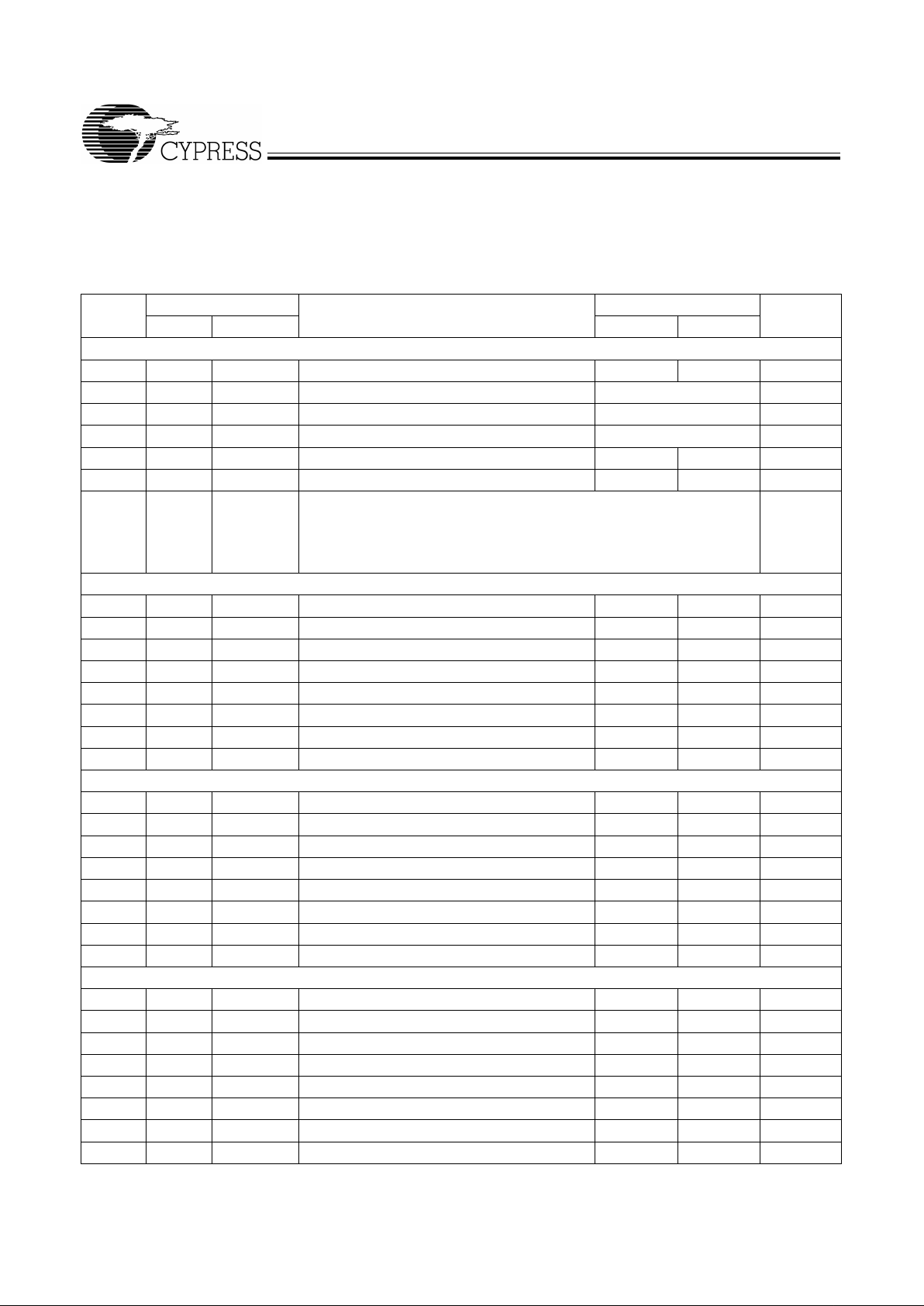

Table 3. Byte Writing Sequence

Byte Sequence Byte Name Bit Sequence Byte Description

1 Slave Address 11010010 Commands the W48S87-72 to accept the bits in Data Bytes 0–7 for

internal register configuration. Since other devices may exist on the

same common serial data bus, it is necessary to hav e a specific slave

address for each potential receiver. The slave recei ver address for the

W48S87-72 is 11010010. Register setti ng will not be made if the Sl av e

Address is not correct ( or is for an alternate slave receiver).

2 Command

Code

Don’t Care Unused by the W48S87-72, the refore bit values are ignored (don’t c are).

This byte m ust be incl uded in the dat a write sequence to maintain pro per

byte allocati on. The Command Code Byt e is part of the standard serial

communication protocol and may be used when writing to another addressed slave receiver on the seri al data bus.

3 Byte Count Don’t Care Unused by the W48S87-72, the refore bit values are ignored (don’t c are).

This byte m ust be incl uded in the dat a write sequence to maintain pro per

byte allocation. The Byte Coun t Byte is part of the standard serial communication protocol and may be used when writing to anot her addressed slave receiver on the seri al data bus.

4 Data Byte 0 Refer to Table 4 The data bits in Data Bytes 0–7 set internal W48S87-72 registers that

control de vice operation. The data bits are only accepted when the Address Byte bit sequence is 11010010, as noted abov e. For descrip ti on

of bit control functions, ref er t o Ta ble 4 , Data Byte Serial Configuration

Map.

5 Data Byte 1

6 Data Byte 2

7 Data Byte 3

8 Data Byte 4

9 Data Byte 5

10 Data Byte 6

11 Data Byte 7

W48S87-72

6

Writing Data Bytes

Each bit in the data bytes control a particular device function

excep t for the “reserved” bits which must be written as a logic

0. Bits are written MSB (most significant bit) first, which is bit

7. Ta bl e 4 gives the bit formats for registers located in Data

Bytes 0–7.

Table 5 details additional frequency selections that are available through t he seri al dat a interface .

Table 6 details the select functions for Byte 0, bits 1 and 0.

Table 4. Data Bytes 0–7 Serial Configuration Map

Bit(s)

Affected Pin

Control Function

Bit Control

DefaultPin No. Pin Name 0 1

Data Byte 0

7-- --(Reserved) -- -- 0

6 -- -- (Reserved) Refer to Table 5 0

5 -- -- SEL_4 Refer to Table 5 0

4 -- -- SEL_3 Refer to Table 5 0

3 23 48/24MHZ 48-/24-MHz Clock Output Frequency Selection 24 MHz 48 MHz 0

2 22 48/24MHZ 48-/24-MHz Clock Output Frequency Selection 24 MHz 48 MHz 0

1–0 -- -- Bit 1 Bit 0 Function (See Table 6 for function details)

0 0 Normal Operation

0 1 Test Mode

1 0 Spread Spec trum On

1 1 All Outputs Three-stated

00

Data Byte 1

7 23 48/24MHZ Cl ock Output Disable Low Active 1

6 22 48/24MHZ Cl ock Output Disable Low Active 1

5-- --(Reserved) -- -- 0

4-- --(Reserved) -- -- 0

3 38 CPU3 Clo ck O utput Disable L ow Active 1

2 39 CPU2 Clo ck O utput Disable L ow Active 1

1 41 CPU1 Clo ck O utput Disable L ow Active 1

0 42 CPU0 Clo ck O utput Disable L ow Active 1

Data Byte 2

7-- --(Reserved) -- -- 0

6 8 PCI_F Clock Output Dis able L ow Active 1

5 16 PCI5 Clo ck O u t p ut Disable Low Active 1

4 14 PCI4 Clo ck O u t p ut Disable Low Active 1

3 13 PCI3 Clo ck O u t p ut Disable Low Active 1

2 12 PCI2 Clo ck O u t p ut Disable Low Active 1

1 11 PCI1 Clo ck O u t p ut Disable Low Active 1

0 9 PCI0 Clock Output Disable Low Active 1

Data Byte 3

7 26 SDRAM7 Clock Output Disable Low Active 1

6 27 SDRAM6 Clock Output Disable Low Active 1

5 29 SDRAM5 Clock Output Disable Low Active 1

4 30 SDRAM4 Clock Output Disable Low Active 1

3 32 SDRAM3 Clock Output Disable Low Active 1

2 33 SDRAM2 Clock Output Disable Low Active 1

1 35 SDRAM1 Clock Output Disable Low Active 1

0 36 SDRAM0 Clock Output Disable Low Active 1

Loading...

Loading...