Cypress W48C111-17H Datasheet

PRELIMINARY

100-MHz Mobile Motherboard System Clock

W48C111-17

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

Novembe r 2, 1999, rev. **

Features

• Maximized EMI suppression usi ng Cypress’s Spread

Spec t r u m techno logy

• Power-on default to spread mode

• T wo copies of CPU output

• Six copies of PCI output (synchr onous w/CPU outputs)

• One copy of 48-MHz USB output

• One Buffered copy of 14.318-MHz input reference signal

• Supports 100-MHz or 66-MHz CPU operation

• Power man agem ent control input pins

• Low Frequency Test Mode

• Av ail able in 28-pin SSOP (209 mil)

Key Specific ati o n s

Supply Voltages:.......................................V

DDQ3

= 3.3V±5%

V

DDQ2

= 2.5V±5%

CPU0: 1 S kew: ....... ... ......... ... .. .......... .. ... ......... ... .. .......175 p s

CPU0: 1 C y cl e- to - C yc le Ji tt er: ....................... .. ... .........20 0 p s

PCI_ F, PCI1:5 Skew : ..... ... .. .......... .. ... .......... .. .............. 5 0 0 ps

PCI_ F, PCI1:5 Cyc le -to-Cycl e Jit te r: . .. .......... .. ... .........250 p s

CPU to PCI Skew: ........................ 1.5 to 4.0 ns (CPU Leads)

Output Duty Cycle: .................................................... 45/55%

PCI_F, PCI Edge Rate :.............................. ............... .>

1 V/ns

CPU_STOP#, PWR_DWN#, PCI_STOP#: 250-kΩ pull-up

resistor

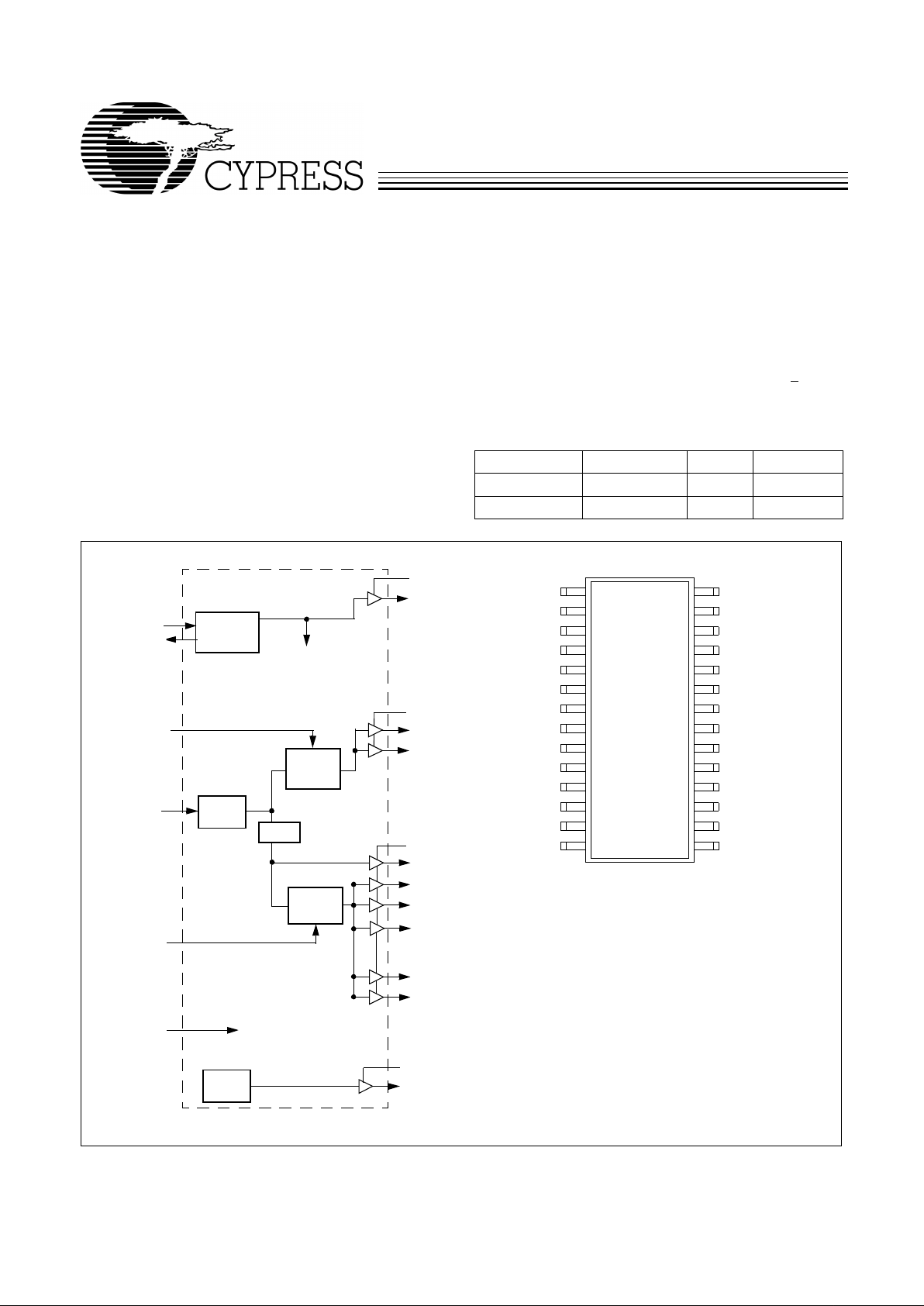

T able 1. Pin Selectable Frequency

SEL100/66# CPU(0:1) PCI Spread%

0 66.6 MHz 33.3 –0.5%

1 100 MHz 33.3 –0.5%

Pin ConfigurationBlock Diagram

GND

VDDQ3

REF

VDDQ2

CPU0

CPU1

GND

VDDQ3

GND

PCI_STOP#

CPU_STOP#

PWR_DWN#

48MHz

SEL100/66#

28

27

26

25

24

23

22

21

20

19

18

17

16

15

X1

X2

GND

PCI_F

PCI1

VDDQ3

PCI2

PCI3

VDDQ3

PCI4

PCI5

GND

VDDQ3

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

VDDQ3

REF

CPU0

CPU1

PCI_F

XTAL

PLL Ref Freq

PLL 1

SEL100/66#

X2

X1

VDDQ3

Stop

Signal

Control

Stop

Signal

Control

PCI1

PWR_DWN#

Power

Down

Control

PCI2

PCI3

PCI4

PCI5

÷2/÷3

OSC

VDDQ2

PCI_STOP#

CPU_STOP#

PLL 2

48MHz

VDDQ3

W48C111-17

PRELIMINARY

2

Pin Definitions

Pin Name

Pin

No.

Pin

Ty pe Pin Description

CPU0:1 24, 23 O

CPU Clock Outputs 0 and 1:

These two CPU clock out puts are controlled by th e

CPU_STOP# control pin. Output volta ge swing is controlle d by voltage applied to

VDDQ2. Frequency of signals is set by SEL100/66# input.

PCI1:5 5, 7 , 8 , 10, 11O

PCI Bus Clock Outputs 1 through 5:

These five PCI clock outputs are controlled

by the PCI _ST OP# contr ol p in. Outpu t v ol tage s wing is co ntr olled b y v olt age applied

to VDDQ3.

PCI_F 4 O

Fixed PCI Clock Output:

Unlike PCI1:5 outputs, this output is not controlled by the

PCI_STOP# control pin; it cannot be forced LOW by PCI_STOP#. Output voltage

swing is controlled by voltage applied to VDDQ3.

48MHz 16 O

48-MHz Output:

Fixed cloc k output at 48 MHz. Out put vol tage swi ng is contr olled b y

voltage applied to VDDQ3.

CPU_STOP# 18 I

CPU_STOP# Input:

When brought LOW, clock outputs CPU0:1 are stopped LOW

after completi ng a full clock cycl e (2–3 CPU clock latency). When brought HIGH,

clock outputs CPU0:1 start with a full clock cycle (2–3 CPU cl o ck l a te ncy).

PCI_STOP# 19 I

PCI_STOP# Input:

The PCI_STOP # input enables the PCI1:5 outputs when HIGH

and causes them to remain at logi c 0 when LOW. The PCI_STOP signal is latched

on the rising edge of PCI_F. Its effect takes place on the next PCI_F clock cycle.

REF 26 O

Fixed 14.318-MHz Output:

Used for various system applications. Output voltage

swing is controlled by voltage applied to VDDQ3.

SEL100/66# 15 I

Frequency Selection Inputs:

Select power -up default CPU clock frequency as

shown in Table 1 on page 1.

X1 1 I

Crystal Connection or External Reference Frequency Input:

This pin can either

be used as a connection to a crystal or to a reference signal.

X2 2 I

Crystal Connection:

An input connection for an external 14.318-MHz crystal. If

using an external reference, this pin must be left unconn ected.

PWR_DWN# 17 I

Power- Down Control:

When this input is LO W, de vi ce goes in to a l ow-po wer standby conditio n. All outputs are held LO W. CPU and PCI clock outputs are st opped LOW

after completi ng a full clock cycl e (2–3 CPU clock cycle latency). When brought

HIGH, CPU and PCI outputs start with a full cloc k cycle at full operating f requency

(3 ms maximum latency).

VDDQ3 6, 9, 13, 21, 27P

Power Connecti on:

Connected to 3.3V supply.

VDDQ2 25 P

Power Connecti on:

Power supply for CPU0:1 output buffer. Connected to 2.5V.

GND 3, 12, 14, 20,

22, 28

G

Ground Connection:

Connect all gro und pins t o the common s yst em g round pl an e.

W48C111-17

PRELIMINARY

3

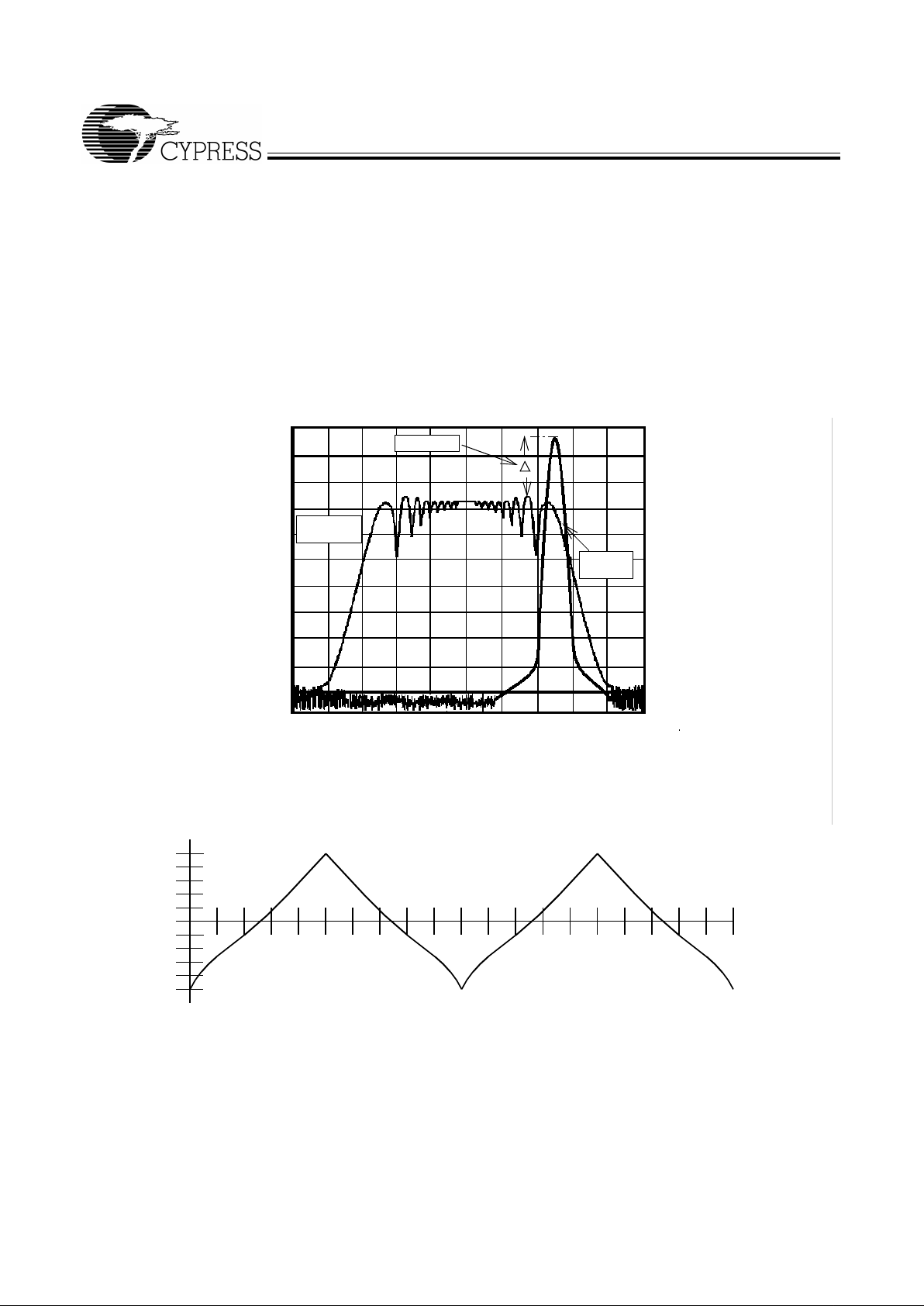

Spread Sp ectrum Feat u re

The device generates a clock that is frequency modulated in

order to increase the bandwidth that it occu pies. By increas ing

the bandwidth of the fundamental and its harmonics, the amplitudes of the radiated electromagnetic emissions are reduced. This effect is depicted in Figure 1.

As shown in Figure 1, a harmonic of a modulated clock has a

much low er amplitude th an that of an un modulated si gnal. The

reduction in amplitude is dependent on the harmonic number

and the frequency deviation or spread. The equation for the

reduction is:

dB = 6.5 + 9*log

10

(P) + 9*log10(F)

Where P is the perce nta ge of de viati on and F is the frequen cy

in MHz where the reduction is measured.

The output clock is modulated with a waveform depicted in

Figure 2. This waveform, as discussed in “Spread Spectrum

Clock Generation f or the Reducti on of Radiated Emissio ns” by

Bush, Fessler, and Hardin produces the maximum reduction

in the amplitude of radiated electromagnetic emissions. The

deviati on select ed for this chi p is –0.5% of the cente r frequency. Figure 2 details the Cypress spreading pattern. Cypress

does offer options with more spread and greater EMI reduction. Contact your local Sales representative for details on

these devices.

Spread

Spectrum

Enabled

EMI Reduction

Spread

Spectrum

Non-

Figure 1. Typi cal Clock and SSFTG Compari son

MAX (+0.5%)

MIN (–0.5%)

10%

20%

30%

40%

50%

60%

70%

80%

90%

100%

10%

20%

30%

40%

50%

60%

70%

80%

90%

100%

FREQUENCY

Figure 2. Typica l Modulation Profile

Loading...

Loading...