Cypress W210H Datasheet

W210

Spread Spectrum FTG for VIA K7 Chipset

Features

• Maximized EMI Suppression usi ng Cypress’s Spread

Spec trum te chnol ogy

• Single-chi p system frequency synthesizer for VIA K7

chipset

• One pair of different ial CPU outputs for K7 Processor

• One open-drain CPU output for VIA K7 chips et

• Six copies of PCI output

• One 48-MHz output for USB

• One 24-MHz or 48-MHz output for SIO

• T wo buffered reference outputs

• Thirteen SDRAM outputs provide support for 3 DIMMs

• Supports frequencies up to 200 MHz

2

•I

C™ interface for programming

• Power man agement control inputs

• Available in 48-pin SSOP

Key Specific ati o n s

CPU to CPU Output Skew:.... .. ................................... 175 ps

PCI to PCI Output Skew:...................... ...................... 500 ps

: .................................................................... 3.3V±5%

V

DDQ3

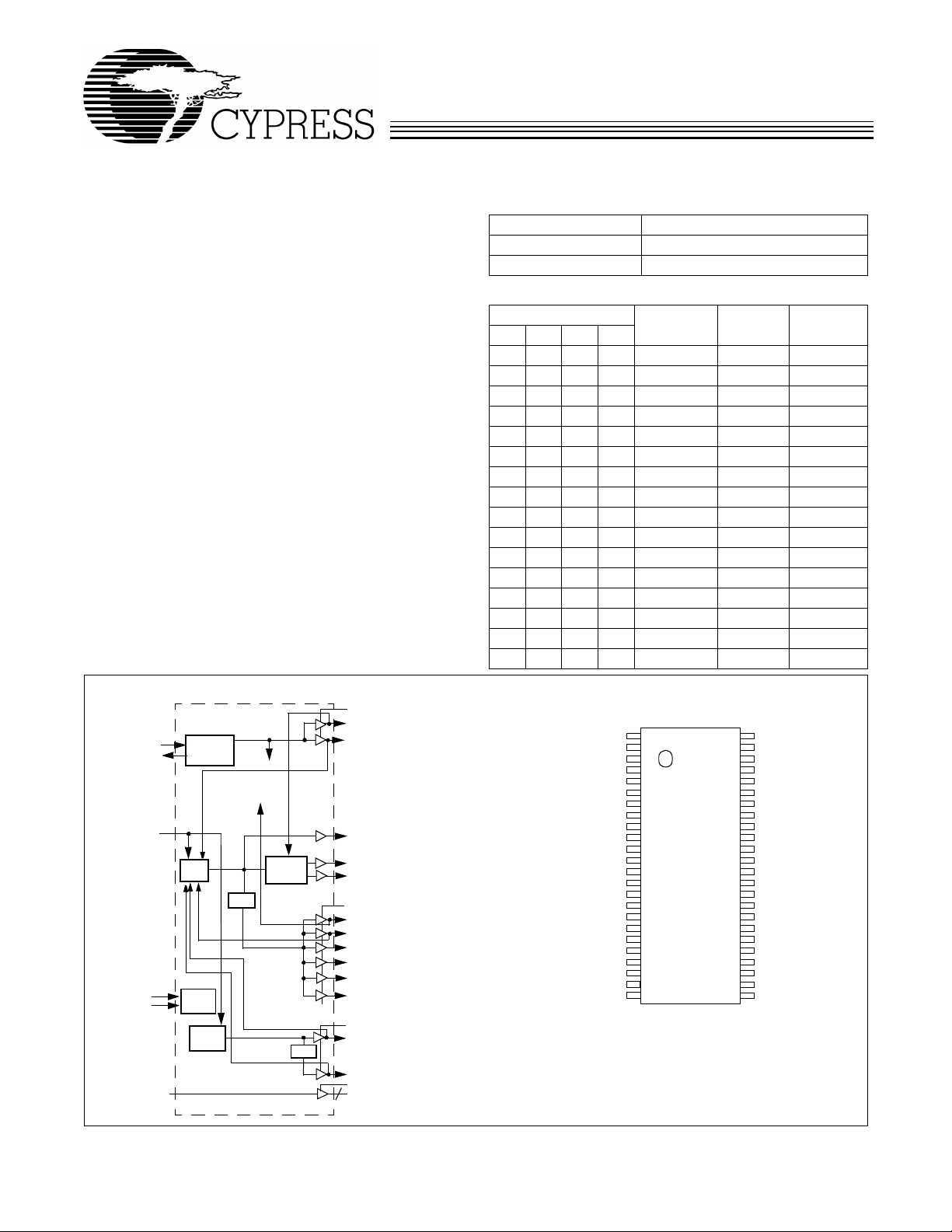

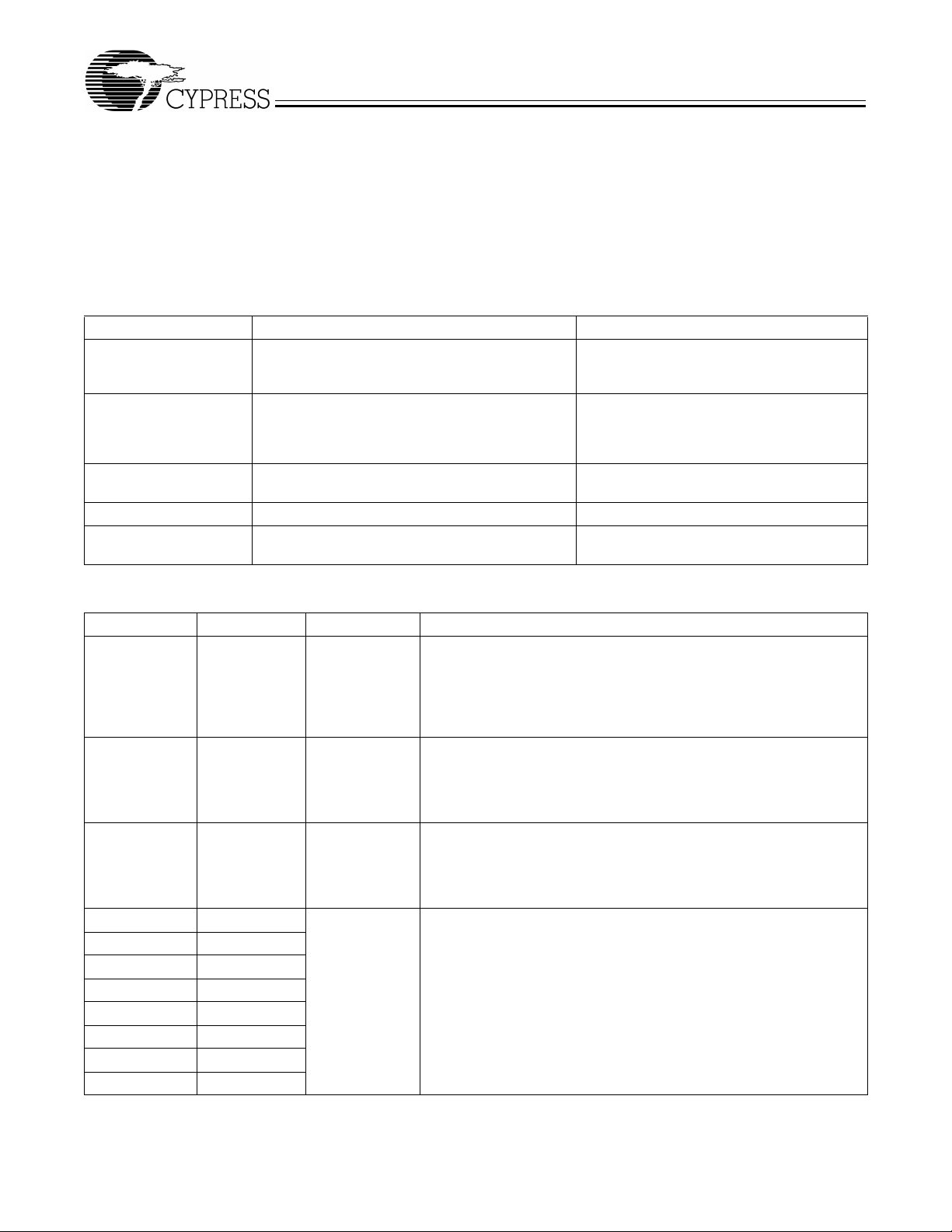

T able 1. Mode Input Table

Mode Pin 2

0 CPU_STOP#

1REF0

T able 2. Pin Selectable Fre quency

Input Address

CPU

(MHz)

PCI0:5

(MHz)

Spread

SpectrumFS3 FS2 FS1 FS0

1 1 1 1 133.3 33.3 ±0.5%

1 1 1 0 75 37.5 ±0.5%

1 1 0 1 100.2 33.3 ±0.5%

1 1 0 0 66.8 33.4 ±0.5%

1 0 1 1 79 39.5 OFF

1 0 1 0 110 36.7 OFF

1 0 0 1 115 38.3 OFF

1 0 0 0 120 30 OFF

0 1 1 1 133.3 33.3 OFF

0 1 1 0 83.3 27.7 OFF

0 1 0 1 100.2 33.3 OFF

0 1 0 0 66.8 33.4 OFF

0 0 1 1 124 31.0 OFF

0 0 1 0 129 32.3 OFF

0 0 0 1 138 34.5 OFF

0 0 0 0 143 35.8 OFF

Block Diagram

X1

X2

PWRDWN#

SDA TA

SCLK

SDRAMIN

I2C is a trademark of Philips Corporation.

PLL 1

I2C

Logic

PLL2

XTAL

OSC

÷2,3,4

PLL Ref Freq

I/O Pin

Control

Control

Stop

Clock

Pin Configuration

VDDQ3

REF0/(CPU_STOP#)

REF1/FS0

CPUT_CS

CPUT0

CPUC0

VDDQ3

PCI0/MODE

PCI1/FS1

PCI2

PCI3

PCI4

PCI5

VDDQ3

÷2

48MHz/FS2

24_48MHz/FS3

VDDQ3

SDRAM0:12

13

REF0/(CPU_STOP#)

Note:

1. Internal pull-up resistors should not be relied upon for setting I/O

VDDQ3

GND

X1

X2

VDDQ3

PCI0/MODE

PCI1/FS1*

GND

PCI2

PCI3

PCI4

PCI5

VDDQ3

SDRAMIN

GND

SDRAM11

SDRAM10

VDDQ3

SDRAM9

SDRAM8

GND

SDA TA

I2C

{

SCLK

pins HIGH. Pin function with parentheses determined by MODE pin

resistor strapping. Unlike other I/O pins, input FS3 has an internal

pull-down resistor.

[1]

REF1/FS0*

W210

48

GND

47

CPUT_CS

46

GND

45

44

CPUC0

43

CPUT0

VDDQ3

42

41

PWRDWN#*

SDRAM12

40

GND

39

SDRAM0

38

SDRAM1

37

VDDQ3

36

SDRAM2

35

SDRAM3

34

GND

33

SDRAM4

32

SDRAM5

31

VDDQ3

30

SDRAM6

29

SDRAM7

28

VDDQ3

27

48MHz/FS2*

26

24_48MHz/FS3^

25

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

April 11, 2000, rev. *C

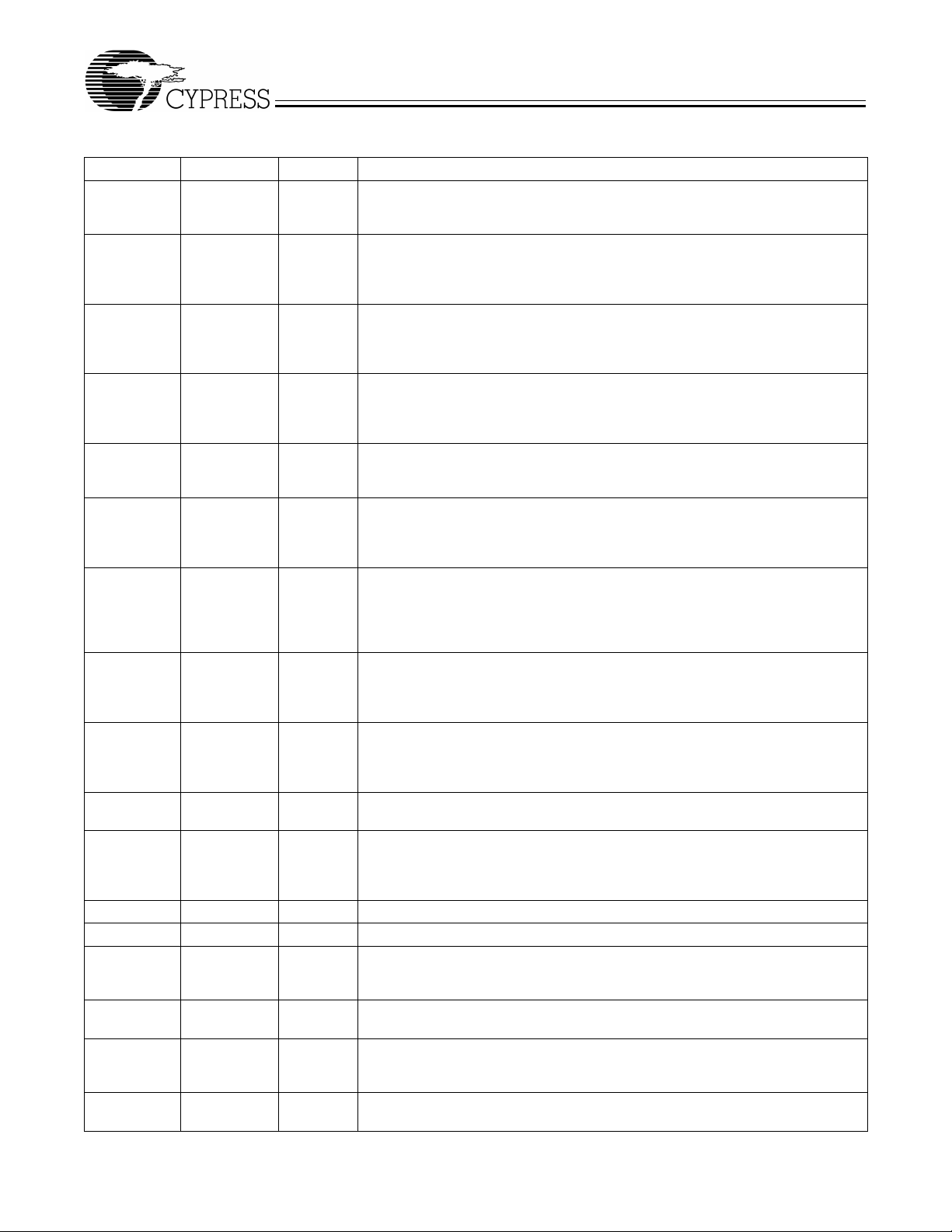

Pin Definitions

Pin Name Pin No. Pin Type Pin Description

CPUT0,

CPUC0,

CPUT_CS

PCI2:5 10, 11, 12, 13 O

PCI1/FS1 8 I/O

PCI0/MODE 7 I/O

PWRDWN# 41 I

48MHz/FS2 26 I/O

24_48MHz/

FS3

REF1/FS0 48 I/O

REF0/

CPU_STOP#

SDRAMIN 15 I

SDRAM0:12 38, 37, 35,

SCLK 24 I Clock pin for I

SDATA 23 I/O Data pi n for I

X1 4 I

X2 5 I

VDDQ3 1, 6, 14, 19,

GND 3, 9, 16, 22,

43, 44, 46 O

(open-

drain)

25 I/O

2 I/O

O

34, 32, 31,

29, 28, 21,

20, 18, 17, 40

P

27, 30, 36, 42

G

33, 39, 45, 47

CPU Clock Output 0:

for the K7 proc essor. CPUT_CS is the open-drain cl ock output for the chips et. It

has the same phase relat ionship as CPUT0.

PCI Clock Outpu ts 2 through 5:

the PWRDWN# control pin. Frequency is set by FS0:3 inputs or through serial

input interface, see Tables 2 and 6 for details. Output voltage swing is controlled

by volt age applied to VDDQ3.

Fixed PCI Clo ck Output/Frequency Select 1:

FS0:3 inputs or through serial input interface. This output is controlled by the

PWRDWN# input. This pin also serves as a power-on strap opt ion to determine

device operating frequency as describe d in Table 2.

Fixed PCI Cloc k Output/Mode:

or through serial inp u t i nterface, see Tables 2 and 6. This output is controlled by

the PWRDWN# input. This pin also serves as a power -on strap option to determine

the function of pin 2, see Table 1 for details.

PWRDWN# Input :

mode when held LOW. In power-down mode,CPUC0 will be three-stated and all

the other output clocks will be driven LOW.

48-MHz Output/Fr equency Se lec t 2:

standard PC systems, this output can be used as the reference for the Uni versal

Serial Bus host control ler. This pin also serves as a power-on strap option to

determine device operating frequency as desc ribe d in Table 2.

24_48-MHz Outpu t/Frequency Sel ect 3:

be used as the clock input f or a Super I/O chip . The output frequency is controlled

by Configur ation Byte 3 bit[6]. The defaul t out put frequency is 24 MHz. This pin

also serves as a power -on strap option to determine device operating frequency

as described in Table 2.

Reference Cloc k Output 1/Frequency Sel ect 2:

This pin also serves as a power-on strap option to dete rmine device operating

frequency as described in Table 2. Upon power-up, FS0 input will be latched, which

will set clock frequencies as described in Table 2.

Reference Cloc k Output 0 or CPU_STOP# Input Pin:

by the MODE pin. When CPU_ST OP# inp ut is asse rted LOW, it will drive CPUT0

and CPUT_CS to l ogic 0, and it will three -state CPUC0. When this pin i s configured

as an output, this pin becom es a 3.3V 14. 318-MHz output clock.

Buffered Input Pin:

(SDRAM0:12).

Buffered Outputs:

provided at the SDRAMIN input. The swing is set by VDDQ3, and they are deactivated when PWRDWN# input is set LOW.

2

C circuitry.

2

C circuitry .

Crystal Connection or Ext ernal Ref erence Frequenc y Input:

functions . It can be used as an external 14.318-MHz crystal con nection or as an

external reference frequency input.

Crystal Connection:

using an external reference, this pin must be left unconnected.

Power Connection:

PCI outputs, ref erence outp uts, 48-MHz ou tput, and 24_4 8-MHz ou tpu t. Connect

to 3.3V supp ly.

Ground Connections:

plane.

CPUT0 and CPUC0 are the differ ential CPU cl oc k output s

These four PCI clock outputs are controlled by

As an output, frequency is set by the F S0:3 inputs

LVTTL-compatibl e inpu t that place s t he de vi ce in po we r-do wn

48 MHz is provi ded in normal operat ion. In

The signal pr ovide d t o this input pin i s buf f ere d to 13 outp uts

These thirteen d edicat ed outpu ts prov ide cop ies of t he sig nal

An input connection for an external 14.318-MHz crystal. If

Power supply for core logic, PLL circuitry, SDRAM outputs,

Connect all ground pins to the common system ground

W210

As an output, frequency is set by

In standard PC systems, th is output can

3.3V 14.318-MHz output clock.

Function is determined

This pin has dual

2

W210

Overview

The W210 was developed as a single-chip device to meet the

clockin g needs of VIA K7 c ore logic chi p sets. I n addition t o the

typical ou tputs provided by a standard FTG, the W210 adds a

thirteenth output buff er, supporting SDRAM DIMM modules in

conjunction with the chipset.

Cypress’s proprietary spread spectrum frequency synthesis

technique is a feature of the CPU and PCI outputs. When enabled, th is feat ure reduces the peak EMI measurement s of not

only the output signals and their harmonics, but also of any

other clock signals that are properly synchr onized to them.

Functional Description

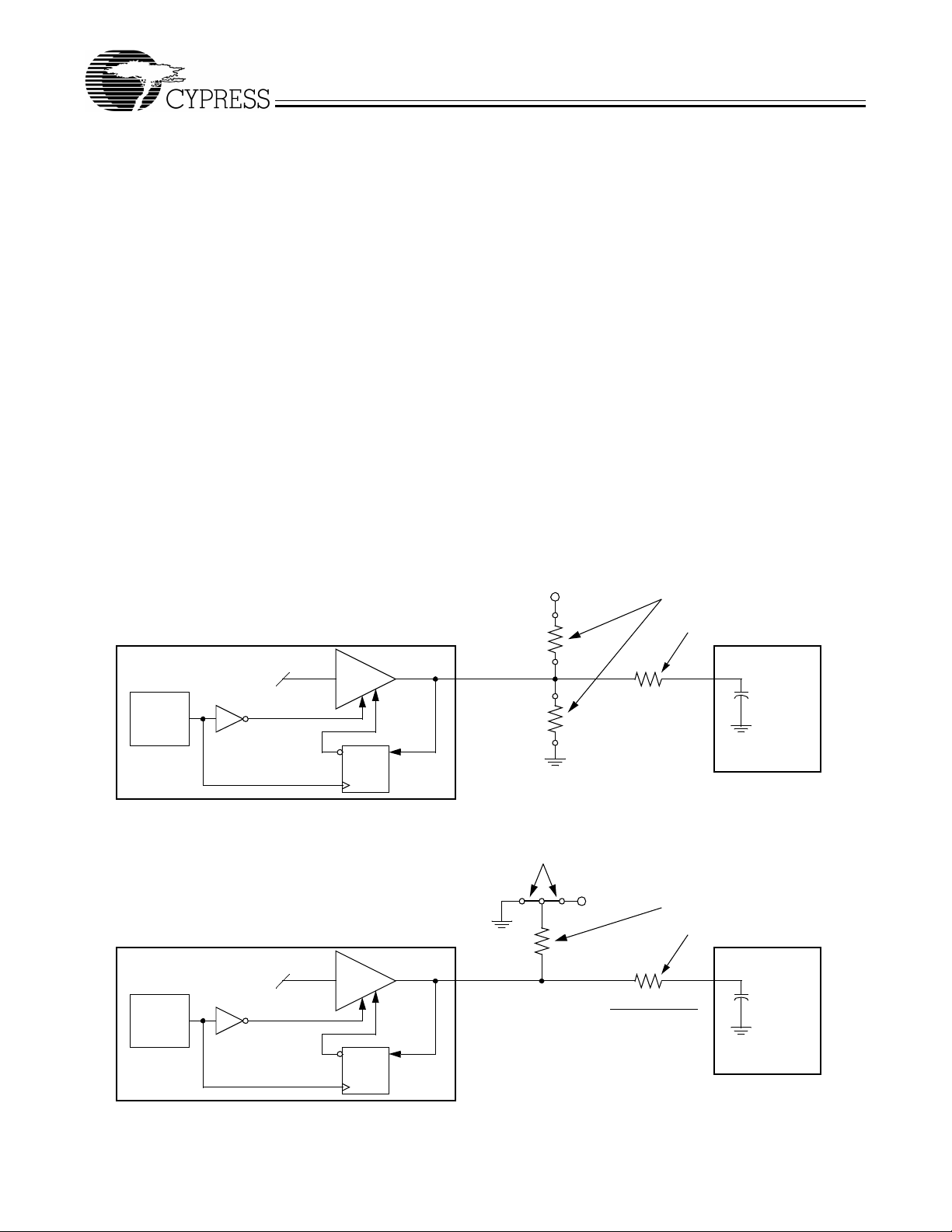

I/O Pin Operation

Pins 7, 8, 25, 26, and 48 are dual-purpose l/O pins. Upon

power-up these pins act as logic inputs, allowing the determination of assigned device functions. A short time after powerup, the logic state of each pin is latched and the pins becom e

clock outputs. This feature reduces device pin count by combining cloc k outputs with input select pins .

An external 10-kΩ “strapping” resistor is connected between

the l/O pin and ground or V

latch to “0,” connection to V

Figure 2 show two suggested methods for strapping resistor

connections.

. Connection to ground sets a

DD

sets a latch to “1.” Fig ure 1 an d

DD

Upon W210 power-up, the first 2 ms of operation is used for

input logic selection. During this period, the five I/O pin s (7, 8,

25, 26, 48) are three-stated, allowing the output strapping resistor on the l/O pins to pull the pins and their associated capacitiv e clock load to either a logic HIGH or LOW state. At the

end of the 2-ms period, the established logic “0” or “1” condition of the l/O pin is latched. Next the output buffer is enabl ed

converting t he l/O pins into operating clock outputs. The 2-ms

timer starts w hen V

be reset by turning V

reaches 2.0V. The input bits can only

DD

off and then back on again.

DD

It should be noted that the strapping resistors have no significant effect on clock output signal integrity. The drive impedance of clock outputs is <40Ω (nominal), which is minimally

affected by the 10-kΩ strap to ground or V

ries termination resistor, the output strapping resistor should

. As with the se-

DD

be placed as close to the l/O pin as possible in order to keep

the interconnecting trace short. The trace from the resistor to

ground or V

should be ke pt less t han tw o i nches i n lengt h t o

DD

prevent system noise coupling during input l ogic sampling.

When the clock outputs are enabled following the 2-ms input

period, the specified output frequency is delivered on the pin,

assuming that V

full value , output frequency initi ally ma y be belo w target b ut will

increase to target once V

case, a shor t output clock cycle may be produced from the

has stabilized. If VDD has not yet reached

DD

voltage has stabilized. In either

DD

CPU clock outputs when the outputs are enabled.

V

DD

Output Stra pp i ng Resi st or

W210

Power-on

Reset

Timer

W210

Power-on

Reset

Timer

10 k

Output Three -state

Output

Buffer

Hold

Output

Low

QD

Data

Latch

(Load Option 1)

(Load Option 0)

10 k

Ω

Ω

Figure 1. Input Logic Selection Through Resistor Load Option

Jumper Options

V

DD

10 k

Ω

Output

Buffer

Output Three -state

Hold

Output

Low

QD

Data

Latch

Resistor Value R

Series Termination Resistor

R

Output Stra pp i ng Resi st or

Series Termination Resistor

R

Clock Load

Clock Load

Figure 2. Input Logic Selection Through Jumper Option

3

W210

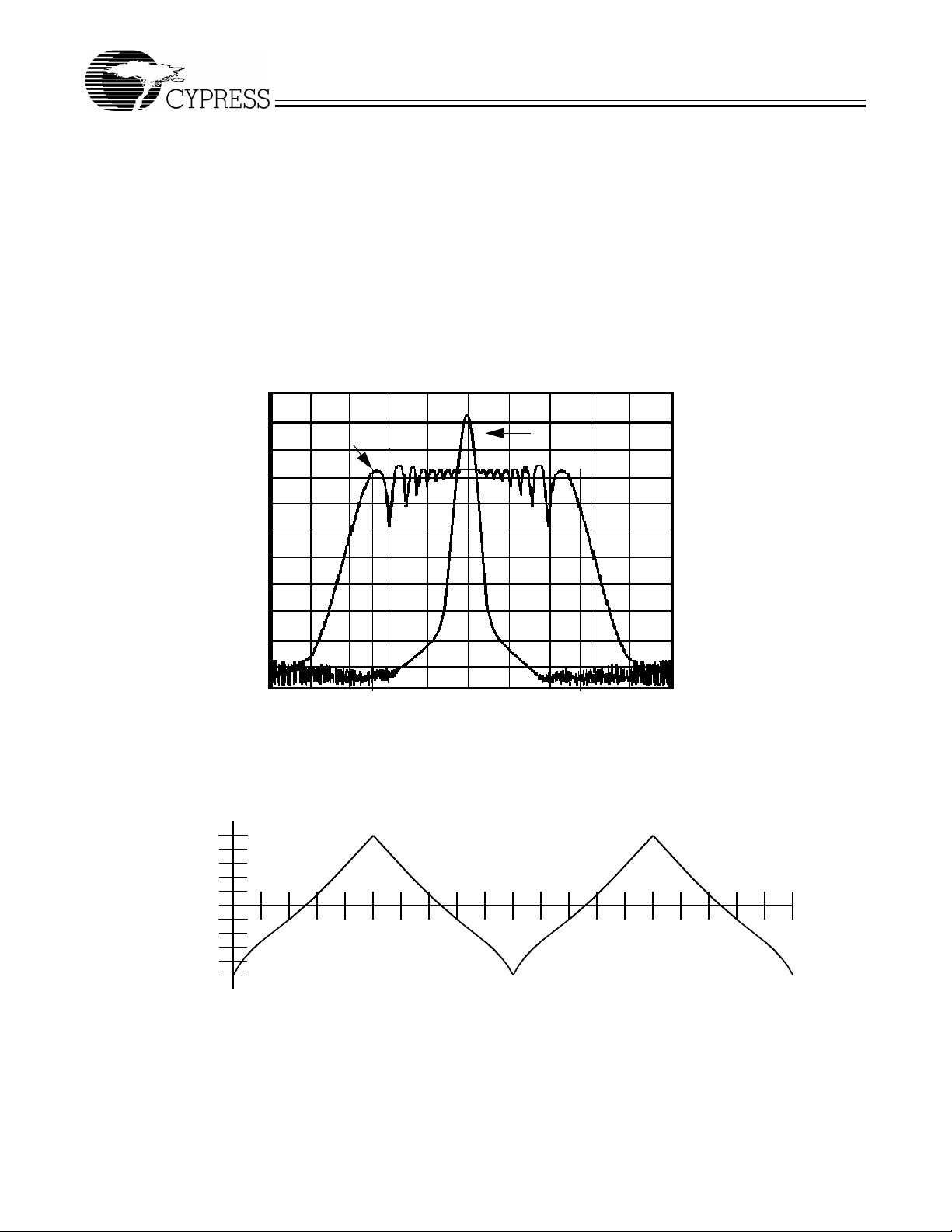

Spread Spectrum Frequency Tim ing G enera to r

The device generates a clock that is frequency modulated in

order to increase the bandwidth that it occu pies. By increas ing

the bandwidth of the fundamental and its harmonics, the amplitudes of the radiated electromagnetic emissions are reduced. This effect is depicted in Figure 3.

As shown in Figure 3, a harmonic of a modulated clock has a

much low er amplitu de than that of an un modulated si gnal. The

reduction in amplitude is dependent on the harmonic number

and the frequency deviation or spread. The equation for the

reduction is:

dB = 6.5 + 9*log

(P) + 9*log10(F)

10

Amplitude (dB)

5 dB/d iv

SSFTG Ty p ic al Clock

Where P is the percenta ge of de vi ation and F is the frequen cy

in MHz where the reduction is measured.

The output clock is modulated with a waveform depicted in

Figure 4. This waveform, as discussed in “Spread Spectrum

Clock Generation f or the Reducti on of Radiated Emissio ns” by

Bush, Fessler, and Hardin produces the maximum reduction

in the amplitude of radiated electromagnetic emissions. The

deviati on select ed for this chi p is speci fied in Table 6. Figure 4

details the Cypress spr eading pat tern. Cypres s does off er options with more spread and greater EMI reduction. Contact

your local Sales representative for details on these devices.

Spread Spectrum clocking is activated or deactivated by selecting the appropriate v al ues fo r bits 1–0 in data byte 0 of the

2

I

C data stream. Refer to Table 6 for more details.

-SS %

Frequency S pan (MHz)

+SS%

Figure 3. Clock Harmonic with and without SSCG Modulation Frequency Domain Representation

MAX (0%)

10%

20%

30%

40%

50%

60%

70%

80%

FREQUENCY

MIN (–0.5%)

90%

100%

10%

20%

30%

40%

50%

60%

70%

80%

90%

Figure 4. Typica l Modulation Profile

100%

4

W210

Serial Data Interface

The W210 features a two-pin, serial data interface that can be

used to configure internal register settings that control particular de vice funct ions. Upon po wer-up , the W210 i nitiali zes wit h

default register settings, therefore the use of this serial data

interface is optional. The serial interface is write-only (to the

clock chi p) and i s the dedi cated f unc tion of de v ice pi ns SDA TA

and SCLOCK. In motherboard applications, SDATA and

SCLOCK are typically driven by two logic outputs of the

T able 3. Serial Data Interface Control Functions Summary

Control Function Description Common Application

Clock Output Disable Any individual clock output(s) can be disabled. Dis-

CPU Clock Frequency

Selection

Spread Spectrum

Enabling

Output Three-state Puts clock output into a high imped ance state. Production PCB testing.

(Reserved) Reserved functio n for future device r evision or pro-

abled outputs ar e actively held LOW.

Provides CPU/PCI frequency selections through

software. Frequency is changed in a smooth and

controlled fashion.

Enables or disables spread spectrum clocking. For EMI reduction.

duc tion devi c e testi n g.

chipset. Clock device register changes are normally made

upon system initialization, if any are required. The interface

can also be used during system operation for power management functions. Tabl e 3 summarizes the control functions of

the serial data interface.

Operation

Data is written to the W210 in elev en bytes of eight bits each.

Bytes are written in the order shown in Table 4.

Unused outputs are di sabled to reduce EMI

and system power. Examples are clock outputs to unused PCI slots.

For alternate microprocessors and power

management options . Smooth freque ncy transition allows CPU frequency change under

normal system operati on.

No user applicat ion. Regist er bit must be wri tten as 0.

Table 4. Byte Writing Sequence

Byte Sequence Byte Name Bit Sequence Byte Description

1 Slave Address 11010010 Commands the W210 to accept the bits in Data Bytes 0–6 for internal

register configuration. Since other devices may exist on the same com mon serial data b us , it is neces sary to ha v e a speci fic s lav e address for

each potential receiver. The slave receiver address for the W210 is

11010010. Register sett ing will not be made if t he Slav e Address is not

correct (or is for an alternate slave recei ver).

2 Command

Code

3 Byte Count Don’t Care Unused by the W210, therefore bit values are ignored (“Don’t C a re”).

4 Data Byte 0 Refer to Ta ble 5 The data bits in Dat a Bytes 0 –7 set internal W 210 regi sters that co ntrol

5 Data Byte 1

6 Data Byte 2

7 Data Byte 3

8 Data Byte 4

9 Data Byte 5

10 Data Byte 6

11 Data Byte 7

Don’t Care Unused by the W210, therefore bit values are ignored (“Don’t Care”).

This byte m ust be inclu ded in the dat a write sequence to maintain pro per

byte allocatio n. The Command Code Byte is part of the standard serial

communication protocol and may be used when writing to another addressed slave receiver on the serial data bus.

This byte m ust be inclu ded in the dat a write sequence to maintain pro per

byte alloc ati on. The Byte Count Byte is part of the standard serial communication pr otocol and may be used wh en writing to another address ed

slave receiver on the serial data bus.

device operation. The data bits are only accept ed when the Address

Byte bit sequence is 11010010, as noted above. F or description of bit

control functions, refer to Table 5, Data Byte Serial Configuration Map.

5

Loading...

Loading...